Содержание

- 2. принципиальная схема С нижним уровнем функционального описания МС и ее составляющих связано понятие физической организации МС—

- 3. логическая организация логическая организация на уровне аппаратуры—это состав, функциональные связи и характеристики взаимодействия аппаратных модулей в

- 4. Архитектура МС это функциональные возможности аппаратных средств МС, используемые для представления программ и данных, а также

- 5. Каждый уровень организации МС и любая ее составная часть имеют достаточно сложную внутреннюю структуру, детализация которой

- 6. структура МПС

- 7. Микросистема состоит из построенного на базе МП центрального процессора (ЦП), основной памяти для хранения программ и

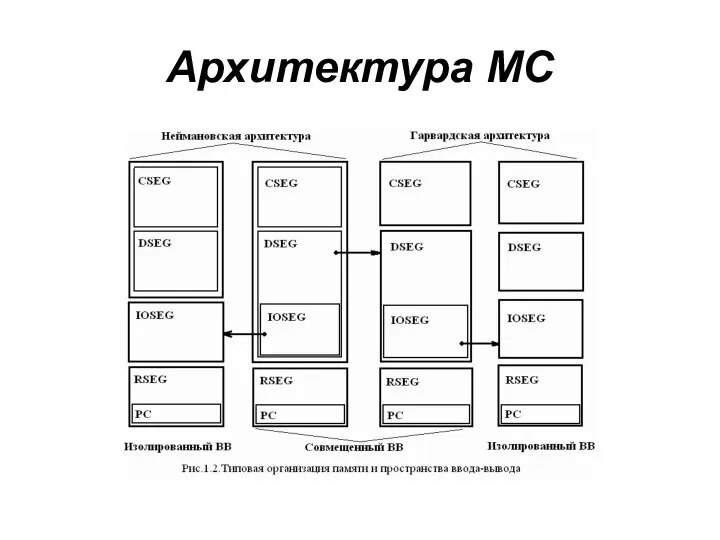

- 8. В большинстве современных микроЭВМ для хранения программ и данных используется одно пространство памяти. Такая организация получила

- 9. однокристальные микро-ЭВМ, представляющие класс однокристальных программируемых микроконтроллеров, выполнены по другой схеме, известной как архитектура Гарвардской лаборатории,

- 10. совершенствование архитектур обоих типов состояло в выделении специального пространства данных небольшого объема, которое сегодня известно как

- 11. Архитектура МС

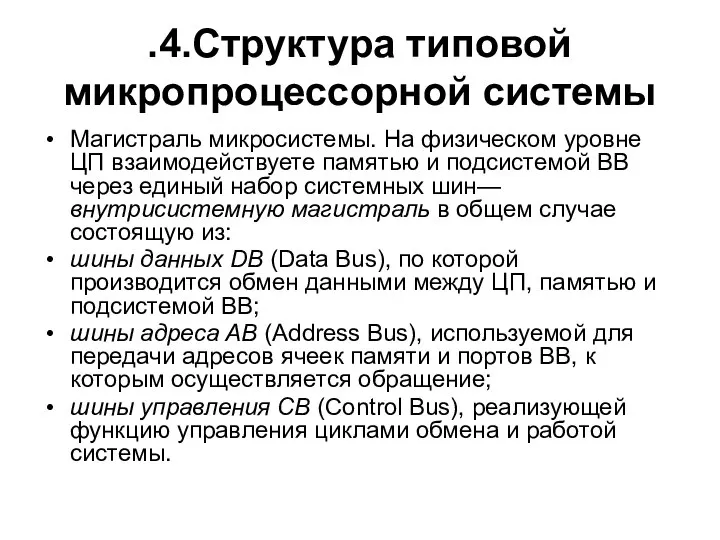

- 12. .4.Структура типовой микропроцессорной системы Магистраль микросистемы. На физическом уровне ЦП взаимодействуете памятью и подсистемой ВВ через

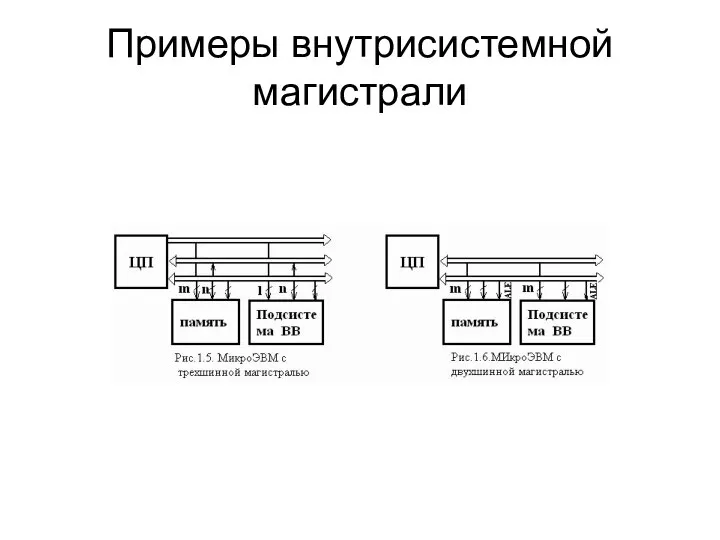

- 13. Примеры внутрисистемной магистрали

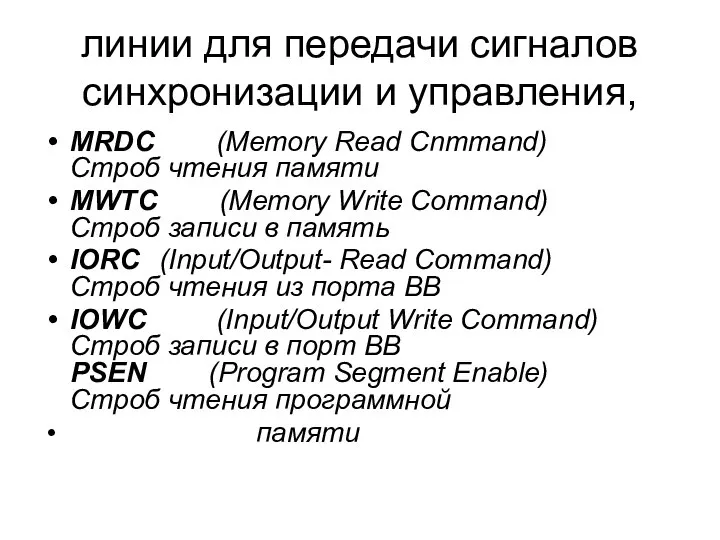

- 14. линии для передачи сигналов синхронизации и управления, MRDC (Memory Read Cnmmand) Строб чтения памяти MWTC (Memory

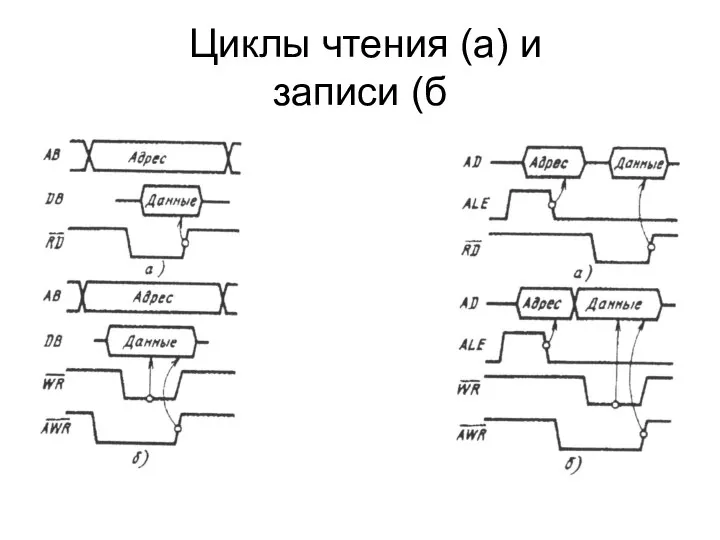

- 15. Циклы чтения (а) и записи (б

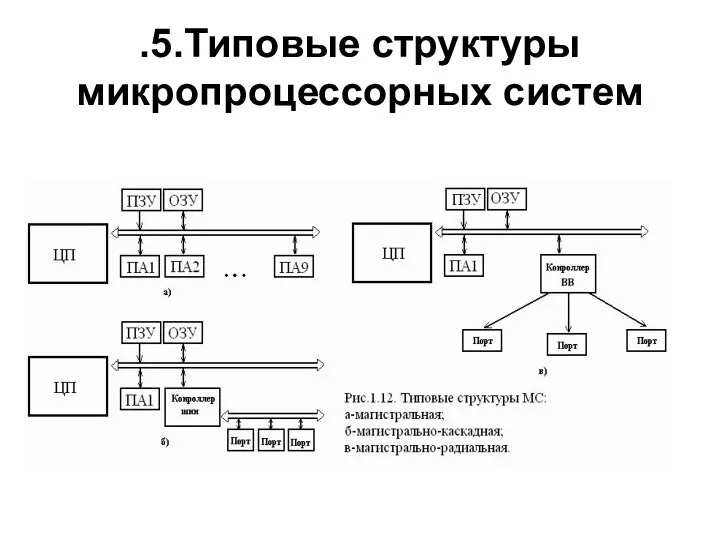

- 16. .5.Типовые структуры микропроцессорных систем

- 17. Типичная структура микропроцессорного устройства, системы.

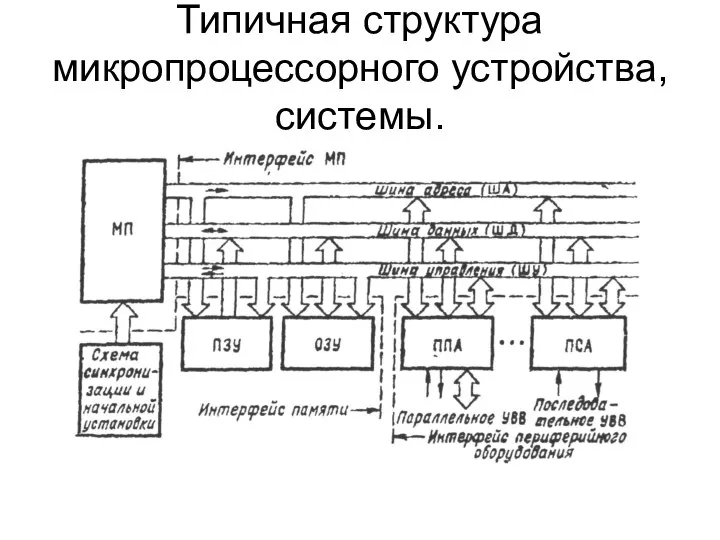

- 19. Скачать презентацию

Бал для золушки - презентация для начальной школы_

Бал для золушки - презентация для начальной школы_ Объединение русских земель вокруг Москвы Выполнила студентка 1-ого курса ФТД группы Т- 116с Цьопа Дарья

Объединение русских земель вокруг Москвы Выполнила студентка 1-ого курса ФТД группы Т- 116с Цьопа Дарья В братской семье ХОРДОВЫХ…

В братской семье ХОРДОВЫХ… Инженерная и научная деятельность

Инженерная и научная деятельность  Звукоусиливающий тракт

Звукоусиливающий тракт Деньги и денежные обращения

Деньги и денежные обращения  Икебана (картины)

Икебана (картины) Сигналы и их преобразования при цифровой обработке. Цифровая обработка сигналов

Сигналы и их преобразования при цифровой обработке. Цифровая обработка сигналов Газоснабжение Калининградской области

Газоснабжение Калининградской области Религия и искусство в системе культуры

Религия и искусство в системе культуры Логическая и физическая схема организации пространства в документальных БД.

Логическая и физическая схема организации пространства в документальных БД.  Дифилоботриоз

Дифилоботриоз Политический образ М.Г. Рахимова

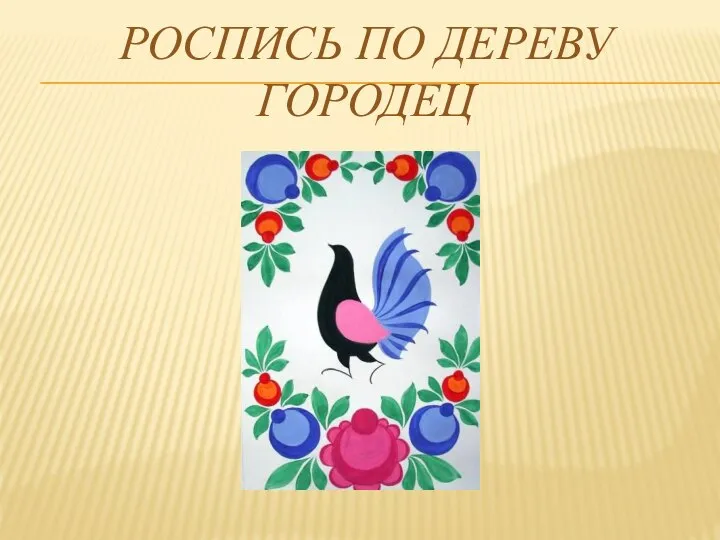

Политический образ М.Г. Рахимова Роспись по дереву ГОРОДЕЦ

Роспись по дереву ГОРОДЕЦ Царство грибов (3 класс) - презентация для начальной школы

Царство грибов (3 класс) - презентация для начальной школы Nicolaus Copernicus

Nicolaus Copernicus Функции менеджмента

Функции менеджмента Презентация Порядок получения и применения предварительного решения о стране происхождения товара

Презентация Порядок получения и применения предварительного решения о стране происхождения товара ГИГИЕНА И ФИЗИОЛОГИЯ ВОЕННОГО ТРУДА

ГИГИЕНА И ФИЗИОЛОГИЯ ВОЕННОГО ТРУДА  Юридическая Группа «СФЕРА»

Юридическая Группа «СФЕРА»  Парная регрессия

Парная регрессия  Diseminarea informaţiei despre resursele, serviciile şi produsele DIB prin intermediul reţelelor sociale Victoria Moşneaga Sergiu Burac

Diseminarea informaţiei despre resursele, serviciile şi produsele DIB prin intermediul reţelelor sociale Victoria Moşneaga Sergiu Burac  Уголовная ответственность медицинских работников

Уголовная ответственность медицинских работников Тема: Развитие индивидуального стиля учебной деятельности учащегося. (ИСУД)

Тема: Развитие индивидуального стиля учебной деятельности учащегося. (ИСУД) Прохождение государственной службы в таможенных органах

Прохождение государственной службы в таможенных органах Модели развития бухгалтерского учета в разных странах

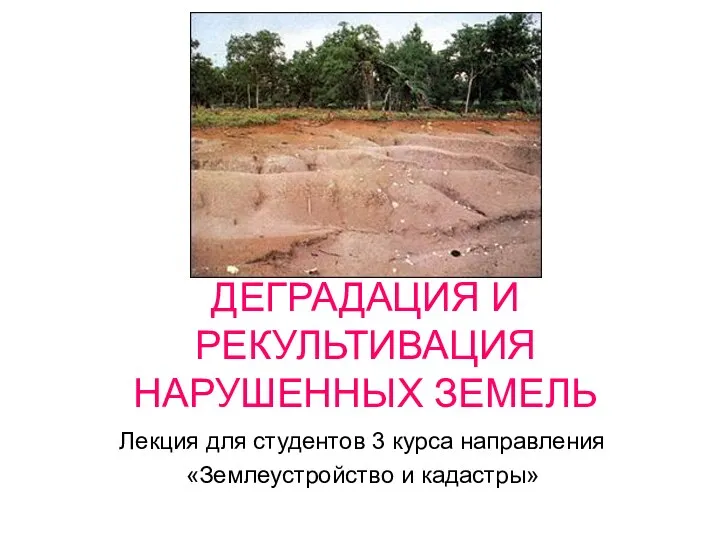

Модели развития бухгалтерского учета в разных странах ДЕГРАДАЦИЯ И РЕКУЛЬТИВАЦИЯ НАРУШЕННЫХ ЗЕМЕЛЬ

ДЕГРАДАЦИЯ И РЕКУЛЬТИВАЦИЯ НАРУШЕННЫХ ЗЕМЕЛЬ Правила игры в волейбол

Правила игры в волейбол