Содержание

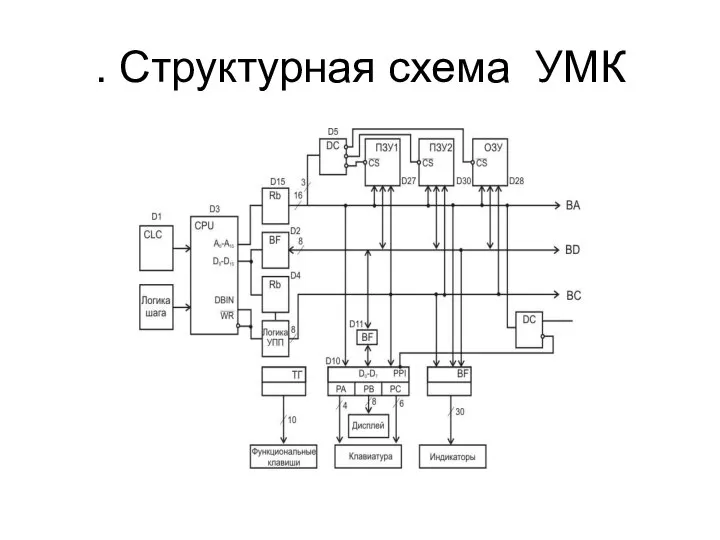

- 2. . Структурная схема УМК

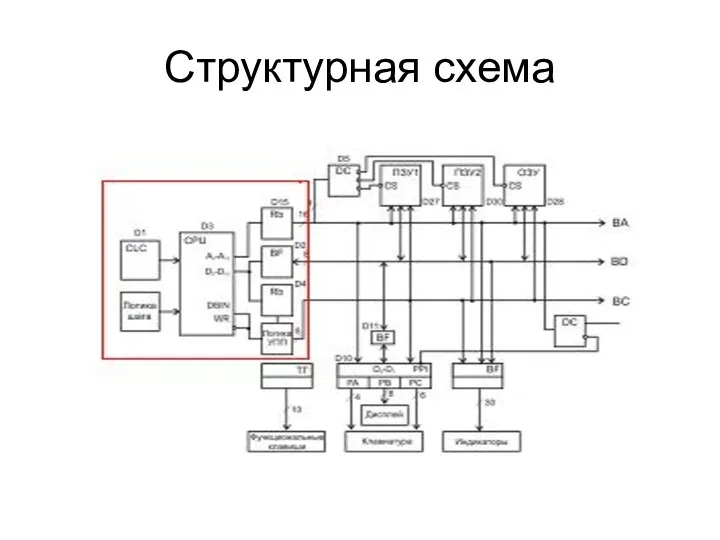

- 3. Структурная схема

- 4. Восьмиразрядные микропроцессоры

- 5. Процессор - основной блок ЭВМ, осуществляющий обработку данных. В настоящее время основным типом процессоров являются цифровые

- 6. Микропроцессор является программируемой универсальной БИС, способной выполнять функции центрального процессора ЭВМ, т. е. микропроцессор может считывать

- 7. Универсальный процессор - процессор, имеющий архитектуру, набор структурных блоков, систем команд и конструктивно-технологическое исполнение, позволяющее одинаково

- 8. Чип микропроцессора

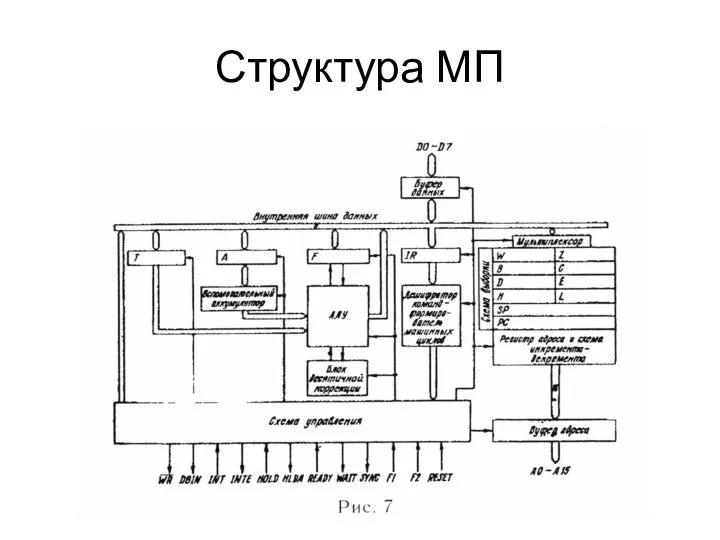

- 9. Структура МП

- 10. Блок регистров

- 12. . Средства обмена МП Начальная установка. При одновременном включении питания —5; +5 и 12 В (или

- 13. Микропроцессор выполняет различные команды за различное время в течение от 1 до 5 машинных циклов (Ml—М5)

- 14. Особые состояния МП 1.Пуск 2.Ожидание 3.Захват 4.Останов 5.Прерывания

- 15. Состояние «ожидание» предназначено для согласования работы микропроцессора с медленнодействующими памятью или внешними устройствами, которые не успевают

- 16. Состояние «захват». По сигналу высокого уровня, поступающего от внешних устройств или пульта оператора на вход HOLD,

- 17. Состояние «останов» похоже на состояние «ожидание», только оно происходит в результате выполнения команды HLT, выйти из

- 18. . Режим прерывания . Режим прерывания может наступить при подаче на вход INT сигнала высокого уровня

- 19. Интерфейс ввода-вывода микропроцессора Первый метод предполагает обращение к внешним устройствам как к ячейкам памяти Таким образом,

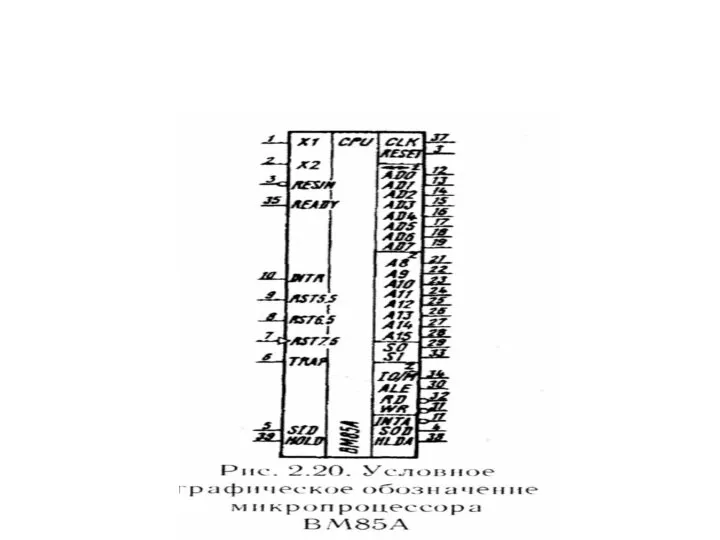

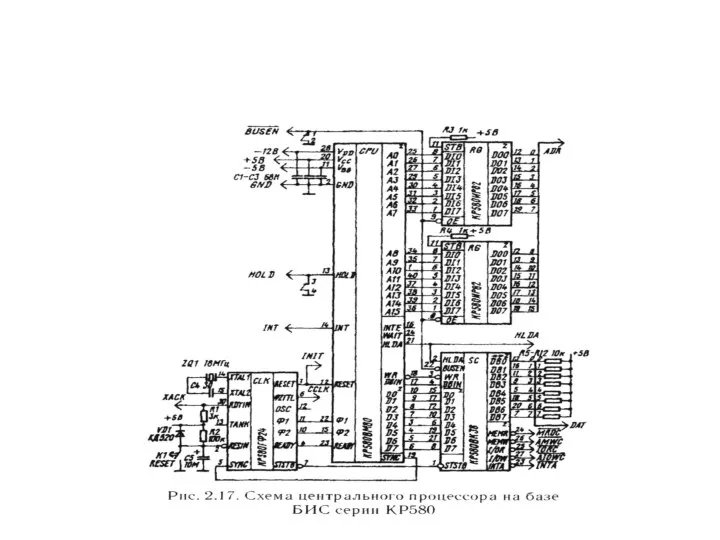

- 22. МОДУЛЬ ЦЕНТРАЛЬНОГО ПРОЦЕССОРА

- 29. Буферный регистр

- 30. Основой схемы является 8-разрядный регистр-защелка со статическим синхро-входом STB (Strobe). Запись данных в регистр разрешена при

- 31. Шинный формирователь

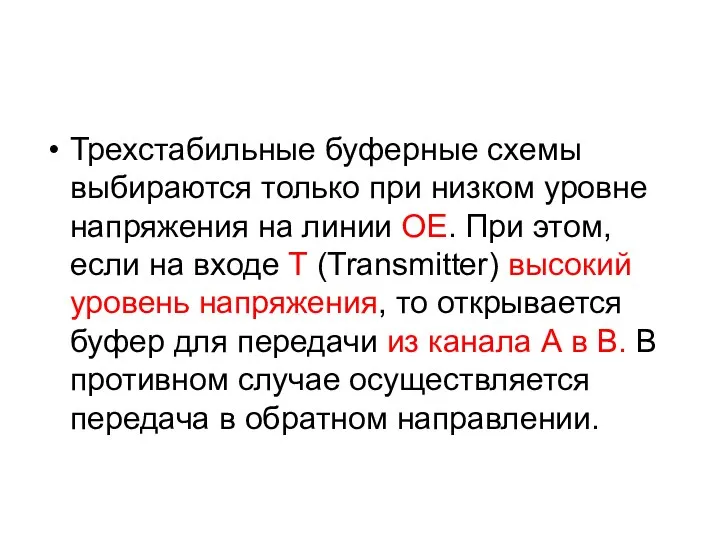

- 32. Трехстабильные буферные схемы выбираются только при низком уровне напряжения на линии ОЕ. При этом, если на

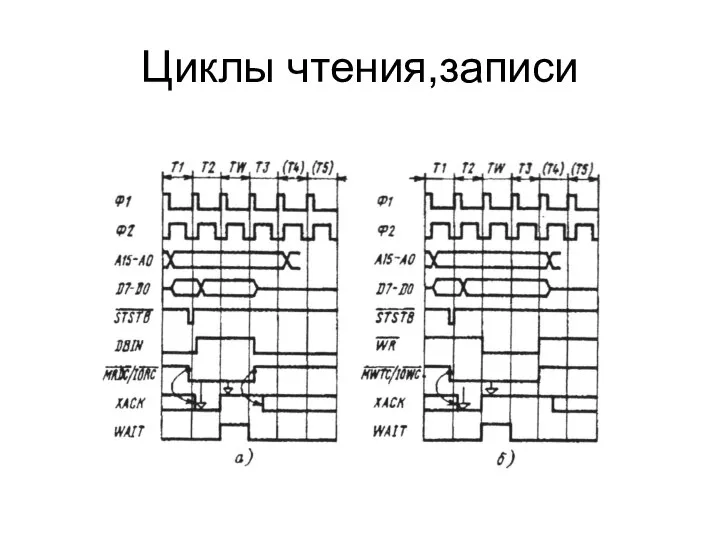

- 33. Циклы чтения,записи

- 34. Процессор с мультиплексируемой шиной

- 36. Скачать презентацию

4 U ЗАГОЛОВКИ

4 U ЗАГОЛОВКИ Солнечная радиация на земле

Солнечная радиация на земле  Свадебные традиции Италии

Свадебные традиции Италии Проблемы подростков и их отражение в русской литературе

Проблемы подростков и их отражение в русской литературе Продовольственная проблема населения

Продовольственная проблема населения Компьютер - инструмент переработки информации

Компьютер - инструмент переработки информации  Аэробика. Направления аэробики

Аэробика. Направления аэробики Методы создания p-n-переходов. Точечные переходы

Методы создания p-n-переходов. Точечные переходы Общее представление о научно-методическом обеспечении спортивной подготовки в спортивных играх

Общее представление о научно-методическом обеспечении спортивной подготовки в спортивных играх Презентация к урока 1-2

Презентация к урока 1-2 Основи діловодства. Розпорядчі документи

Основи діловодства. Розпорядчі документи Основные черты права Древнего Китая Выполнила студентка группы ю104 Рыжкова Анастасия

Основные черты права Древнего Китая Выполнила студентка группы ю104 Рыжкова Анастасия Виды корректуры и методы работы с корректурой

Виды корректуры и методы работы с корректурой Тема: Наклонение глагола. (урок - сказка) Учитель: Шитова С.И.

Тема: Наклонение глагола. (урок - сказка) Учитель: Шитова С.И. Гигиена кожи. принципы закаливания

Гигиена кожи. принципы закаливания The Inventor of Basketball

The Inventor of Basketball Основы религиозных культур и светской этики Основы религиозных культур и светской этики

Основы религиозных культур и светской этики Основы религиозных культур и светской этики  Управление проектами расширенный курс Семинар-тренинг на тему общего менеджмента

Управление проектами расширенный курс Семинар-тренинг на тему общего менеджмента Правовой статус личности. Тема 1.7

Правовой статус личности. Тема 1.7 Презентация Анализ мировых запасов нефти, природного газа

Презентация Анализ мировых запасов нефти, природного газа  1. Замок феодала.

1. Замок феодала. Питание в походе

Питание в походе PHP. Функции. Основы работы

PHP. Функции. Основы работы Презентация на тему "Целиакия" - скачать презентации по Медицине

Презентация на тему "Целиакия" - скачать презентации по Медицине Мастер-класс «Учебно-исследовательская, проектная деятельность в обучении географии как ресурс формирования опыта творческой де

Мастер-класс «Учебно-исследовательская, проектная деятельность в обучении географии как ресурс формирования опыта творческой де Коммуникативный подход Карла Роджерса

Коммуникативный подход Карла Роджерса  ХУДОЖЕСТВЕННОЕ ТВОРЧЕСТВО КАК ДЕЯТЕЛЬНОСТЬ, ПРОЦЕСС И ПРОДУКТ

ХУДОЖЕСТВЕННОЕ ТВОРЧЕСТВО КАК ДЕЯТЕЛЬНОСТЬ, ПРОЦЕСС И ПРОДУКТ Тормозная система легкового автомобиля

Тормозная система легкового автомобиля