Содержание

- 2. АЦП параллельного преобразования АЦП прямого преобразования получили широкое распространение в 1960-1970 годах, и стали производиться в

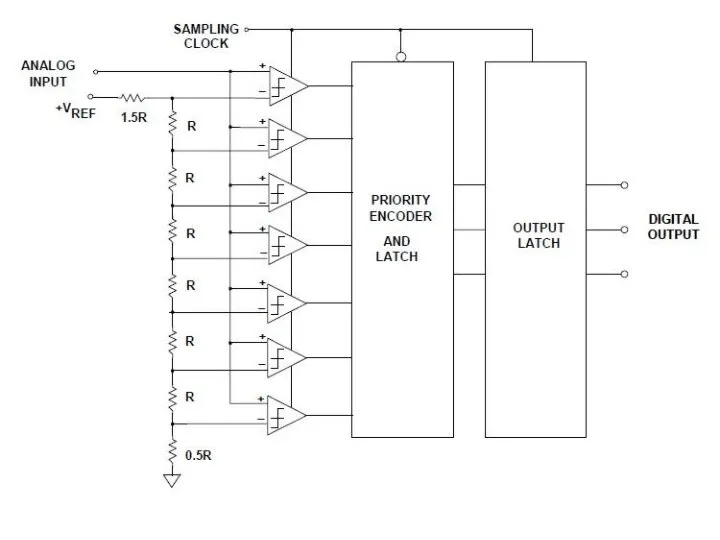

- 4. Принцип действия АЦП предельно прост: входной сигнал поступает одновременно на все «плюсовые» входы компараторов, а на

- 5. АЦП последовательного приближения АЦП последовательного приближения реализует алгоритм «взвешивания», восходящий еще к Фибоначчи. В своей книге

- 6. Аналого-цифровой преобразователь последовательного приближения (SAR, Successive Approximation Register) измеряет величину входного сигнала, осуществляя ряд последовательных «взвешиваний»,

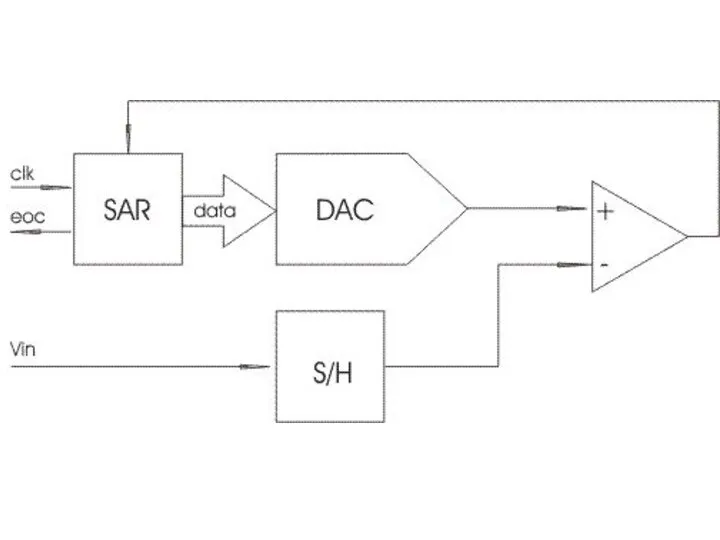

- 8. Таким образом, АЦП последовательного приближения состоит из следующих узлов: Компаратор. Он сравнивает входную величину и текущее

- 9. Достоинством устройства является относительно высокая скорость преобразования: время преобразования N-битного АЦП составляет N тактов. Точность преобразования

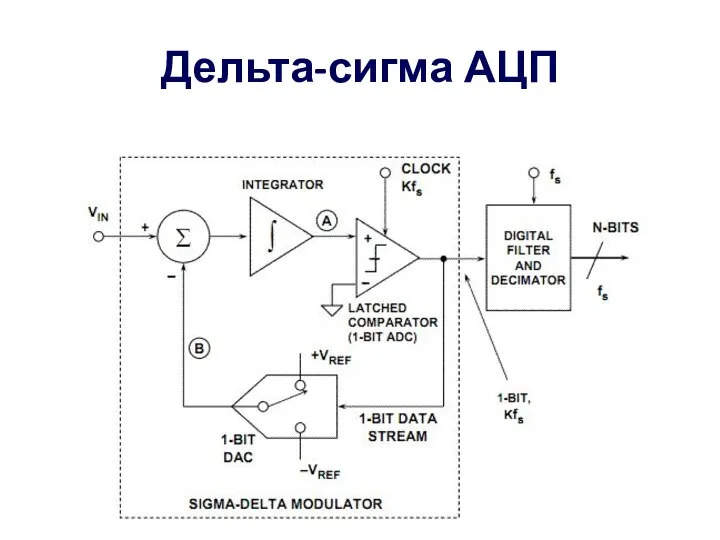

- 10. Дельта-сигма АЦП

- 11. Принцип действия данного АЦП несколько более сложен, чем у других типов АЦП. Его суть в том,

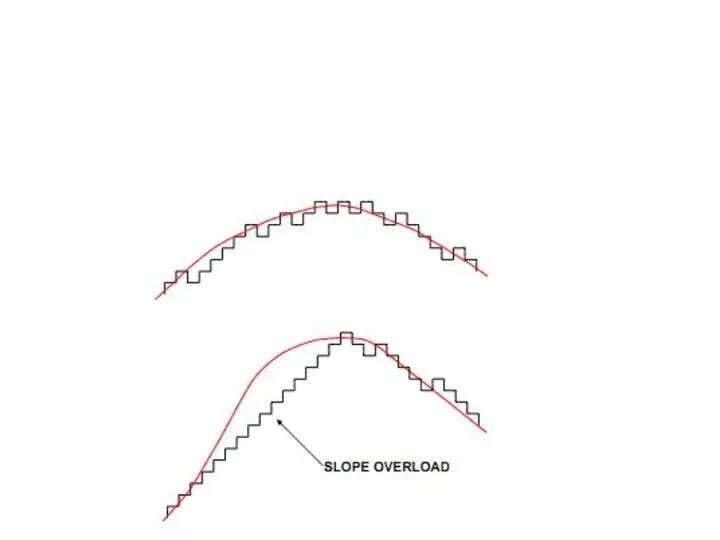

- 13. Показаны сигналы в АЦП при нулевом уровне на входе (сверху) и при уровне Vref/2 (снизу).

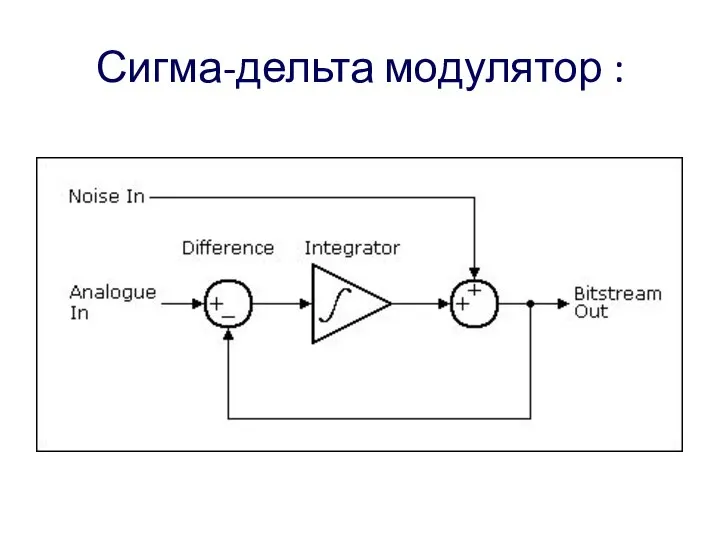

- 14. Сигма-дельта модулятор :

- 15. Здесь компаратор представлен как сумматор, который суммирует непрерывный полезный сигнал и шум квантования. Пусть интегратор имеет

- 17. Скачать презентацию

Министерство образования и науки Российской Федерациии

Министерство образования и науки Российской Федерациии Берегите воду - презентация для начальной школы_

Берегите воду - презентация для начальной школы_ Личная гигиена. Гигиена кожи, одежды. Цель: объяснить значение личной гигиены для общего состояния здоровья; сформировать предста

Личная гигиена. Гигиена кожи, одежды. Цель: объяснить значение личной гигиены для общего состояния здоровья; сформировать предста Организация и размещение населения в защитных сооружениях Работу выполнила Зыкова Анна

Организация и размещение населения в защитных сооружениях Работу выполнила Зыкова Анна Расчет основного оборудования электрической части ТЭЦ 2×110;110 МВт

Расчет основного оборудования электрической части ТЭЦ 2×110;110 МВт ВОЗМОЖНОСТИ ИСПОЛЬЗОВАНИЯ ИКТ НА УРОКАХ ФИЗИЧЕСКОЙ КУЛЬТУРЫ Подготовила: Учитель физической культуры 1 квалификационной катег

ВОЗМОЖНОСТИ ИСПОЛЬЗОВАНИЯ ИКТ НА УРОКАХ ФИЗИЧЕСКОЙ КУЛЬТУРЫ Подготовила: Учитель физической культуры 1 квалификационной катег Основы проектной деятельности

Основы проектной деятельности 8429 и 8430 ТНВЭД ТС Терешкова М. ДС5 ФТД5

8429 и 8430 ТНВЭД ТС Терешкова М. ДС5 ФТД5 Ассортимент декоративных растений

Ассортимент декоративных растений Культура. Культурный комплекс. Культурное наследие. Культурные универсалии. Культурные нормы

Культура. Культурный комплекс. Культурное наследие. Культурные универсалии. Культурные нормы Thanksgiving Day

Thanksgiving Day Современные средства радиоконтроля производства предприятия ООО «Радиософт»

Современные средства радиоконтроля производства предприятия ООО «Радиософт» ЗДОРОВЬЕ и ВРЕДНЫЕ ПРИВЫЧКИ

ЗДОРОВЬЕ и ВРЕДНЫЕ ПРИВЫЧКИ Формы реализации права

Формы реализации права Малыш и Карлсон - часть 2 - презентация для начальной школы

Малыш и Карлсон - часть 2 - презентация для начальной школы Повторение курса «Христианские добродетели»

Повторение курса «Христианские добродетели» Духовная жизнь серебряного века

Духовная жизнь серебряного века Особенности восприятия изобразительного искусства Выполнила: Накраплённая Е.А.

Особенности восприятия изобразительного искусства Выполнила: Накраплённая Е.А. Производственно-техническая база предприятий автосервиса (Лекция № 5)

Производственно-техническая база предприятий автосервиса (Лекция № 5) Витамины и минеральный обмен

Витамины и минеральный обмен Абсолютные относительные и средние величины

Абсолютные относительные и средние величины Современные подходы к управлению производственными предприятиями

Современные подходы к управлению производственными предприятиями Введение в язык шейдеров OpenGL

Введение в язык шейдеров OpenGL Порядок надання адміністративних послуг, насамперед базових, і параметри якості послуг

Порядок надання адміністративних послуг, насамперед базових, і параметри якості послуг Презентация Роль и значение таможни в современной торговле

Презентация Роль и значение таможни в современной торговле  Распределение памяти

Распределение памяти Причины снижения продуктивности скважин при РНМ

Причины снижения продуктивности скважин при РНМ Строки в Pascal. Решение задач

Строки в Pascal. Решение задач