Содержание

- 2. ОСНОВНЫЕ ТЕМЫ ЛЕКЦИИ ТРИГГЕРЫ : R-S-, D- ОДНОТАКТНЫЕ и ДВУХТАКТНЫЕ ТРИГГЕРЫ ТРИГГЕРЫ : J-K-, T-

- 3. ТРИГГЕРЫ С точки зрения общей электроники ТРИГГЕР - это УСИЛИТЕЛЬ ПОСТОЯННОГО ТОКА с глубокой положительной обратной

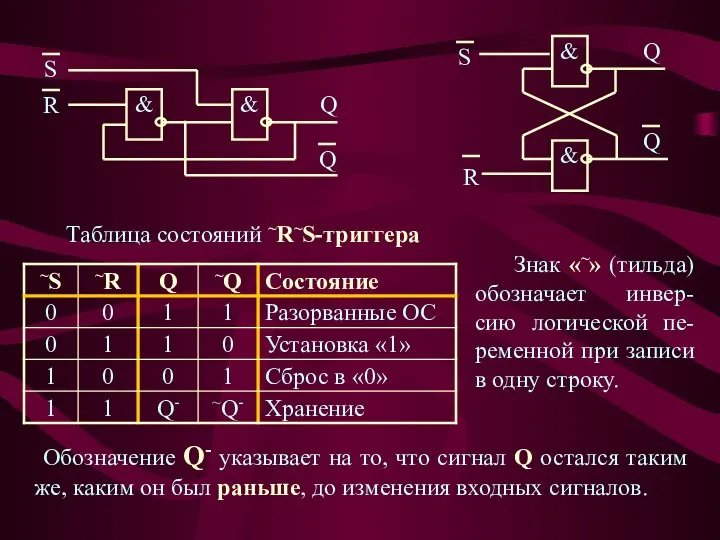

- 4. Обозначение Q- указывает на то, что сигнал Q остался таким же, каким он был раньше, до

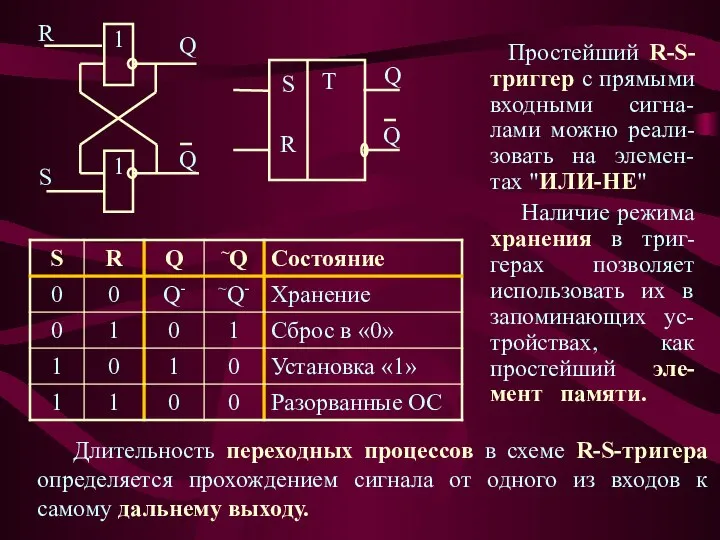

- 5. Простейший R-S-триггер с прямыми входными сигна-лами можно реали-зовать на элемен-тах "ИЛИ-НЕ" Наличие режима хранения в триг-герах

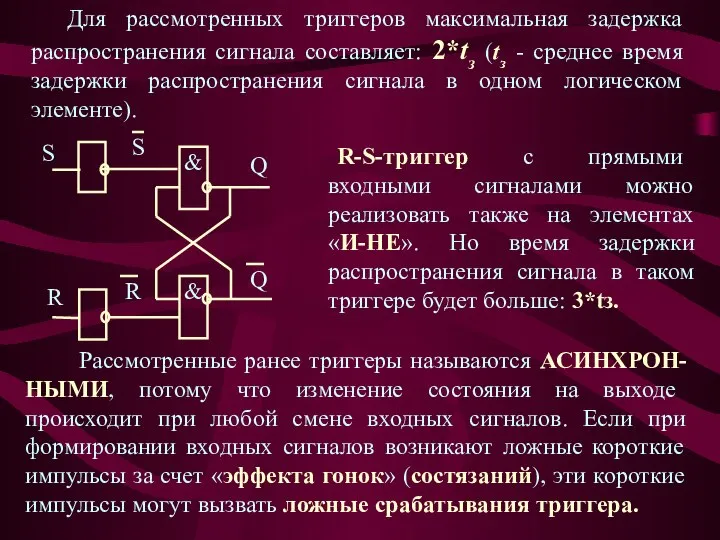

- 6. R-S-триггер с прямыми входными сигналами можно реализовать также на элементах «И-НЕ». Но время задержки распространения сигнала

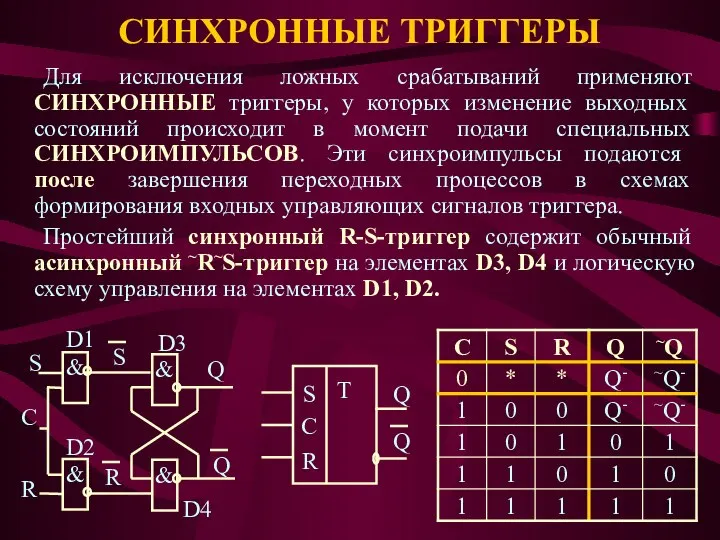

- 7. СИНХРОННЫЕ ТРИГГЕРЫ Для исключения ложных срабатываний применяют СИНХРОННЫЕ триггеры, у которых изменение выходных состояний происходит в

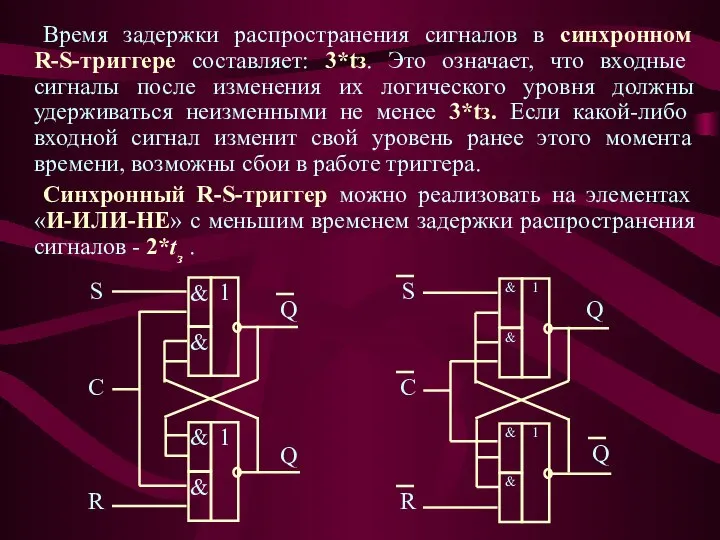

- 8. Время задержки распространения сигналов в синхронном R-S-триггере составляет: 3*tз. Это означает, что входные сигналы после изменения

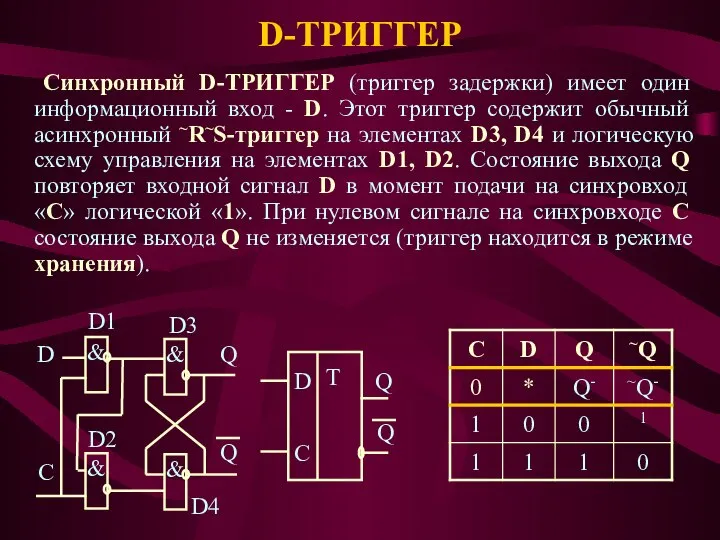

- 9. D-ТРИГГЕР Синхронный D-ТРИГГЕР (триггер задержки) имеет один информационный вход - D. Этот триггер содержит обычный асинхронный

- 10. У синхронного D-триггера отсутствует режим разрыва положительной обратной связи, т.е. все комбинации входных сигналов являются допустимыми.

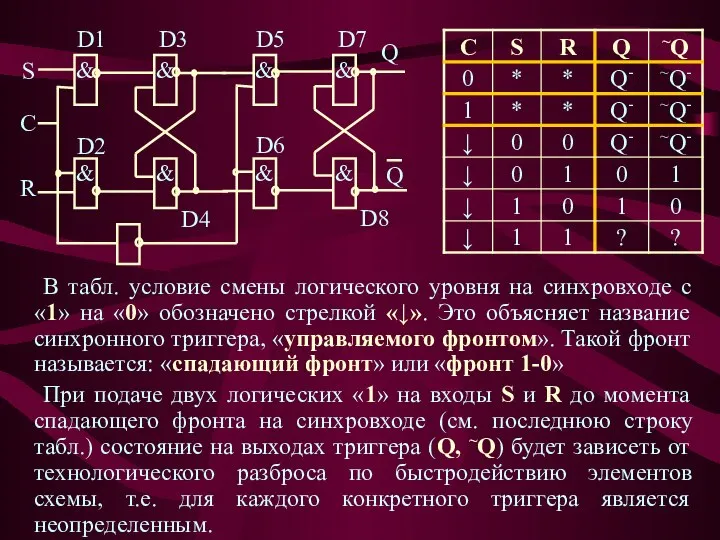

- 11. В табл. условие смены логического уровня на синхровходе с «1» на «0» обозначено стрелкой «↓». Это

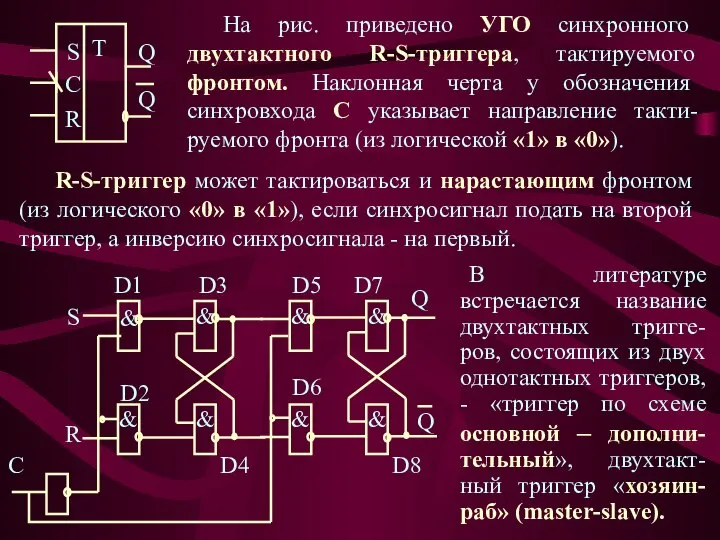

- 12. В литературе встречается название двухтактных тригге-ров, состоящих из двух однотактных триггеров, - «триггер по схеме основной

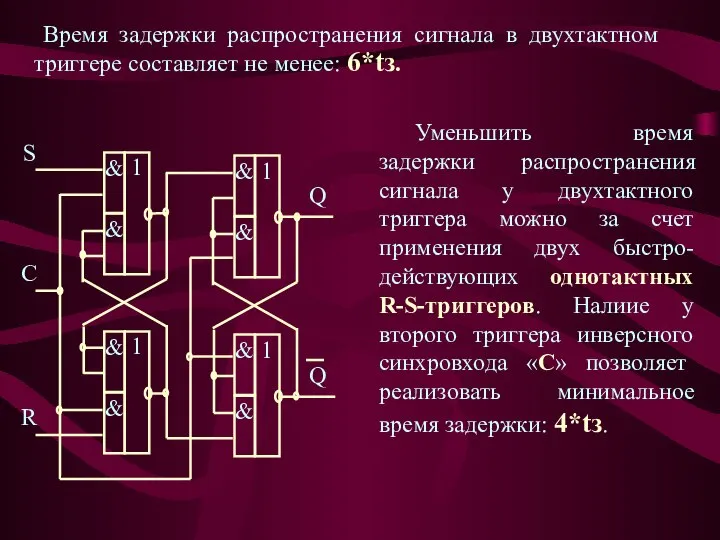

- 13. Время задержки распространения сигнала в двухтактном триггере составляет не менее: 6*tз. Уменьшить время задержки распространения сигнала

- 14. Т-триггер На основе R-S-триггера можно реализовать Т-триггер (счетный триггер), т.е. триггер, изменяющий свое выходное состояние по

- 15. Для построения Т-триггера принципиально необходим двухтактный триггер. Первый триггер в течение одного логического уровня на входе

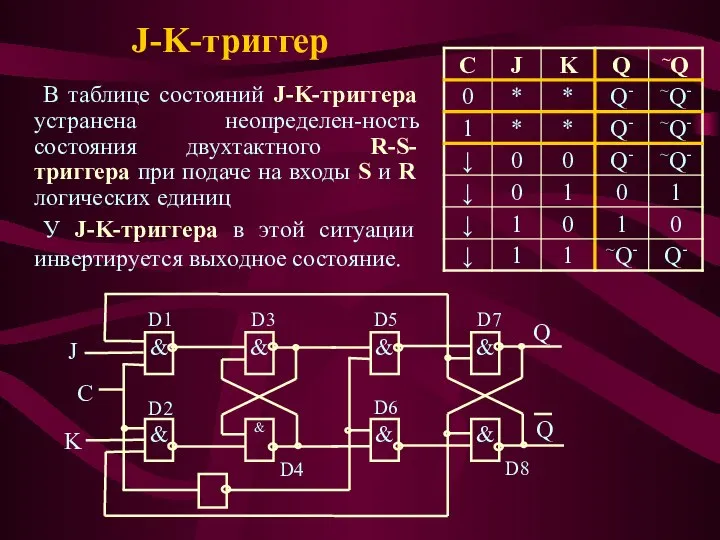

- 16. J-K-триггер В таблице состояний J-K-триггера устранена неопределен-ность состояния двухтактного R-S-триггера при подаче на входы S и

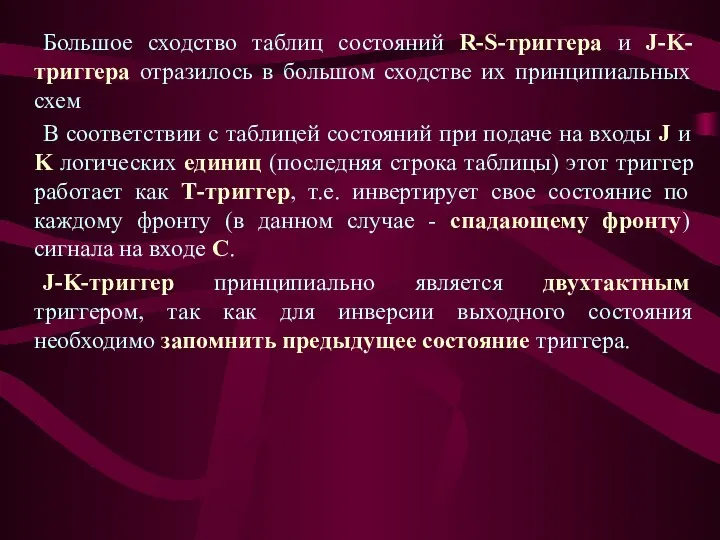

- 17. Большое сходство таблиц состояний R-S-триггера и J-K-триггера отразилось в большом сходстве их принципиальных схем В соответствии

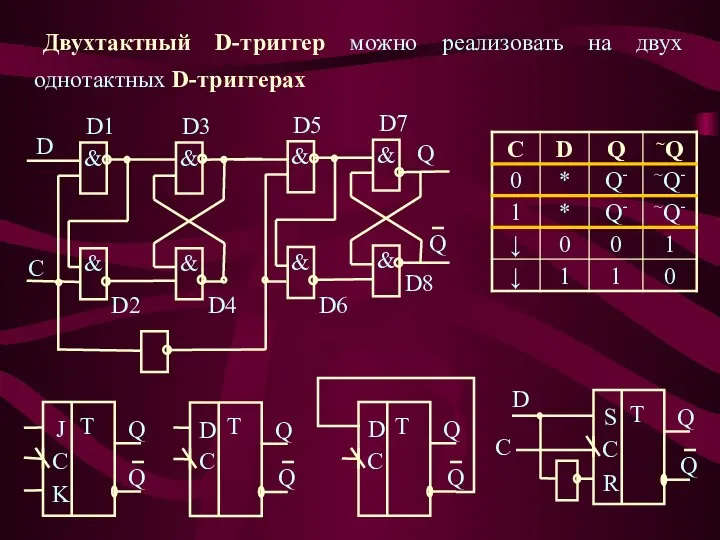

- 18. Двухтактный D-триггер можно реализовать на двух однотактных D-триггерах D1 D2 & & D3 D4 & &

- 19. Вопросы для экспресс-контроля 1. Назовите основные состояния триггера. 2. Какие недостатки имеются у асинхронного триггера? 3.

- 20. Вопросы для экспресс-контроля 7. Чем отличаются R-S- и J-K-триггеры? 8. Что такое счетный триггер? Как можно

- 22. Скачать презентацию

Разработка программного обеспечения (Software Engineering). Создание ПО

Разработка программного обеспечения (Software Engineering). Создание ПО Достижения субкультуры

Достижения субкультуры  Физическая культура и ее структурные компоненты

Физическая культура и ее структурные компоненты Казань. Достопримечательности

Казань. Достопримечательности Михаил Иванович Грибушин (1832 – 1889)

Михаил Иванович Грибушин (1832 – 1889) Знакомство с БПЛА. История развития, области применения

Знакомство с БПЛА. История развития, области применения Семья. Семейные традиции

Семья. Семейные традиции Шок

Шок Статика и динамика технологических объектов управления

Статика и динамика технологических объектов управления Брендинг в условиях меняющегося мира

Брендинг в условиях меняющегося мира Комплексная система контроля доступа и видеонаблюдения на базе программного обеспечения TRASSIR и Sphinx

Комплексная система контроля доступа и видеонаблюдения на базе программного обеспечения TRASSIR и Sphinx Алкоголизм г. Бердянск 2010

Алкоголизм г. Бердянск 2010 Тақырыбы:Томбоз,Эмболия, Ишемия. Орындаған:Нұрәділ Айгерім ЛД305топ.

Тақырыбы:Томбоз,Эмболия, Ишемия. Орындаған:Нұрәділ Айгерім ЛД305топ. РАННЕЕ ДЕТСТВО

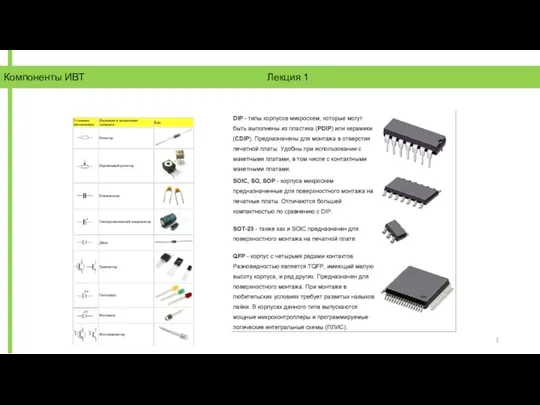

РАННЕЕ ДЕТСТВО Компоненты средств ИВТ

Компоненты средств ИВТ Национальная хозяйственная система Сингапура

Национальная хозяйственная система Сингапура Смесеобразование в бензиновых двигателях

Смесеобразование в бензиновых двигателях Теория алгоритмов. Сортировка массива. (Лекция 17)

Теория алгоритмов. Сортировка массива. (Лекция 17) Роль средств массовой информации в демократическом правовом государстве

Роль средств массовой информации в демократическом правовом государстве Методы точечного оценивания

Методы точечного оценивания  Презентация "Рембрандт, его картины" - скачать презентации по МХК

Презентация "Рембрандт, его картины" - скачать презентации по МХК Анализ работы ШМО учителей начальных классов

Анализ работы ШМО учителей начальных классов История развития ГТО

История развития ГТО Заборы и ворота

Заборы и ворота Механические и строительные свойства и характеристики грунтов

Механические и строительные свойства и характеристики грунтов Презентация Третьи лица, не заявляющие самостоятельные требования относительно предмета спора

Презентация Третьи лица, не заявляющие самостоятельные требования относительно предмета спора Допуски и посадки. Взаимозаменяемость

Допуски и посадки. Взаимозаменяемость Новогодние обычаи Японии

Новогодние обычаи Японии