Содержание

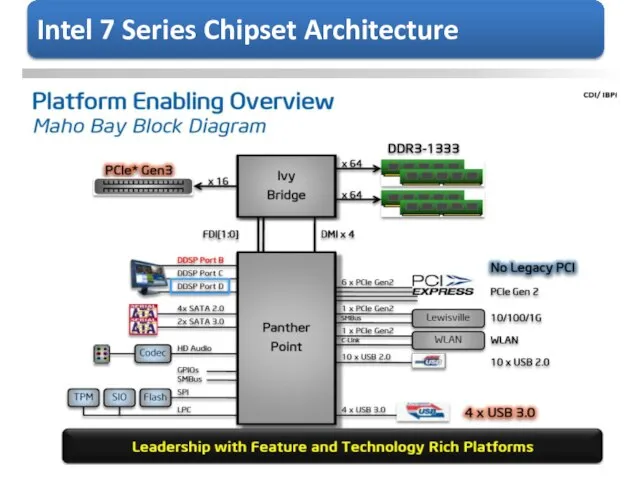

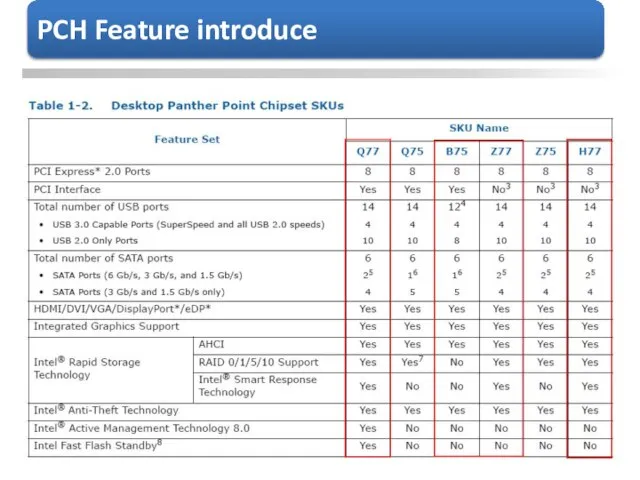

- 2. Platform Structure CPU feature introduce Intel 7 series chipset architecture Critical Power Flow Clock Distribution Power

- 8. Platform Structure CPU feature introduce Intel 7 series chipset architecture Critical Power Flow Clock Distribution Power

- 11. Platform Structure CPU feature introduce Intel 7 series chipset architecture Critical Power Flow Clock Distribution Power

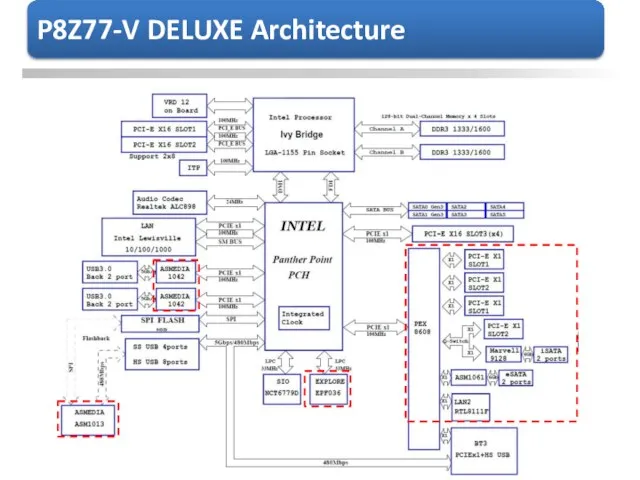

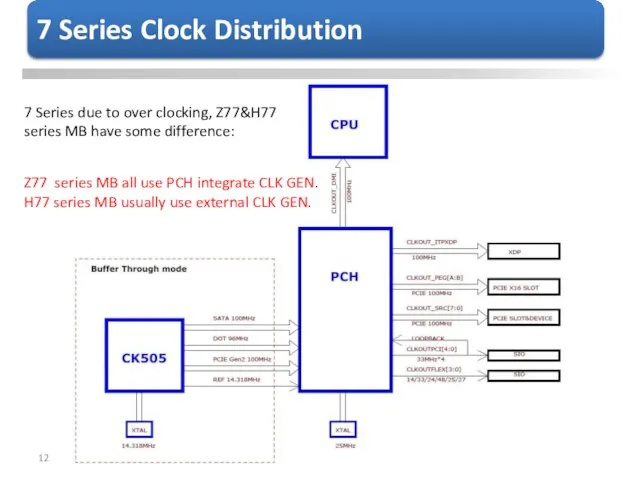

- 12. 7 Series due to over clocking, Z77&H77 series MB have some difference: Z77 series MB all

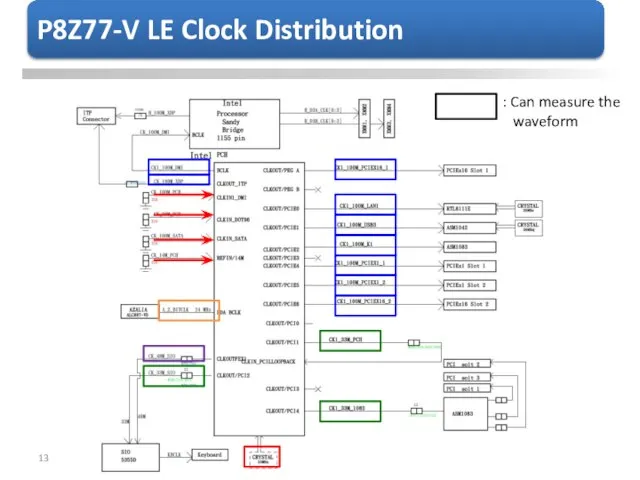

- 13. : Can measure the waveform

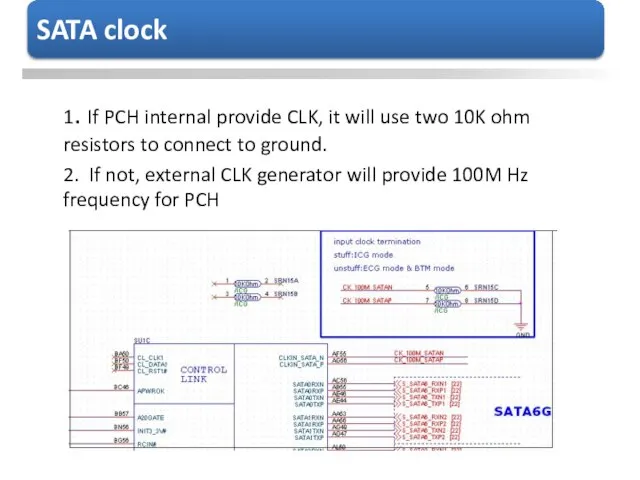

- 14. 1. If PCH internal provide CLK, it will use two 10K ohm resistors to connect to

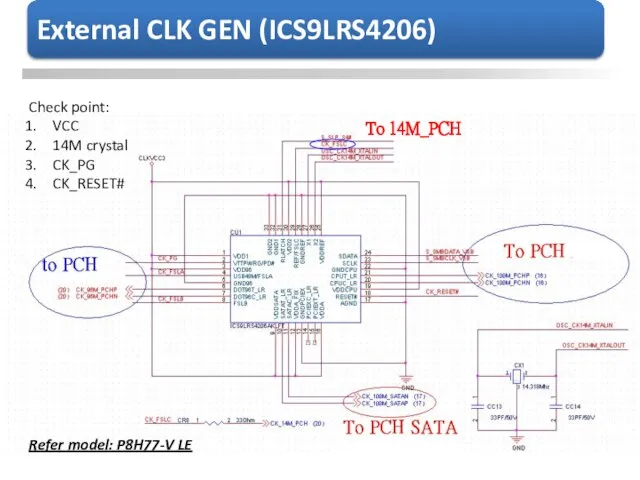

- 15. To 14M_PCH Check point: VCC 14M crystal CK_PG CK_RESET# Refer model: P8H77-V LE

- 16. Platform Structure CPU feature introduce Intel 7 series chipset architecture Critical Power Flow Clock Distribution Power

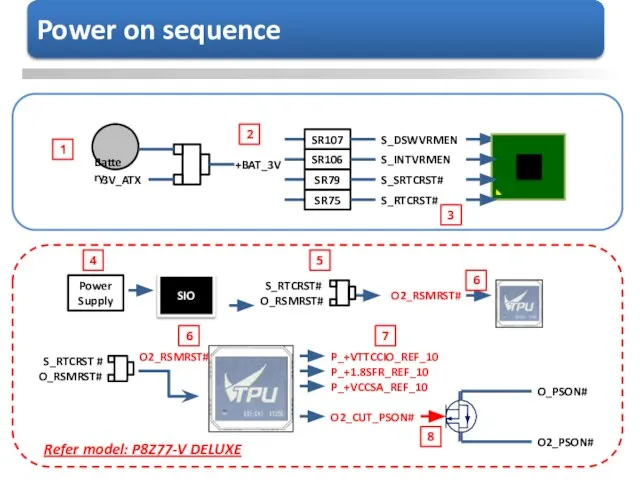

- 17. SIO 3V_ATX +BAT_3V SR107 S_DSWVRMEN Power Supply S_RTCRST# O_RSMRST# O2_RSMRST# 1 2 3 4 6 SR106

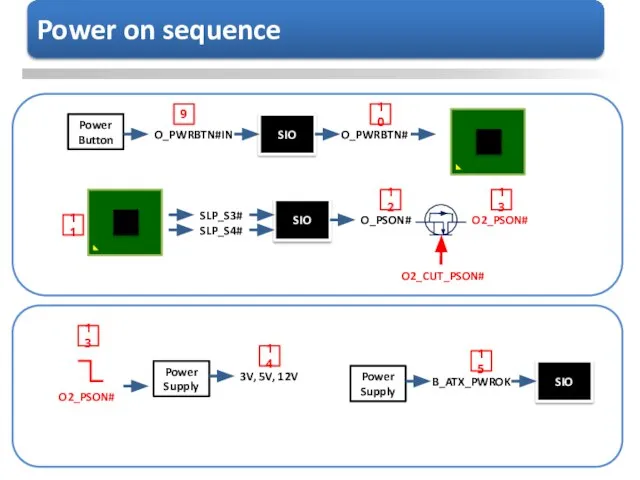

- 18. SIO Power Button O_PWRBTN#IN O_PWRBTN# SIO SLP_S3# SLP_S4# O_PSON# O2_CUT_PSON# O2_PSON# Power Supply O2_PSON# 3V, 5V,

- 20. Platform Structure CPU feature introduce Intel 7 series chipset architecture Critical Power Flow Clock Distribution Power

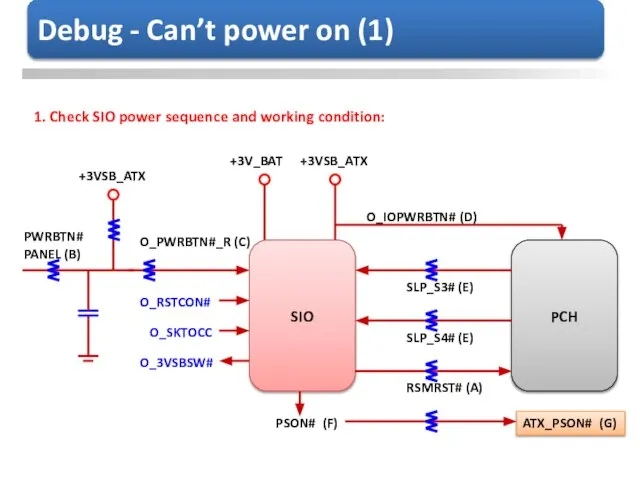

- 21. +3VSB_ATX +3VSB_ATX PWRBTN# PANEL (B) 1. Check SIO power sequence and working condition: SIO PCH O_PWRBTN#_R

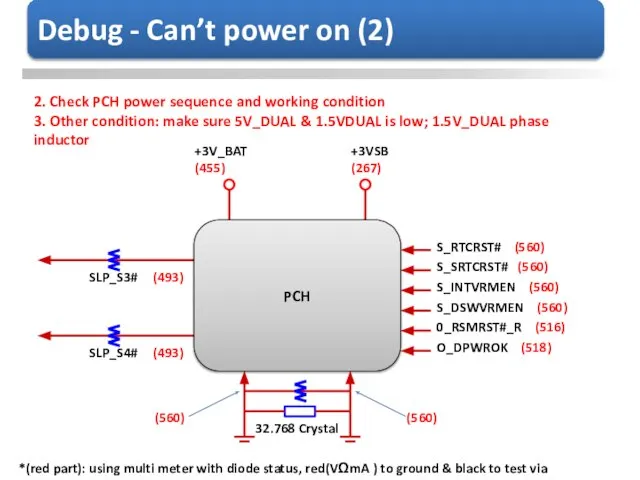

- 22. 2. Check PCH power sequence and working condition 3. Other condition: make sure 5V_DUAL & 1.5VDUAL

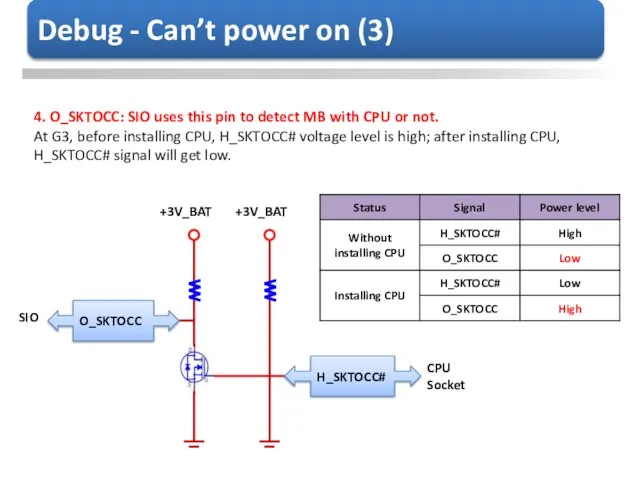

- 23. 4. O_SKTOCC: SIO uses this pin to detect MB with CPU or not. At G3, before

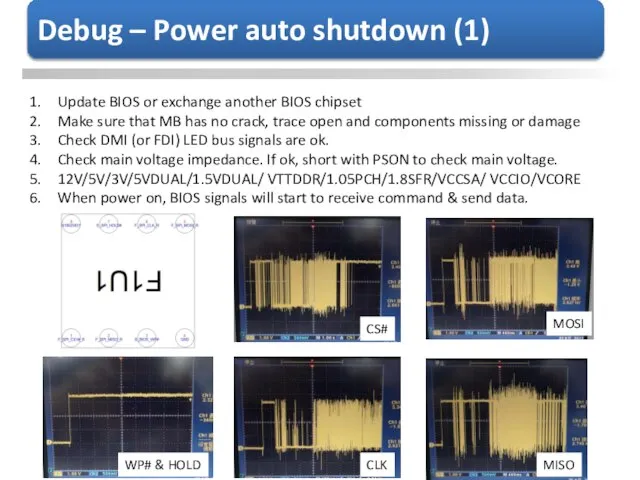

- 24. Update BIOS or exchange another BIOS chipset Make sure that MB has no crack, trace open

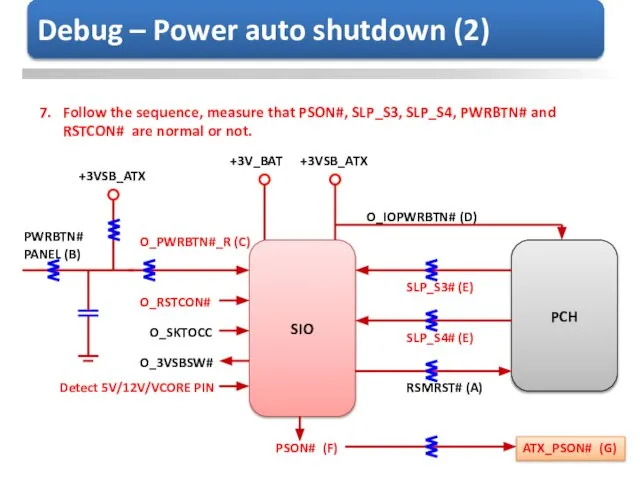

- 25. +3VSB_ATX +3VSB_ATX PWRBTN# PANEL (B) SIO PCH O_PWRBTN#_R (C) O_IOPWRBTN# (D) SLP_S3# (E) SLP_S4# (E) RSMRST#

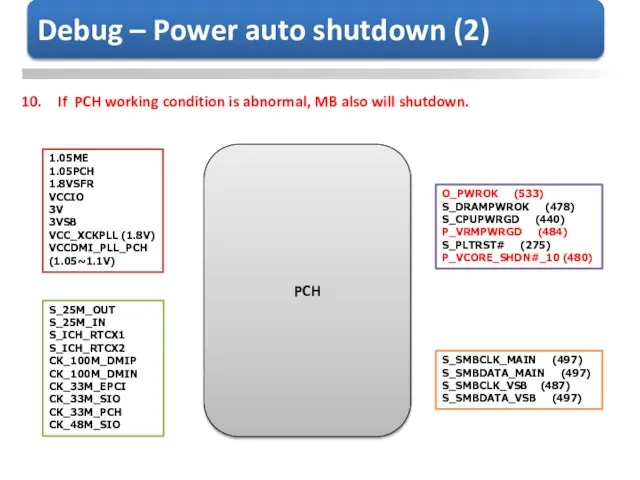

- 26. If PCH working condition is abnormal, MB also will shutdown. PCH 1.05ME 1.05PCH 1.8VSFR VCCIO 3V

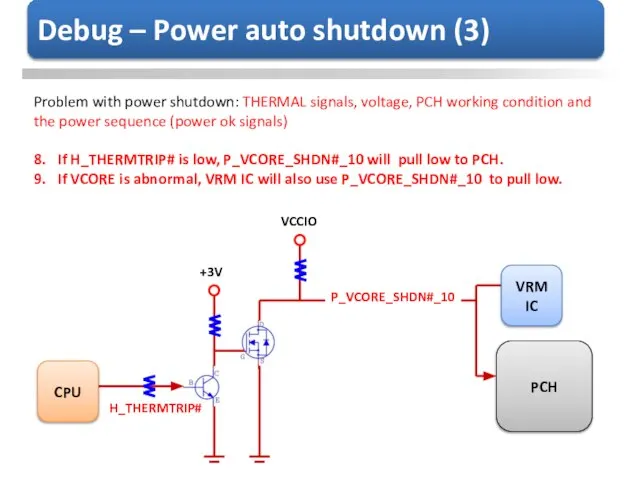

- 27. Problem with power shutdown: THERMAL signals, voltage, PCH working condition and the power sequence (power ok

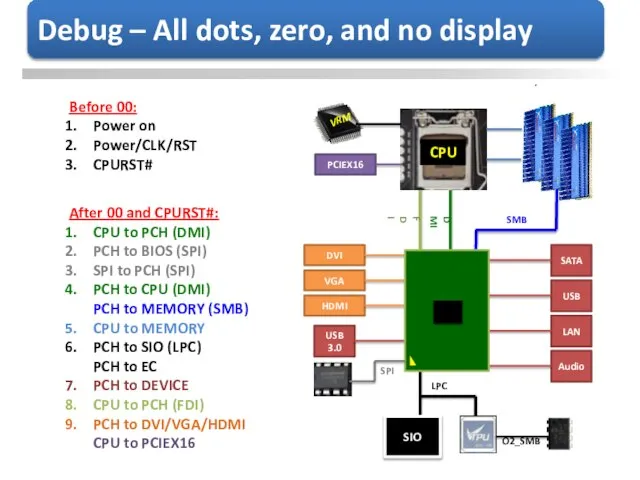

- 28. After 00 and CPURST#: CPU to PCH (DMI) PCH to BIOS (SPI) SPI to PCH (SPI)

- 29. Measure BUS: DMI: H_DMI_RXN/P[0:3] H_DMI_TXN/P[0:3] S_DMICOMP S_DMIRBIAS VCCDMI_PLL_PCH SMB: S_SMBCLK_MAIN S_SMBDATA_MAIN S_SMBCLK_PCI S_SMBDATA_PCI Memory to CPU

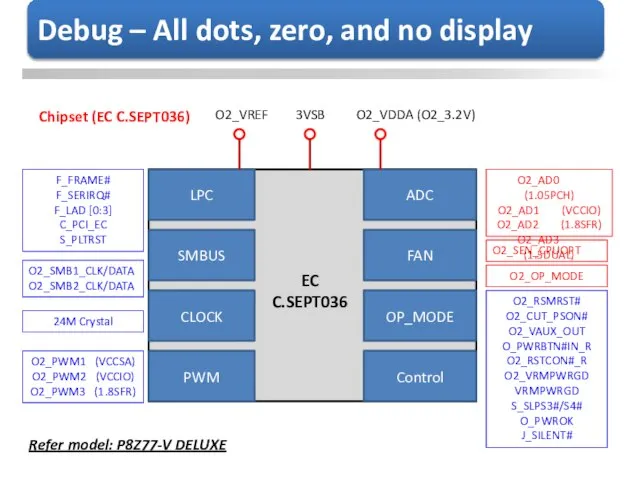

- 30. LPC SMBUS CLOCK PWM ADC FAN OP_MODE Control O2_VREF 3VSB O2_VDDA (O2_3.2V) EC C.SEPT036 24M Crystal

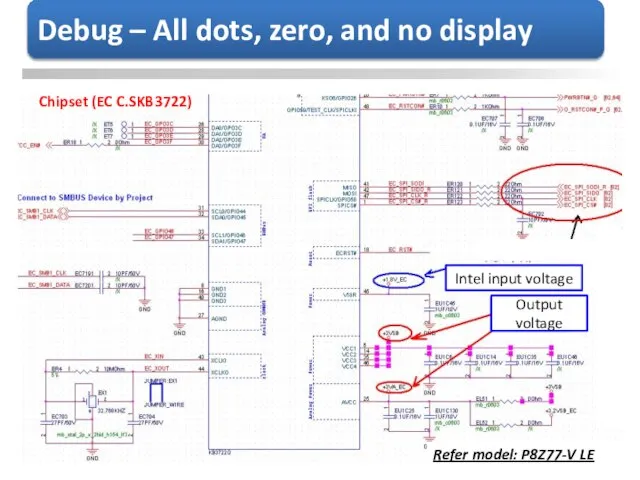

- 31. Refer model: P8Z77-V LE Intel input voltage Output voltage Chipset (EC C.SKB3722)

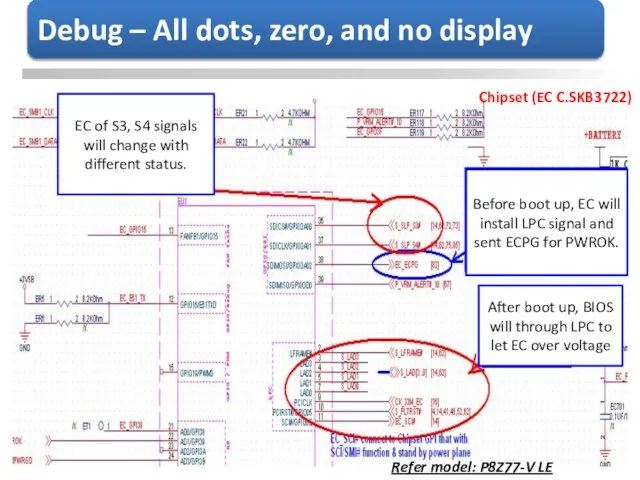

- 32. Refer model: P8Z77-V LE EC of S3, S4 signals will change with different status. Before boot

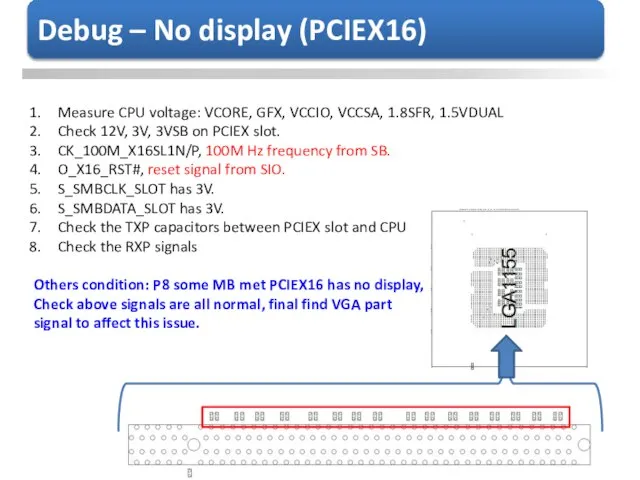

- 33. Measure CPU voltage: VCORE, GFX, VCCIO, VCCSA, 1.8SFR, 1.5VDUAL Check 12V, 3V, 3VSB on PCIEX slot.

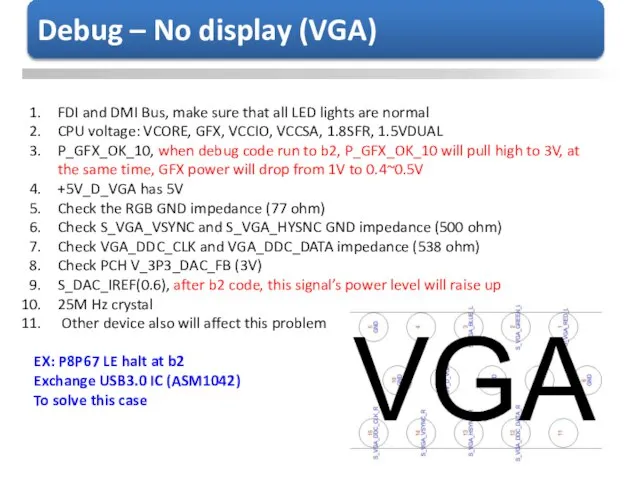

- 34. FDI and DMI Bus, make sure that all LED lights are normal CPU voltage: VCORE, GFX,

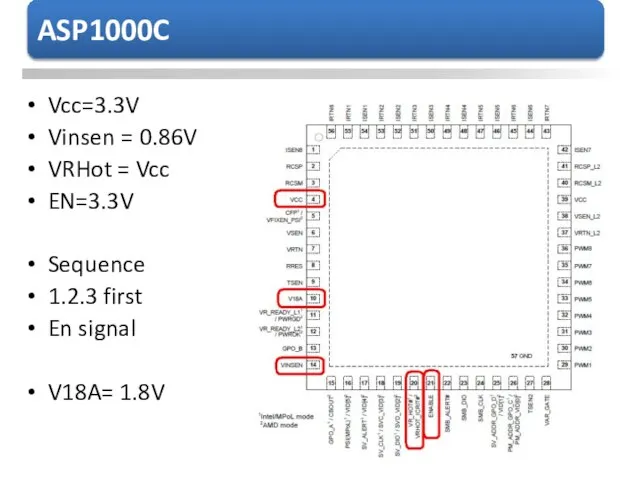

- 35. Vcc=3.3V Vinsen = 0.86V VRHot = Vcc EN=3.3V Sequence 1.2.3 first En signal V18A= 1.8V

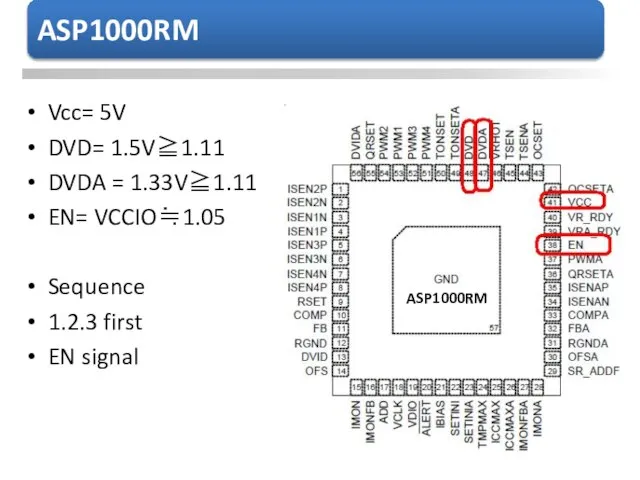

- 36. Vcc= 5V DVD= 1.5V≧1.11 DVDA = 1.33V≧1.11 EN= VCCIO≒1.05 Sequence 1.2.3 first EN signal ASP1000RM

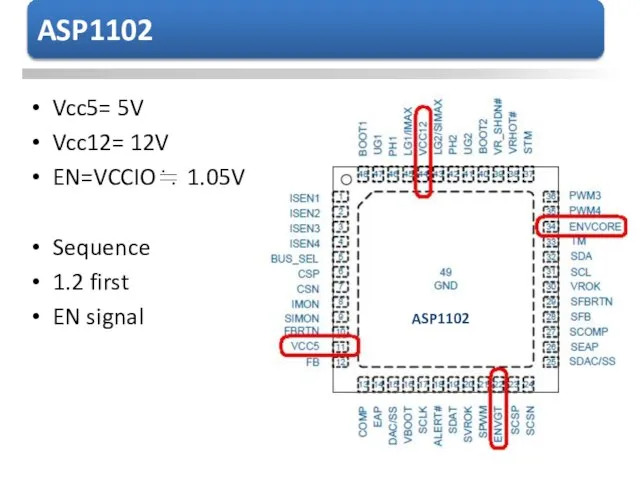

- 37. Vcc5= 5V Vcc12= 12V EN=VCCIO≒ 1.05V Sequence 1.2 first EN signal ASP1102

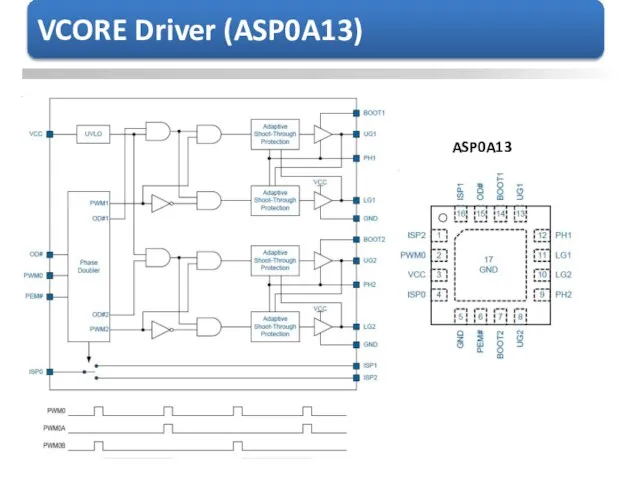

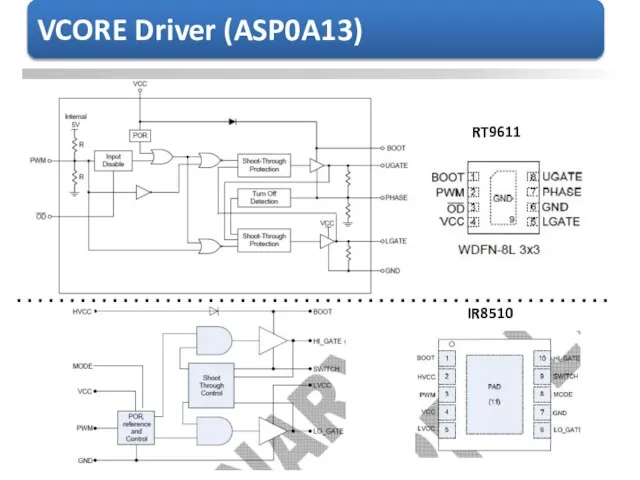

- 38. ASP0A13

- 39. IR8510

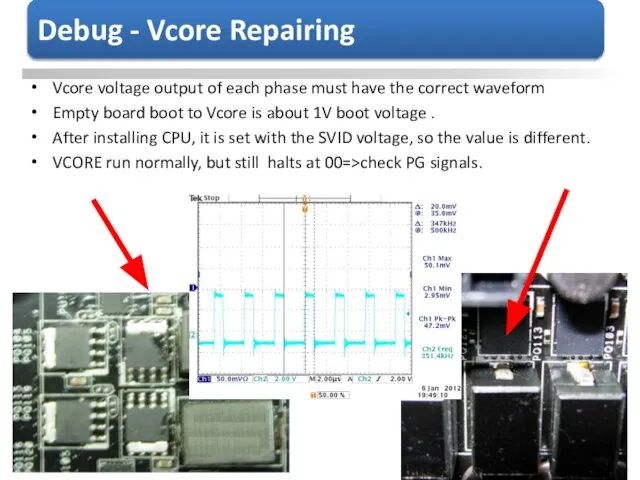

- 40. Vcore voltage output of each phase must have the correct waveform Empty board boot to Vcore

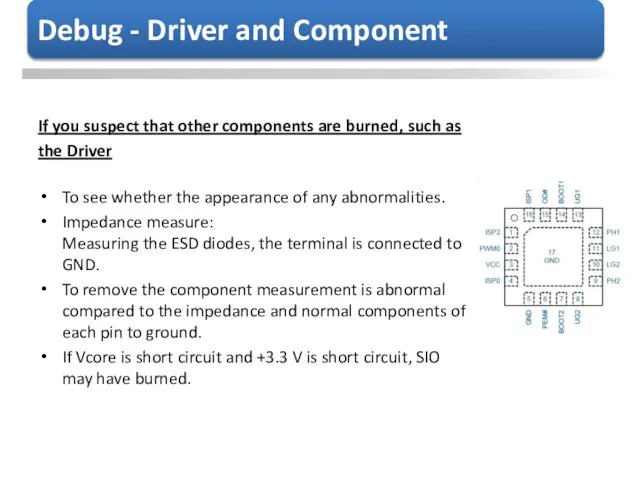

- 41. If you suspect that other components are burned, such as the Driver To see whether the

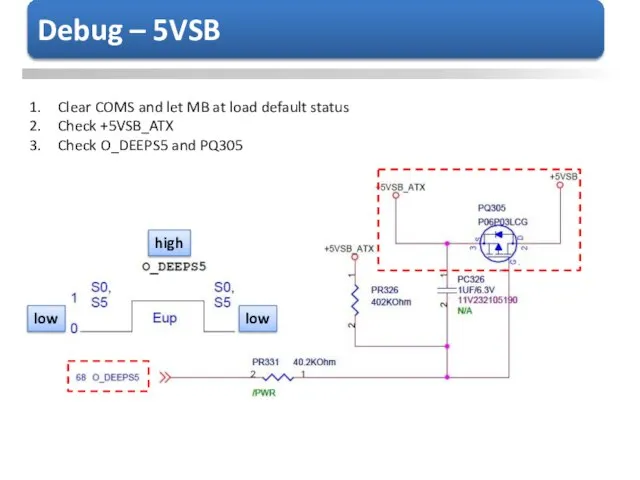

- 42. high low Clear COMS and let MB at load default status Check +5VSB_ATX Check O_DEEPS5 and

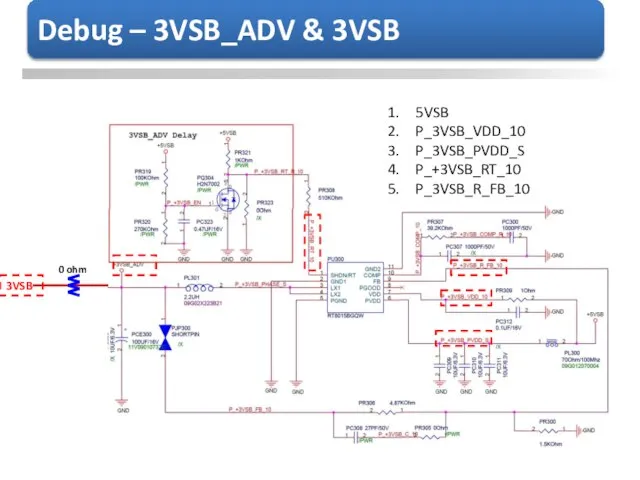

- 43. 5VSB P_3VSB_VDD_10 P_3VSB_PVDD_S P_+3VSB_RT_10 P_3VSB_R_FB_10 3VSB 0 ohm

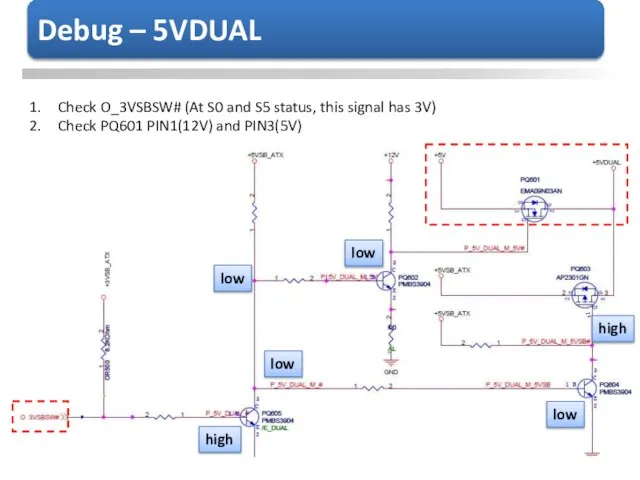

- 44. high low low low high low Check O_3VSBSW# (At S0 and S5 status, this signal has

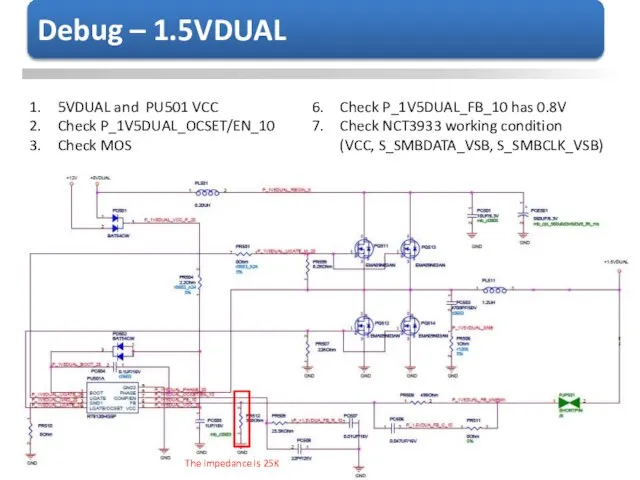

- 45. 5VDUAL and PU501 VCC Check P_1V5DUAL_OCSET/EN_10 Check MOS Check P_1V5DUAL_FB_10 has 0.8V Check NCT3933 working condition

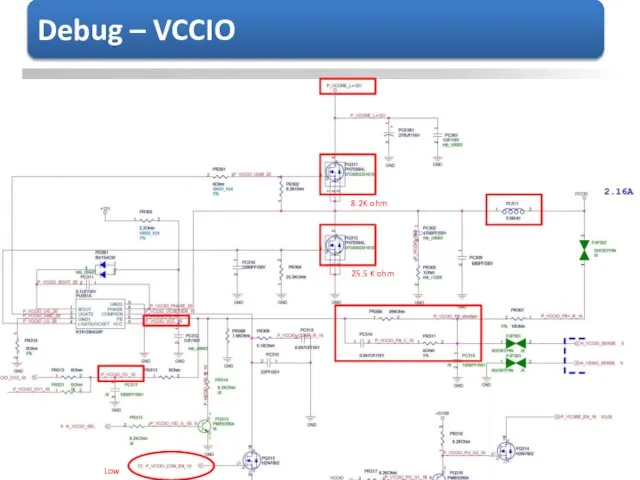

- 46. 8.2K ohm 25.5 K ohm Low

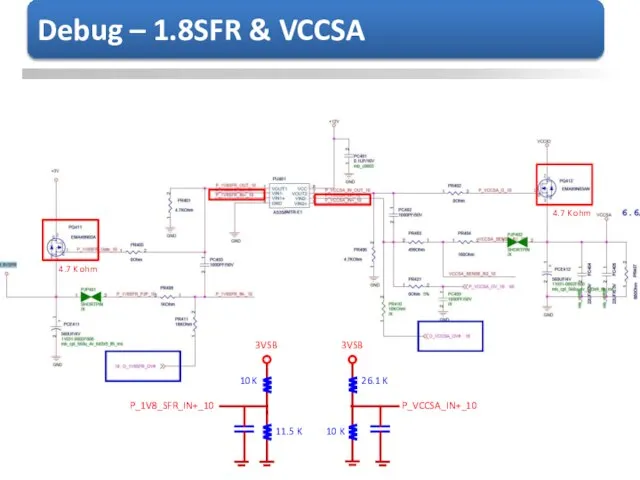

- 47. 3VSB 3VSB 10K 11.5 K 10 K 26.1 K P_1V8_SFR_IN+_10 P_VCCSA_IN+_10 4.7 K ohm 4.7 K

- 49. Скачать презентацию

![Measure BUS: DMI: H_DMI_RXN/P[0:3] H_DMI_TXN/P[0:3] S_DMICOMP S_DMIRBIAS VCCDMI_PLL_PCH SMB: S_SMBCLK_MAIN S_SMBDATA_MAIN](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/559719/slide-28.jpg)

1С:Медицина. Стоматологическая клиника

1С:Медицина. Стоматологическая клиника Задачи SCADA-систем и их решение в программных комплексах

Задачи SCADA-систем и их решение в программных комплексах Создание Web-страниц на языке HTML

Создание Web-страниц на языке HTML CRM-приложения, обеспечивающие работу электронного правительства

CRM-приложения, обеспечивающие работу электронного правительства Create a own Database

Create a own Database Цифровая культура

Цифровая культура Файловая структура компьютера

Файловая структура компьютера Event Sourcing

Event Sourcing Актуальность информационной безопасности детей

Актуальность информационной безопасности детей Основы WLAN

Основы WLAN Архитектура ORACLE. Процессы и потоки Windows (Лекция 6)

Архитектура ORACLE. Процессы и потоки Windows (Лекция 6) Язык программирования SAS Base

Язык программирования SAS Base Моделирование, как метод познания. Общие свойства моделей

Моделирование, как метод познания. Общие свойства моделей Консоль или ПК?

Консоль или ПК? О кассах, маркировке ЭДО и электронных подписях

О кассах, маркировке ЭДО и электронных подписях Технологии программирования. Курс на базе Microsoft Solutions Framework Семинар 1. Повтор принципов объектно-ориентированного подхода

Технологии программирования. Курс на базе Microsoft Solutions Framework Семинар 1. Повтор принципов объектно-ориентированного подхода  Требования к оформлению. Межвузовские, региональные, отборочные чемпионаты

Требования к оформлению. Межвузовские, региональные, отборочные чемпионаты Grafka i komunikacja człowieka z komputerem

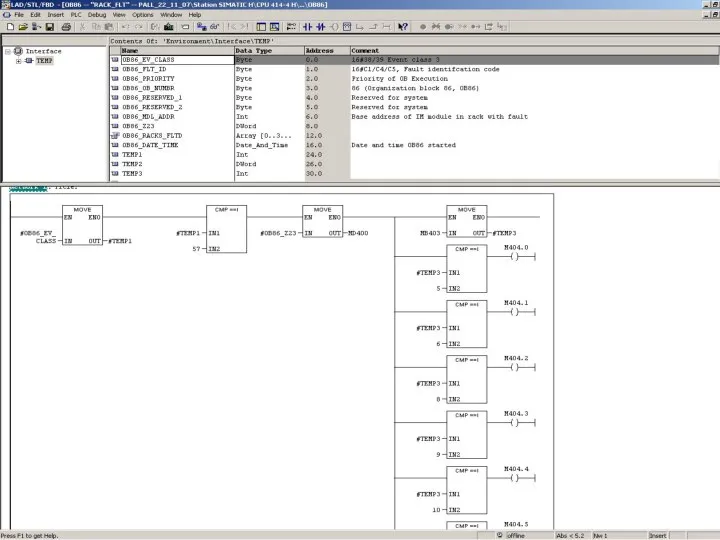

Grafka i komunikacja człowieka z komputerem Программирование на языке fbd codesys

Программирование на языке fbd codesys Массивы. Лекция 5

Массивы. Лекция 5 Работа с информацией

Работа с информацией Учебный курс Введение в цифровую электронику Лекция 4 Основные понятия микропроцессорной техники кандидат технических н

Учебный курс Введение в цифровую электронику Лекция 4 Основные понятия микропроцессорной техники кандидат технических н Урок информатики 5 класс

Урок информатики 5 класс Хранение информации Память человека и память человечества Оперативная и долговременная память Файлы и папки Это интересно

Хранение информации Память человека и память человечества Оперативная и долговременная память Файлы и папки Это интересно Компьютерные вирусы и антивирусные программы

Компьютерные вирусы и антивирусные программы Компьютерные средства управления технологическими процессами

Компьютерные средства управления технологическими процессами Зачем вам блог

Зачем вам блог Итак, представляю вам последнюю разработку корпорации Microsoft: Windows Vista

Итак, представляю вам последнюю разработку корпорации Microsoft: Windows Vista