Содержание

- 2. Физическая и функциональная структура микропроцессора Физическая структура микропроцессора достаточно сложна. Ядро процессора содержит главный управляющий модуль

- 3. В состав микропроцессора Pentium обычно входят следующие физические компоненты: Core – ядро МП; Execution Unit –

- 4. Функционально МП можно разделить на две части: операционную, содержащую устройство управления (УУ), арифметико-логическое устройство (АЛУ) и

- 5. Обе части МП работают параллельно, причем интерфейсная часть опережает операционную, так что выборка очередной команды из

- 6. Устройство управления Устройство управления (УУ) является функционально наиболее сложным устройством ПК – оно вырабатывает управляющие сигналы,

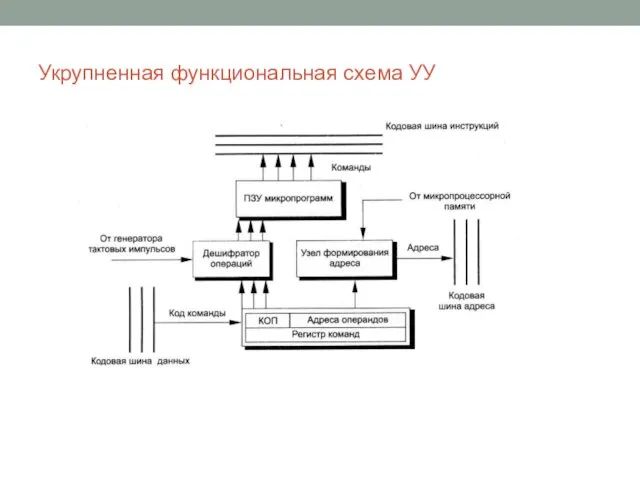

- 7. Укрупненная функциональная схема УУ

- 8. На рисунке представлены: регистр команд – запоминающий регистр, в котором хранится код команды: код выполняемой операции

- 9. узел формирования адреса (находится в интерфейсной части МП) – устройство, вычисляющее полный адрес ячейки памяти (регистра)

- 10. В общем случае УУ формирует управляющие сигналы для выполнения следующих основных процедур: выборки из регистра-счетчика адреса

- 11. считывания из регистра команд и регистров МПП отдельных составляющих адресов операндов (чисел), участвующих в вычислениях, и

- 12. Арифметико-логическое устройство Арифметико-логическое устройство (АЛУ) предназначено для выполнения арифметических и логических операций преобразования информации. Функционально простейшее

- 13. Сумматор – вычислительная схема, выполняющая процедуру сложения поступающих на ее вход двоичных кодов; сумматор имеет разрядность

- 14. Схемы управления принимают по кодовым шинам инструкций управляющие сигналы от устройства управления и преобразуют их в

- 15. Микропроцессорная память Микропроцессорная память (МПП) базового МП 8086 включает в себя 14 двухбайтовых запоминающих регистров. У

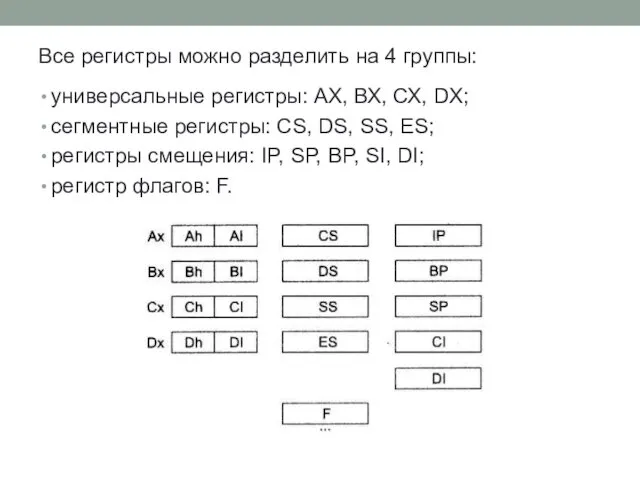

- 16. Все регистры можно разделить на 4 группы: универсальные регистры: АХ, ВХ, СХ, DX; сегментные регистры: CS,

- 17. Если регистры 4-байтовые или 8-байтовые, их имена несколько изменяются, например, 4-байтовые универсальные регистры АХ, ВХ, СХ,

- 18. Универсальные регистры Регистры АХ, ВХ, СХ и DX являются универсальными (их часто называют регистрами общего назначения

- 19. В частности: регистр АХ – регистр-аккумулятор, через него осуществляется ввод-вывод данных в МП, а при выполнении

- 20. Сегментные регистры Регистры сегментной адресации CS, DS, SS, ES используются для хранения начальных адресов полей памяти

- 21. Регистры смещений Регистры смещений (внутрисегментной адресации) IP, SP, BP, SI, DI предназначены для хранения относительных адресов

- 22. Регистр флагов Регистр флагов F содержит условные одноразрядные признаки-маски или флаги, управляющие прохождением программы в ПК;

- 23. Статусные флаги: CF (Carry Flag) – флаг переноса. Содержит значение «переносов» (0 или 1) из старшего

- 24. ZF (Zero Flag) – флаг нуля. Устанавливается в 1, если результат операции равен нулю; если результат

- 25. Управляющие флаги: TF (Trap Flag) – флаг системного прерывания (трассировки). Единичное состояние этого флага переводит процессор

- 26. Интерфейсная часть МП Интерфейсная часть МП предназначена для связи и согласования МП с системной шиной ПК,

- 27. Некоторые из названных устройств, такие как узел формирования адреса и регистр команды, непосредственно выполняемой МП, функционально

- 28. Схема управления шиной и портами выполняет следующие функции: формирование адреса порта и управляющей информации для него

- 29. Схема управления шиной и портами использует для связи с портами кодовые шины инструкций, адреса и данные

- 31. Скачать презентацию

Отчет о проделанной работе. Заказ комплектующих компьютера. Рейтинг Интернет - Сми, электронные библиотеки

Отчет о проделанной работе. Заказ комплектующих компьютера. Рейтинг Интернет - Сми, электронные библиотеки Отображение данных из нескольких таблиц

Отображение данных из нескольких таблиц Лекция 6. Графические редакторы и программы по обработке изображений

Лекция 6. Графические редакторы и программы по обработке изображений Онлайн курсы и индивидуальные занятия по спортивному ориентированию

Онлайн курсы и индивидуальные занятия по спортивному ориентированию Слайд-шоу за 5 минут

Слайд-шоу за 5 минут Администрирование информационных систем Начало работы с MS SQL Server 2000

Администрирование информационных систем Начало работы с MS SQL Server 2000 Рациональная тактика развития. Тактика противодействия

Рациональная тактика развития. Тактика противодействия Библиотека. ПК

Библиотека. ПК Анонимность e-mail Алексей Августинович, webhome.by

Анонимность e-mail Алексей Августинович, webhome.by Контроль каналов утечки критически важных объектов информатизации (КВОИ)

Контроль каналов утечки критически важных объектов информатизации (КВОИ) Анализ бизнес информации – основные принципы

Анализ бизнес информации – основные принципы Сучасні комп’ютерні технології в економічній науці та практиці

Сучасні комп’ютерні технології в економічній науці та практиці World-building. Word formation

World-building. Word formation Компоненты ввода и вывода

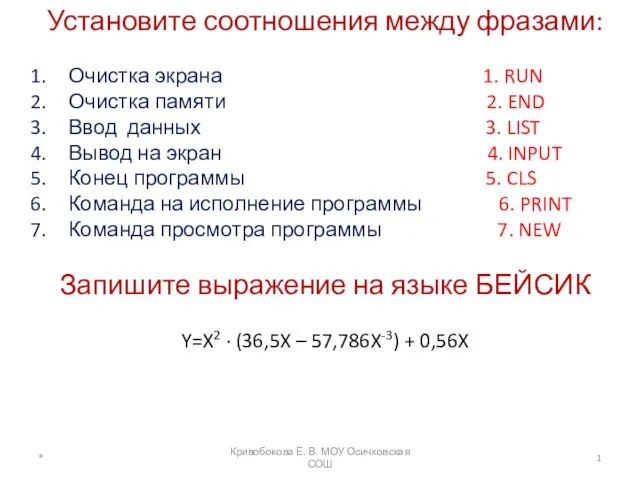

Компоненты ввода и вывода Презентация "Составить программу для нахождения значения выражения" - скачать презентации по Информатике

Презентация "Составить программу для нахождения значения выражения" - скачать презентации по Информатике Copywrite digital printers

Copywrite digital printers Решение логических задач табличным способом

Решение логических задач табличным способом Программное обеспечение компьютера

Программное обеспечение компьютера Изучение принципа действия и организации компьютерных сетей на основе кабеля витая пара

Изучение принципа действия и организации компьютерных сетей на основе кабеля витая пара Инструкция. Олимпиада

Инструкция. Олимпиада Устройство компьютера

Устройство компьютера Объекты компьютерной графики

Объекты компьютерной графики Презентация "Получение новой информации" - скачать презентации по Информатике

Презентация "Получение новой информации" - скачать презентации по Информатике Российская игровая индустрия в 90-х и начале нулевых

Российская игровая индустрия в 90-х и начале нулевых Базові моделі даних

Базові моделі даних Базы данных. Системы управления базами данных

Базы данных. Системы управления базами данных Введение в НТМL. Язык разметки гипертекста

Введение в НТМL. Язык разметки гипертекста Как не заскучать в онлайне?

Как не заскучать в онлайне?