7. НЕМНОГО ПРО Cyclone

Среди всех семейств Altera, имеющих встроенные трансиверы,

СБИС ПЛ Cyclone IV отличаются самой низкой стоимостью логического элемента и самым низким энергопотреблением. Кроме трансиверов микросхемы содержат аппаратные умножители, блоки встроенного ОЗУ и аппаратные IP-блоки контроллеров PCI Express.

Семейство Cyclone IV состоит из следующих подсемейств:

Cyclone IV E – не содержит встроенных трансиверов и аппаратных контроллеров;

Cyclone IV GX – содержит встроенные трансиверы с максимальной скоростью передачи данных 3.125 Гбит/с или 2.5 Гбит/с, и аппаратный контроллер PCI Express (его мы и будем использовать).

СБИС ПЛ семейства Cyclone IV

3 лабораторная. Часть 2: Кодим

3 лабораторная. Часть 2: Кодим Презентация "Современные способы и средства защиты информации" - скачать презентации по Информатике

Презентация "Современные способы и средства защиты информации" - скачать презентации по Информатике Нелинейные алгоритмы. Язык программирования Паскаль. 8 класс

Нелинейные алгоритмы. Язык программирования Паскаль. 8 класс Разработка автоматизированной информационной системы для автосервиса

Разработка автоматизированной информационной системы для автосервиса Перспективные модели баз данных

Перспективные модели баз данных Компьютерное моделирование

Компьютерное моделирование Электронндық үкімет және электрондық қызметтер

Электронндық үкімет және электрондық қызметтер Операторы языка Паскаль

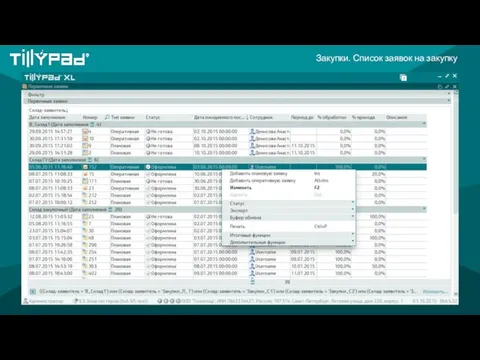

Операторы языка Паскаль Tillipad. Инструкция по использованию

Tillipad. Инструкция по использованию Ингибитер или проблемы цифровизации

Ингибитер или проблемы цифровизации Архив журнала «Вопросы истории»

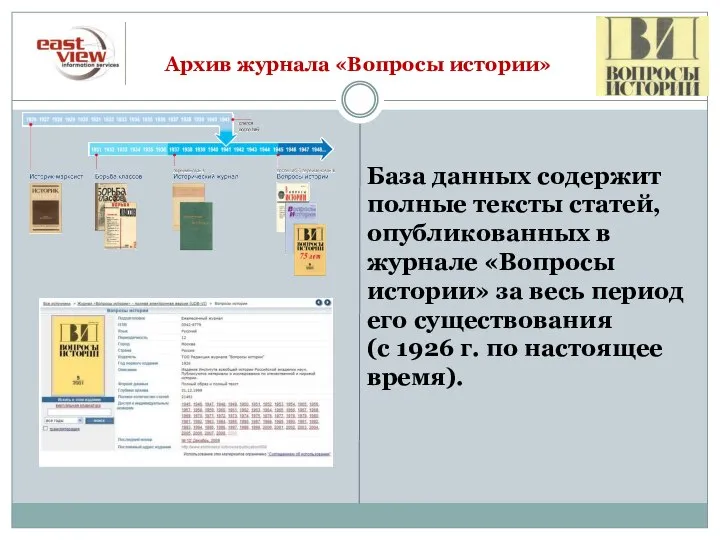

Архив журнала «Вопросы истории» Введение в объектно-ориентированное программирование

Введение в объектно-ориентированное программирование  Деструктивное поведение

Деструктивное поведение Adobe Photoshop Автор: Белкина Елизавета

Adobe Photoshop Автор: Белкина Елизавета Методика обучения библиотекаря созданию электронных таблиц в программе MS Excel В рамках проекта «Информатизация системы

Методика обучения библиотекаря созданию электронных таблиц в программе MS Excel В рамках проекта «Информатизация системы  Введение в специальность BIG DATA

Введение в специальность BIG DATA Разработка интернет-магазина для сайта электроники

Разработка интернет-магазина для сайта электроники Создание БД в LibreOffice Base

Создание БД в LibreOffice Base Информатика как наука

Информатика как наука Библиотека matplotlib Python разработка

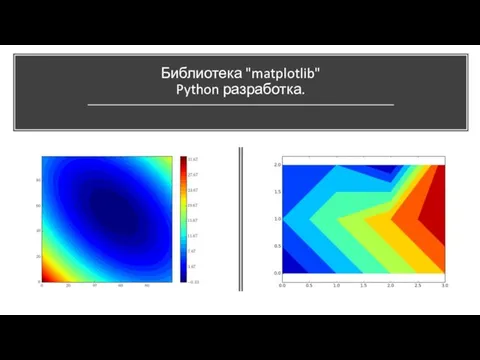

Библиотека matplotlib Python разработка Основы логики

Основы логики Информационные модели на графах. Введение

Информационные модели на графах. Введение XPath. Выборка данных из загруженных XML-документов

XPath. Выборка данных из загруженных XML-документов Первый взгляд на платформу Net. (Лекция 1)

Первый взгляд на платформу Net. (Лекция 1) Виды информации

Виды информации Наследование ( C#, Лекция 2)

Наследование ( C#, Лекция 2) Вычислительные управляющие системы самолёта ТУ-204-100. Обучающая программа

Вычислительные управляющие системы самолёта ТУ-204-100. Обучающая программа Учебный курс Язык UML в анализе и проектировании программных систем и бизнес-процессов Лекция 1 Базовые принципы и понятия техн

Учебный курс Язык UML в анализе и проектировании программных систем и бизнес-процессов Лекция 1 Базовые принципы и понятия техн