Логические основы компьютера Базовые логические элементы Автор: Сергеев Евгений Викторович МОУ СОШ №4 г. Миньяра Челябинской

Содержание

- 2. Базовые логические элементы Компьютер выполняет арифметические и логические операции при помощи т.н. базовых логических элементов, которые

- 3. Составные элементы Любая логическая операция может быть представлена через конъюнкцию, дизъюнкцию и инверсию Любой сколь угодно

- 4. Сигналы-аргументы и сигналы-функции Вентили оперируют с электрическими импульсами: Импульс имеется – логический смысл сигнала «1» Импульса

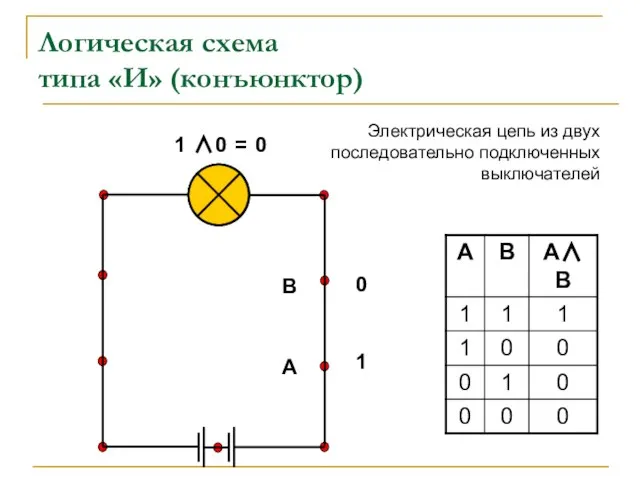

- 5. Логическая схема типа «И» (конъюнктор) 1 ∧ 0 = 0 1 0 A В Электрическая цепь

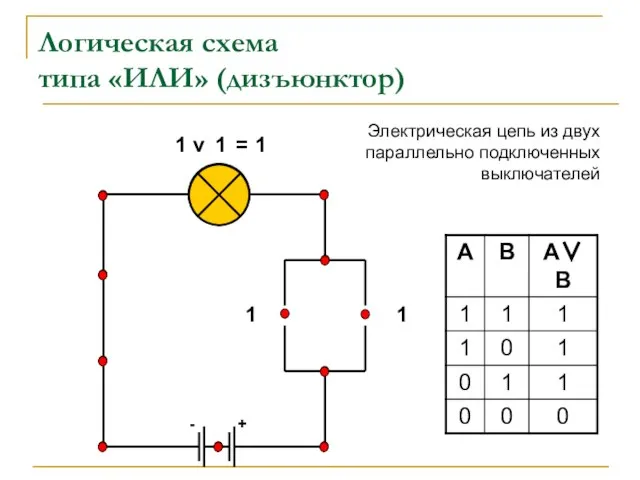

- 6. + - Логическая схема типа «ИЛИ» (дизъюнктор) 1 1 1 v 1 = 1 Электрическая цепь

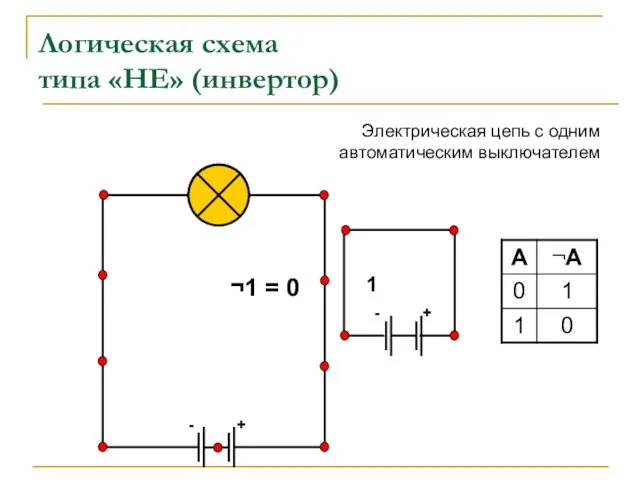

- 7. + - Логическая схема типа «НЕ» (инвертор) + - ¬1 = 0 1 Электрическая цепь с

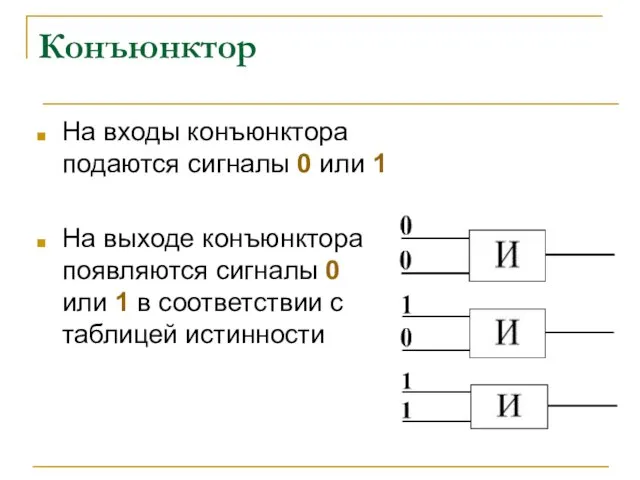

- 8. Конъюнктор На входы конъюнктора подаются сигналы 0 или 1 На выходе конъюнктора появляются сигналы 0 или

- 9. Дизъюнктор На входы дизъюнктора подаются сигналы 0 или 1 На выходе дизъюнктора появляются сигналы 0 или

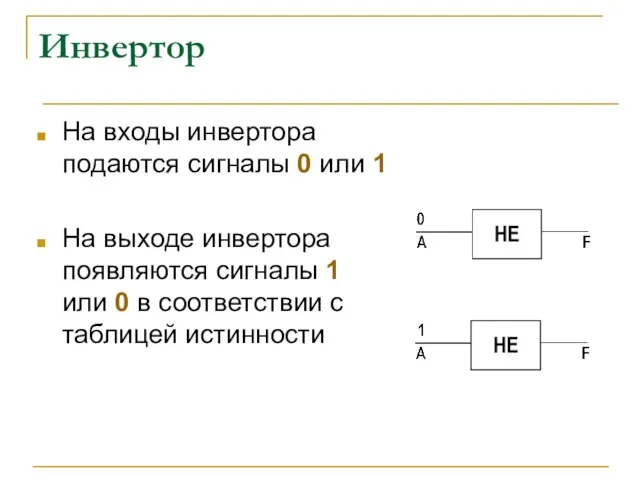

- 10. Инвеpтор На входы инвертора подаются сигналы 0 или 1 На выходе инвертора появляются сигналы 1 или

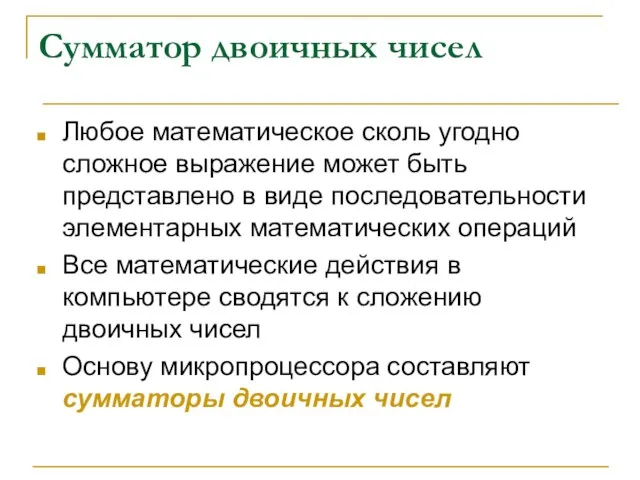

- 11. Сумматор двоичных чисел Любое математическое сколь угодно сложное выражение может быть представлено в виде последовательности элементарных

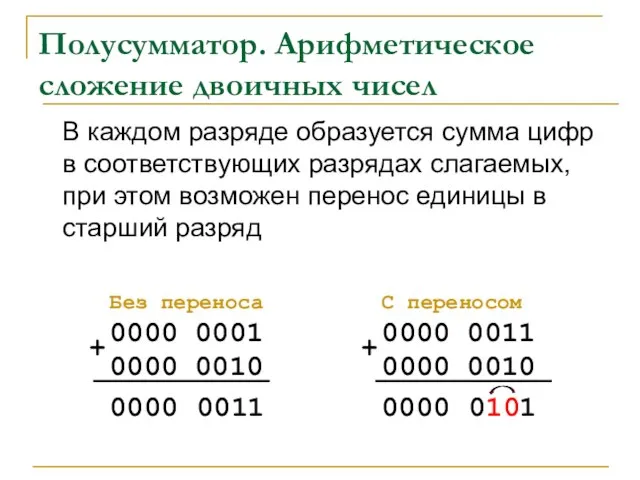

- 12. Полусумматор. Арифметическое сложение двоичных чисел В каждом разряде образуется сумма цифр в соответствующих разрядах слагаемых, при

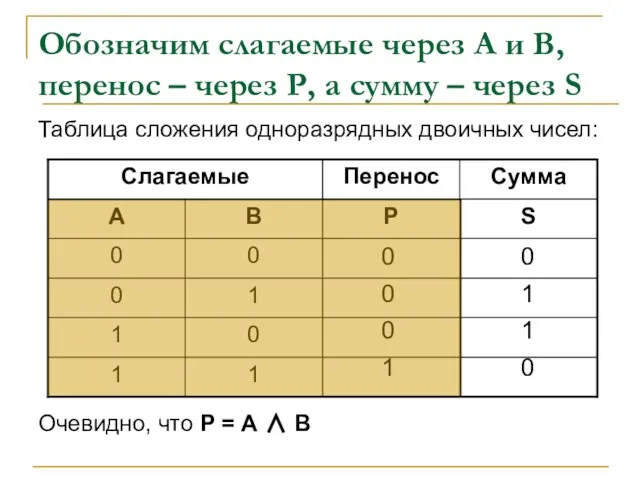

- 13. Обозначим слагаемые через А и В, перенос – через Р, а сумму – через S Таблица

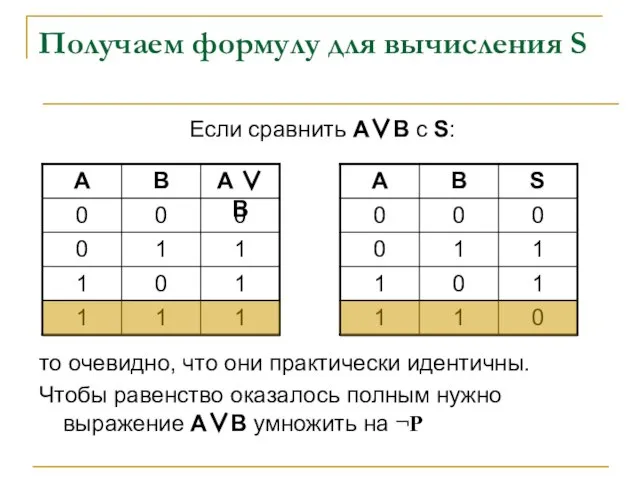

- 14. Получаем формулу для вычисления S Если сравнить А∨В c S: то очевидно, что они практически идентичны.

- 15. Получаем формулу для вычисления S S = (А ∨ В) ∧ ¬P ⇒ (А ∨ В)

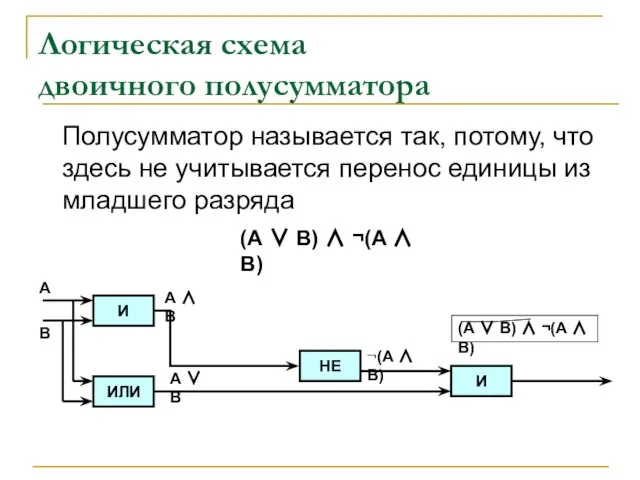

- 16. Логическая схема двоичного полусумматора Полусумматор называется так, потому, что здесь не учитывается перенос единицы из младшего

- 17. Полный одноразрядный сумматор Должен иметь три входа (А, В и Р0) и два выхода (S и

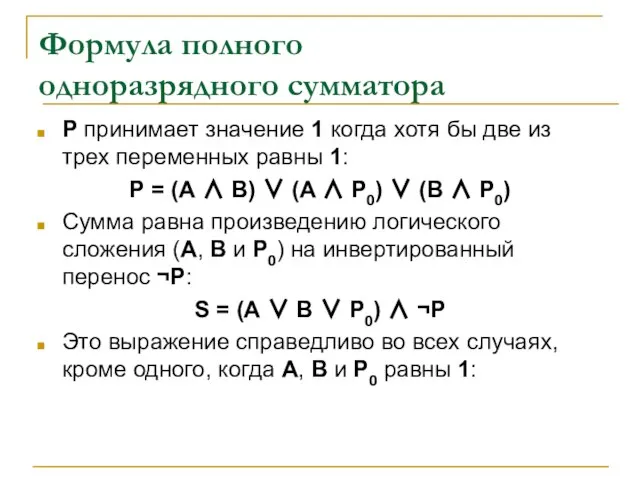

- 18. Формула полного одноразрядного сумматора Р принимает значение 1 когда хотя бы две из трех переменных равны

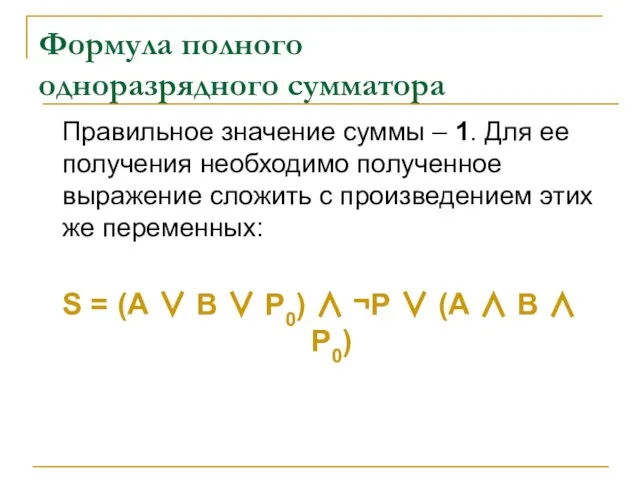

- 19. Формула полного одноразрядного сумматора Правильное значение суммы – 1. Для ее получения необходимо полученное выражение сложить

- 20. Многоразрядный сумматор Построен на основе полных одноразрядных сумматоров (по одному на каждый разряд), причем таким образом,

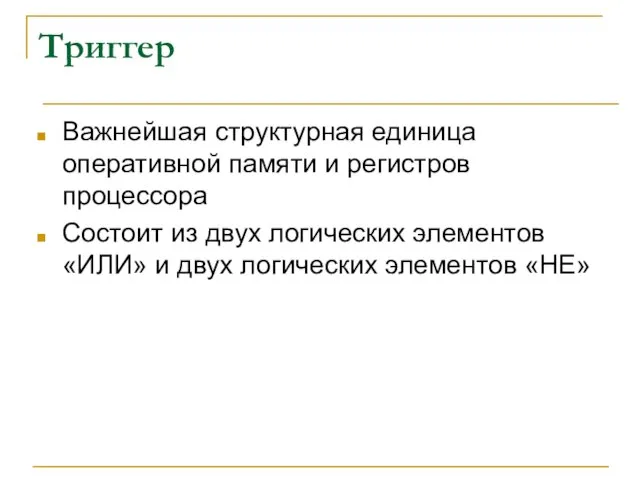

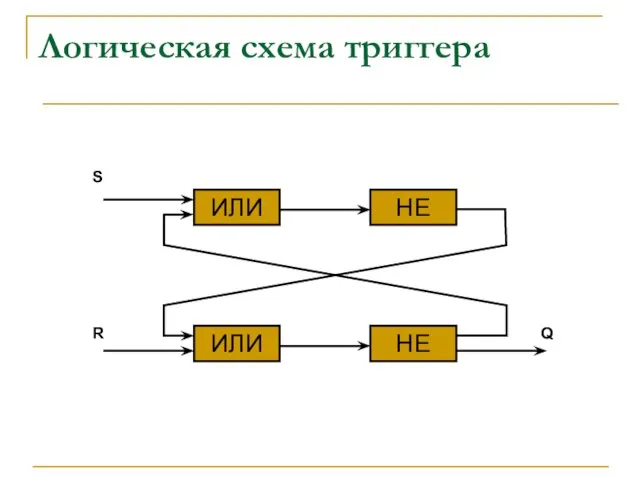

- 21. Триггер Важнейшая структурная единица оперативной памяти и регистров процессора Состоит из двух логических элементов «ИЛИ» и

- 22. Логическая схема триггера ИЛИ ИЛИ НЕ НЕ S R Q

- 24. Скачать презентацию

ТЕХНОЛОГИЯ РАБОТЫ С ТАБЛИЦАМИ В БАЗАХ ДАННЫХ

ТЕХНОЛОГИЯ РАБОТЫ С ТАБЛИЦАМИ В БАЗАХ ДАННЫХ Построение филогенетических деревьев

Построение филогенетических деревьев Разработка сайтов

Разработка сайтов Система Help Desk

Система Help Desk Динамические массивы

Динамические массивы Режимы и способы обработки данных

Режимы и способы обработки данных Ведение аккаунта Instagram и контент-план

Ведение аккаунта Instagram и контент-план Режиссура мультимедийной истории

Режиссура мультимедийной истории Хранение, выборка и редактирование данных

Хранение, выборка и редактирование данных Устройство компьютера. Ребусы

Устройство компьютера. Ребусы Пространство имен RegularExpressions (C#)

Пространство имен RegularExpressions (C#) Информационная безопасность. Виды возможных угроз

Информационная безопасность. Виды возможных угроз Коммерческое предложение. Продвижение сайта

Коммерческое предложение. Продвижение сайта Информация и информационные процессы (10 класс)

Информация и информационные процессы (10 класс) Основы языка SQL

Основы языка SQL Система автоматизации проектирования Quartus II. Компиляция. Назначение контактов. Моделирование

Система автоматизации проектирования Quartus II. Компиляция. Назначение контактов. Моделирование КОМПЬЮТЕРНАЯ ГРАФИКА ОБРАБОТКА ГРАФИЧЕСКОЙ ИНФОРМАЦИИ

КОМПЬЮТЕРНАЯ ГРАФИКА ОБРАБОТКА ГРАФИЧЕСКОЙ ИНФОРМАЦИИ «Антивирусные программы» Учитель информатики Мурашова Татьяна Юрьевна

«Антивирусные программы» Учитель информатики Мурашова Татьяна Юрьевна Презентация на тему Носители информации

Презентация на тему Носители информации  Representation of data in computer systems

Representation of data in computer systems Android Notifications. Toast-уведомления. Оповещения

Android Notifications. Toast-уведомления. Оповещения Defect tracking

Defect tracking Поколения ЭВМ. Компьютеры 4, 5 и 6 поколения

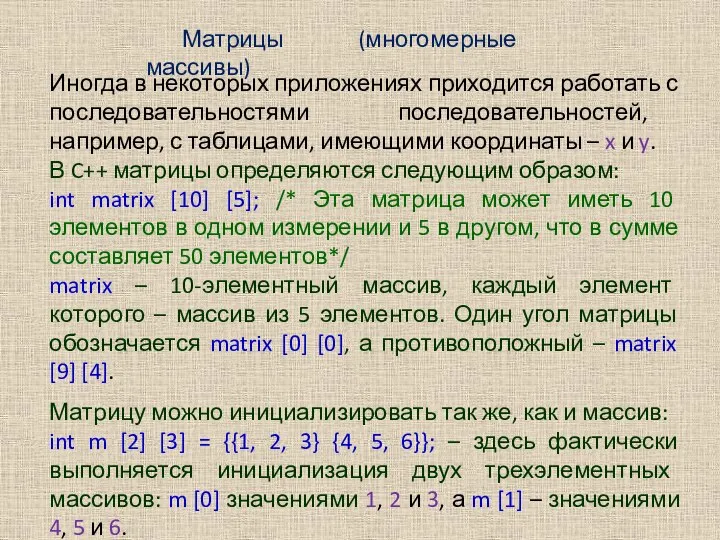

Поколения ЭВМ. Компьютеры 4, 5 и 6 поколения Матрицы (многомерные массивы)

Матрицы (многомерные массивы) Презентация "Алгоритм – как модель деятельности" - скачать презентации по Информатике

Презентация "Алгоритм – как модель деятельности" - скачать презентации по Информатике Количество информации. Единицы измерения количества информации

Количество информации. Единицы измерения количества информации Растровая и векторная графика Форматы графических файлов

Растровая и векторная графика Форматы графических файлов Programming_C._Practice_1

Programming_C._Practice_1