Содержание

- 2. ПЗУМ – ROM(M) - Mask ROM ППЗУ – PROM (Programmable ROM) РПЗУ-УФ – EPROM (Erasable Programmable

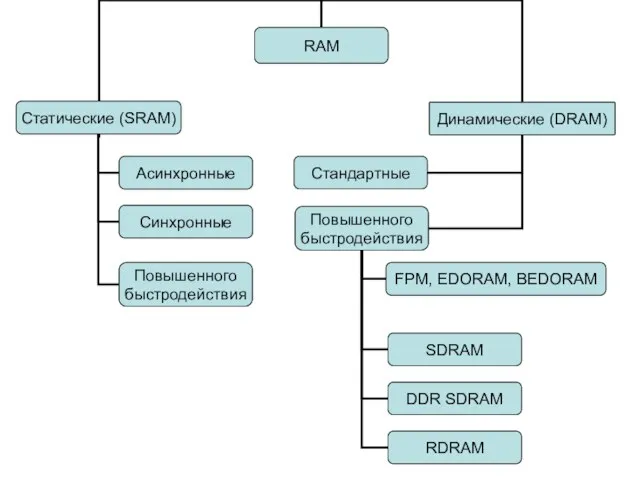

- 4. Структуры ЗУ

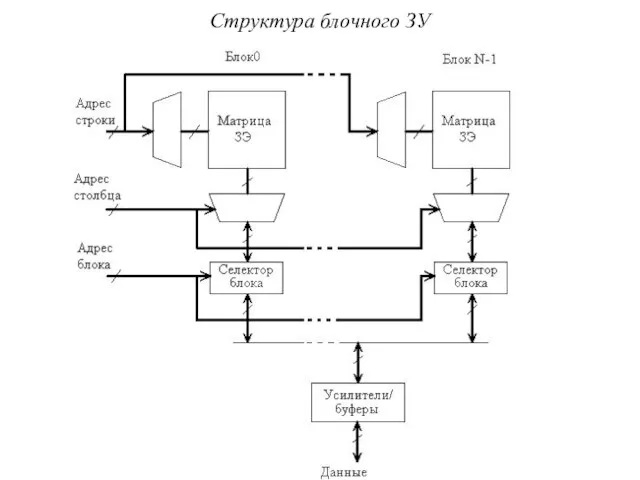

- 7. Структура блочного ЗУ

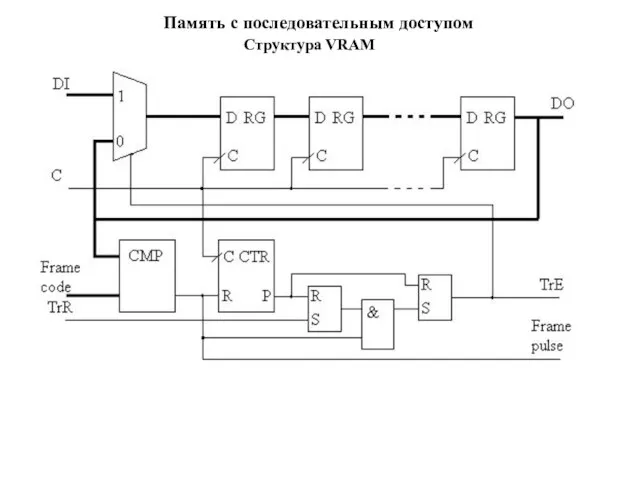

- 8. Память с последовательным доступом Структура VRAM

- 9. Структура FIFO

- 10. Накопитель ROM(M)

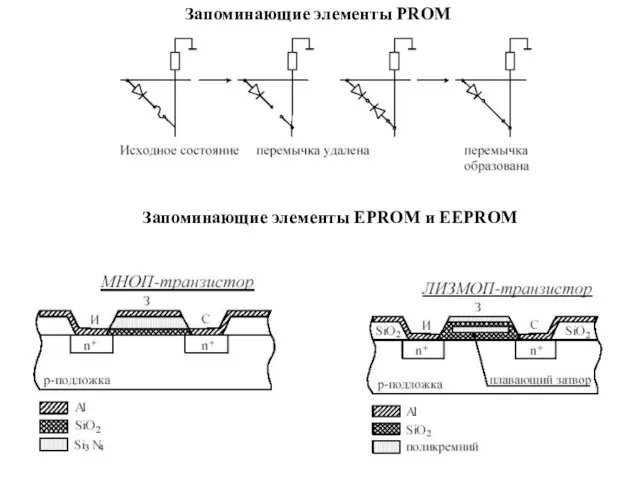

- 11. Запоминающие элементы PROM Запоминающие элементы EPROM и EEPROM

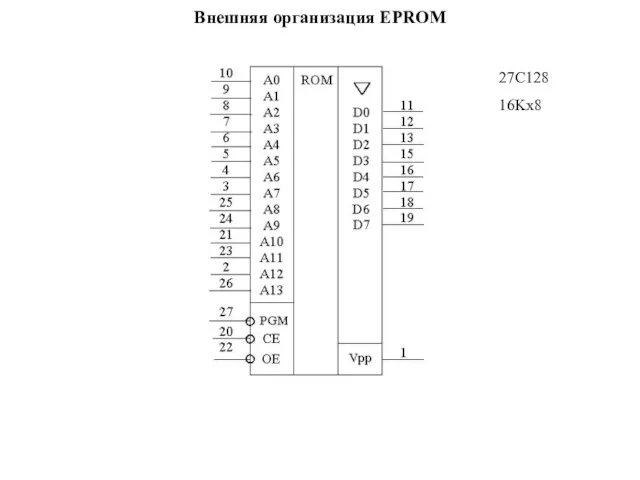

- 12. Внешняя организация EPROM 27C128 16Kx8

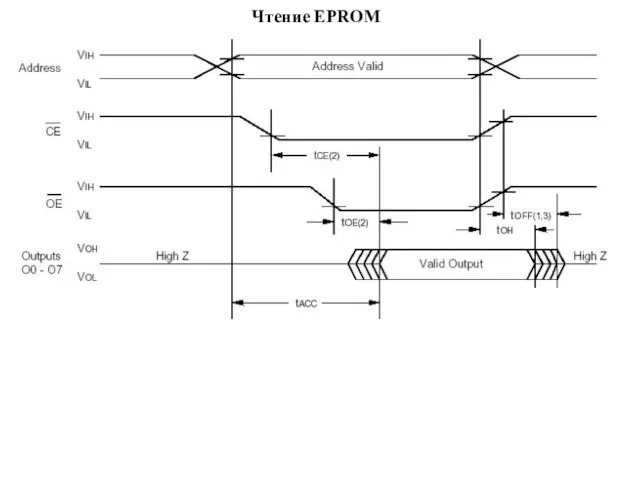

- 13. Чтение EPROM

- 14. Запись EPROM

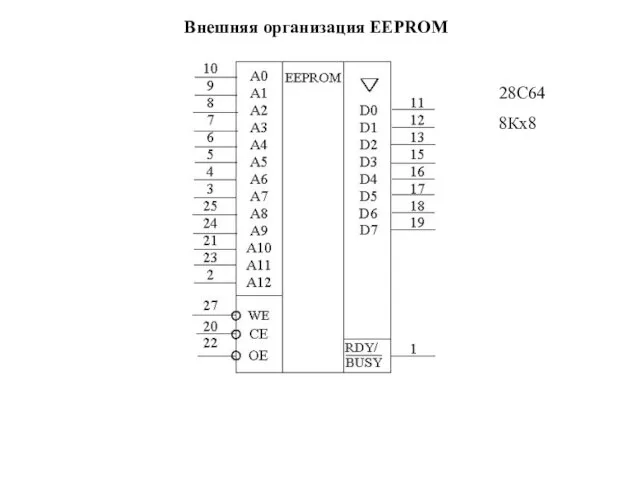

- 15. Внешняя организация EEPROM 28С64 8Кх8

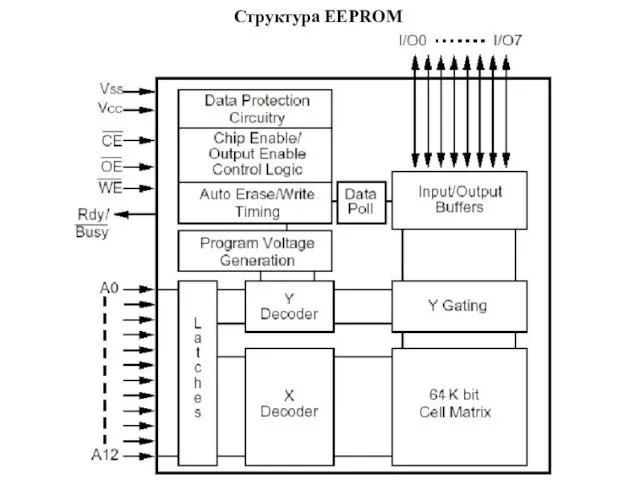

- 16. Структура EEPROM

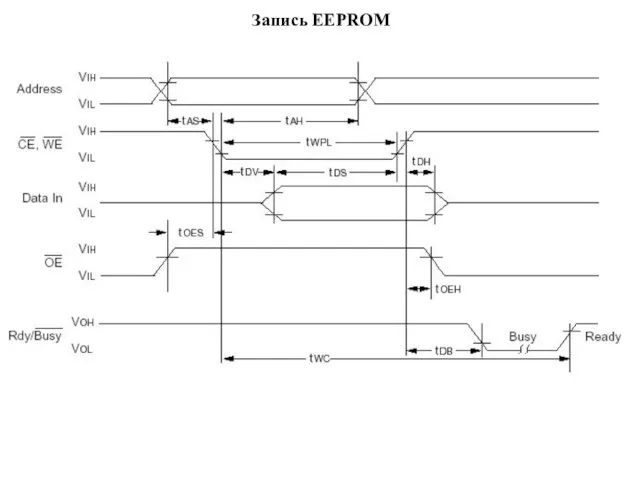

- 17. Запись EEPROM

- 18. Последовательные EEPROM 24С02 256х8

- 19. Интерфейс I2C

- 20. Запись байта Чтение байта по текущему адресу Чтение байта по произвольному адресу

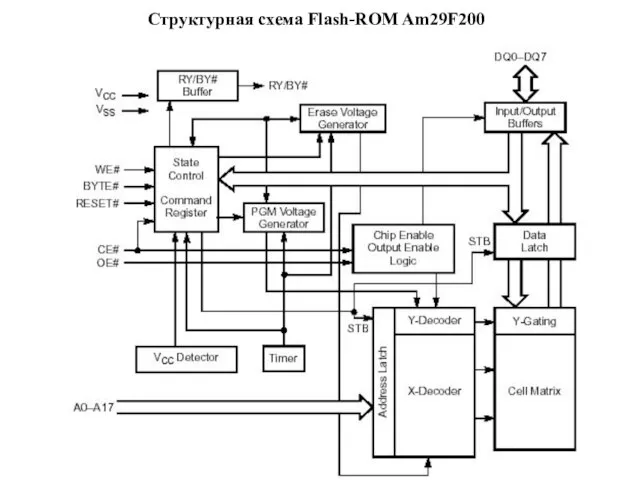

- 21. Структурная схема Flash-ROM Am29F200

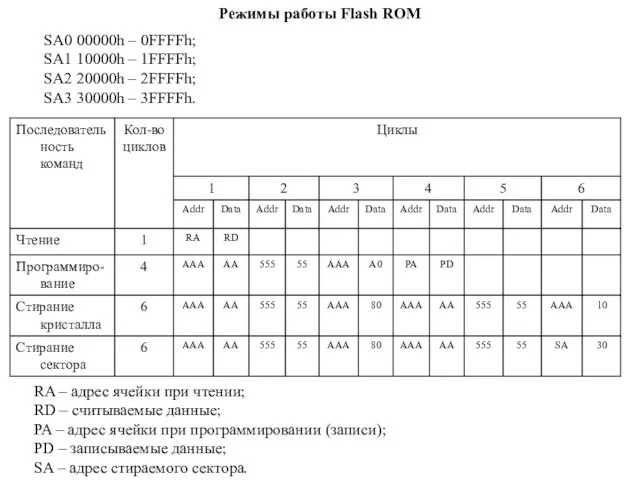

- 22. Режимы работы Flash ROM SA0 00000h – 0FFFFh; SA1 10000h – 1FFFFh; SA2 20000h – 2FFFFh;

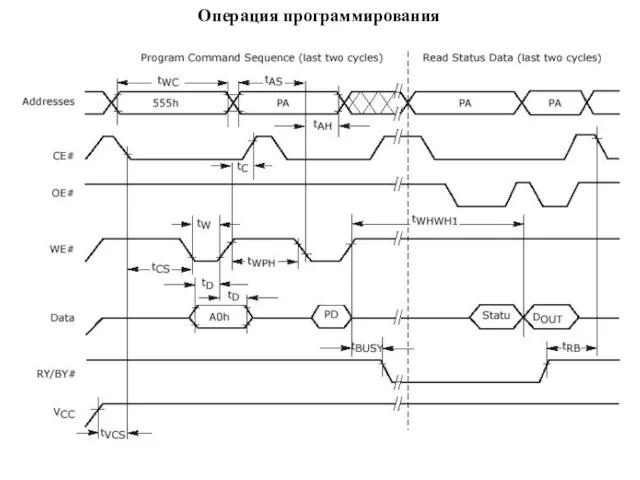

- 23. Операция программирования

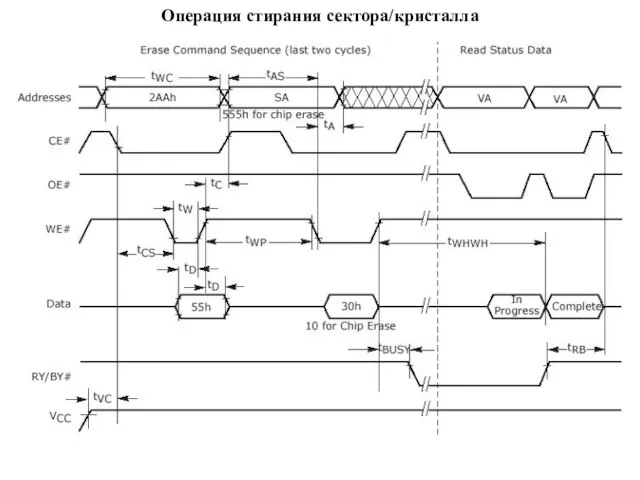

- 24. Операция стирания сектора/кристалла

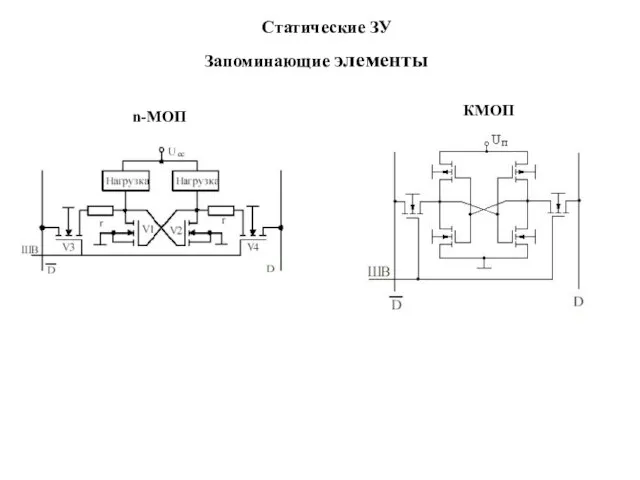

- 25. Запоминающие элементы n-МОП КМОП Статические ЗУ

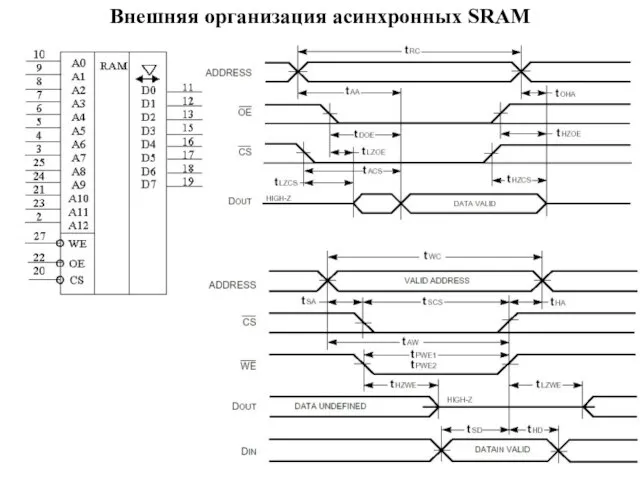

- 26. Внешняя организация асинхронных SRAM

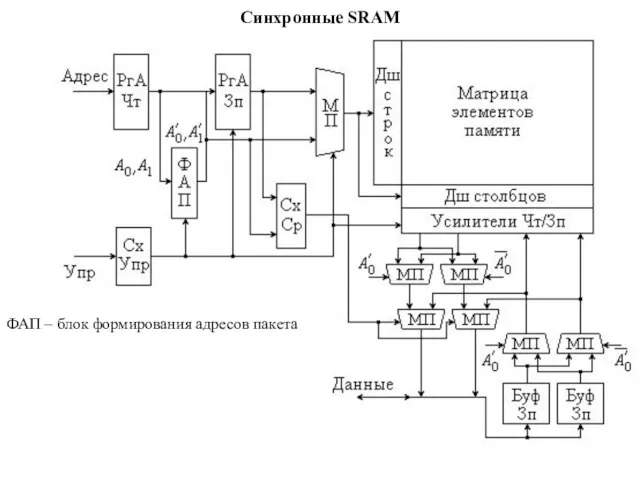

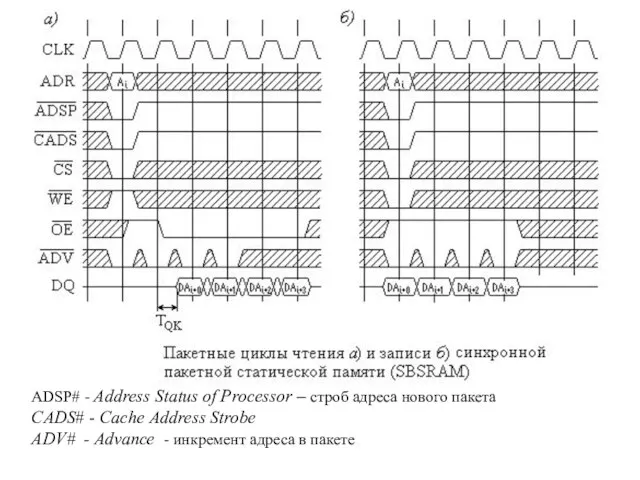

- 27. Синхронные SRAM ФАП – блок формирования адресов пакета

- 28. ADSP# - Address Status of Processor – строб адреса нового пакета CADS# - Cache Address Strobe

- 29. DDR Pipelined Burst SRAM DDR - Double Data Rate - двойная скорость передачи данных CQ и

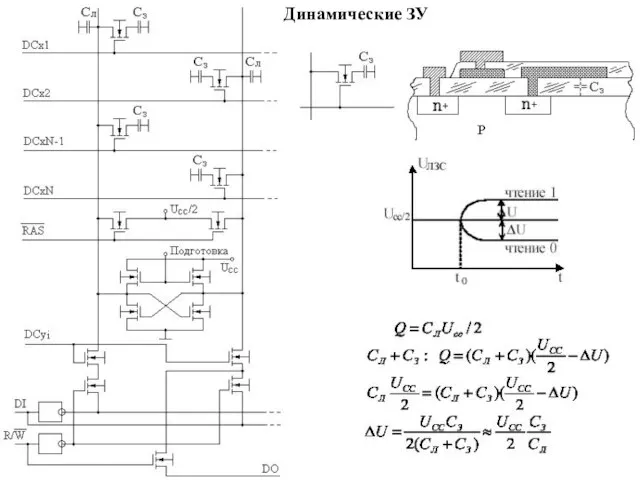

- 30. Динамические ЗУ

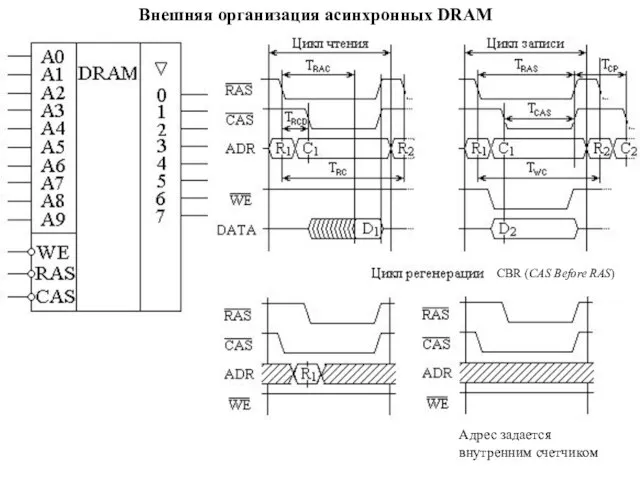

- 31. Внешняя организация асинхронных DRAM Адрес задается внутренним счетчиком CBR (CAS Before RAS)

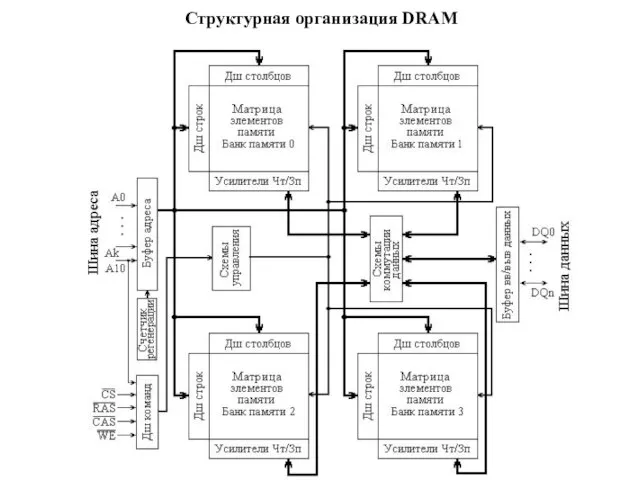

- 32. Структурная организация DRAM

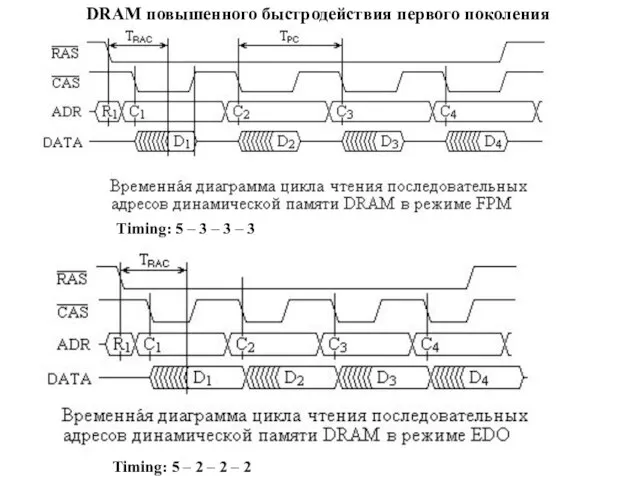

- 33. DRAM повышенного быстродействия первого поколения Timing: 5 – 3 – 3 – 3 Timing: 5 –

- 34. Синхронные DRAM (SDRAM) 1. CLK – синхросигнал (по переднему фронту). 2. CKE (Clock Enable) разрешения (низкий

- 37. Регенерация (refresh) SDRAM

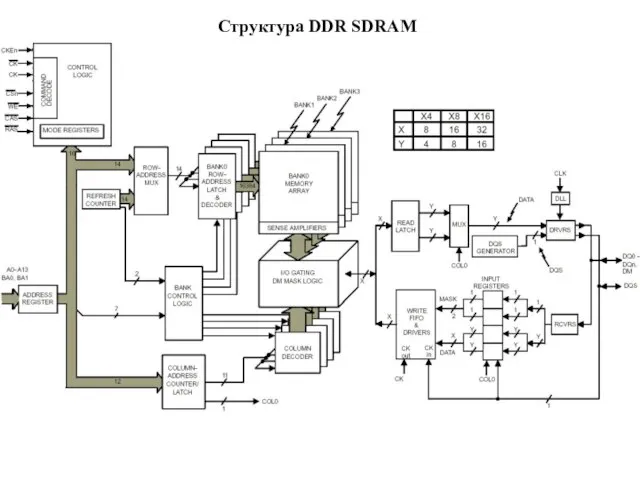

- 38. Структура DDR SDRAM

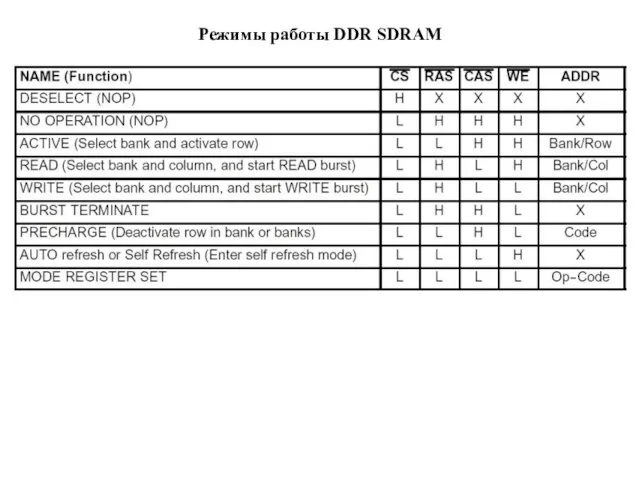

- 39. Режимы работы DDR SDRAM

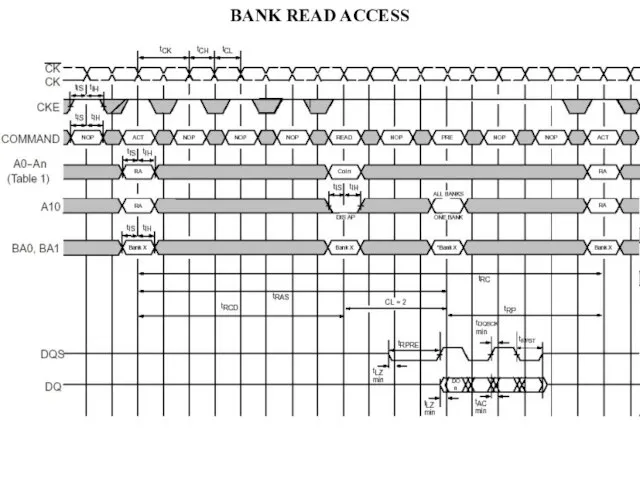

- 40. BANK READ ACCESS

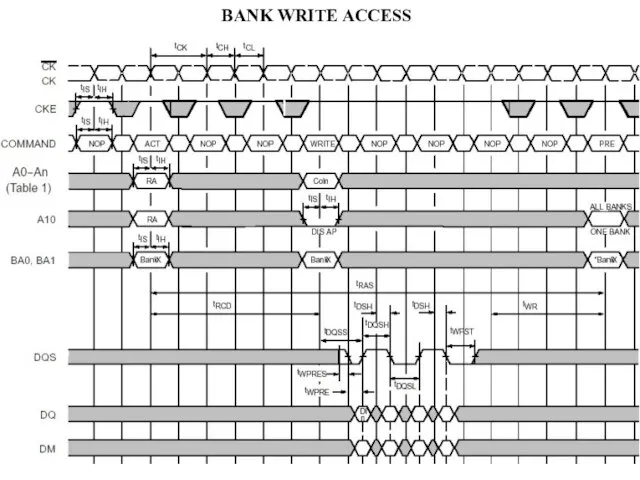

- 41. BANK WRITE ACCESS

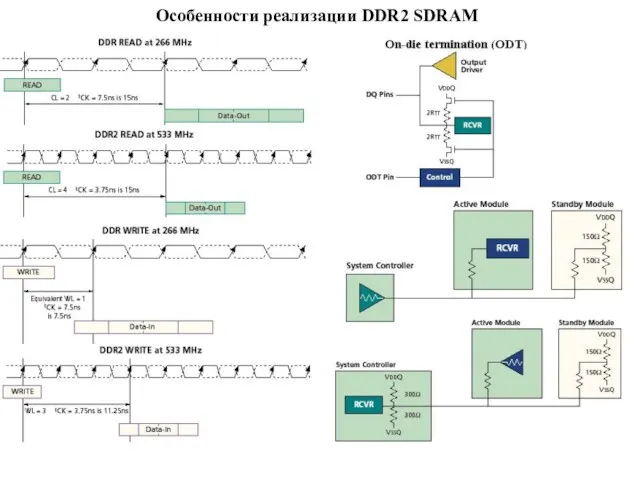

- 42. Особенности реализации DDR2 SDRAM

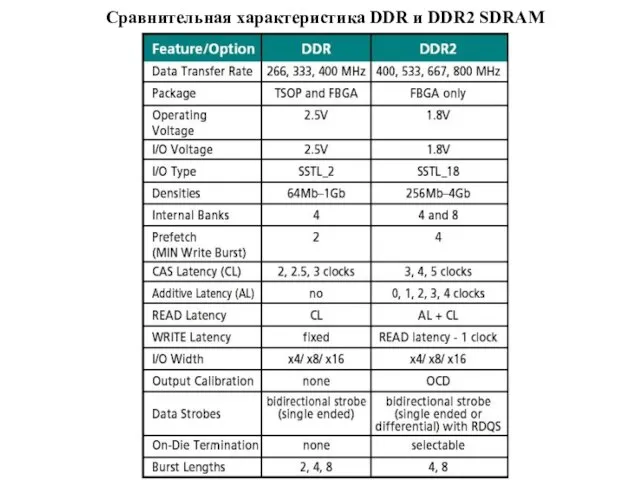

- 43. Сравнительная характеристика DDR и DDR2 SDRAM

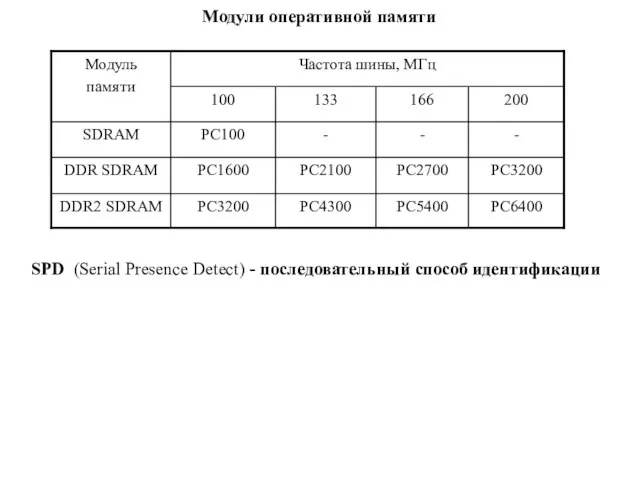

- 44. Модули оперативной памяти SPD (Serial Presence Detect) - последовательный способ идентификации

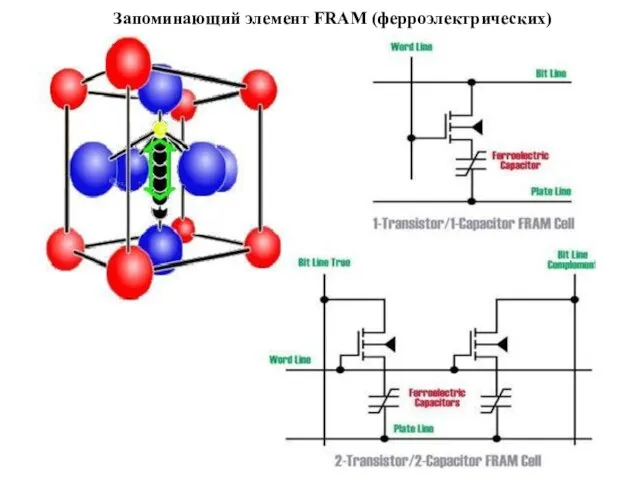

- 45. Запоминающий элемент FRAM (ферроэлектрических)

- 47. Скачать презентацию

20171104_komi_skazka_prezentatsiya

20171104_komi_skazka_prezentatsiya Лего школа. Занятие

Лего школа. Занятие ЗАО ЭКСМАШ. Колесный экскаватор Е140W

ЗАО ЭКСМАШ. Колесный экскаватор Е140W Жестяное кашпо из банки

Жестяное кашпо из банки Евангелие и я

Евангелие и я Экологический обзор

Экологический обзор Базовые формы оригами

Базовые формы оригами Стандарты и спецификации смазочных материалов

Стандарты и спецификации смазочных материалов Публичное акционерное общество Т Плюс

Публичное акционерное общество Т Плюс Притчи о прощение обид и взаимопомощи

Притчи о прощение обид и взаимопомощи Закономерности развития психики детей с соматическими заболеваниями

Закономерности развития психики детей с соматическими заболеваниями мунк

мунк ИСХОДНИК Презентация BODY-PIT-3 (2)

ИСХОДНИК Презентация BODY-PIT-3 (2) 20110409_Proekt_Pobeda_deda_-_semi_pobeda

20110409_Proekt_Pobeda_deda_-_semi_pobeda 20131030_cheloek_biosotsialnoe_sushchestvo_0

20131030_cheloek_biosotsialnoe_sushchestvo_0 Система топливного, пускового и импульсного газа

Система топливного, пускового и импульсного газа Siltuma elektrostacijas

Siltuma elektrostacijas Мисс Бобруйщина - 2014. Запольская Мария Владимировна

Мисс Бобруйщина - 2014. Запольская Мария Владимировна Контекстные задачи как способ формирования у школьников навыков решения практических проблем

Контекстные задачи как способ формирования у школьников навыков решения практических проблем Тері эпителийі эволюциялық динамикасының кейбір заңдылықтары

Тері эпителийі эволюциялық динамикасының кейбір заңдылықтары Последний звонок

Последний звонок BTS'22 — механика, customer journey, призы (1)

BTS'22 — механика, customer journey, призы (1) Darts

Darts Лекция №2

Лекция №2 Электроснабжение горных предприятий

Электроснабжение горных предприятий Барельеф .А. Сидоран (2)

Барельеф .А. Сидоран (2) Разработка способа для увода наноспутников CubeSat c низких околоземных орбит

Разработка способа для увода наноспутников CubeSat c низких околоземных орбит Организация деятельности обучающихся по выполнению индивидуального проекта

Организация деятельности обучающихся по выполнению индивидуального проекта