Содержание

- 2. Состав и структура персональных ЭВМ и вычислительных систем

- 3. Вычислительные архитектуры

- 4. принстонская и гарвардская архитектуры В 30-х годах прошлого века военное ведомство США поручило Гарвардскому и Принстонскому

- 5. Принципы фон Неймана(1945г.) Принцип программного управления Принцип однородности памяти Принцип адресности Принцип двоичного кодирования -согласно этому

- 6. Принципы фон Неймана(2000 –е годы) Оперативная память(ОП) организована как совокупность машинных слов(МС) фиксированной длины или разрядности

- 7. Функциональные блоки Центральное устройство(ЦУ) включает ЦП(CPU) и ОП(RAM) Арифметико-логическое устройство(АЛУ) Внешние устройства(ВУ) Интерфейсы(каналы связи)

- 8. Машина фон Неймана состоит из запоминающего устройства (памяти) - ЗУ, арифметико-логического устройства - АЛУ, устройства управления

- 9. Архитектура «звезда» Оперативная память Процессор Внешнее устройство

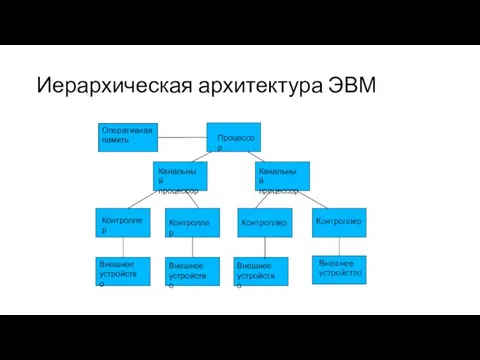

- 10. Иерархическая архитектура ЭВМ Оперативная память Процессор Канальный процессор Канальный процессор Контроллер Контроллер Внешнее устройство Внешнее устройство

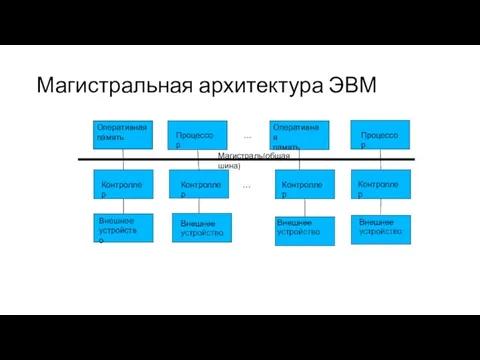

- 11. Магистральная архитектура ЭВМ Оперативная память Оперативная память Процессор Процессор Контроллер Контроллер Контроллер Контроллер Внешнее устройство Магистраль(общая

- 13. Скачать презентацию

Вера православных христиан

Вера православных христиан Кризисные состояния у детей и подростков

Кризисные состояния у детей и подростков Что такое комбинаторика?

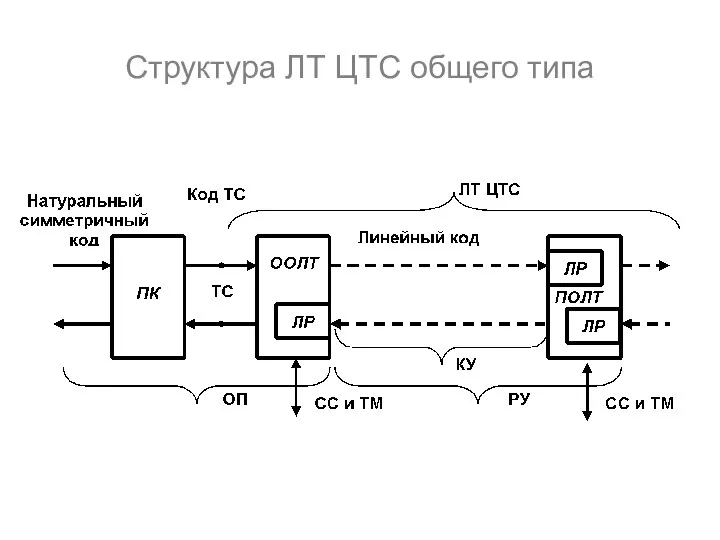

Что такое комбинаторика? Структура линейных трактов центральной телекоммуникационной системы общего типа

Структура линейных трактов центральной телекоммуникационной системы общего типа Бекеттік автоматика және телемеханика жүйелері. Электрлік орталықтандыру жүйелерінің топтастырылуы. (Дәріс 1)

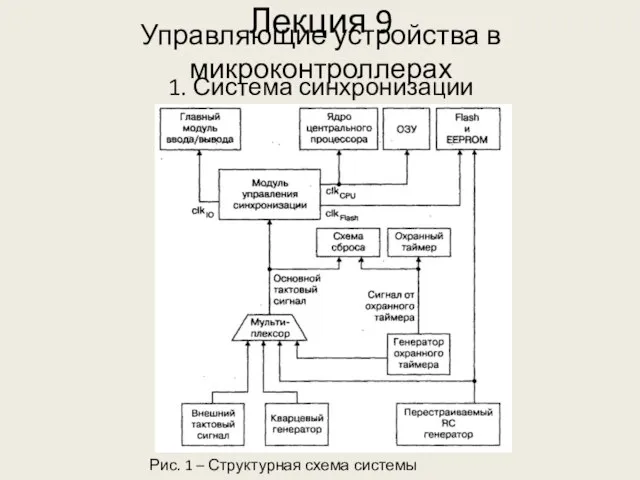

Бекеттік автоматика және телемеханика жүйелері. Электрлік орталықтандыру жүйелерінің топтастырылуы. (Дәріс 1) Управляющие устройства в микроконтроллерах. (Лекция 9)

Управляющие устройства в микроконтроллерах. (Лекция 9) Презентация (12)

Презентация (12) Сердце отданное комсомолу…

Сердце отданное комсомолу… Внутренние разделители для пултрузии

Внутренние разделители для пултрузии Benefits of Top Best Sex Cams

Benefits of Top Best Sex Cams Ислам в России

Ислам в России Холдинг БелОМО. План технологического развития до 2020 года

Холдинг БелОМО. План технологического развития до 2020 года Призначення, склад та технічні характеристики телефонних апаратів систем МБ, ЦБ. Класифікація АТС

Призначення, склад та технічні характеристики телефонних апаратів систем МБ, ЦБ. Класифікація АТС Modlitwa Jana Pawła II o powołania

Modlitwa Jana Pawła II o powołania 20150110_industrialnaya_revolyutsiya

20150110_industrialnaya_revolyutsiya Алатау - 2016

Алатау - 2016 20160704_st._v_proze_turgenev

20160704_st._v_proze_turgenev 20110829_P_L_Yu_Shch

20110829_P_L_Yu_Shch Альтернативные источники энергии ветра

Альтернативные источники энергии ветра Проектирование электрооборудования автозаправкинг

Проектирование электрооборудования автозаправкинг Сварочные деформации

Сварочные деформации ЗВУК И ВИДЕО В ИНТЕРНЕТЕ

ЗВУК И ВИДЕО В ИНТЕРНЕТЕ Полупроводниковые диоды. Тема 3

Полупроводниковые диоды. Тема 3 Технология производства термо-формуемых ППУ стелек

Технология производства термо-формуемых ППУ стелек Обслуживание трансформаторов

Обслуживание трансформаторов Технологический процесс обработки и сборки воротников в изделиях пальтово-костюмного ассортимента

Технологический процесс обработки и сборки воротников в изделиях пальтово-костюмного ассортимента Кинематограф 90-х гг

Кинематограф 90-х гг Схема проезда на ЦТ Климовск

Схема проезда на ЦТ Климовск