Содержание

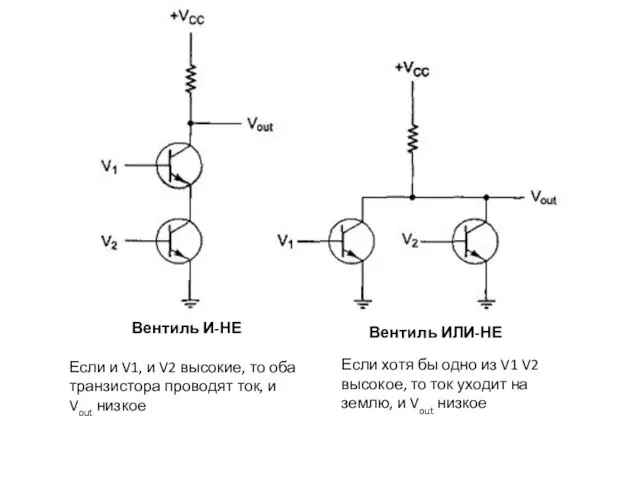

- 2. Вентиль И-НЕ Если и V1, и V2 высокие, то оба транзистора проводят ток, и Vout низкое

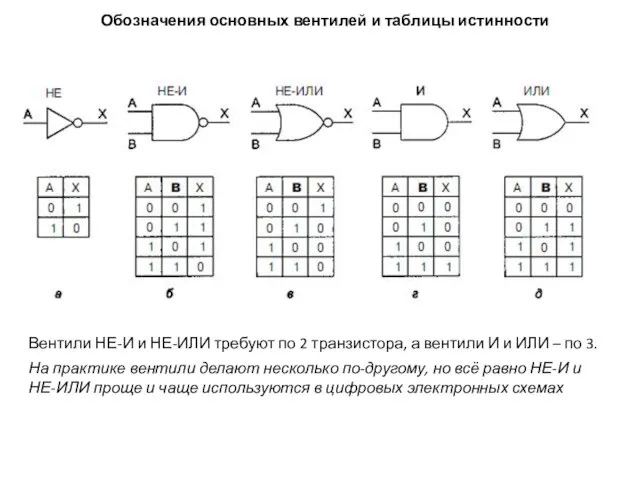

- 3. Обозначения основных вентилей и таблицы истинности Вентили НЕ-И и НЕ-ИЛИ требуют по 2 транзистора, а вентили

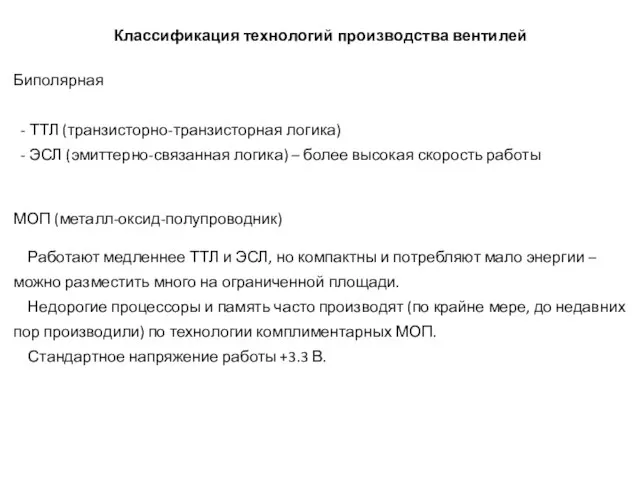

- 4. Классификация технологий производства вентилей Биполярная - ТТЛ (транзисторно-транзисторная логика) - ЭСЛ (эмиттерно-связанная логика) – более высокая

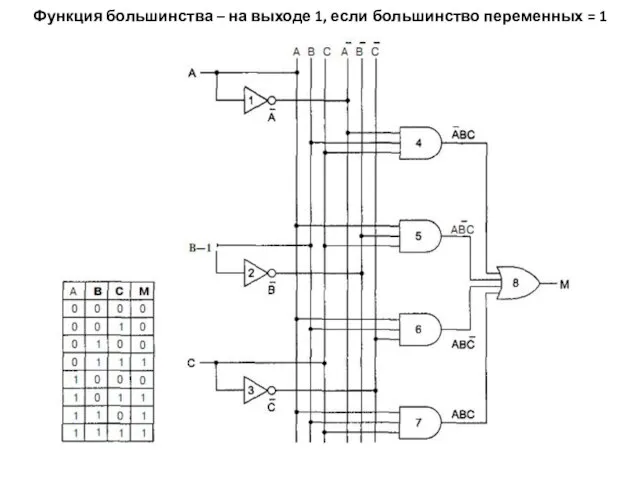

- 5. Функция большинства – на выходе 1, если большинство переменных = 1

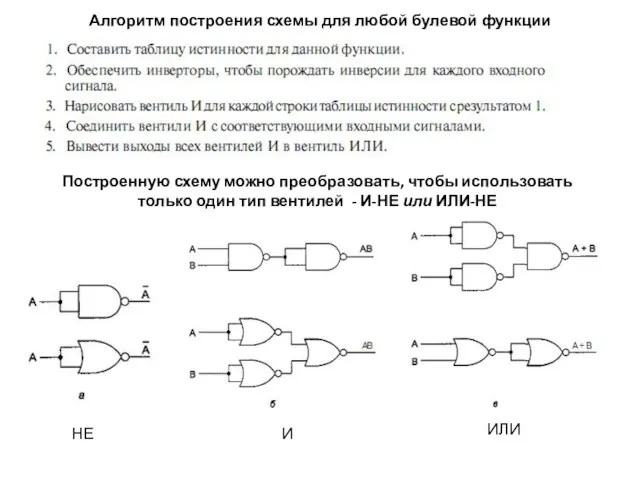

- 6. Алгоритм построения схемы для любой булевой функции Построенную схему можно преобразовать, чтобы использовать только один тип

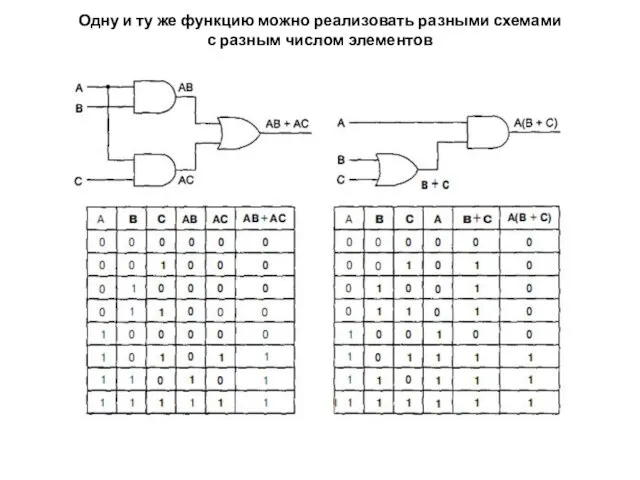

- 7. Одну и ту же функцию можно реализовать разными схемами с разным числом элементов

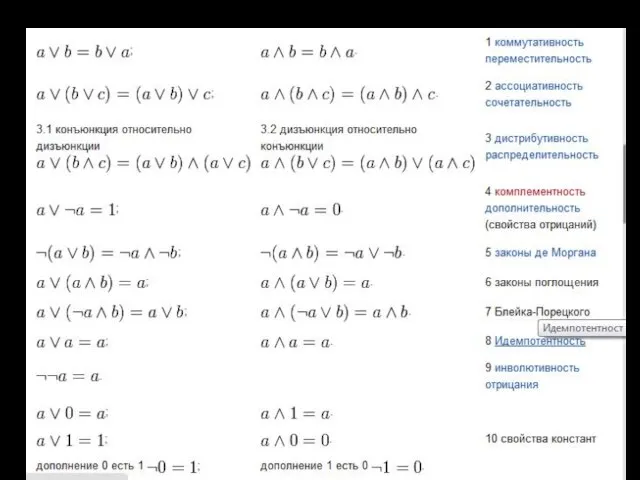

- 8. Для минимизации булевых функций используются законы булевой алгебры

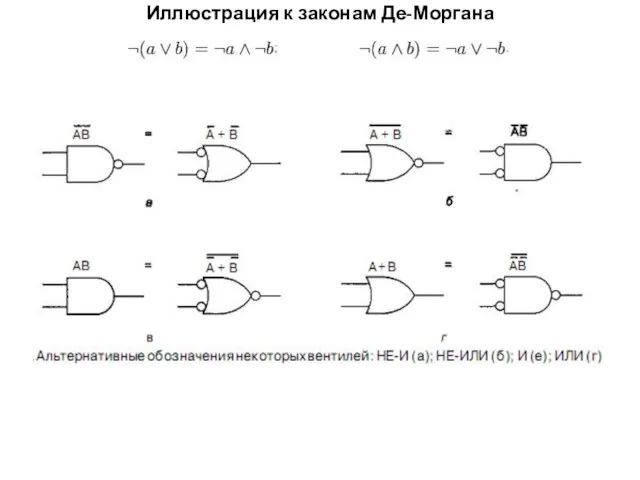

- 9. Иллюстрация к законам Де-Моргана

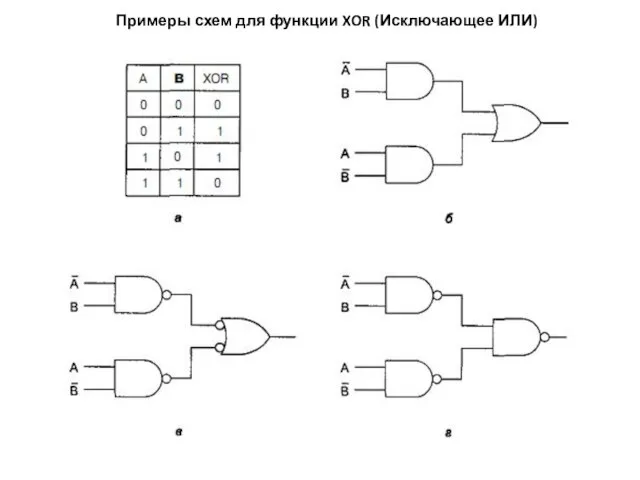

- 10. Примеры схем для функции XOR (Исключающее ИЛИ)

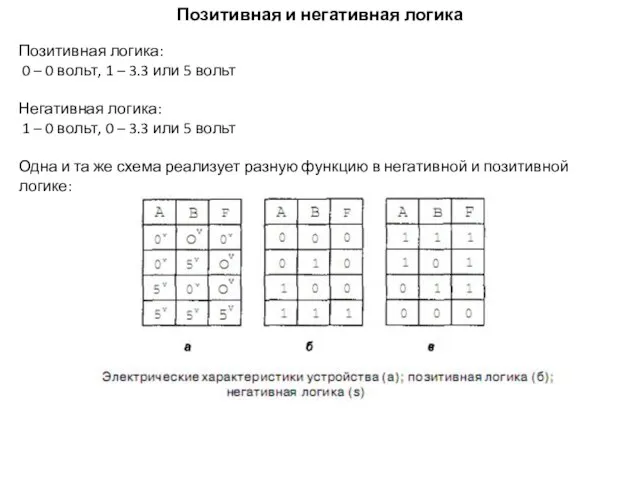

- 11. Позитивная и негативная логика Позитивная логика: 0 – 0 вольт, 1 – 3.3 или 5 вольт

- 12. Интегральные схемы Сейчас на одну микросхему помещают уже десятки миллионов транзисторов

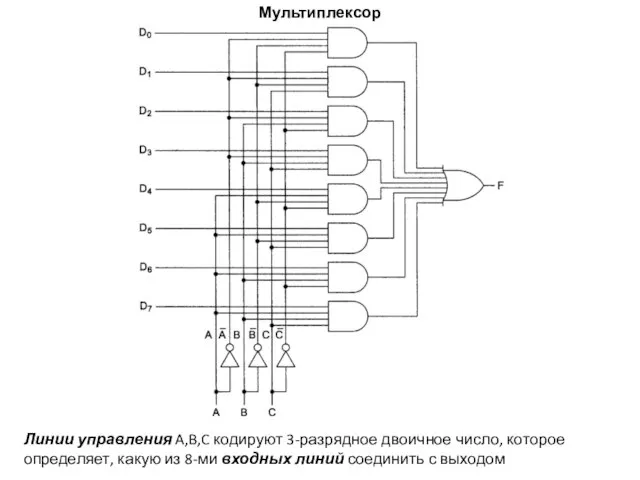

- 13. Мультиплексор Линии управления A,B,C кодируют 3-разрядное двоичное число, которое определяет, какую из 8-ми входных линий соединить

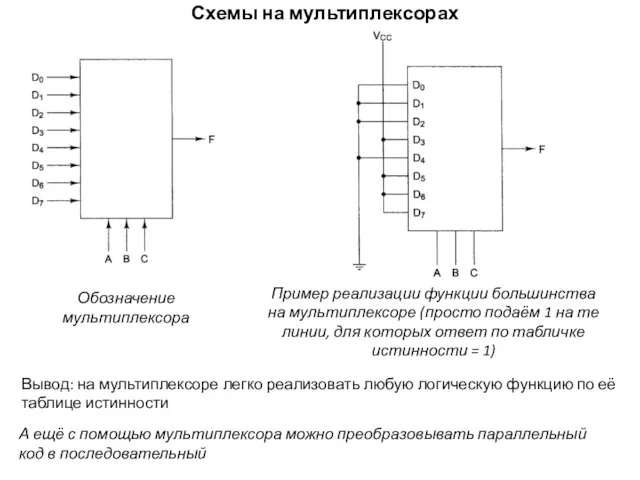

- 14. Схемы на мультиплексорах Обозначение мультиплексора Пример реализации функции большинства на мультиплексоре (просто подаём 1 на те

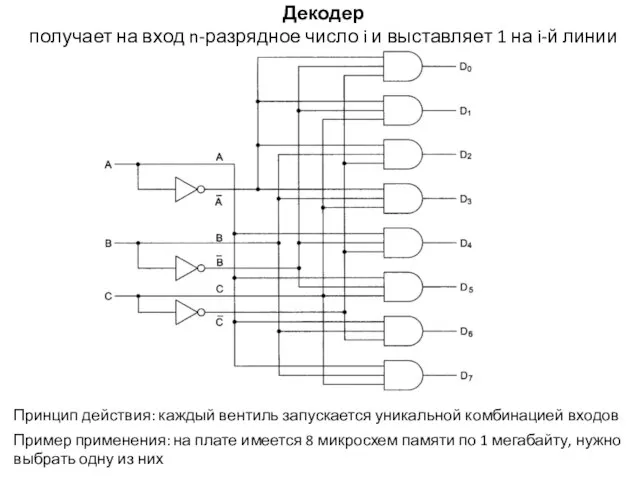

- 15. Декодер получает на вход n-разрядное число i и выставляет 1 на i-й линии Принцип действия: каждый

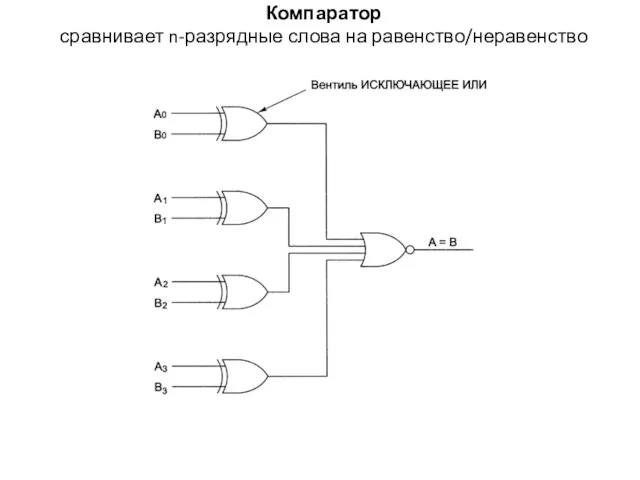

- 16. Компаратор сравнивает n-разрядные слова на равенство/неравенство

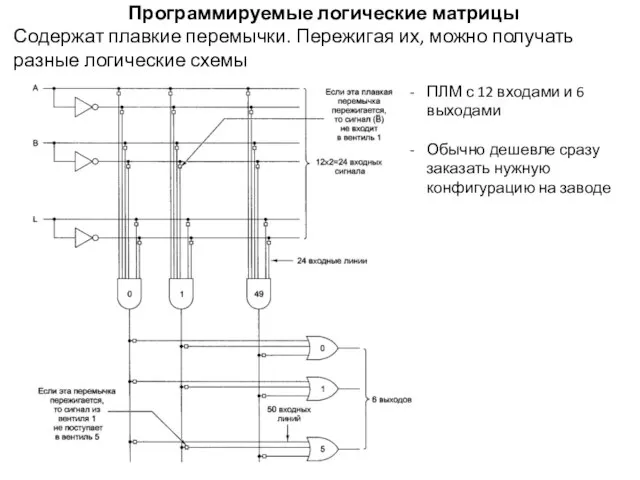

- 17. Программируемые логические матрицы Содержат плавкие перемычки. Пережигая их, можно получать разные логические схемы ПЛМ с 12

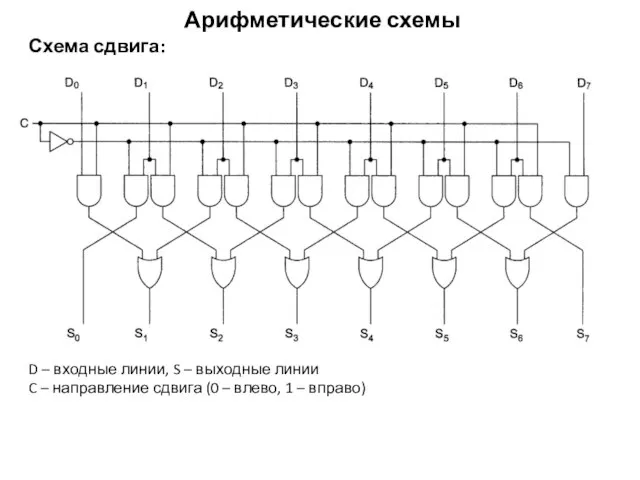

- 18. Арифметические схемы Схема сдвига: D – входные линии, S – выходные линии C – направление сдвига

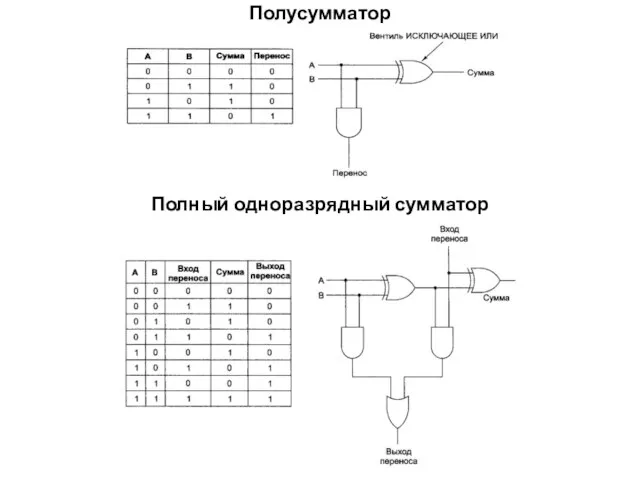

- 19. Полусумматор Полный одноразрядный сумматор

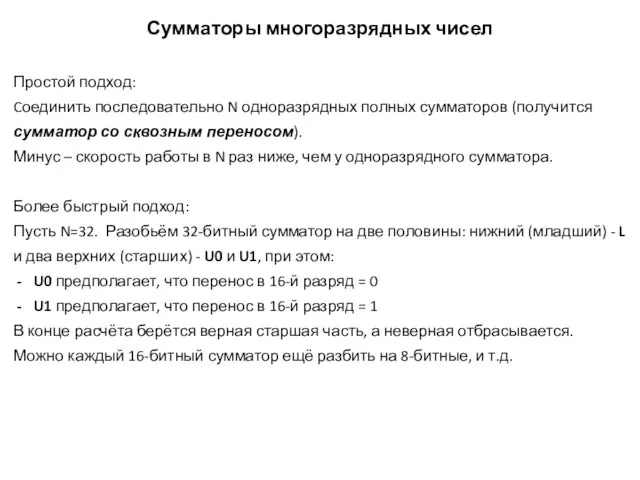

- 20. Сумматоры многоразрядных чисел Простой подход: Cоединить последовательно N одноразрядных полных сумматоров (получится сумматор со сквозным переносом).

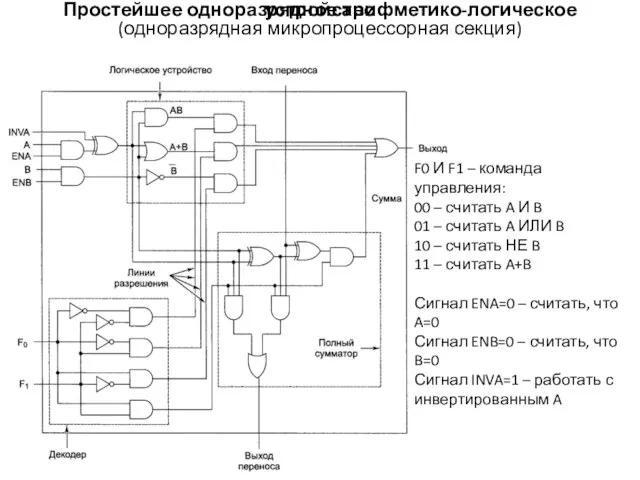

- 21. Простейшее одноразрядное арифметико-логическое устройство (одноразрядная микропроцессорная секция) F0 И F1 – команда управления: 00 – считать

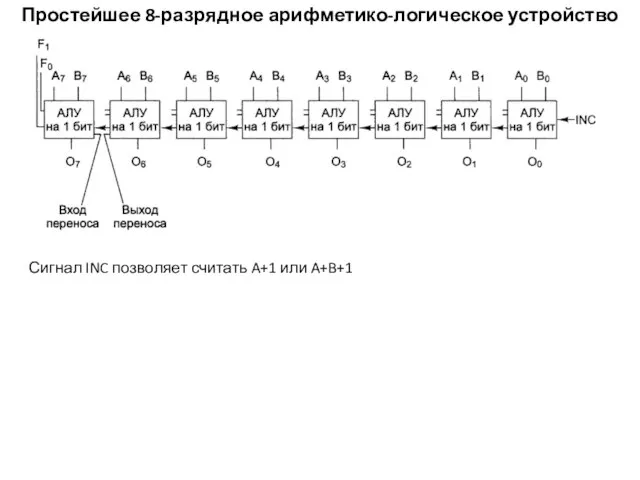

- 22. Простейшее 8-разрядное арифметико-логическое устройство Сигнал INC позволяет считать A+1 или A+B+1

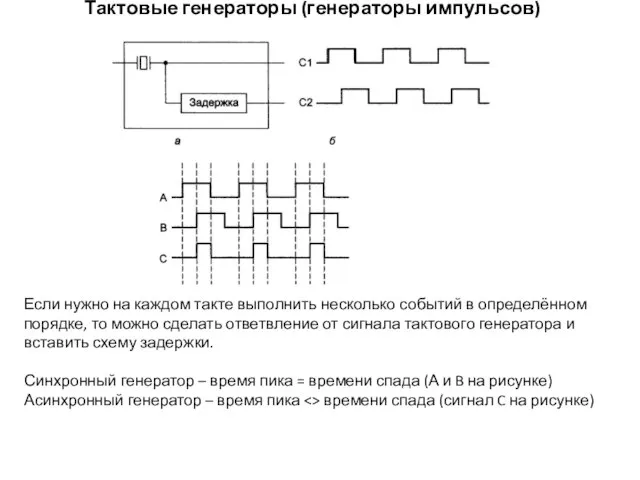

- 23. Тактовые генераторы (генераторы импульсов) Если нужно на каждом такте выполнить несколько событий в определённом порядке, то

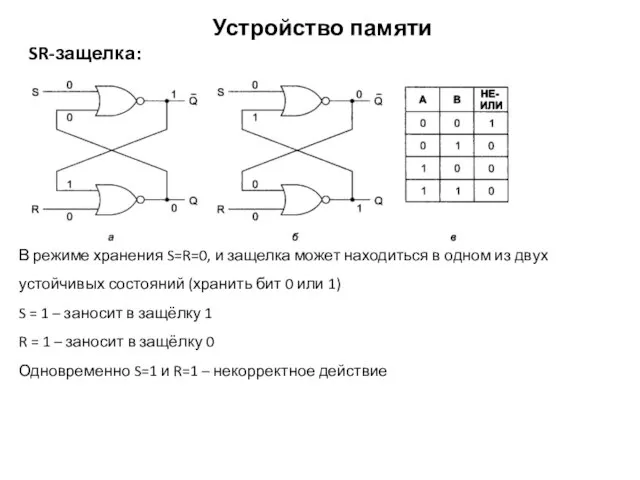

- 24. Устройство памяти SR-защелка: В режиме хранения S=R=0, и защелка может находиться в одном из двух устойчивых

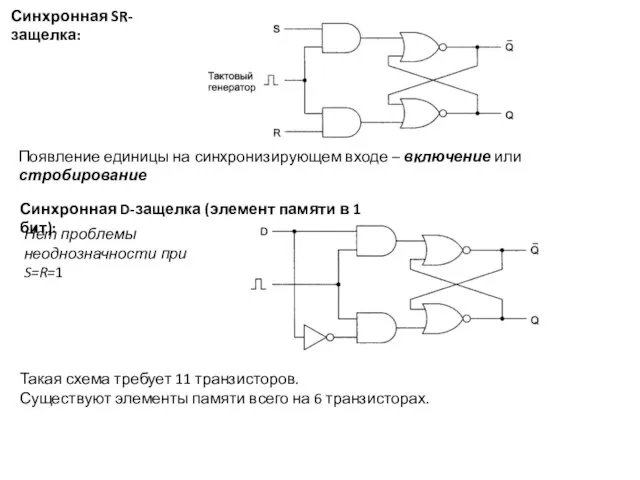

- 25. Синхронная SR-защелка: Появление единицы на синхронизирующем входе – включение или стробирование Синхронная D-защелка (элемент памяти в

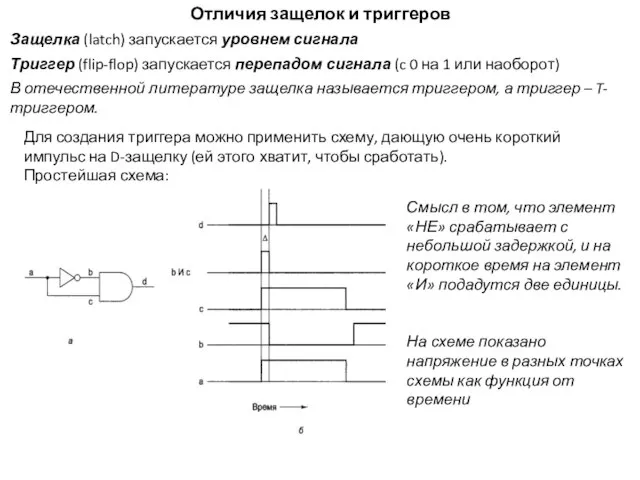

- 26. Отличия защелок и триггеров Защелка (latch) запускается уровнем сигнала Триггер (flip-flop) запускается перепадом сигнала (c 0

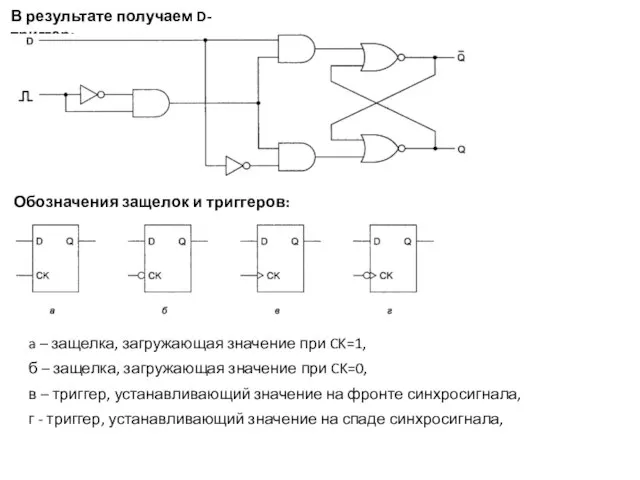

- 27. В результате получаем D-триггер: Обозначения защелок и триггеров: a – защелка, загружающая значение при CK=1, б

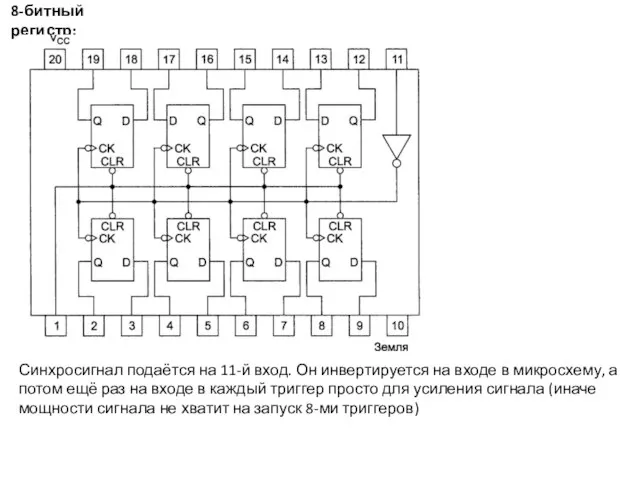

- 28. 8-битный регистр: Синхросигнал подаётся на 11-й вход. Он инвертируется на входе в микросхему, а потом ещё

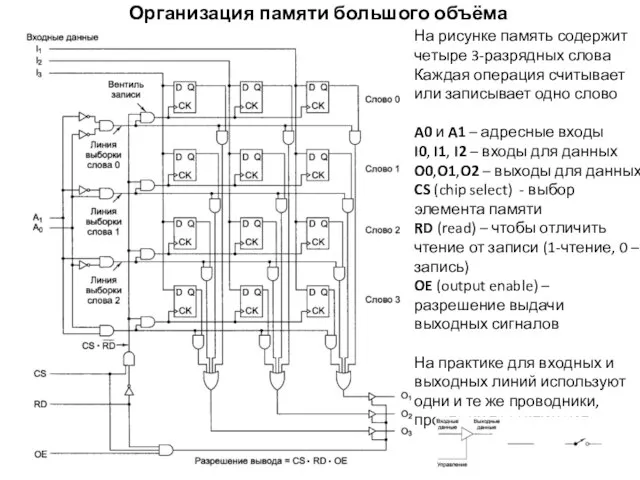

- 29. Организация памяти большого объёма На рисунке память содержит четыре 3-разрядных слова Каждая операция считывает или записывает

- 31. Скачать презентацию

Жеңіл өнеркәсіп

Жеңіл өнеркәсіп Портердің

Портердің Капиллярная дефектоскопия

Капиллярная дефектоскопия Чудосветова. Презентация

Чудосветова. Презентация Викторина Волшебный Мир

Викторина Волшебный Мир Определение объемов и трудоемкости монтажных работ

Определение объемов и трудоемкости монтажных работ Разработка дизайн проекта своей квартиры

Разработка дизайн проекта своей квартиры Активный перфорационный состав

Активный перфорационный состав Будет в НБ 30.03-05.04

Будет в НБ 30.03-05.04 Compliance, Safety, Accountability (CSA) and Drivers

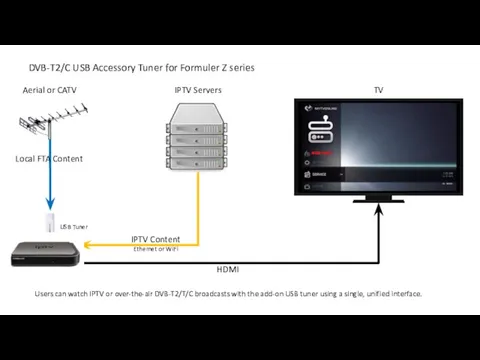

Compliance, Safety, Accountability (CSA) and Drivers DVB-T2/C USB Accessory Tuner for Formuler Z series

DVB-T2/C USB Accessory Tuner for Formuler Z series Проект системы энергоснабжения производственно-жилого микрорайона

Проект системы энергоснабжения производственно-жилого микрорайона Визначення навантажень на раму однопрольотної будівлі

Визначення навантажень на раму однопрольотної будівлі Системы и сети подвижной радиосвязи

Системы и сети подвижной радиосвязи Prezentatsia

Prezentatsia Team4 (1)

Team4 (1) День открытых дверей!

День открытых дверей! Обработка жилета

Обработка жилета Буддизм История. Направления. Религиозный культ. Тема 9

Буддизм История. Направления. Религиозный культ. Тема 9 20140616_impressionizm

20140616_impressionizm Зимние праздники от Рождества до Крещения

Зимние праздники от Рождества до Крещения Ветеринарно-санитарная техника 2013 г

Ветеринарно-санитарная техника 2013 г Человек в религиозных традициях мира

Человек в религиозных традициях мира 20130217_obshchestvo_5_klass

20130217_obshchestvo_5_klass 20151009_voennye_pohody_faraonov_tehnologicheskaya_karta_uroka

20151009_voennye_pohody_faraonov_tehnologicheskaya_karta_uroka Baumaterialien

Baumaterialien Шишигин Интересный больной практика

Шишигин Интересный больной практика Multimeter

Multimeter