Цифровые устройства и микропроцессоры. Тема 1. Основы схемотехники и элементная база цифровых электронных устройств

Содержание

- 2. СТРУКТУРА УЧЕБНОЙ ДИСЦИПЛИНЫ ДС-1321

- 3. Содержание темы 1 «Основы схемотехники и элементная база комбинационных цифровых электронных устройств»

- 4. ЛЕКЦИЯ №3 Основы схемотехники и элементная база типовых комбинационных цифровых электронных устройств

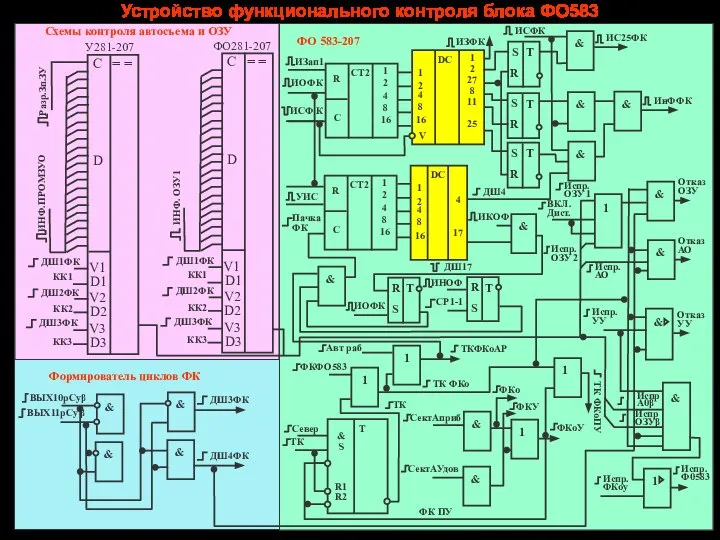

- 5. С = = V1 D1 V2 D2 V3 D3 D КК3 КК2 КК1 ИНФ.ПРОМЗУО Разр.Зп.ЗУ С

- 6. Систематизировать основы научных знаний по основам схемотехники и элементной базе комбинационных цифровых устройств. УЧЕБНАЯ ЦЕЛЬ ЛЕКЦИИ

- 7. УЧЕБНЫЕ ВОПРОСЫ ЛЕКЦИИ Шифраторы и дешифраторы. Мультиплексоры и демультиплексоры. Сумматоры и арифметико-логические устройства. Схемы контроля четности.

- 8. Цифровые устройства и микропроцессоры [Электронный ресурс]: Учебное пособие / Е. Н. Жидков и [др.]. – Тверь:

- 9. 1. Шифраторы и дешифраторы

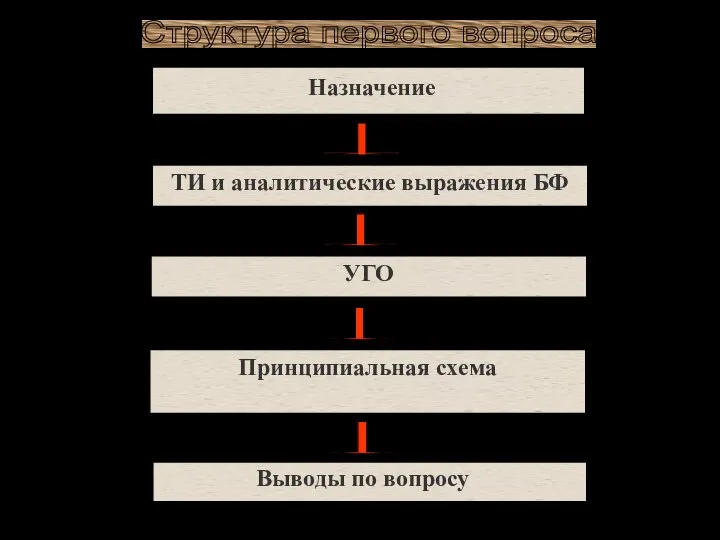

- 10. Структура первого вопроса

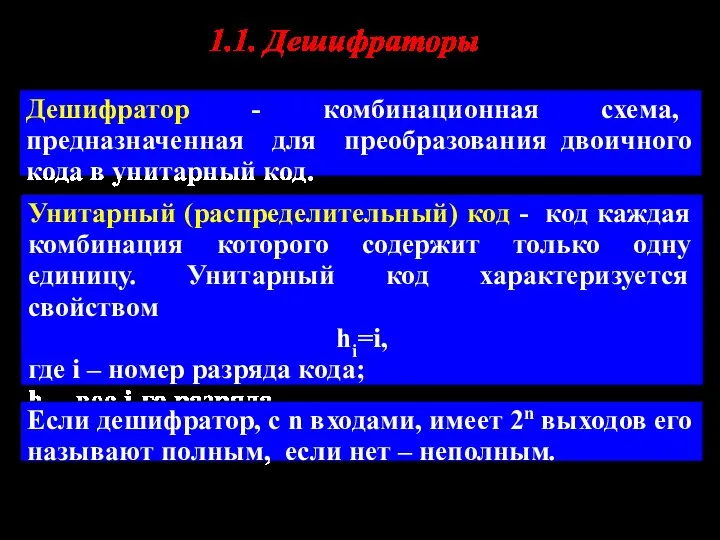

- 11. Дешифратор - комбинационная схема, предназначенная для преобразования двоичного кода в унитарный код. Унитарный (распределительный) код -

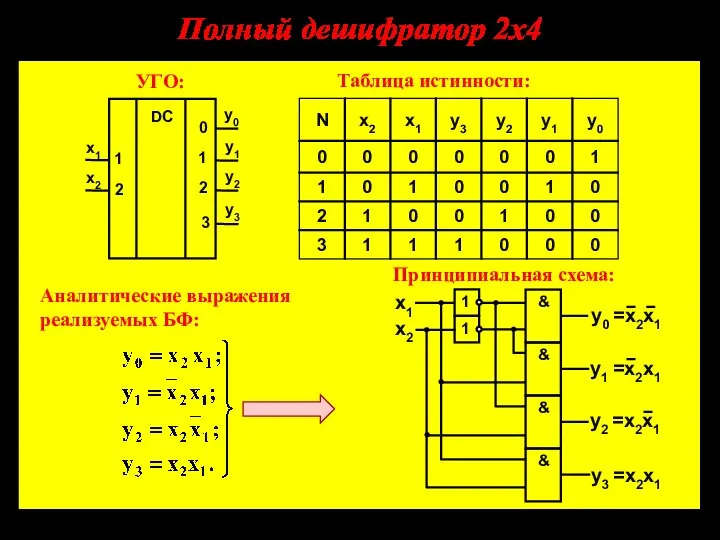

- 12. УГО: Полный дешифратор 2х4

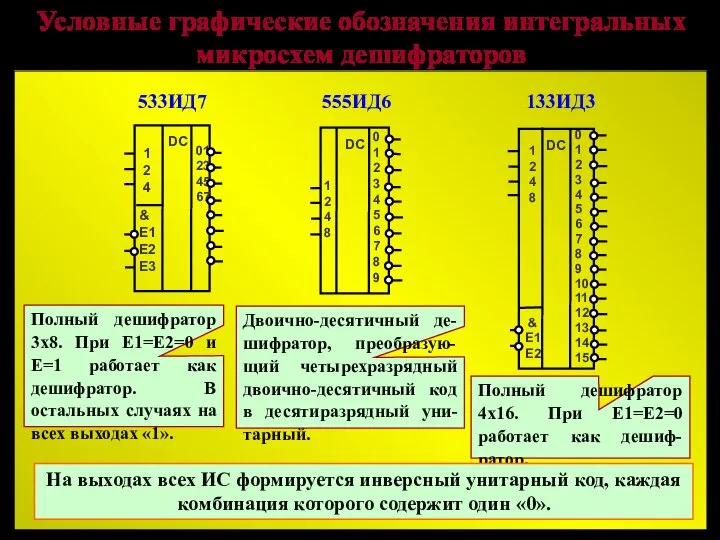

- 13. Полный дешифратор 3х8. При Е1=Е2=0 и Е=1 работает как дешифратор. В остальных случаях на всех выходах

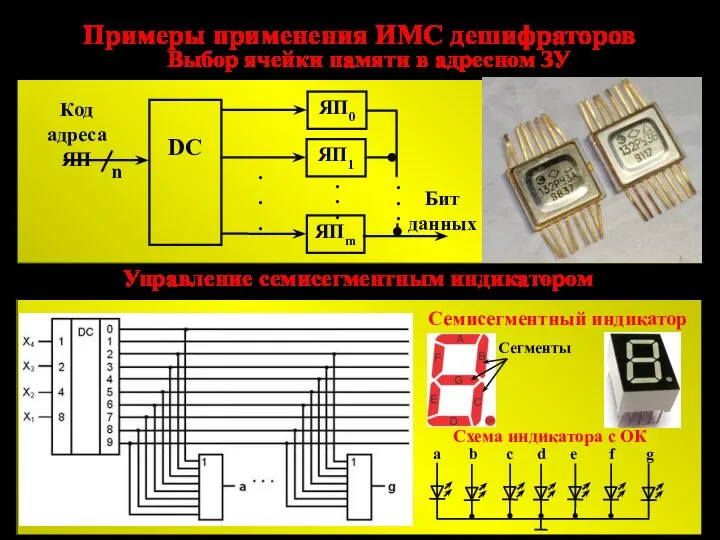

- 14. Примеры применения ИМС дешифраторов

- 15. Корпус 239.24-1 2 – тип корпуса; 39 – подтип; 24 – количество выводов; 1 – регистрационный

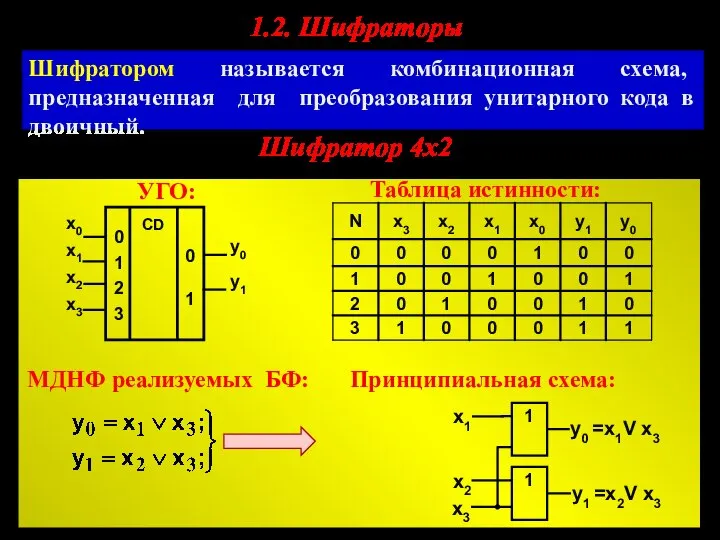

- 16. Шифратором называется комбинационная схема, предназначенная для преобразования унитарного кода в двоичный. 1.2. Шифраторы Шифратор 4х2

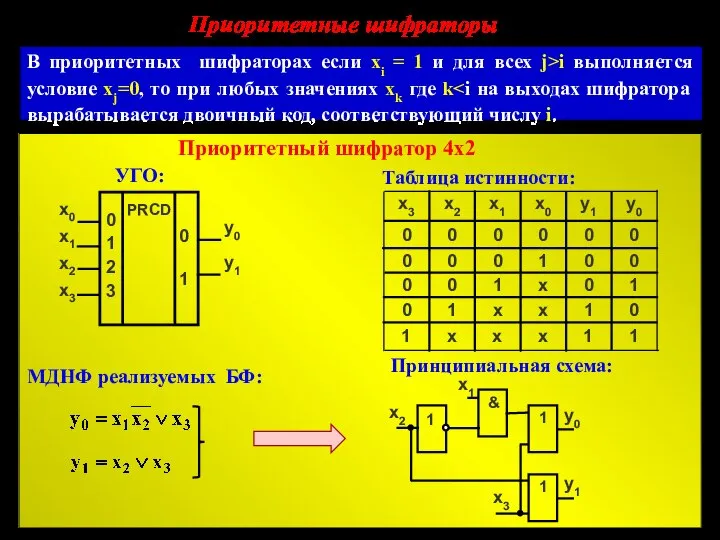

- 17. В приоритетных шифраторах если xi = 1 и для всех j>i выполняется условие xj=0, то при

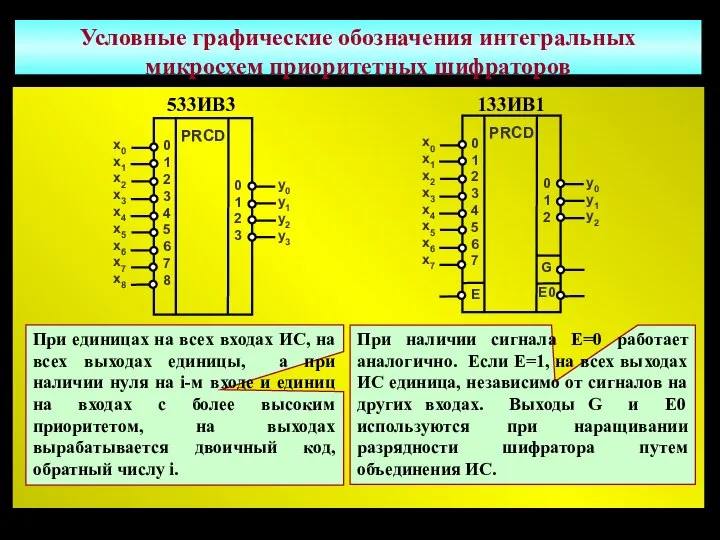

- 18. Условные графические обозначения интегральных микросхем приоритетных шифраторов При единицах на всех входах ИС, на всех выходах

- 19. Пример применения ИМС шифратора для организации простейшей клавиатуры

- 20. Выводы по вопросу Дешифраторы преобразуют двоичный код в унитарный, а шифраторы преобразуют унитарный код в двоичный,

- 21. 2. Мультиплексоры и демультиплексоры

- 22. Структура второго вопроса

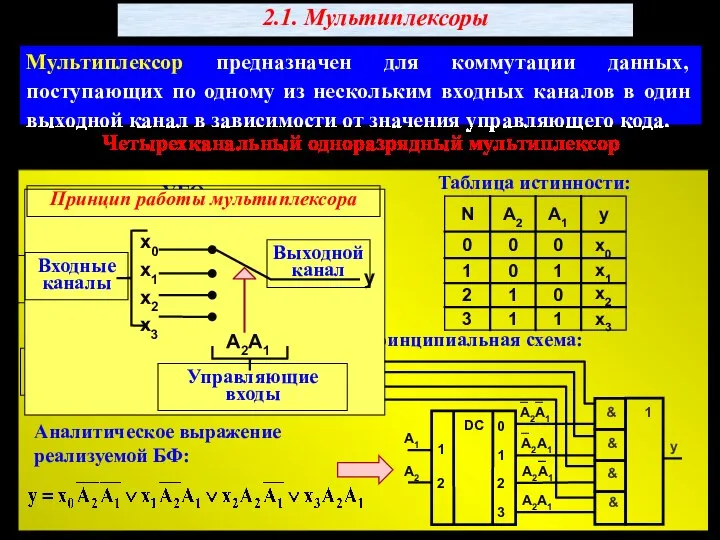

- 23. Мультиплексор предназначен для коммутации данных, поступающих по одному из нескольким входных каналов в один выходной канал

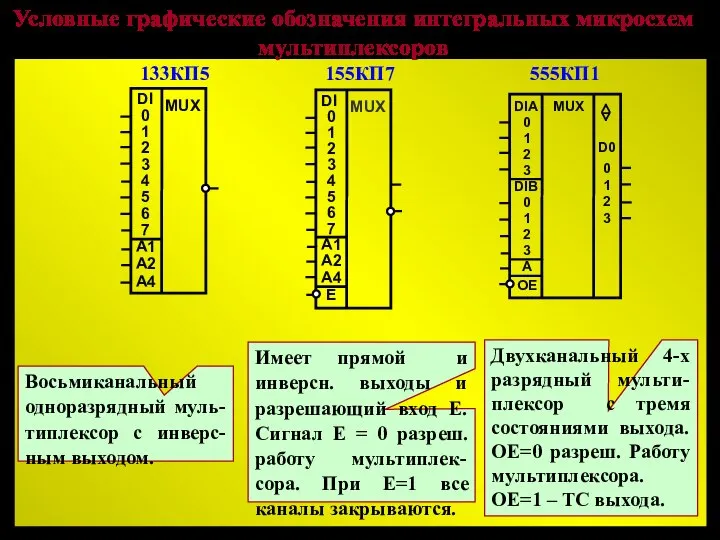

- 24. Восьмиканальный одноразрядный муль-типлексор с инверс-ным выходом. Имеет прямой и инверсн. выходы и разрешающий вход Е. Сигнал

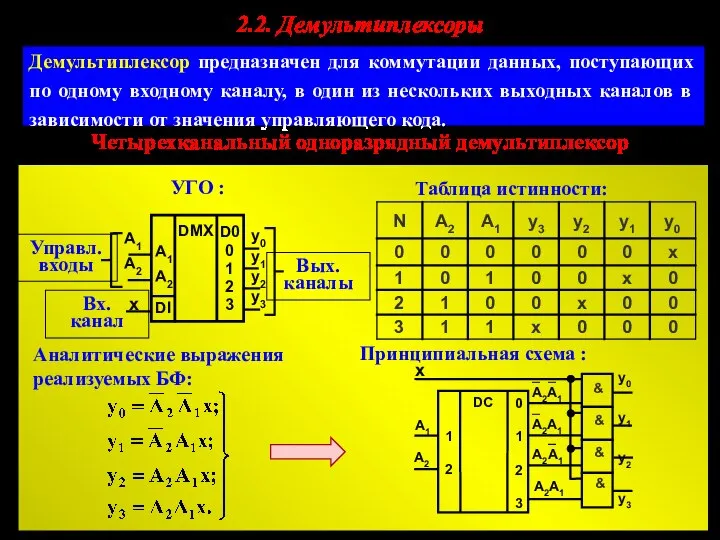

- 25. Демультиплексор предназначен для коммутации данных, поступающих по одному входному каналу, в один из нескольких выходных каналов

- 26. Выводы по вопросу Мультиплексоры коммутируют данные, поступающие по нескольким входным каналам в один выходной канал, а

- 27. 3. Сумматоры и арифметико-логические устройства

- 28. Структура третьего вопроса

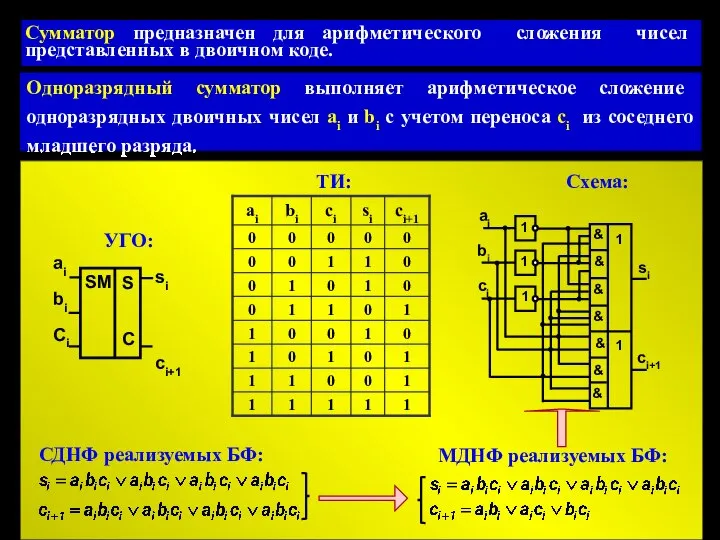

- 29. Одноразрядный сумматор выполняет арифметическое сложение одноразрядных двоичных чисел ai и bi с учетом переноса сi из

- 30. Многоразрядный сумматор с последовательным переносом строится на основе одноразрядных сумматоров путем соединения их по цепям переноса.

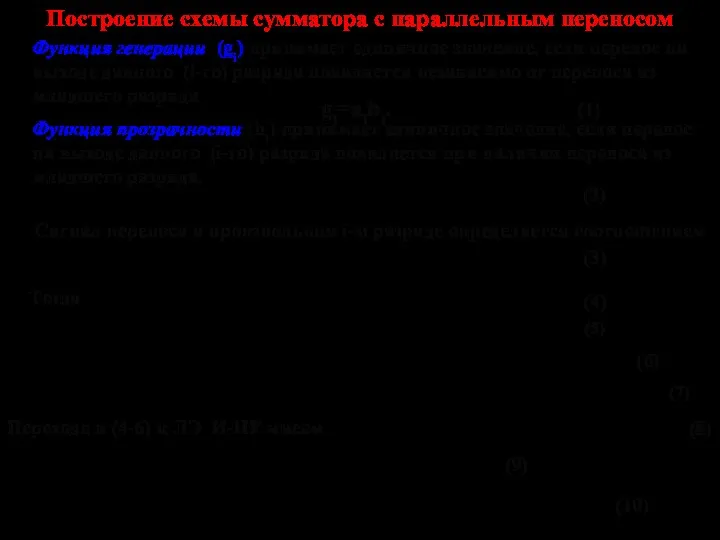

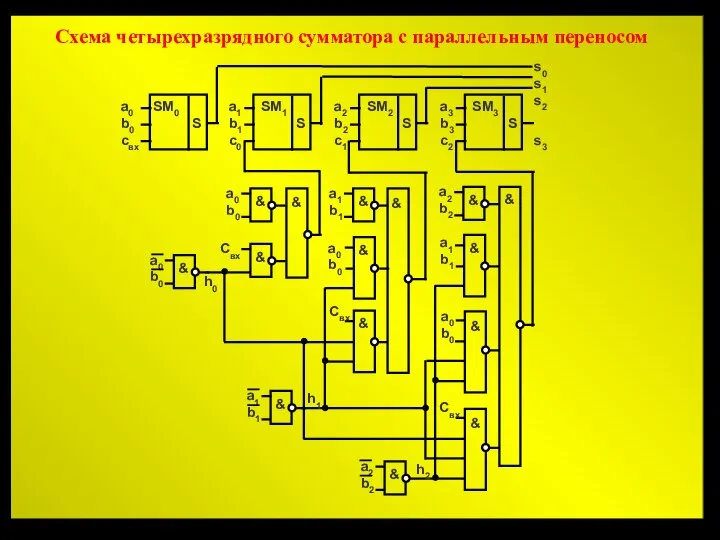

- 31. В сумматорах с параллельным переносом во всех разрядах рез-ты суммирования выраб. одновременно с помощью специальных схем

- 32. Построение схемы сумматора с параллельным переносом

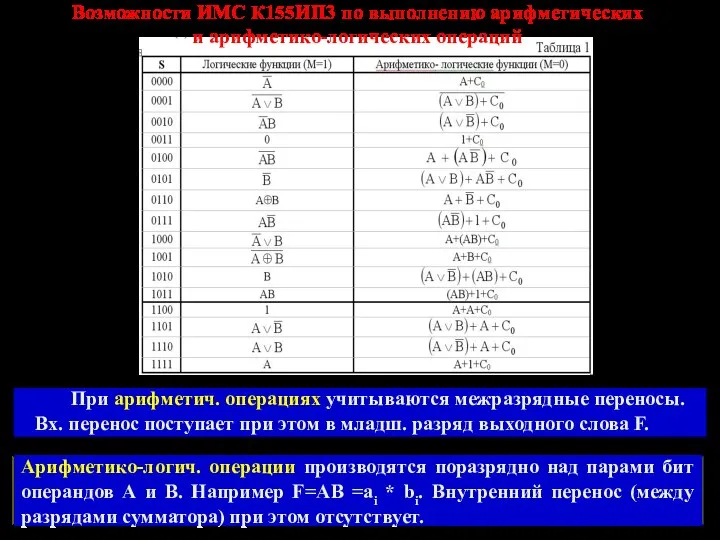

- 34. Арифметическо-логические устройства (АЛУ) Тип выполняемой операции: М=1- логические; М=0 – арифметико-логические Выход сравнения на равенство с

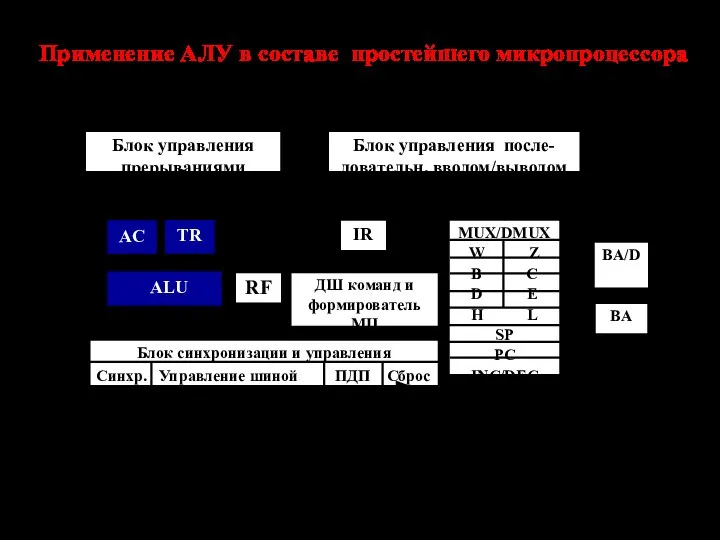

- 36. Применение АЛУ в составе простейшего микропроцессора ALU 8 Блок управления прерываниями Блок управления после-довательн. вводом/выводом INTR

- 37. Выводы по вопросу Сумматоры служат для арифметического сложения двоичных чисел. Многоразрядные сумматоры строятся на основе одноразрядных.

- 38. 4. Схемы контроля четности

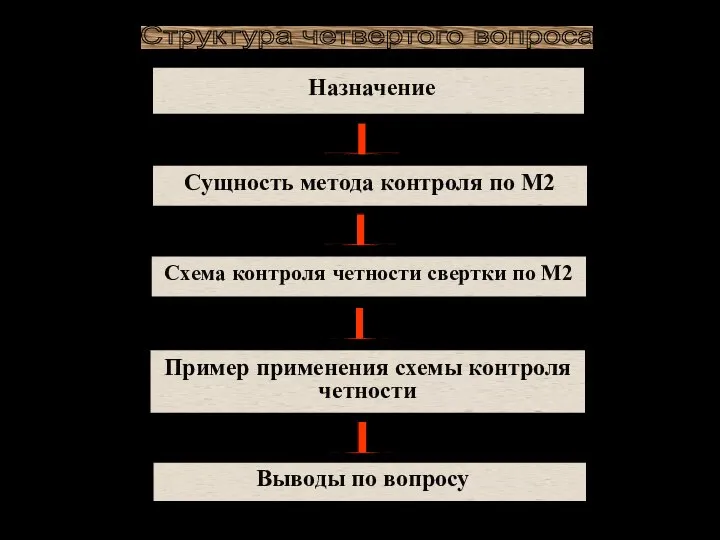

- 39. Структура четвертого вопроса

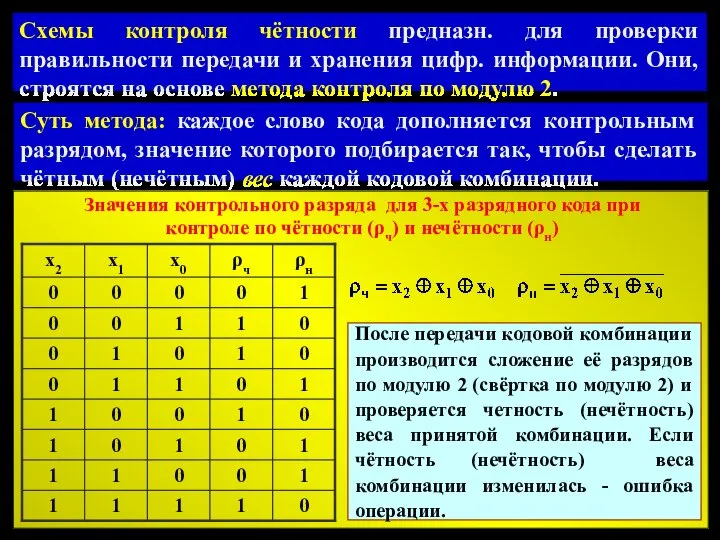

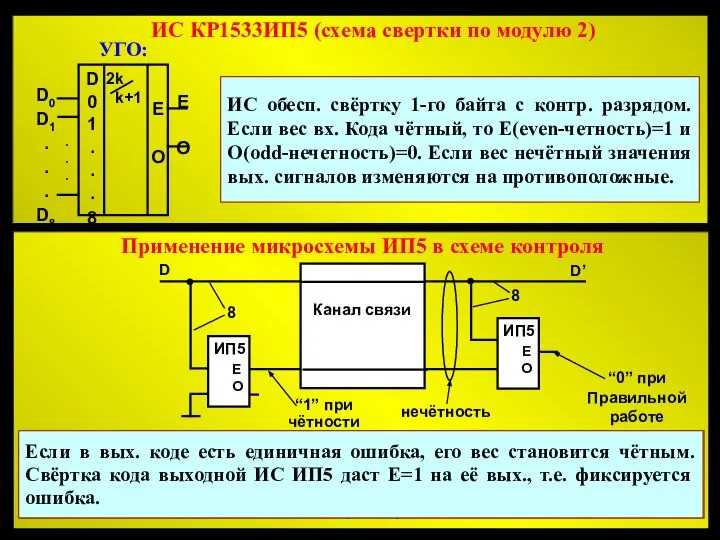

- 40. Схемы контроля чётности предназн. для проверки правильности передачи и хранения цифр. информации. Они, строятся на основе

- 41. ИС обесп. свёртку 1-го байта с контр. разрядом. Если вес вх. Кода чётный, то Е(еven-четность)=1 и

- 42. 5. Методы расчета типовых комбинационных цифровых устройств

- 43. Структура пятого вопроса

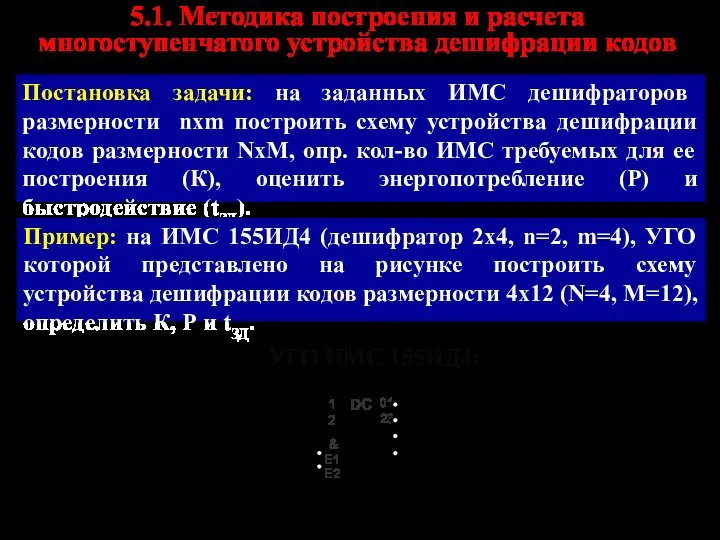

- 44. 5.1. Методика построения и расчета многоступенчатого устройства дешифрации кодов Постановка задачи: на заданных ИМС дешифраторов размерности

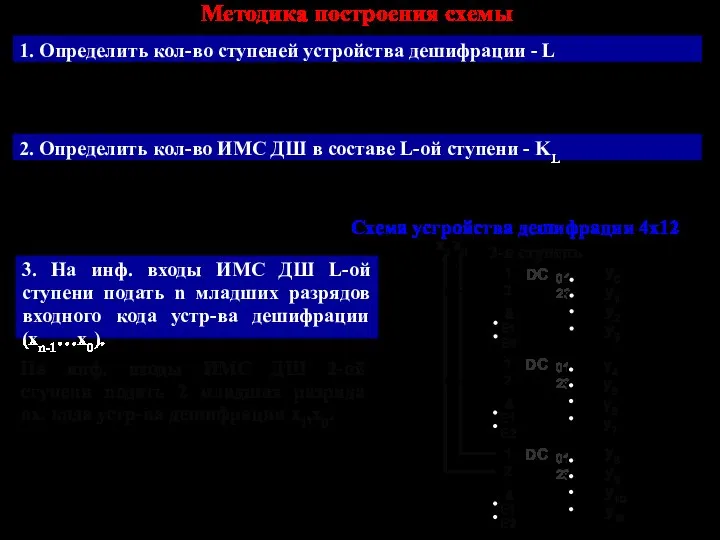

- 45. Методика построения схемы Схема устройства дешифрации 4х12 2-я ступень 3. На инф. входы ИМС ДШ L-ой

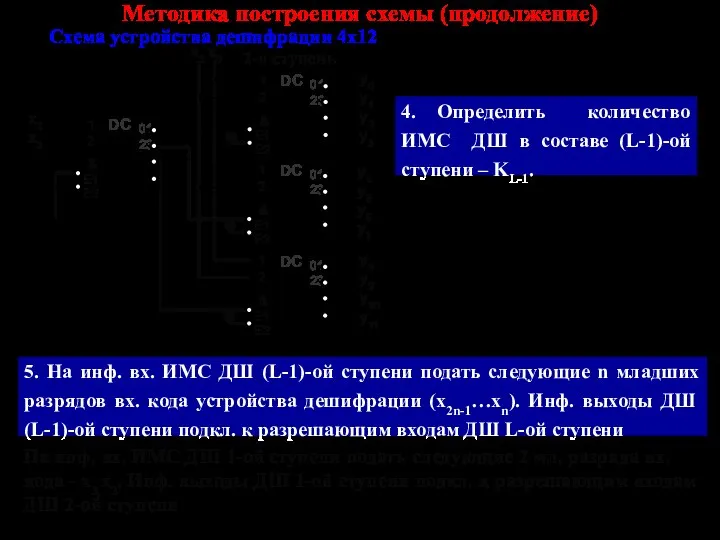

- 46. Методика построения схемы (продолжение) 5. На инф. вх. ИМС ДШ (L-1)-ой ступени подать следующие n младших

- 47. 6. Если КL-1=1 схема построена. При КL-1 более 1 п.4…6 повторяются для (L-2)-ой и т.д. ступеней

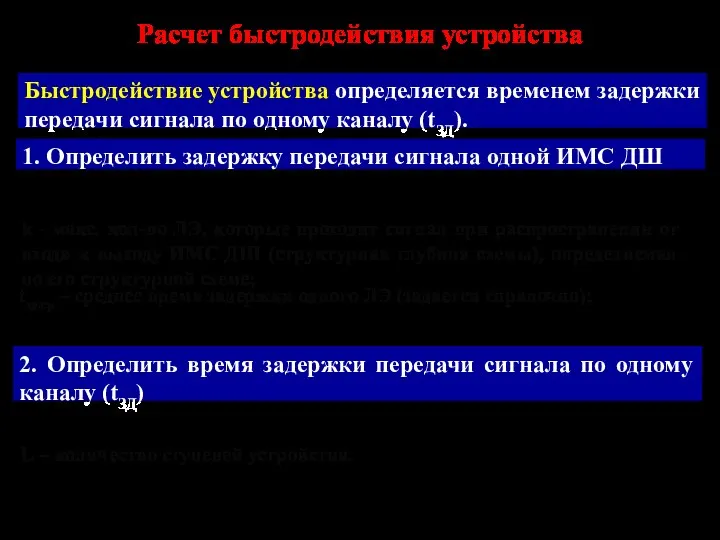

- 48. Расчет быстродействия устройства Быстродействие устройства определяется временем задержки передачи сигнала по одному каналу (tЗД). 1. Определить

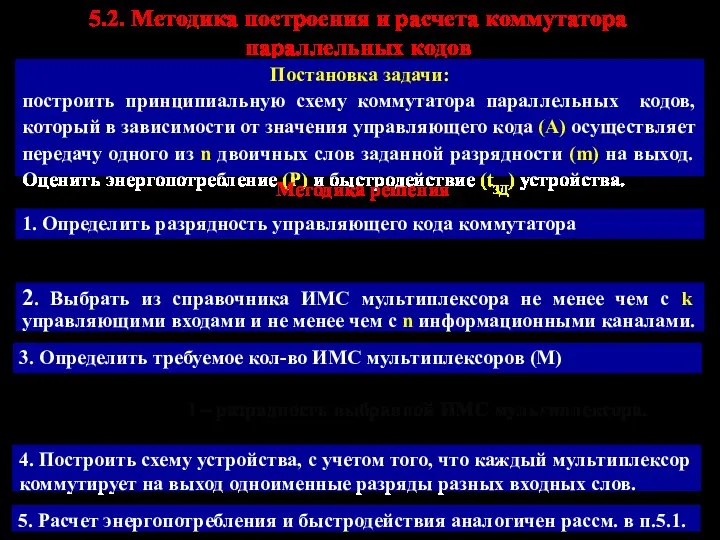

- 49. 5.2. Методика построения и расчета коммутатора параллельных кодов Постановка задачи: построить принципиальную схему коммутатора параллельных кодов,

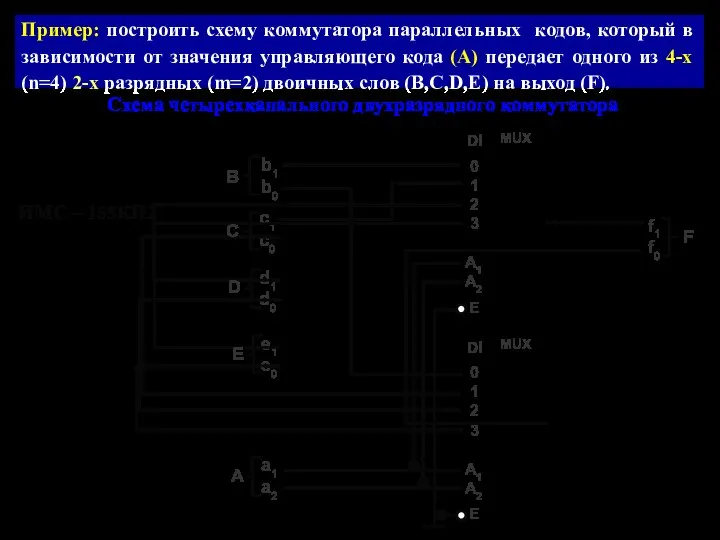

- 50. Пример: построить схему коммутатора параллельных кодов, который в зависимости от значения управляющего кода (А) передает одного

- 52. Скачать презентацию

![Цифровые устройства и микропроцессоры [Электронный ресурс]: Учебное пособие / Е. Н.](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/681560/slide-7.jpg)

Разработка и оценка эффективности работы интернет магазина ООО Икеа Дом

Разработка и оценка эффективности работы интернет магазина ООО Икеа Дом Особенности проведения изотопного анализа спектральными методами

Особенности проведения изотопного анализа спектральными методами Кара Нина 24 группа

Кара Нина 24 группа Рисунок

Рисунок Повышение эффективности функционирования логистической системы предприятия (по материалам ООО Аква Юг)

Повышение эффективности функционирования логистической системы предприятия (по материалам ООО Аква Юг) Демонстрація сили тиску атмосферного повітря

Демонстрація сили тиску атмосферного повітря Русский христианский социализм

Русский христианский социализм 20140924_pyat_shansov

20140924_pyat_shansov Конкурс

Конкурс Осенняя аппликация из пластилина

Осенняя аппликация из пластилина Б История Баскетбола

Б История Баскетбола Василь Стус

Василь Стус Круглый год

Круглый год Бандитские татуировки Выполнила студентка 515 группы Киселёва Ольга

Бандитские татуировки Выполнила студентка 515 группы Киселёва Ольга Курсовая работа Общественное здание в Красоярске

Курсовая работа Общественное здание в Красоярске Флортайм 2022 на конференцию

Флортайм 2022 на конференцию фотоотчет

фотоотчет Подготовка к визиту на предприятие_Сбор информации и составление сценария переговоров

Подготовка к визиту на предприятие_Сбор информации и составление сценария переговоров 20140301_muzyka_v_khrame

20140301_muzyka_v_khrame Личная история

Личная история С Днем 8 Марта!

С Днем 8 Марта! Частотно-временная область ЦИТ

Частотно-временная область ЦИТ Реклама без обратной связи

Реклама без обратной связи Рулетка одежда

Рулетка одежда Изображение диких животных. Белка

Изображение диких животных. Белка ОАО Газпром нефть

ОАО Газпром нефть Электротехника и электроника. Интегрирующие и дифференцирующие электрические цепи

Электротехника и электроника. Интегрирующие и дифференцирующие электрические цепи Кредит

Кредит