Содержание

- 2. План лекции 1.Адресное пространство МПС 2. Методы дешифрации адресов. 3. Схемы адресных дешифраторов 4.Использование ПЗУ в

- 3. Адресное пространство МПС Адресное пространство представляет собой упорядоченное множество кодов 0, 1, 2,., (2*n—1); где n—число

- 6. Адресное пространство определяет число возможных отличимых друг от друга кодовых комбинаций (адресов), которые может выдать на

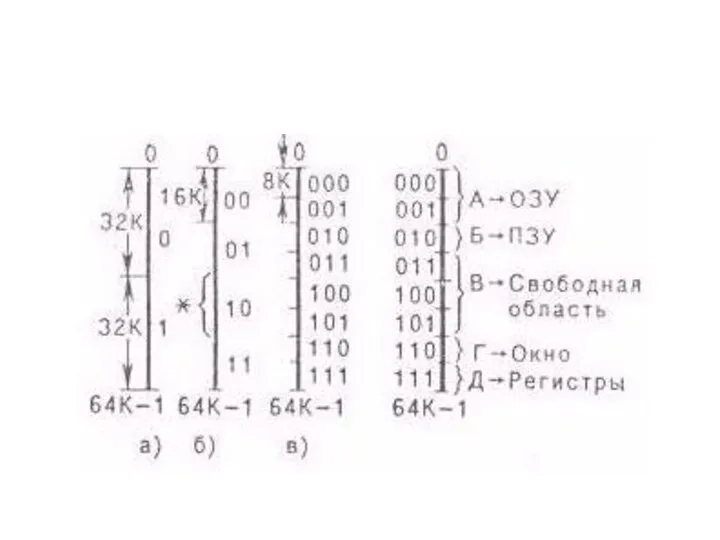

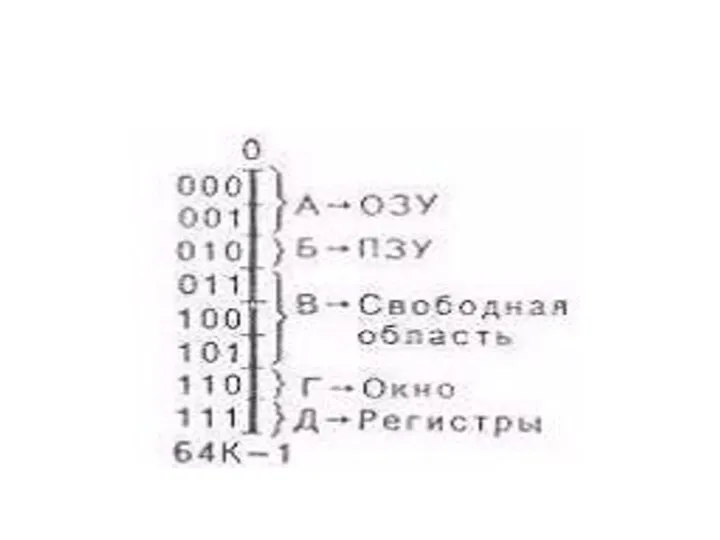

- 7. Понятие адресного пространства позволяет наглядно представлять размещение в нем различных программно-доступных объектов.

- 9. А- зона 16К (0000-3FFF), отведенная для адресов ОЗУ; Б- зона 8К (4000-5FFF) отведенная для адресов ПЗУ;

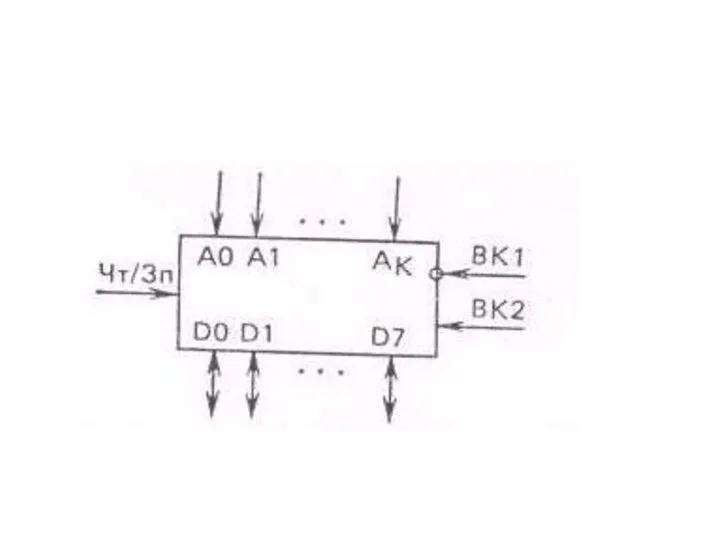

- 10. Методы дешифрации адресов. Принцип полной дешифрации Для решения задачи подключения триггера нужно, во-первых, определить, его «положение»

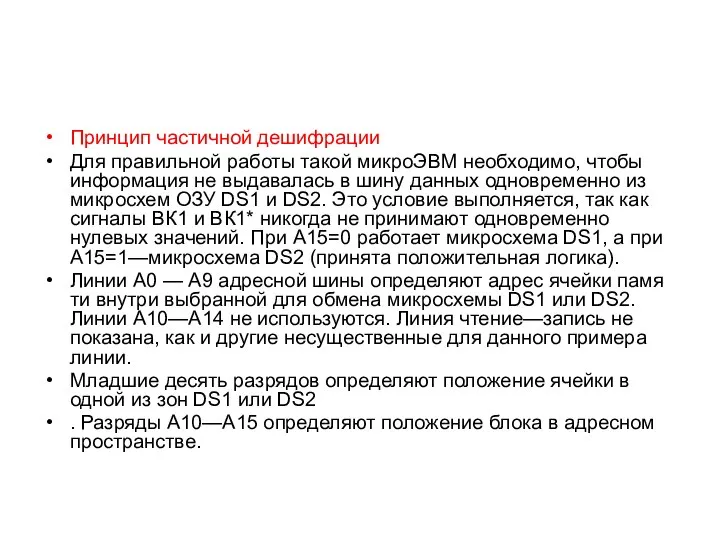

- 12. Принцип частичной дешифрации Для правильной работы такой микроЭВМ необходимо, чтобы информация не выдавалась в шину данных

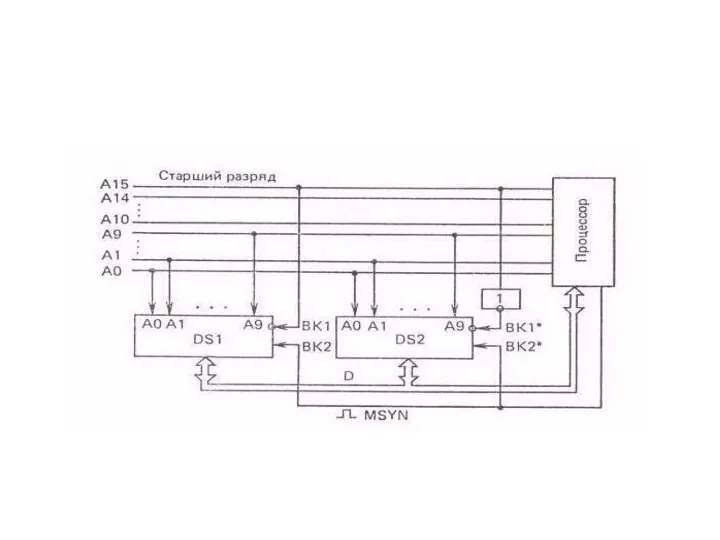

- 16. Если адресная шина содержит : три сигнальные линии, то по ней можно передать 2*3= 8 различных

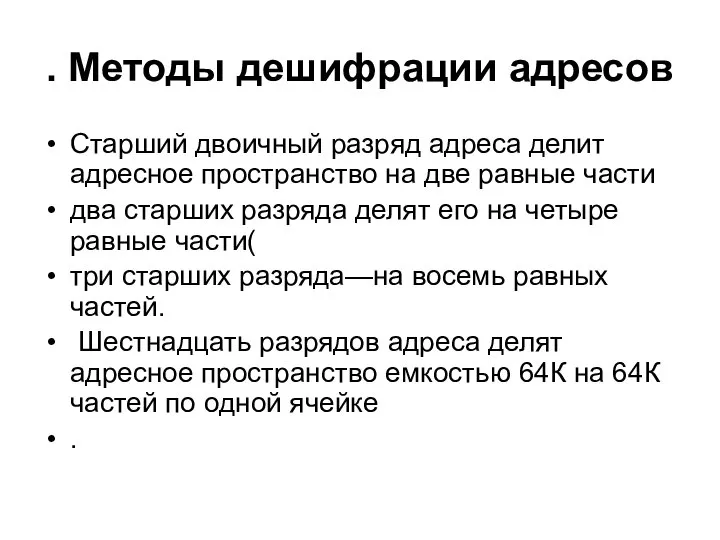

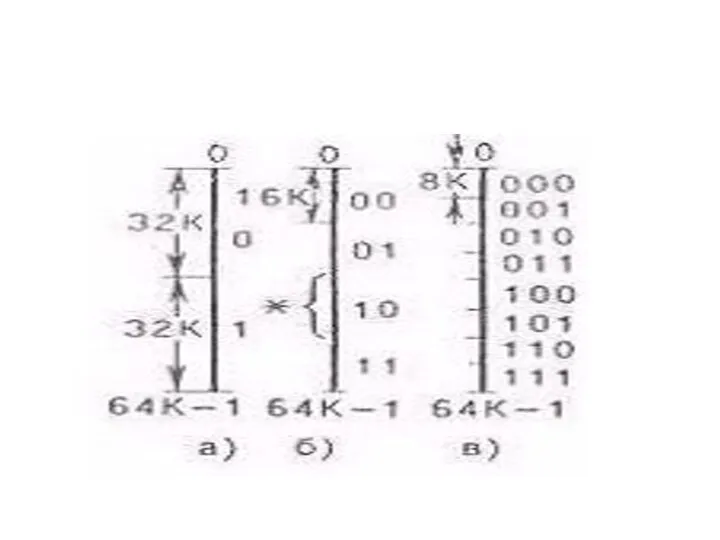

- 17. . Методы дешифрации адресов Старший двоичный разряд адреса делит адресное пространство на две равные части два

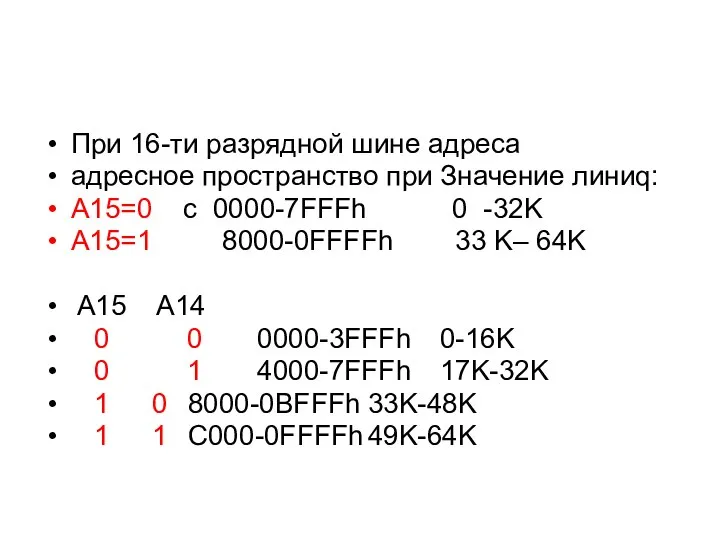

- 19. При 16-ти разрядной шине адреса адресное пространство при Значение линиq: А15=0 с 0000-7FFFh 0 -32K A15=1

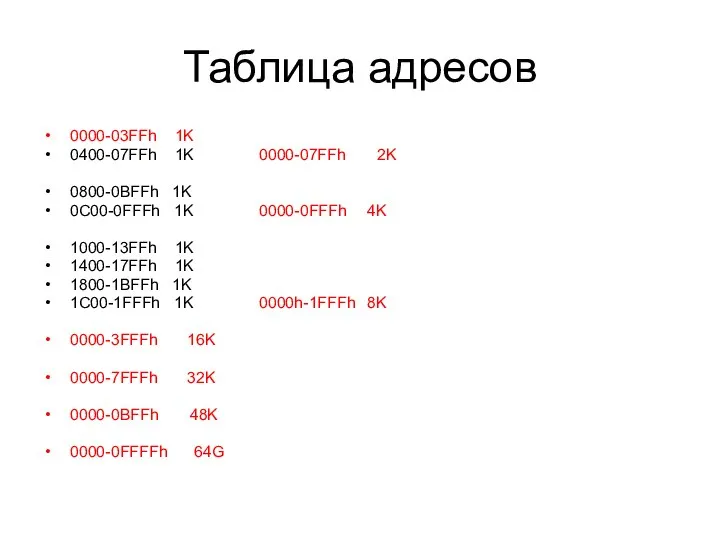

- 20. Таблица адресов 0000-03FFh 1K 0400-07FFh 1K 0000-07FFh 2K 0800-0BFFh 1K 0C00-0FFFh 1K 0000-0FFFh 4K 1000-13FFh 1K

- 21. Схемы адресных дешифраторов

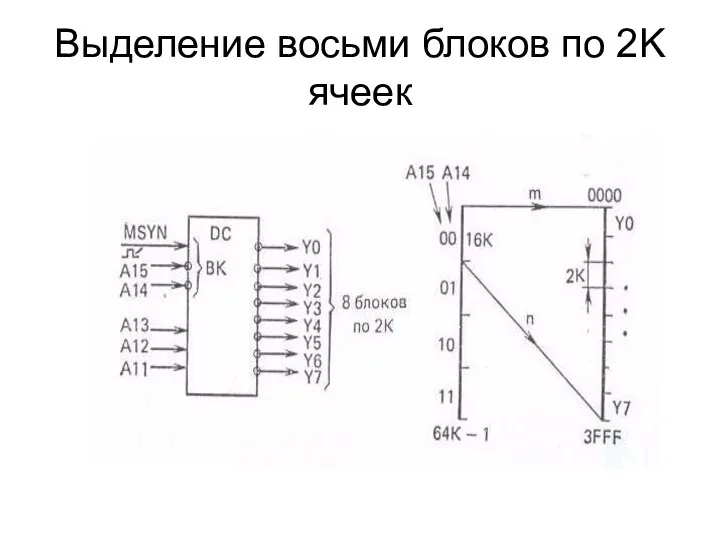

- 22. Выделение восьми блоков по 2K ячеек

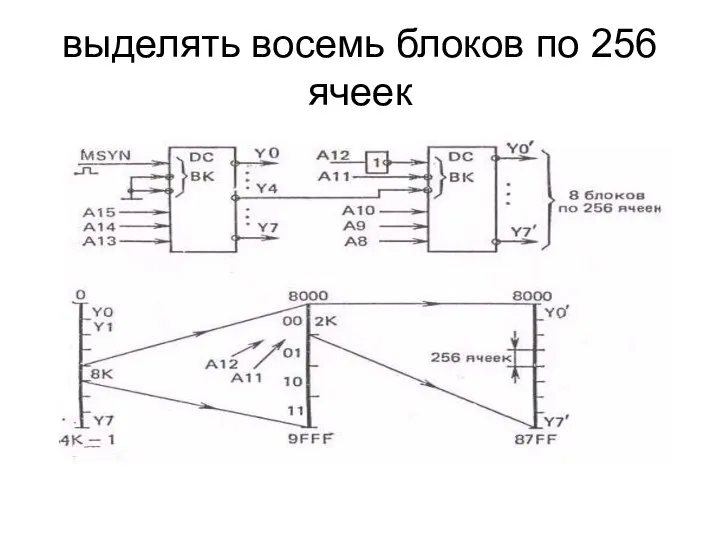

- 23. выделять восемь блоков по 256 ячеек

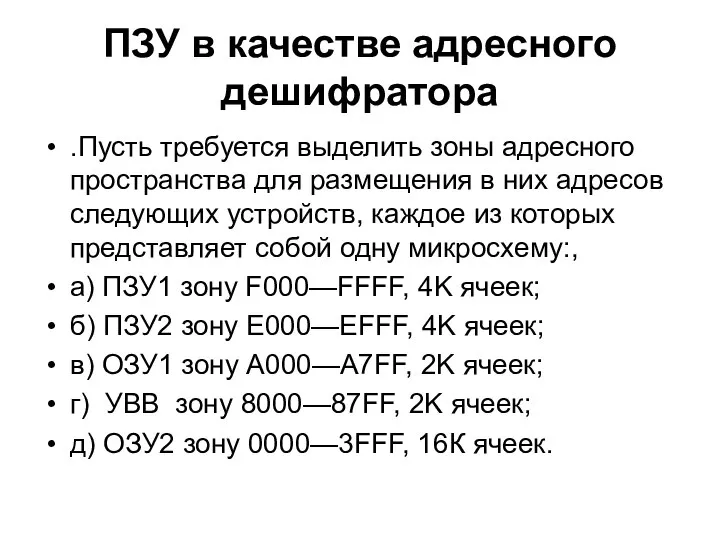

- 24. ПЗУ в качестве адресного дешифратора .Пусть требуется выделить зоны адресного пространства для размещения в них адресов

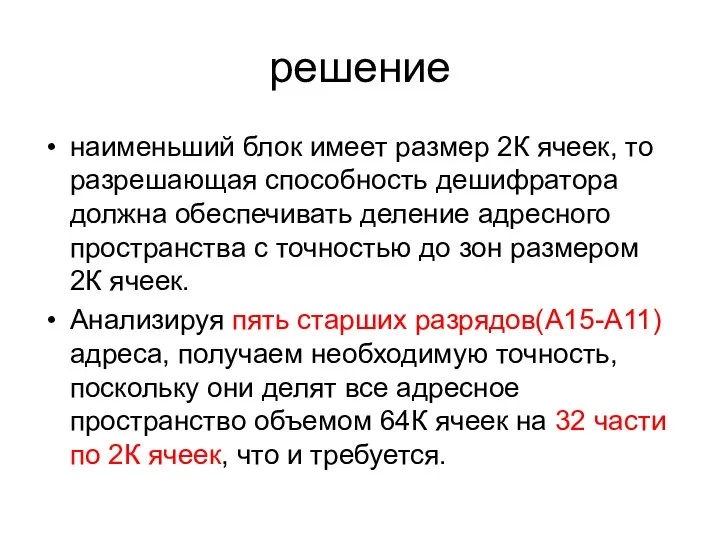

- 25. решение наименьший блок имеет размер 2К ячеек, то разрешающая способность дешифратора должна обеспечивать деление адресного пространства

- 26. дешифратор Выбираем за основу ПЗУ с пятью адресными входами, имеющее структуру 32х8 бит Выходы А—Д этого

- 27. . Микросхема ПЗУ

- 29. Скачать презентацию

Западная школа геополитики

Западная школа геополитики Методы управления рисками. Метод компенсации рисков Выполнили: Минниахметова М., Сочнева а., Чуева в., Шипилова д.

Методы управления рисками. Метод компенсации рисков Выполнили: Минниахметова М., Сочнева а., Чуева в., Шипилова д. Государственные образования на белорусских землях в IX-XVII веках

Государственные образования на белорусских землях в IX-XVII веках Презентация на тему "Гигиена Зрения. Нарушения зрения у детей и их профилактика" - скачать презентации по Медицине

Презентация на тему "Гигиена Зрения. Нарушения зрения у детей и их профилактика" - скачать презентации по Медицине Филимоновская игрушка (для старших дошкольников)

Филимоновская игрушка (для старших дошкольников) Упражнения для ног и ягодиц

Упражнения для ног и ягодиц НЕПРОВЕРЯЕМЫЕ БЕЗУДАРНЫЕ ГЛАСНЫЕ. учитель: Громова С.А. МСОШ № 2 имени Е.В.Камышева города Гагарина.

НЕПРОВЕРЯЕМЫЕ БЕЗУДАРНЫЕ ГЛАСНЫЕ. учитель: Громова С.А. МСОШ № 2 имени Е.В.Камышева города Гагарина. Национальная программа « Образование» Подготовил студент группы Т093 Котов Павел

Национальная программа « Образование» Подготовил студент группы Т093 Котов Павел 4. Java OOP. 5. Abstract Classes

4. Java OOP. 5. Abstract Classes Сущность качества

Сущность качества Неорганические строительные материалы Керамические материалы. Фарфор. Фаянс. Керамика.

Неорганические строительные материалы Керамические материалы. Фарфор. Фаянс. Керамика. Организация технического обслуживания и ремонта автомобиля УАЗ Патриот

Организация технического обслуживания и ремонта автомобиля УАЗ Патриот Международная безопасность. Политический реализм и неореализм. (Лекция 12)

Международная безопасность. Политический реализм и неореализм. (Лекция 12) Ұлттық салт-дәстүрлеріміз, тіліміз бен музыкамыз, әдебиетіміз, жоралғыларымыз

Ұлттық салт-дәстүрлеріміз, тіліміз бен музыкамыз, әдебиетіміз, жоралғыларымыз PubMed – медициналық ақпапарттық желісі 4- топша

PubMed – медициналық ақпапарттық желісі 4- топша Псалмы

Псалмы Кодекс профессиональной этики инженерии программного обеспечения

Кодекс профессиональной этики инженерии программного обеспечения Открытый урок во 2 «А» классе по русскому языку

Открытый урок во 2 «А» классе по русскому языку Проблема - её роль, в жизни подростка. «Главное для человека не то, что есть, а то, что хочется….» Работы выполнила педагог-ор

Проблема - её роль, в жизни подростка. «Главное для человека не то, что есть, а то, что хочется….» Работы выполнила педагог-ор Суперкомп’ютери. Основні типи комп'ютерів

Суперкомп’ютери. Основні типи комп'ютерів ГСИ. Методики выполнения измерений

ГСИ. Методики выполнения измерений Изменения в нормативной базе для НФО (4937-У, 5075-У, 5084-У, 32-ФЗ)

Изменения в нормативной базе для НФО (4937-У, 5075-У, 5084-У, 32-ФЗ) Общественные пространства - 2018

Общественные пространства - 2018 Методические основы занятий физической культурой и спортом

Методические основы занятий физической культурой и спортом Международный бизнес проект PROэкспрессКарьера

Международный бизнес проект PROэкспрессКарьера Пристрої цифрової обробки радіолокаційних сигналів (заняття № 2.5)

Пристрої цифрової обробки радіолокаційних сигналів (заняття № 2.5) Концепция развития Свердловского округа г. Иркутска

Концепция развития Свердловского округа г. Иркутска Тема 1. Роль и назначение международных стандартов финансовой отчётности в гармонизации системы бухгалтерского учёта 1. Основные

Тема 1. Роль и назначение международных стандартов финансовой отчётности в гармонизации системы бухгалтерского учёта 1. Основные