Содержание

- 2. В современных ЭВМ арифметико-логическое устройство не является самостоятельным схемотехническим блоком. Оно входит в состав микропроцессора, на

- 3. Арифметико-логические устройства АЛУ (ALU, Arithmetic-Logic Unit) выполняют над словами ряд действий. Основой АЛУ служит сумматор, схема

- 4. Арифметико-логические устройства Основными арифметическими операциями являются сложение и вычитание. Разработаны коды дополнительный и обратный, которые позволяют

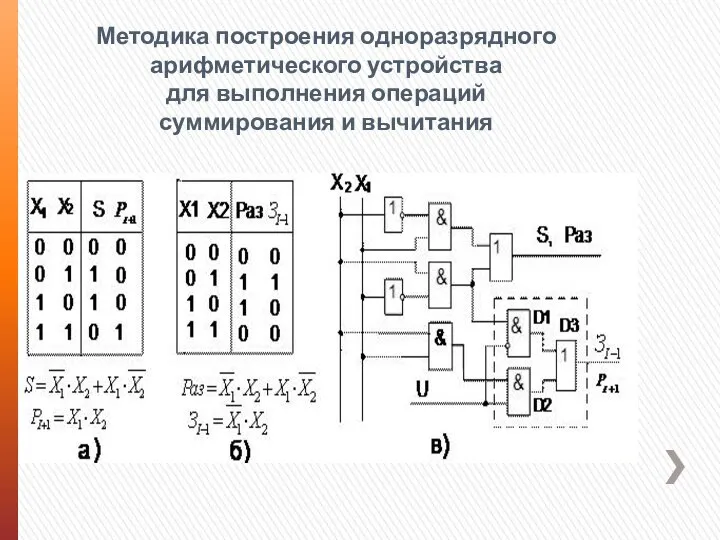

- 5. Методика построения одноразрядного арифметического устройства для выполнения операций суммирования и вычитания

- 6. Операция вычитания Для выполнения операции вычитания не требуется получение дополнительных сигналов, поэтому и не требуются дополнительные

- 7. Вычитание Вычитание числа В из А выполняется путем суммирования отрицательного числа В в дополнительном коде с

- 8. Многоразрядные АЛУ Многоразрядные АЛУ выпускаются в виде интегральных микросхем или входят в состав процессоров, являясь их

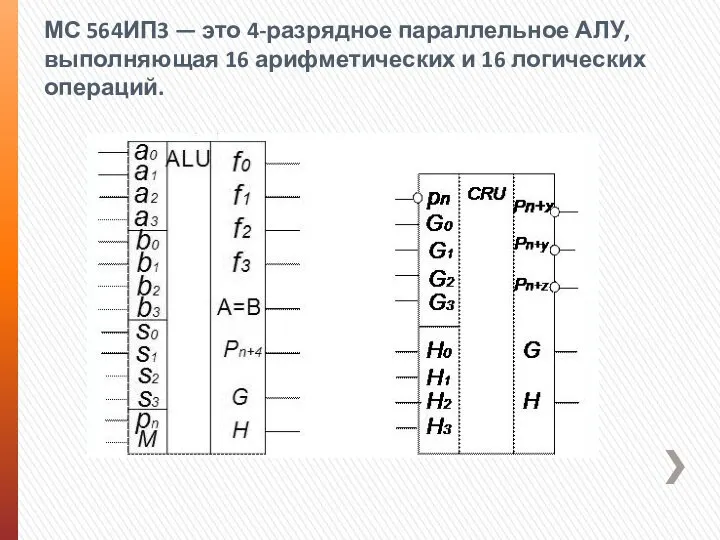

- 9. МС 564ИП3 — это 4-разрядное параллельное АЛУ, выполняющая 16 арифметических и 16 логических операций.

- 10. A(а0–а3) — первый операнд, B(b0–b3) — второй операнд, S(s0–s3) — код операции — 4 разряда. Если

- 11. Обычно АЛУ четырехразрядны и для наращивания разрядности объединяются с формированием последовательных или параллельных переносов. Логические возможности

- 12. АЛУ имеет входы операндов А и В, входы выбора операций S, вход переноса Ci и вход

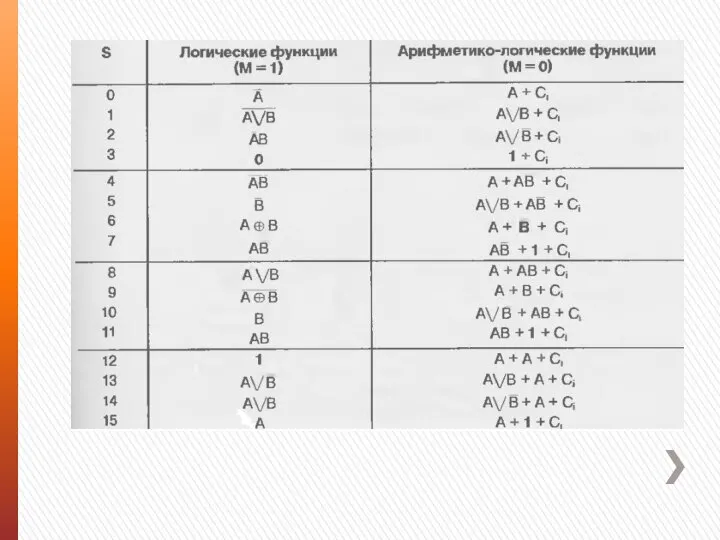

- 13. Перечень выполняемых АЛУ операций дан в табл. Для краткости двоичные числа s3s2s1s0 представлены их десятичными эквивалентами.

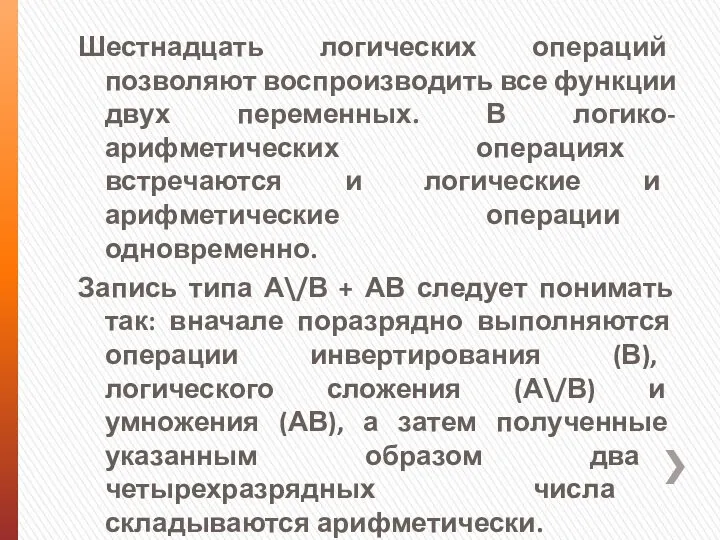

- 15. Шестнадцать логических операций позволяют воспроизводить все функции двух переменных. В логико-арифметических операциях встречаются и логические и

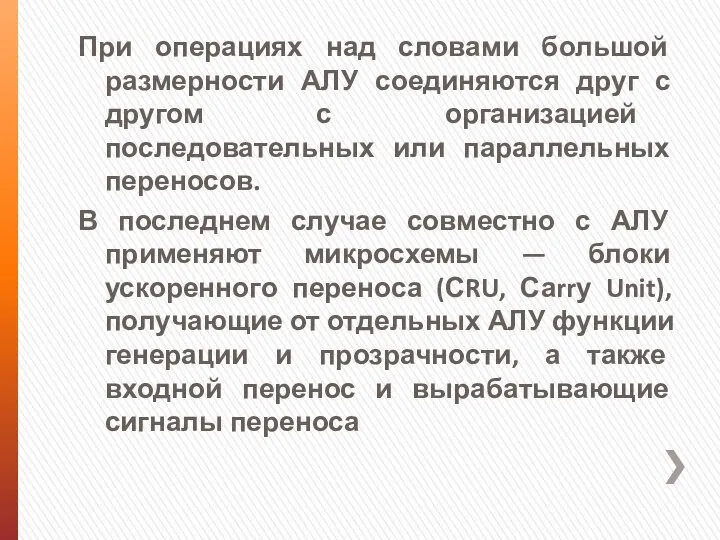

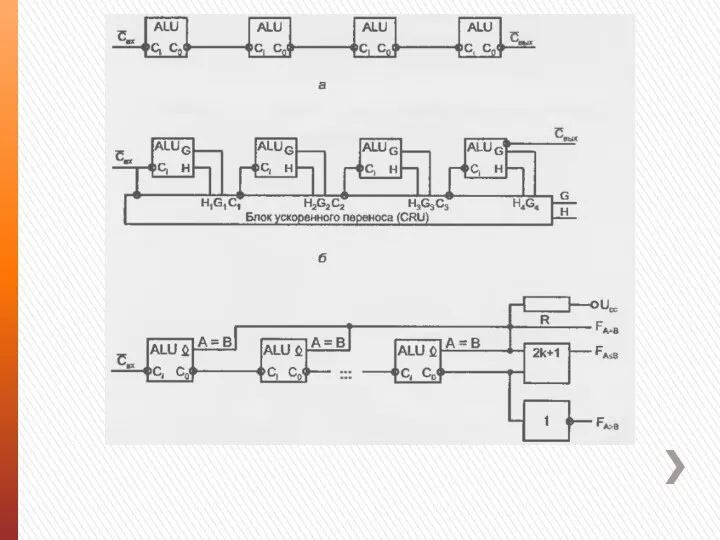

- 16. При операциях над словами большой размерности АЛУ соединяются друг с другом с организацией последовательных или параллельных

- 18. Классификация АЛУ По способу представления чисел различают АЛУ: - для чисел с фиксированной запятой; - для

- 19. Классификация АЛУ По способу действия над операндами АЛУ делятся на последовательные и параллельные.

- 20. Классификация АЛУ В параллельных АЛУ операнды представляются параллельным кодом и операции совершаются параллельно во времени над

- 21. Классификация АЛУ В последовательных АЛУ операнды представляются в последовательном коде, а операции производятся последовательно во времени

- 22. Классификация АЛУ По выполняемым функциям АЛУ делятся на многофункциональные и функциональные (блочные).

- 23. Классификация АЛУ В блочном АЛУ операции над числами с фиксированной и плавающей запятой, десятичными и алфавитно-цифровыми

- 24. Классификация АЛУ В многофункциональных АЛУ всевозможные операции для всех форм представления чисел выполняются одними и теми

- 25. Классификация АЛУ По структурной организации АЛУ можно разделить на устройства, имеющие: регистровую структуру с непосредственными связями

- 26. Классификация АЛУ магистральную структуру с сосредоточенной памятью и логикой. Магистральная структура АЛУ отличается тем, что в

- 27. Для лучшего понимания этих вопросов проведем синтез арифметического устройства, предназначенного для выполнения только одной операции –

- 28. Синтез АЛУ проходит в несколько этапов. Сначала необходимо выбрать метод, по которому предполагается выполнение операции, и

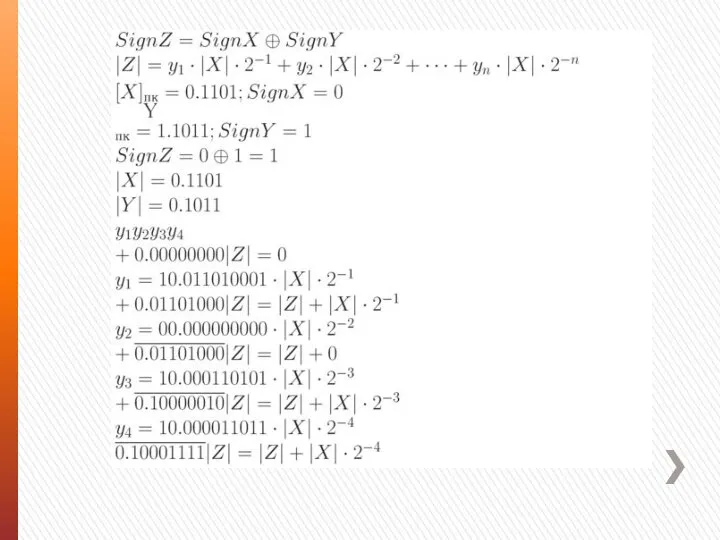

- 29. Пусть операнды имеют вид: [X]пк = x0x1x2…xn [Y]пк = y0y1y2…yn где x0, y0 – знаковые разряды.

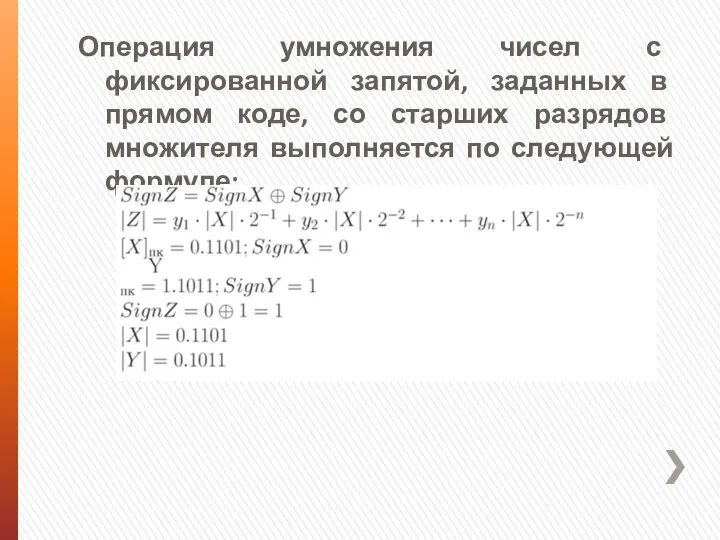

- 30. Операция умножения чисел с фиксированной запятой, заданных в прямом коде, со старших разрядов множителя выполняется по

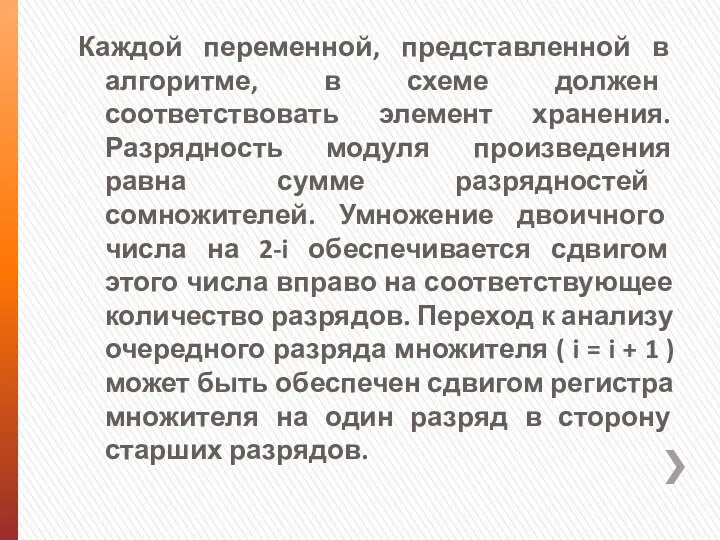

- 32. Каждой переменной, представленной в алгоритме, в схеме должен соответствовать элемент хранения. Разрядность модуля произведения равна сумме

- 34. Структурная схема устройства представлена на рис.

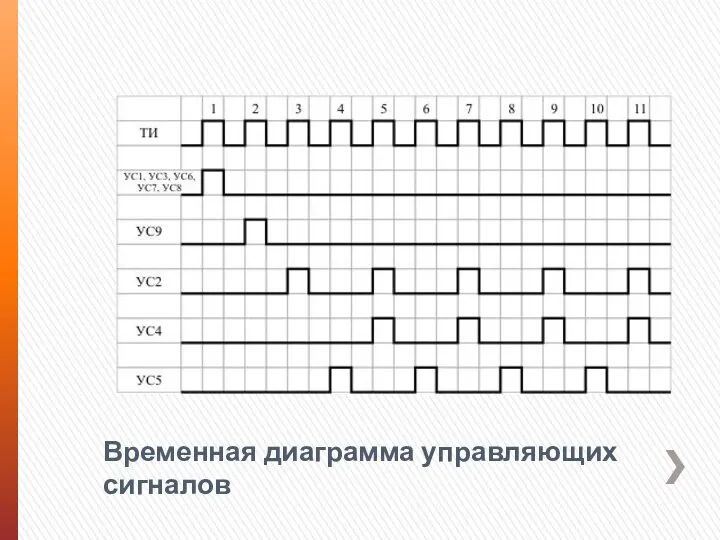

- 35. Временная диаграмма управляющих сигналов

- 37. Скачать презентацию

![Пусть операнды имеют вид: [X]пк = x0x1x2…xn [Y]пк = y0y1y2…yn где x0, y0 – знаковые разряды.](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1472194/slide-28.jpg)

СТОЛБНЯК (Tetanus) (А35)

СТОЛБНЯК (Tetanus) (А35)  Технология OAuth

Технология OAuth Презентация на тему "Типология уроков деятельностной направленности" - скачать презентации по Педагогике

Презентация на тему "Типология уроков деятельностной направленности" - скачать презентации по Педагогике Футбольная грамота. Победная тактика

Футбольная грамота. Победная тактика Искусство и духовная жизнь 10 класс. Обществознание.

Искусство и духовная жизнь 10 класс. Обществознание. Сущность и структура политического процесса. (Лекция 4)

Сущность и структура политического процесса. (Лекция 4) Презентация «ПЕРЕВОЗКА»

Презентация «ПЕРЕВОЗКА» Учитель или компьютер? Выполнили ученики 11 «б» класса COШ №9 Мартиросян Диана, Кузив Евгения Города Елизово Под руководством Во

Учитель или компьютер? Выполнили ученики 11 «б» класса COШ №9 Мартиросян Диана, Кузив Евгения Города Елизово Под руководством Во НЕТРАДИЦИОННАЯ ТЕХНИКА РИСОВАНИЯ Монотипия

НЕТРАДИЦИОННАЯ ТЕХНИКА РИСОВАНИЯ Монотипия Рэлігія – вера чалавека ў звышнатуральныя сілы

Рэлігія – вера чалавека ў звышнатуральныя сілы Новый год в различных странах

Новый год в различных странах SCSI - системный интерфейс для малых компьютеров

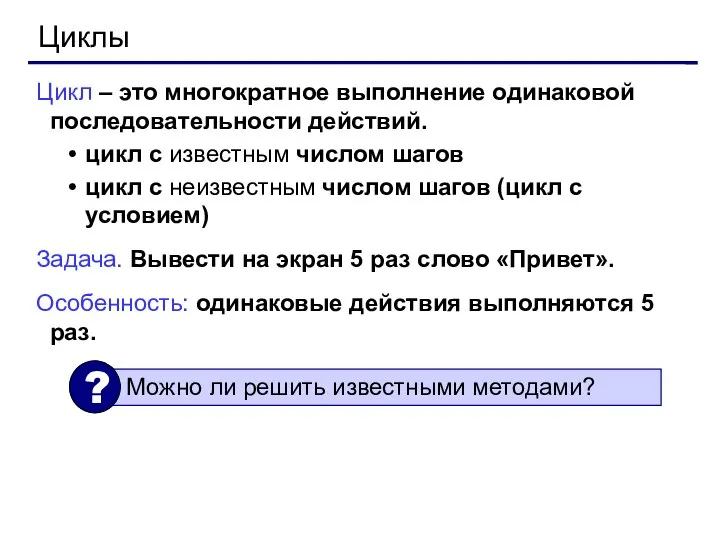

SCSI - системный интерфейс для малых компьютеров Цикл со счетчиком

Цикл со счетчиком Подготовка к КР по теме «Мой класс»

Подготовка к КР по теме «Мой класс» Конкурентоспособность ЮАР

Конкурентоспособность ЮАР Числівник. Особливості відмінювання та правопису

Числівник. Особливості відмінювання та правопису Поэтика ОБЭРИУтов

Поэтика ОБЭРИУтов TCP

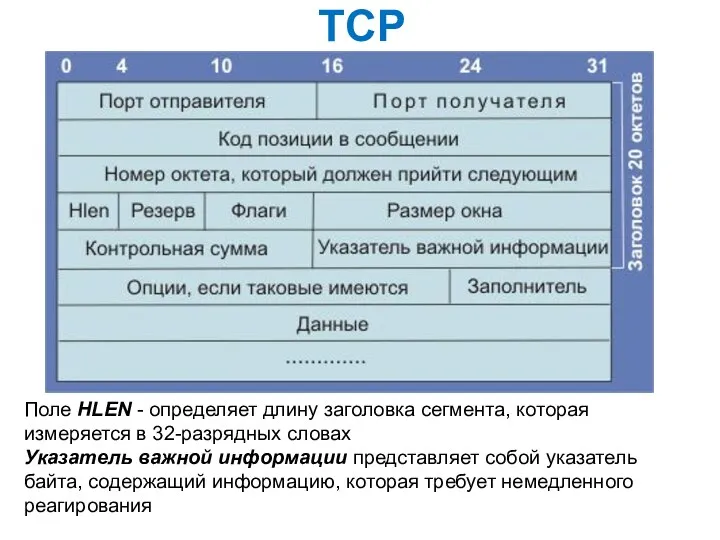

TCP Мойдодыр - презентация для начальной школы

Мойдодыр - презентация для начальной школы Русь, Россия, Родина моя! Виды, государственные символы России

Русь, Россия, Родина моя! Виды, государственные символы России Счетчики с произвольным порядком счета. Лекция 5

Счетчики с произвольным порядком счета. Лекция 5 Сергей Петрович Тарасов - советский и российский биатлонист

Сергей Петрович Тарасов - советский и российский биатлонист Скелет – надежный каркас 8 класс

Скелет – надежный каркас 8 класс  Народный костюм

Народный костюм Оптимальная компьютерная учебно-методическая среда в учебно-воспитательном процессе Заседание педсовета МОУ СОШ №1 г. Ессенту

Оптимальная компьютерная учебно-методическая среда в учебно-воспитательном процессе Заседание педсовета МОУ СОШ №1 г. Ессенту Факультативный курс для старшеклассников «Применение производной в решении задач школьного курса математики» Выполнила: студен

Факультативный курс для старшеклассников «Применение производной в решении задач школьного курса математики» Выполнила: студен ВЫПУСКНАЯ КВАЛИФИКАЦИОННАЯ РАБОТА на высшую категорию Активизация мыслительной деятельности младших подростков средствами г

ВЫПУСКНАЯ КВАЛИФИКАЦИОННАЯ РАБОТА на высшую категорию Активизация мыслительной деятельности младших подростков средствами г Внеклассная работа по физическому воспитанию учащихся в школе. (Лекция 14)

Внеклассная работа по физическому воспитанию учащихся в школе. (Лекция 14)