Содержание

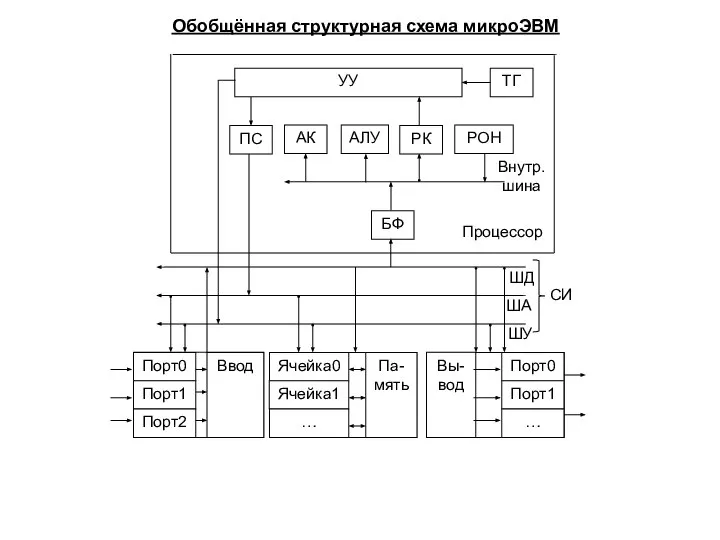

- 2. Обобщённая структурная схема микроЭВМ БФ АК АЛУ РОН УУ ТГ Вы-вод Внутр. шина РК ПС СИ

- 3. Алгоритм функционирования ЭВМ Алгоритм отражает выполнение команд от момента включения до момента выключения. 1. Инициализация ЭВМ.

- 4. Процессор предназначен для обработки данных и управления режимами работы ЭВМ. Память предназначена для хранения программы и

- 5. Процессор (П) УУ (устройство управления) предназначено для управления П и ЭВМ в целом. Исходной информацией для

- 6. Выполнение команды в микроЭВМ Выполнения любой команды начинается с загрузки команды. Для загрузки команды процессор устанавливает

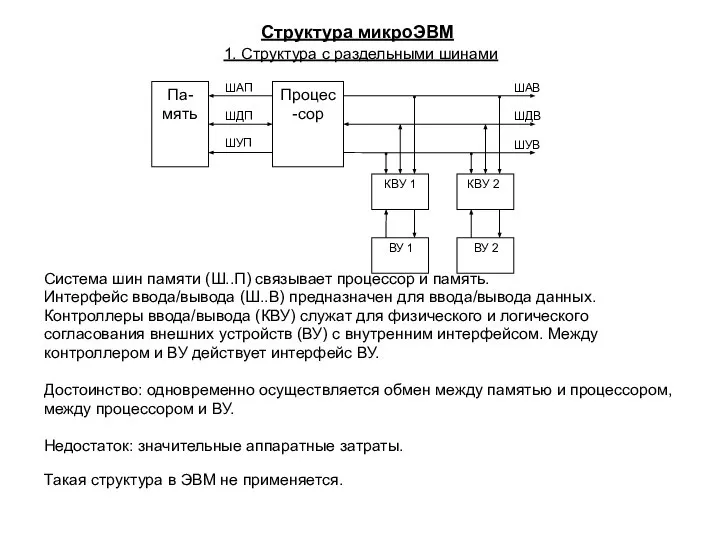

- 7. Структура микроЭВМ 1. Структура с раздельными шинами Система шин памяти (Ш..П) связывает процессор и память. Интерфейс

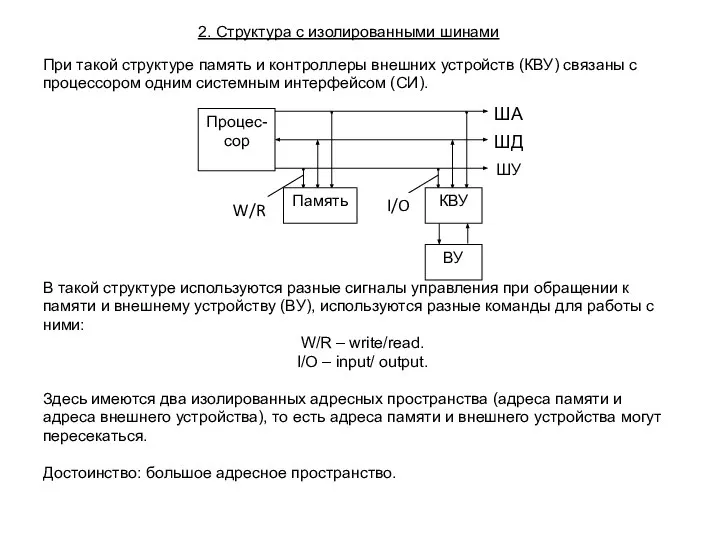

- 8. 2. Структура с изолированными шинами При такой структуре память и контроллеры внешних устройств (КВУ) связаны с

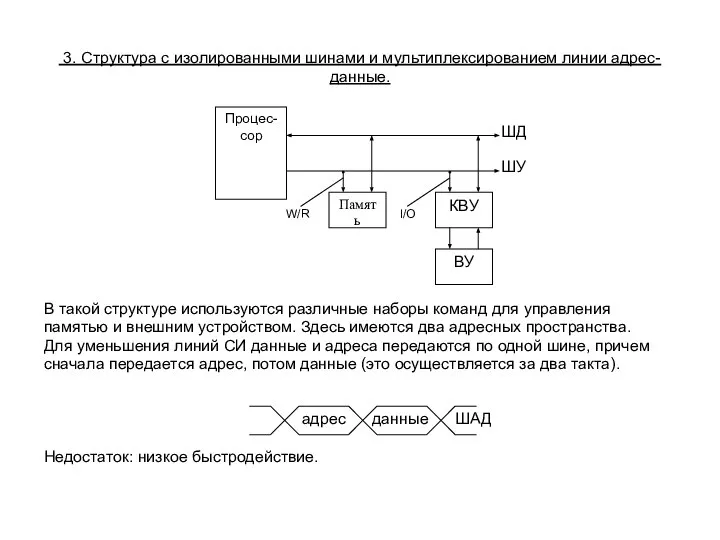

- 9. 3. Структура с изолированными шинами и мультиплексированием линии адрес-данные. В такой структуре используются различные наборы команд

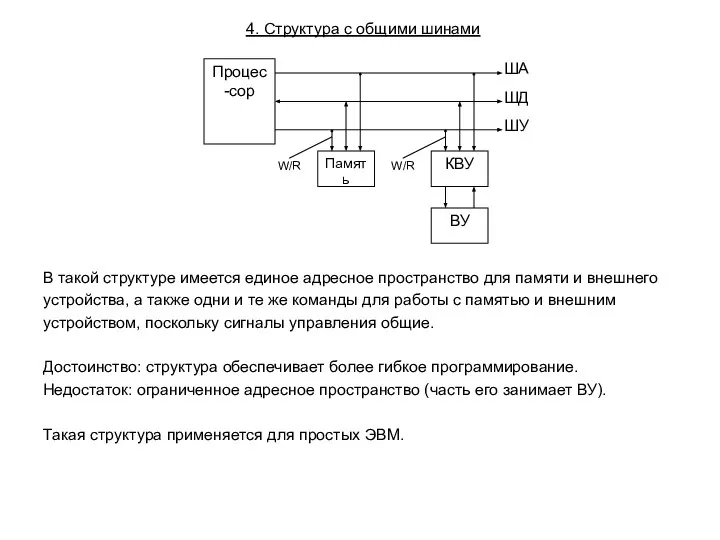

- 10. 4. Структура с общими шинами В такой структуре имеется единое адресное пространство для памяти и внешнего

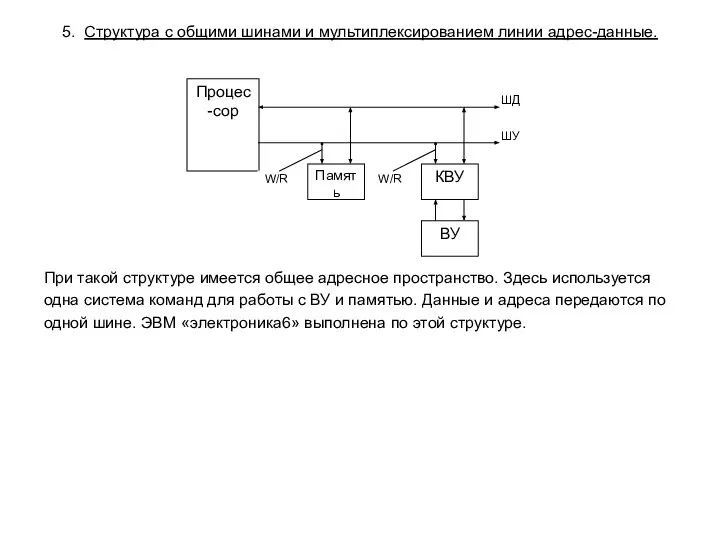

- 11. 5. Структура с общими шинами и мультиплексированием линии адрес-данные. При такой структуре имеется общее адресное пространство.

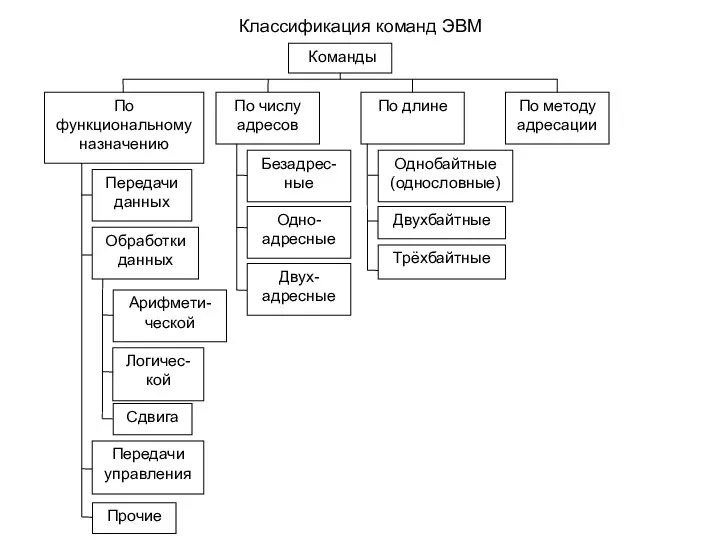

- 12. Классификация команд ЭВМ

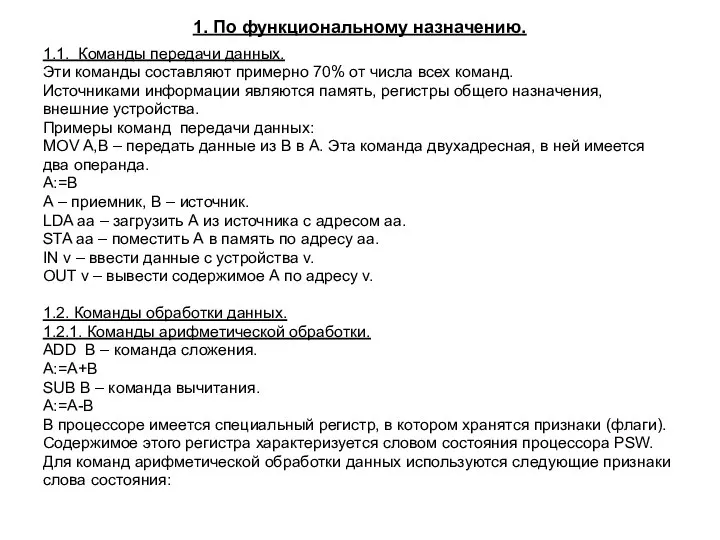

- 13. 1. По функциональному назначению. 1.1. Команды передачи данных. Эти команды составляют примерно 70% от числа всех

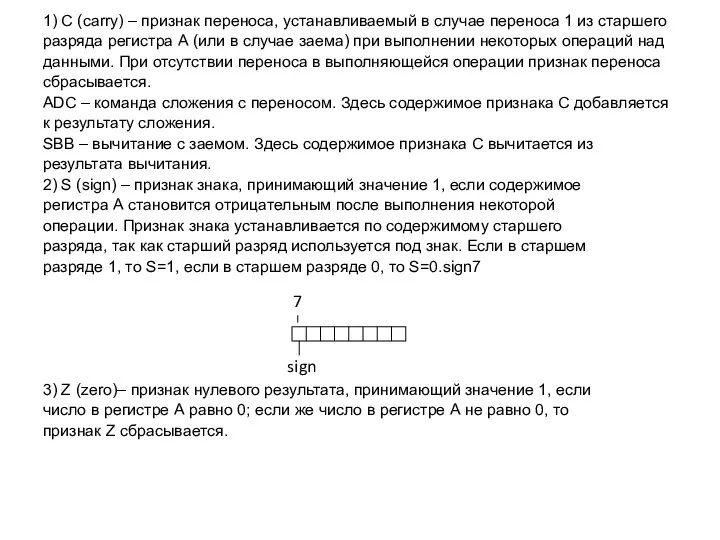

- 14. 1) C (carry) – признак переноса, устанавливаемый в случае переноса 1 из старшего разряда регистра А

- 15. 1.2.2. Команды логической обработки данных. ANA B – содержимое регистра В подвергается логическому И с содержимым

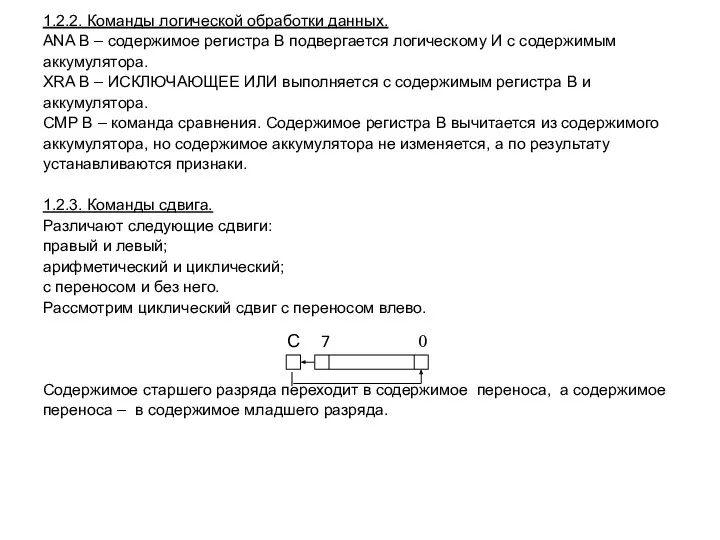

- 16. 1.3. Команды передачи управления. Команды передачи управления бывают условные и безусловные. Условные команды используют признаки слова

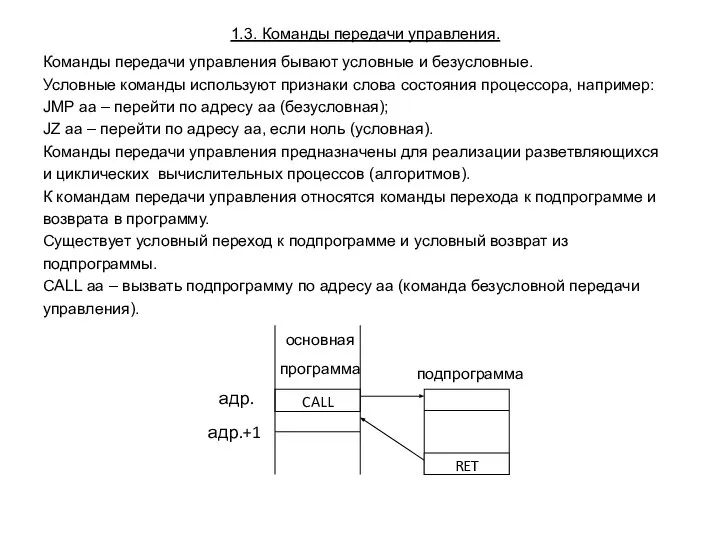

- 17. Для сохранения адреса возврата служит стек. Стек – это область оперативной памяти, доступ к которой организован

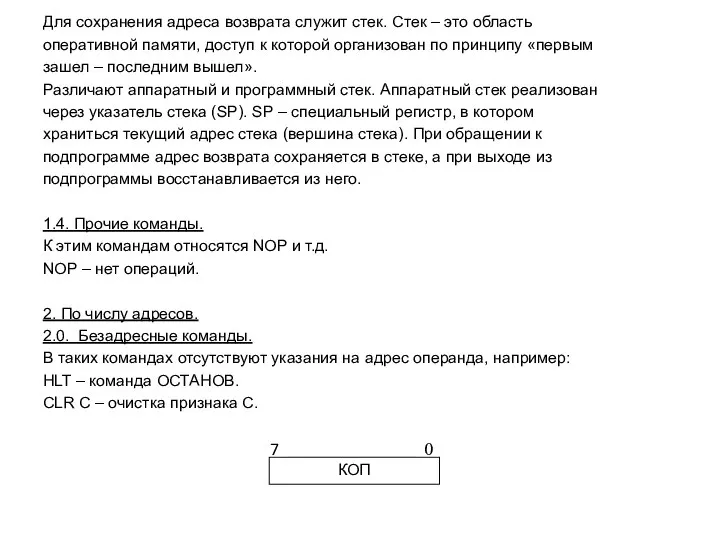

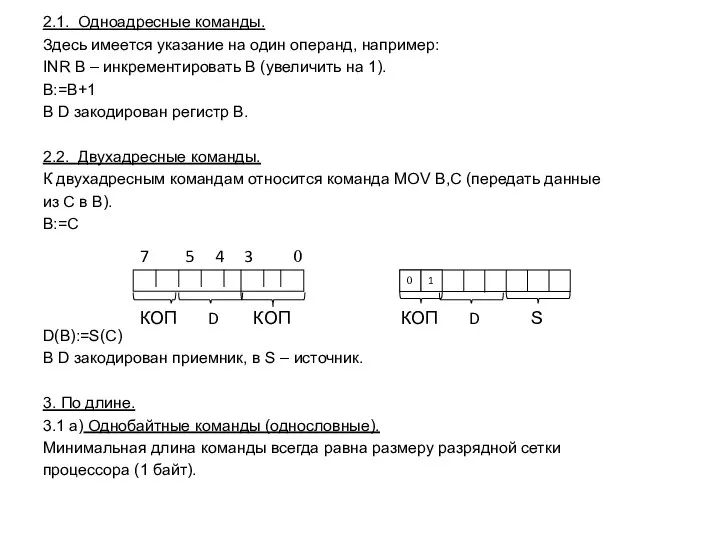

- 18. 2.1. Одноадресные команды. Здесь имеется указание на один операнд, например: INR B – инкрементировать В (увеличить

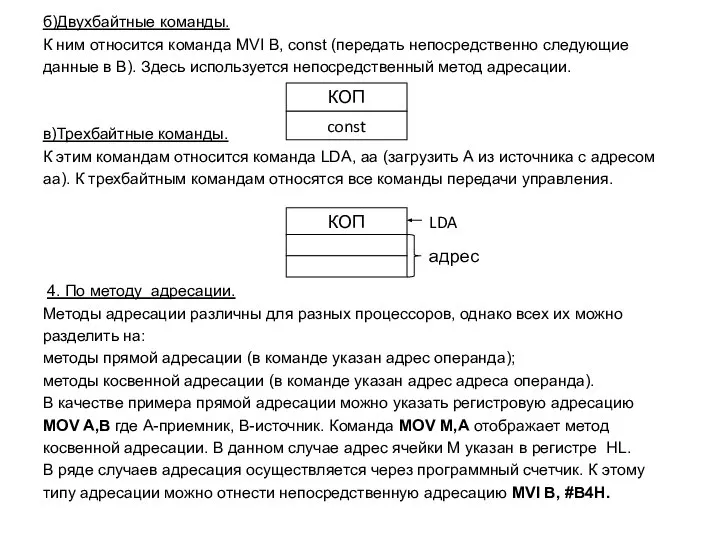

- 19. б)Двухбайтные команды. К ним относится команда MVI B, const (передать непосредственно следующие данные в В). Здесь

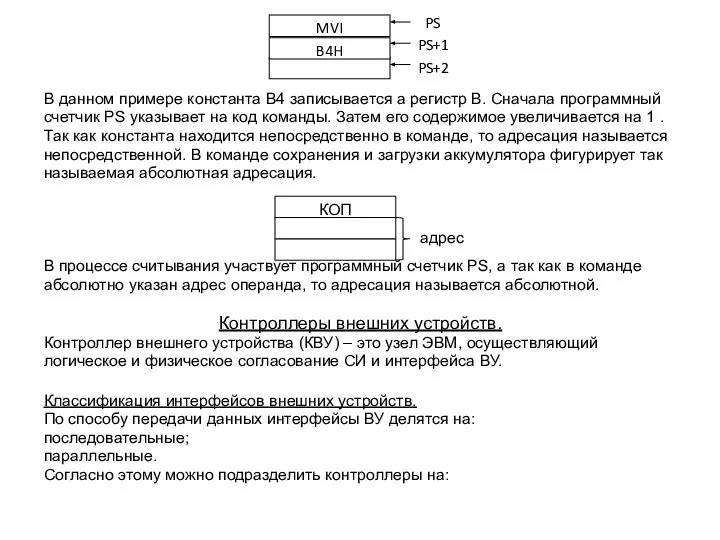

- 20. В данном примере константа В4 записывается а регистр В. Сначала программный счетчик PS указывает на код

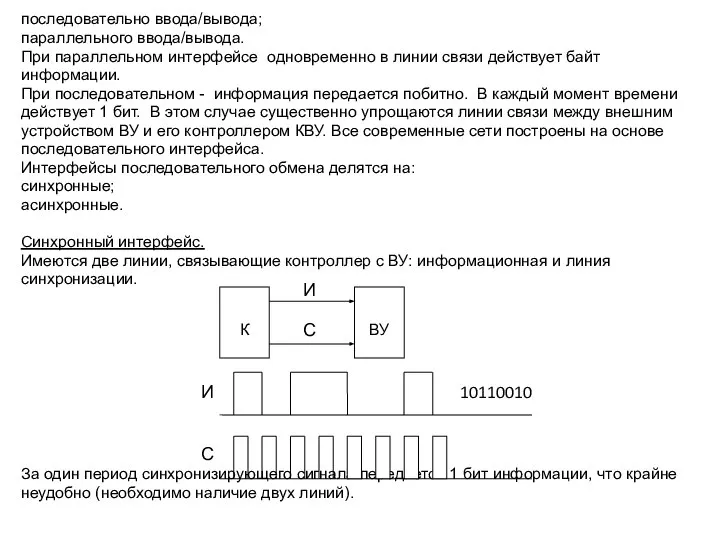

- 21. последовательно ввода/вывода; параллельного ввода/вывода. При параллельном интерфейсе одновременно в линии связи действует байт информации. При последовательном

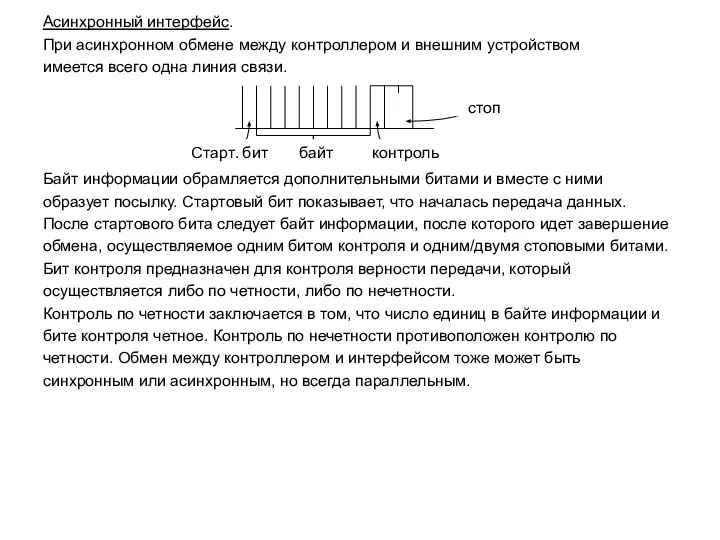

- 22. Асинхронный интерфейс. При асинхронном обмене между контроллером и внешним устройством имеется всего одна линия связи. Байт

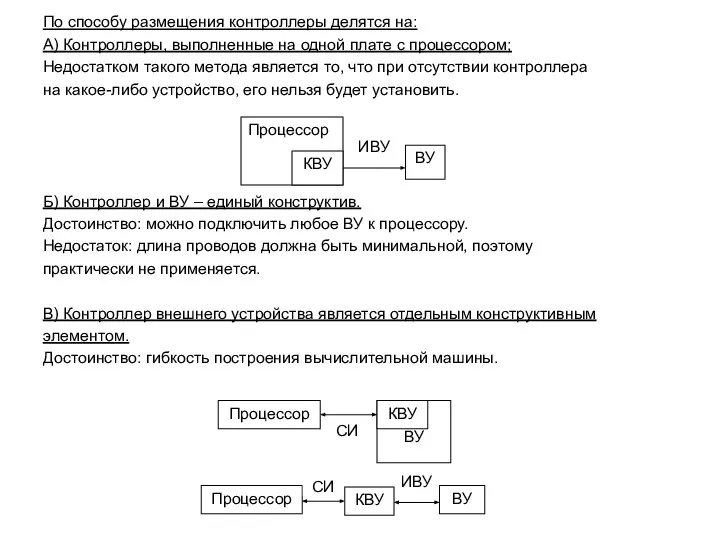

- 23. По способу размещения контроллеры делятся на: А) Контроллеры, выполненные на одной плате с процессором; Недостатком такого

- 24. Типовая структурная схема КВУ. КВУ включает в себя следующие основные узлы: приемопередатчики шины данных ШД; приемопередатчики

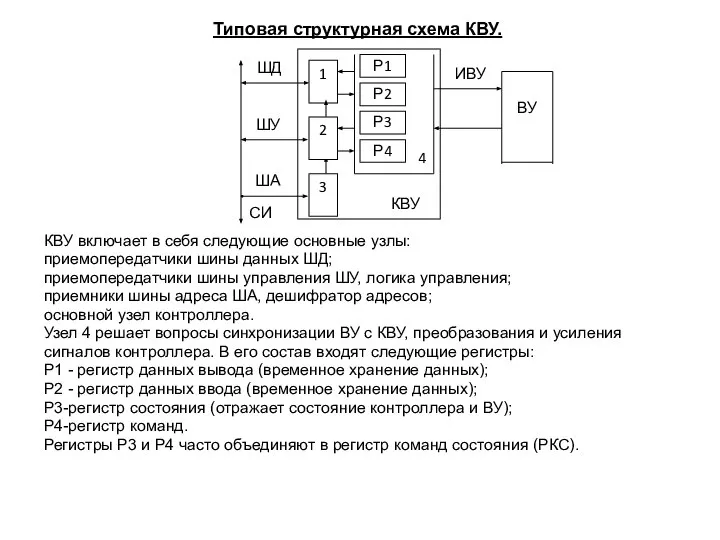

- 25. Алгоритм асинхронного обмена СИ с контроллером. Обмен данными может осуществляться в 2-ух режимах: синхронном (данные вводятся/выводятся

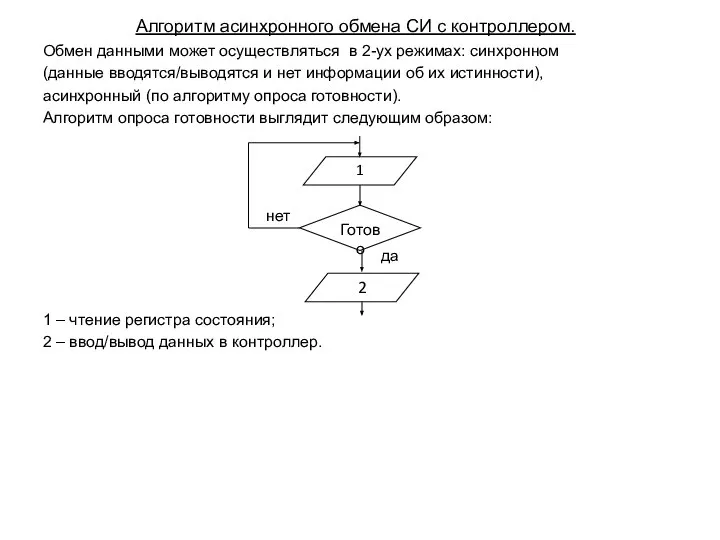

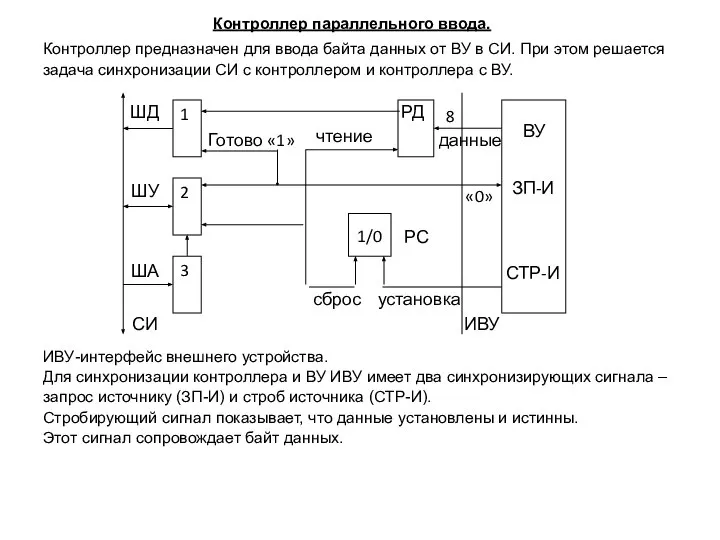

- 26. Контроллер параллельного ввода. Контроллер предназначен для ввода байта данных от ВУ в СИ. При этом решается

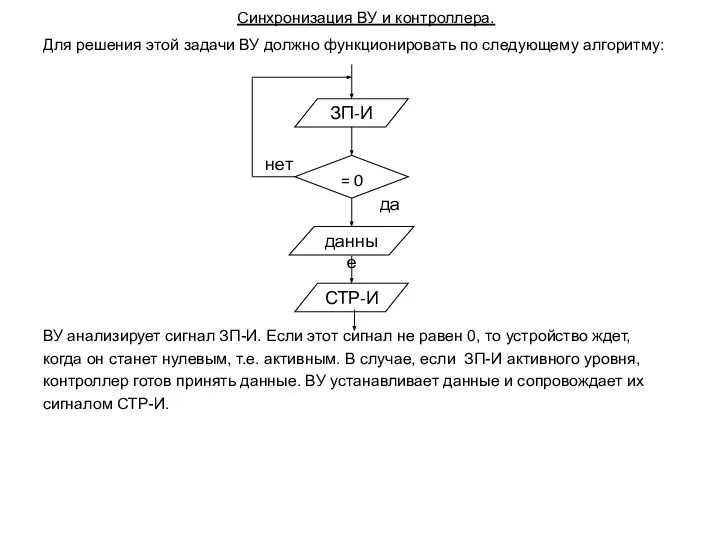

- 27. Синхронизация ВУ и контроллера. Для решения этой задачи ВУ должно функционировать по следующему алгоритму: ВУ анализирует

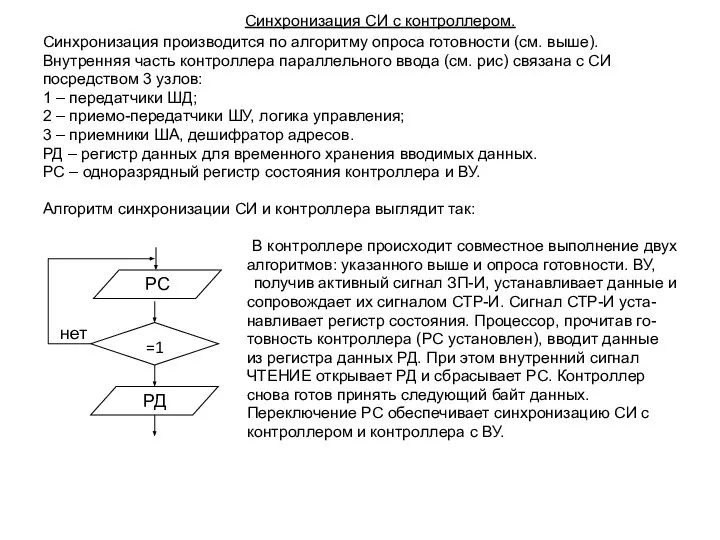

- 28. Синхронизация СИ с контроллером. Синхронизация производится по алгоритму опроса готовности (см. выше). Внутренняя часть контроллера параллельного

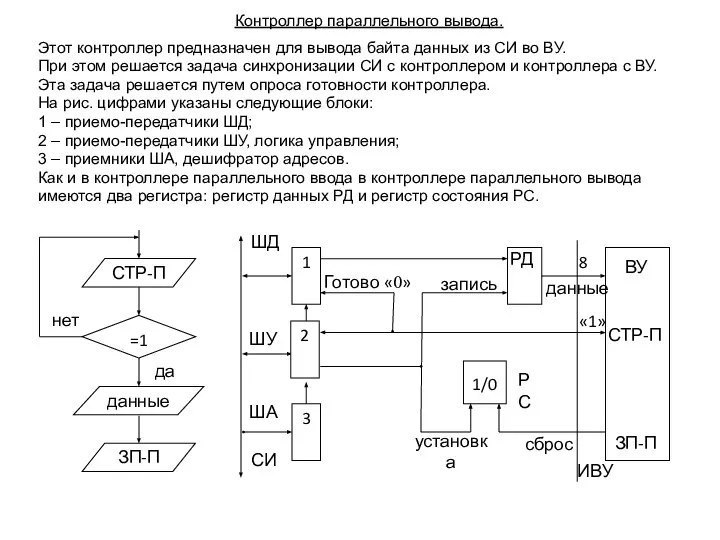

- 29. Контроллер параллельного вывода. Этот контроллер предназначен для вывода байта данных из СИ во ВУ. При этом

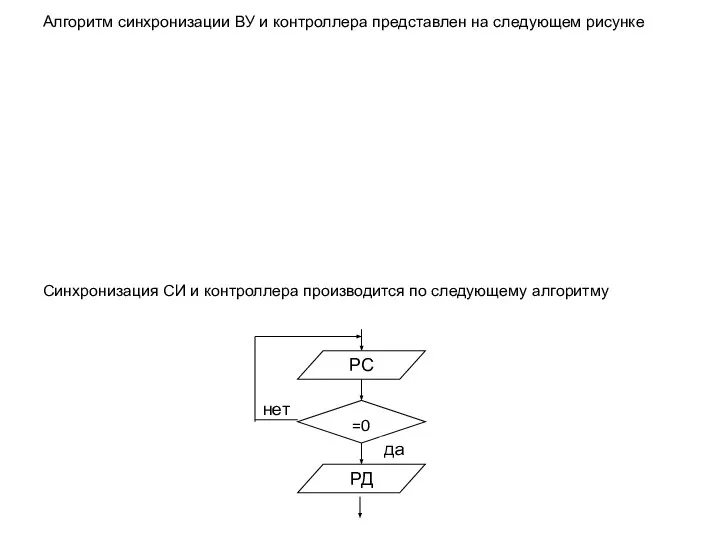

- 30. Алгоритм синхронизации ВУ и контроллера представлен на следующем рисунке Синхронизация СИ и контроллера производится по следующему

- 31. Между СИ и контроллером осуществляется асинхронный обмен, т.е. процессор опрашивает РС (готовность контроллера). Если контроллер готов,

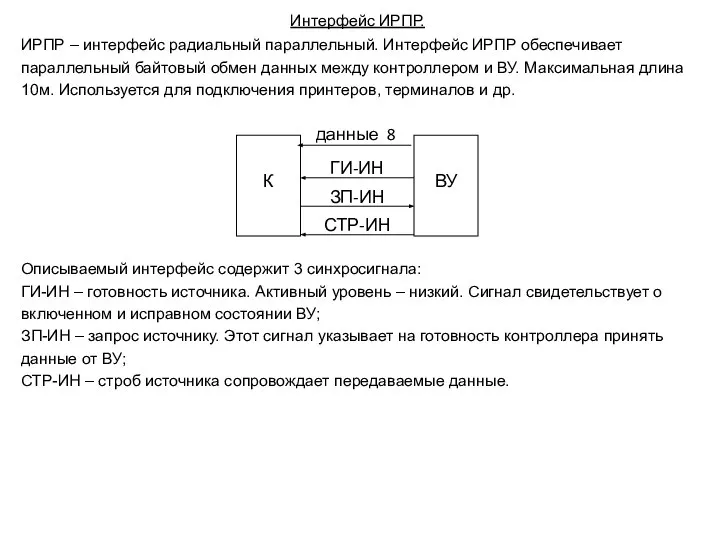

- 32. Интерфейс ИРПР. ИРПР – интерфейс радиальный параллельный. Интерфейс ИРПР обеспечивает параллельный байтовый обмен данных между контроллером

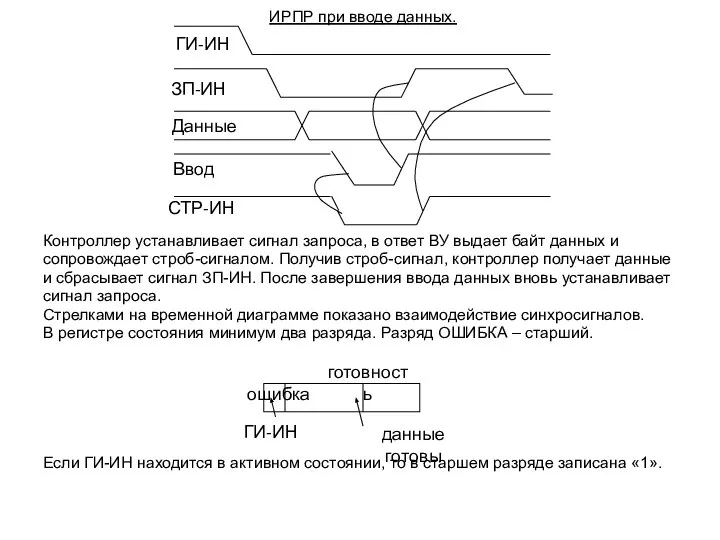

- 33. ИРПР при вводе данных. Контроллер устанавливает сигнал запроса, в ответ ВУ выдает байт данных и сопровождает

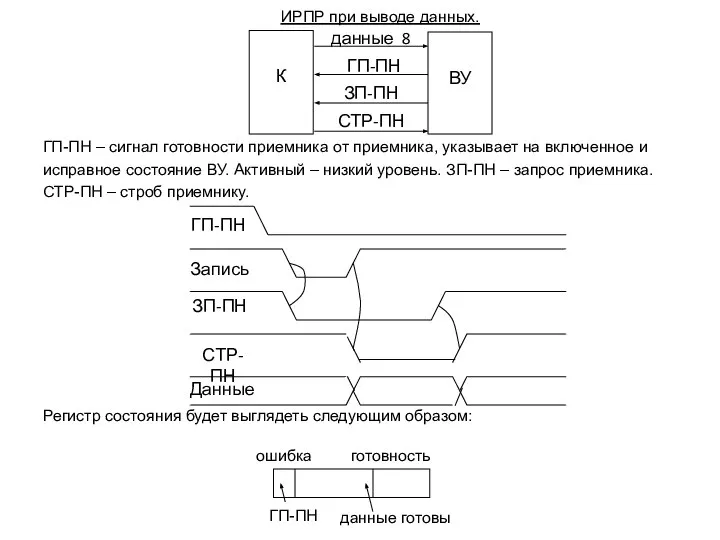

- 34. ИРПР при выводе данных. ГП-ПН – сигнал готовности приемника от приемника, указывает на включенное и исправное

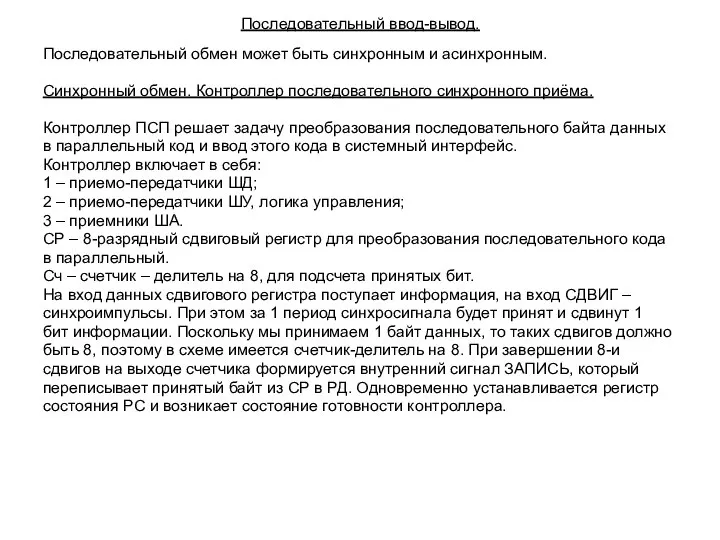

- 35. Последовательный ввод-вывод. Последовательный обмен может быть синхронным и асинхронным. Синхронный обмен. Контроллер последовательного синхронного приёма. Контроллер

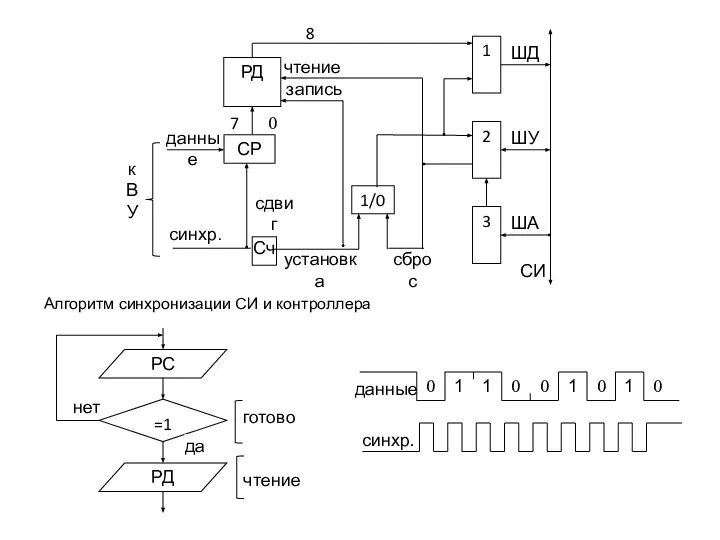

- 36. Алгоритм синхронизации СИ и контроллера 1 2 3 РД СР Сч 1/0 установка сброс ШУ СИ

- 37. Контроллер последовательной синхронной передачи. Этот контроллер предназначен для синхронной передачи данных в линию, связывающую контроллер с

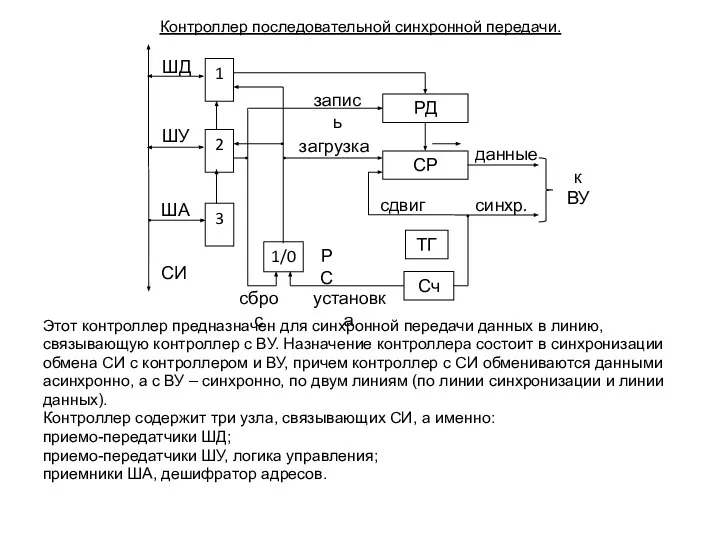

- 38. Также в контроллере имеются восьмиразрядный регистр данных (РД) и одноразрядный регистр состояния (РС). Восьмиразрядный сдвиговый регистр

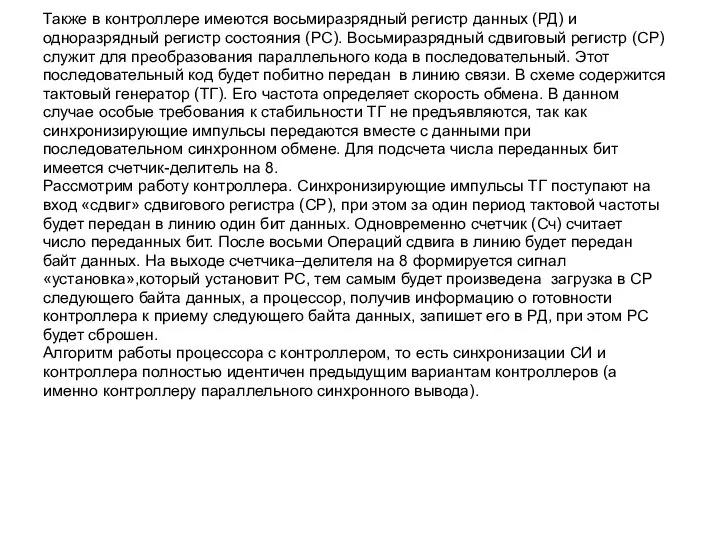

- 39. Асинхронный обмен. Контроллер последовательной асинхронной передачи решает задачу формирования посылки и тем самым синхронизации контроллера и

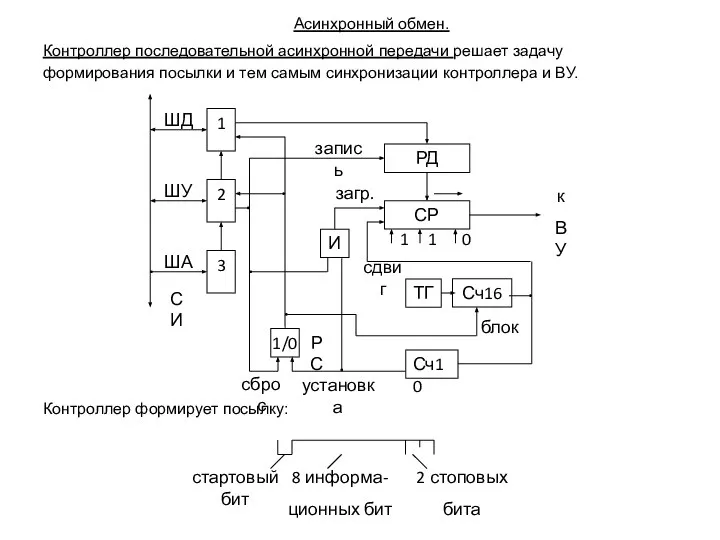

- 40. Бит контроля четности в данном случае не формируется. Данный контроллер содержит следующие узлы связи и синхронизации

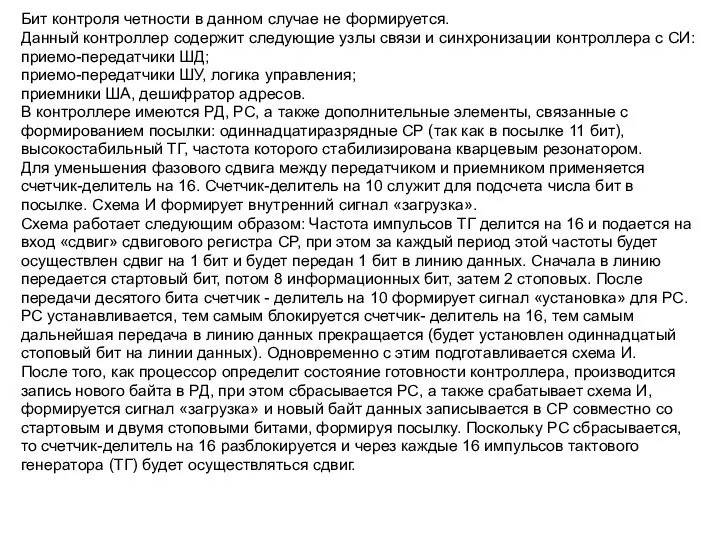

- 41. Контроллер последовательного асинхронного приема. Назначение этого контроллера состоит в преобразовании посылки в байт данных и ввода

- 42. Узлы 1, 2, 3, РС, РД аналогичны соответствующим узлам предыдущих контроллеров. Первым на вход контроллера стартовый

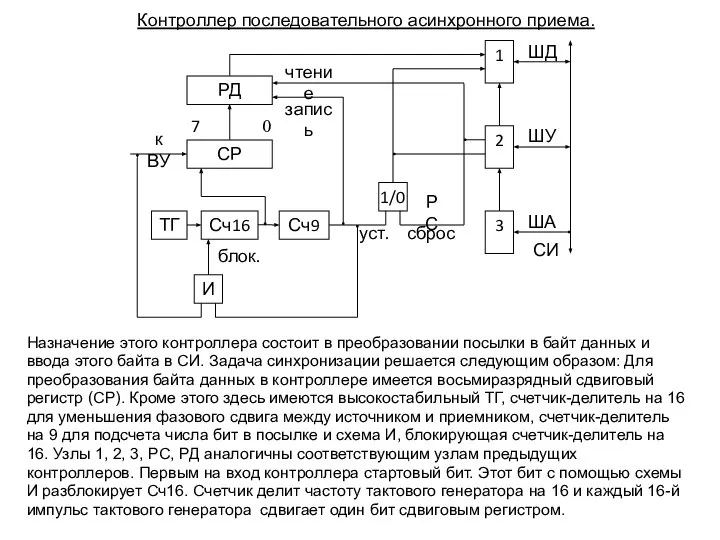

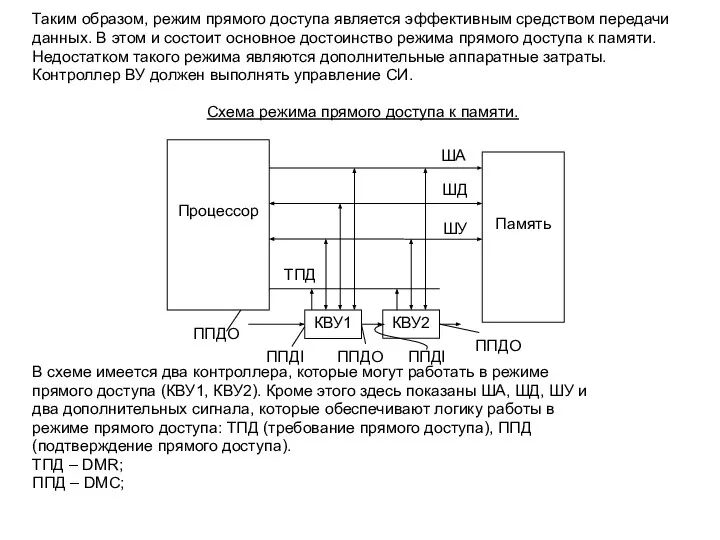

- 43. Таким образом, режим прямого доступа является эффективным средством передачи данных. В этом и состоит основное достоинство

- 44. Для реализации прямого доступа контроллер запрашивает прямой доступ путем установки сигнала ТПД. Активный уровень сигнала –

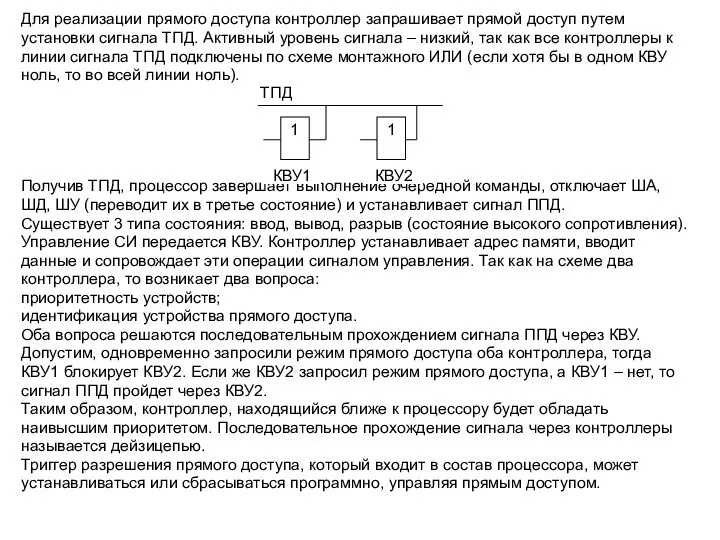

- 45. Режим работы по прерыванию. Рассмотрим временную диаграмму прерывания. Основная программа и прерывающая работают асинхронно, следовательно, очень

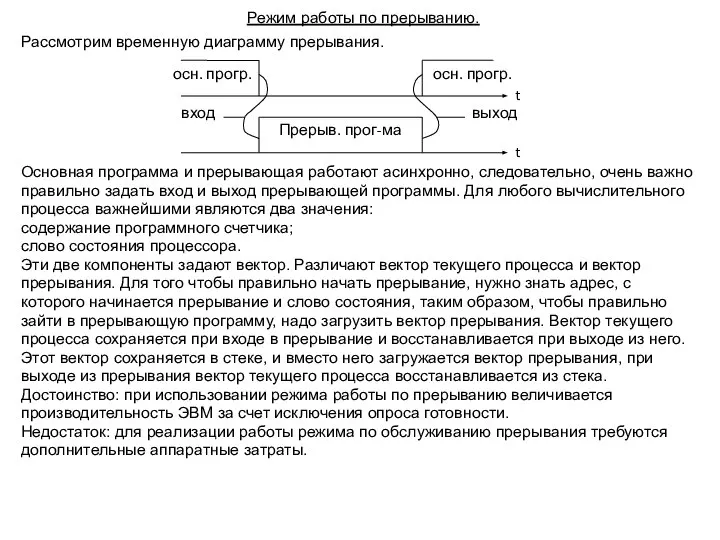

- 46. Приоритеты прерывания. Прерывания подразделяются на внутренние и внешние. Внутренние прерывания контролируют внутренние события вычислительной машины. Внешние

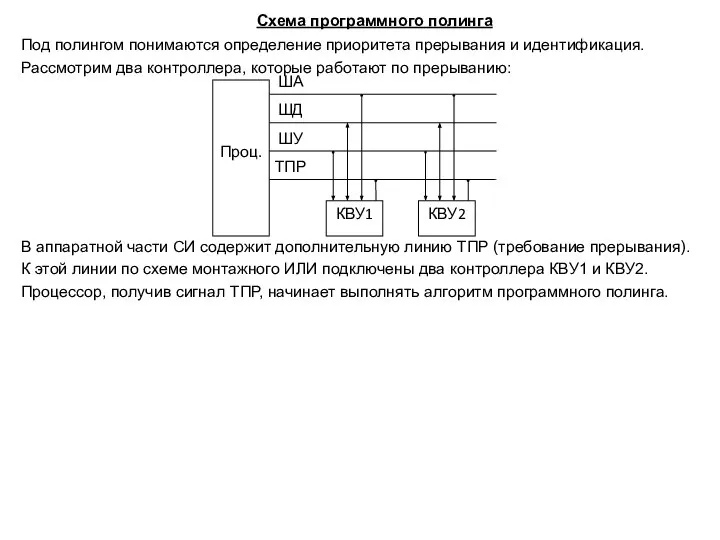

- 47. Схема программного полинга Под полингом понимаются определение приоритета прерывания и идентификация. Рассмотрим два контроллера, которые работают

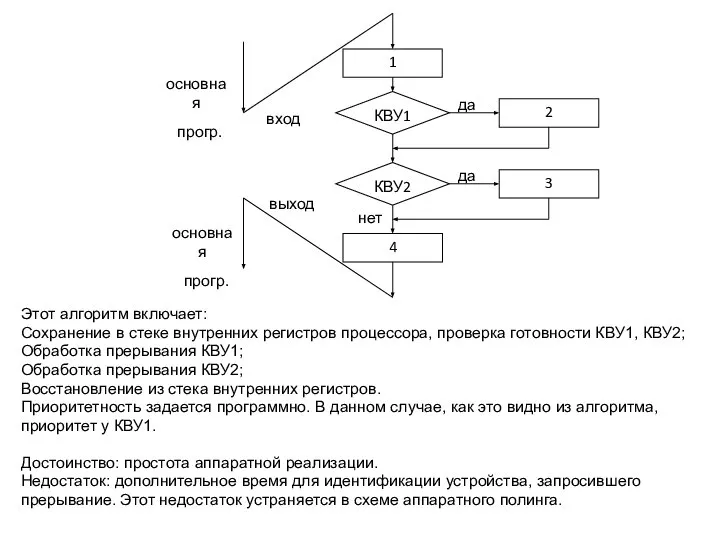

- 48. Этот алгоритм включает: Сохранение в стеке внутренних регистров процессора, проверка готовности КВУ1, КВУ2; Обработка прерывания КВУ1;

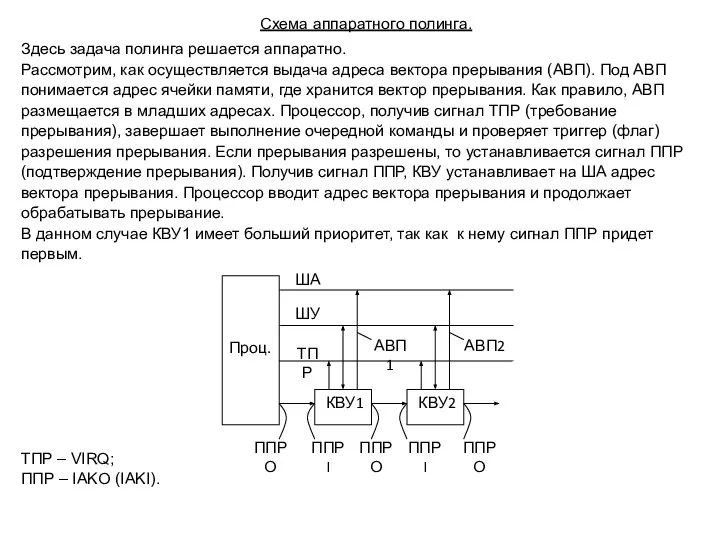

- 49. Схема аппаратного полинга. Здесь задача полинга решается аппаратно. Рассмотрим, как осуществляется выдача адреса вектора прерывания (АВП).

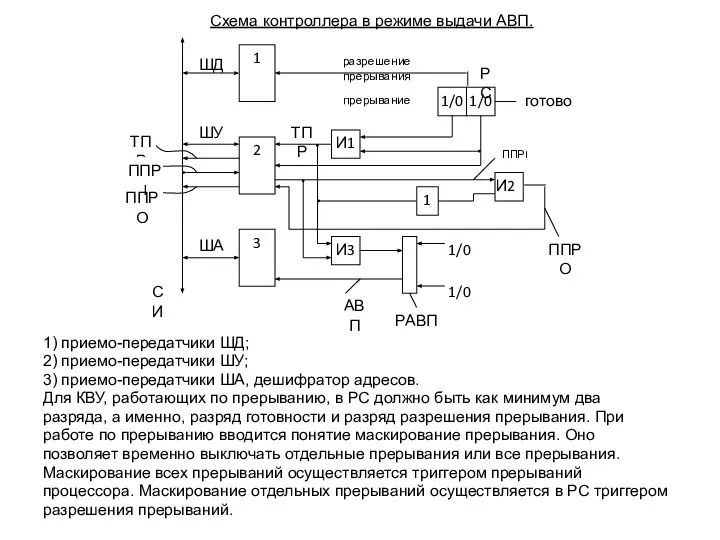

- 50. Схема контроллера в режиме выдачи АВП. 1) приемо-передатчики ШД; 2) приемо-передатчики ШУ; 3) приемо-передатчики ША, дешифратор

- 51. Ситуация прерывания возникает в контроллере в случае, если прерывания разрешены и данные готовы. С помощью схемы

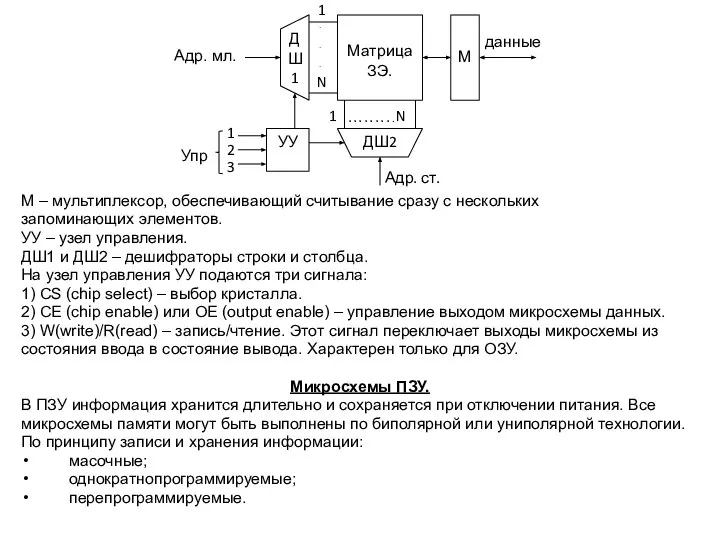

- 52. М – мультиплексор, обеспечивающий считывание сразу с нескольких запоминающих элементов. УУ – узел управления. ДШ1 и

- 53. Типы ПЗУ и технологии изготовления представлены в следующей схеме Масочные микросхемы ПЗУ программируются на заводе –

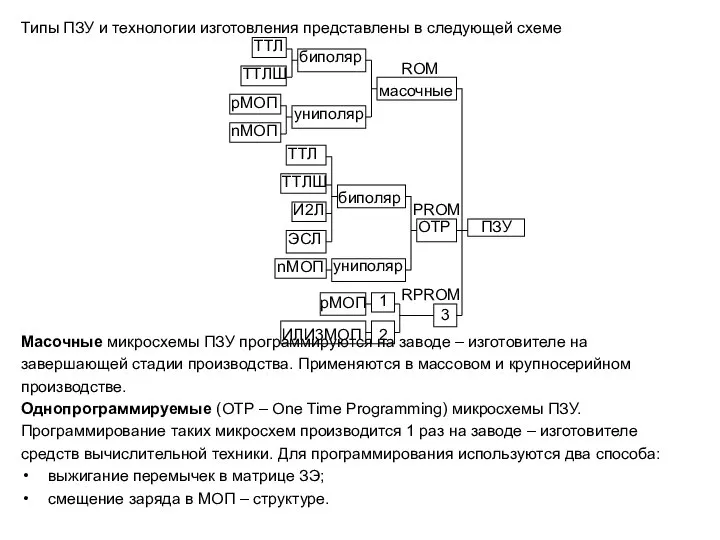

- 54. ОТР применяются в серийном и массовом производстве. Перепрограммируемые микросхемы ПЗУ. Такие микросхемы позволяют многократно стирать и

- 55. Принцип записи и хранения в МОП – структуре. МОП – металл, окисел, полупроводник. В область затвора

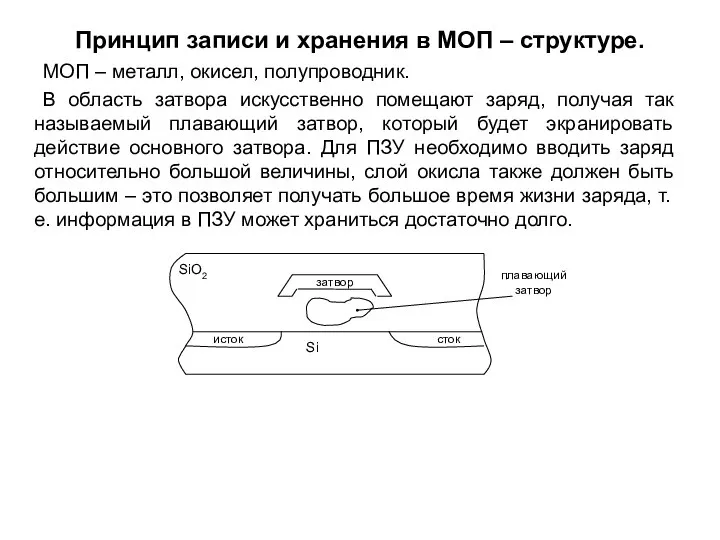

- 56. Способ записи и хранения информации путем выжигания перемычек. В схеме имеется перемычка из материала высокого сопротивления

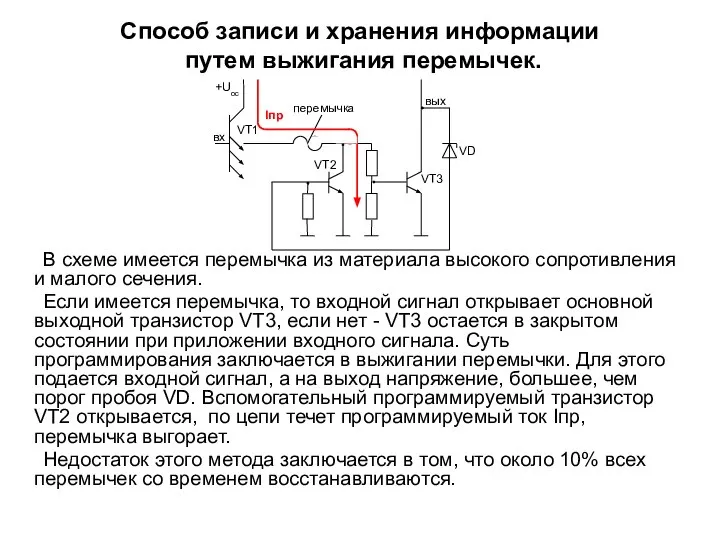

- 57. Микросхемы ОЗУ. ОЗУ предназначено для временного хранения программ и данных. В микросхеме статического ОЗУ информация сохраняется

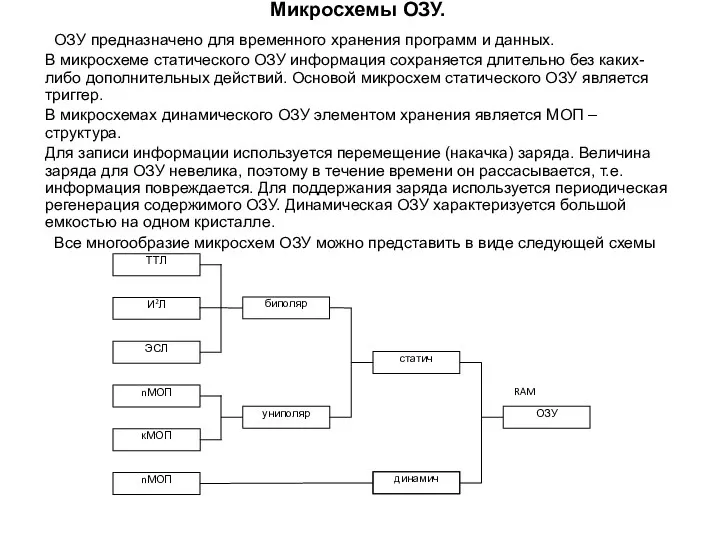

- 58. Структура микросхемы статической ОЗУ на примере МС КР537РУ10 емкостью 2048×8 бит. Типовым элементом хранения является триггер

- 59. Состояние микросхемы отражает следующая таблица Если сигнал CS равен 1, то микросхема находится в режиме хранения.

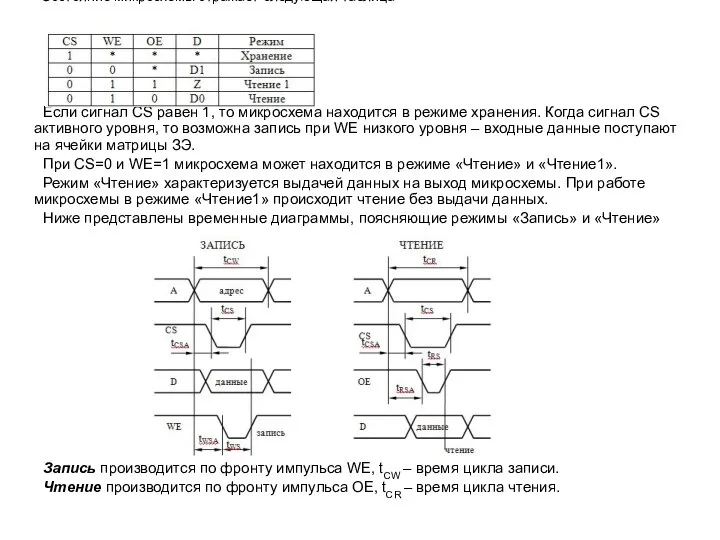

- 60. Микросхемы динамического ОЗУ. Микросхемы динамического ОЗУ обладают значительно большей емкостью, нежели микросхемы статического ОЗУ. Основная сложность

- 61. В качестве примера динамического ОЗУ рассмотрим микросхему КР565РУ5 объемом 64×1кбай Основа микросхемы – матрица ЗЭ. Организация

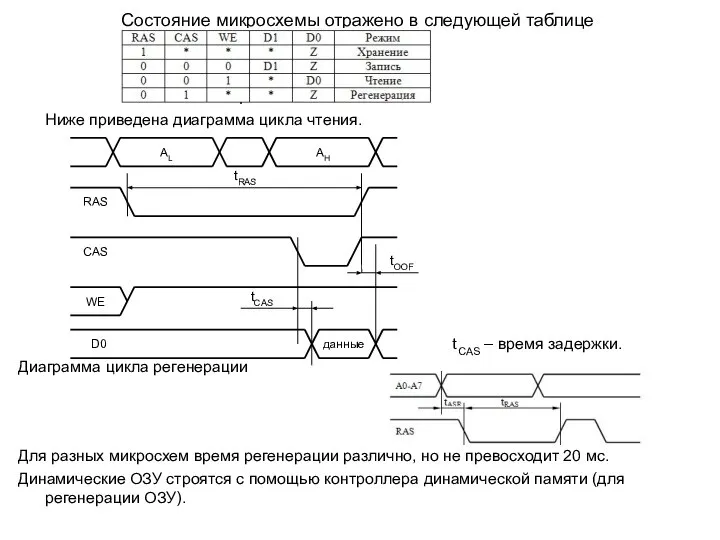

- 62. Состояние микросхемы отражено в следующей таблице Ниже приведена диаграмма цикла чтения. tCAS – время задержки. Диаграмма

- 63. Контроллеры динамического ОЗУ. Контроллеры динамического ОЗУ можно классифицировать следующим образом: 1. Контроллеры асинхронной регенерации. Процесс регенерации

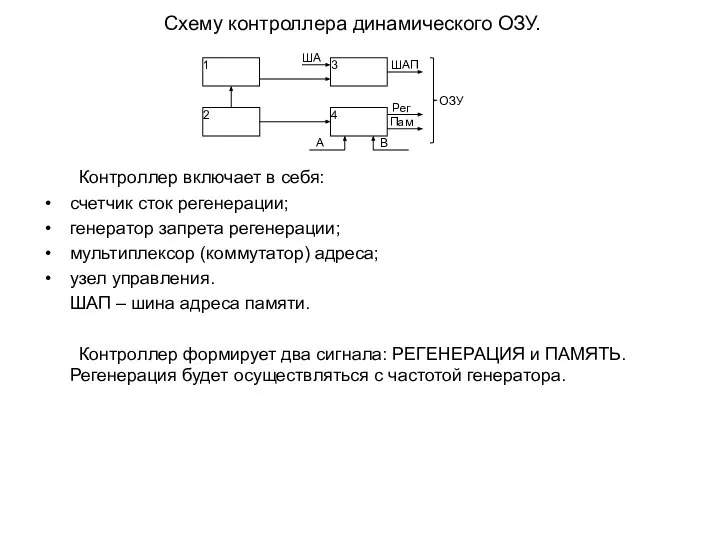

- 64. Схему контроллера динамического ОЗУ. Контроллер включает в себя: счетчик сток регенерации; генератор запрета регенерации; мультиплексор (коммутатор)

- 65. Наращивание объемов памяти. Задача наращивания объемов памяти возникает в двух случаях: когда емкости одной микросхемы памяти

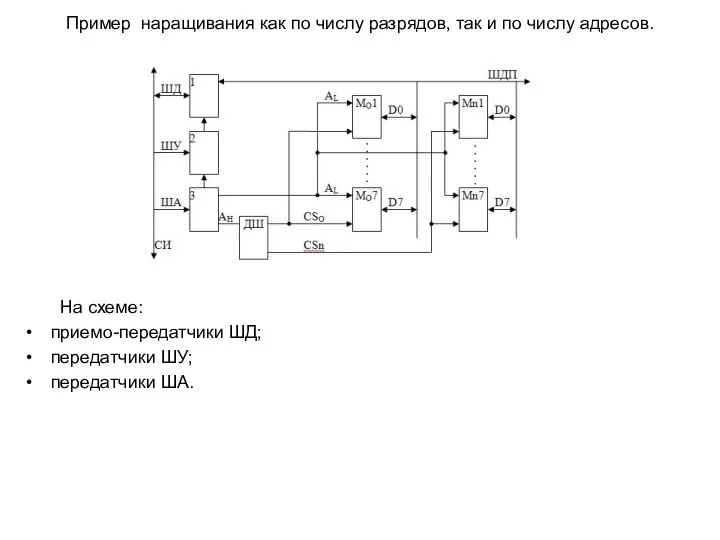

- 66. Пример наращивания как по числу разрядов, так и по числу адресов. На схеме: приемо-передатчики ШД; передатчики

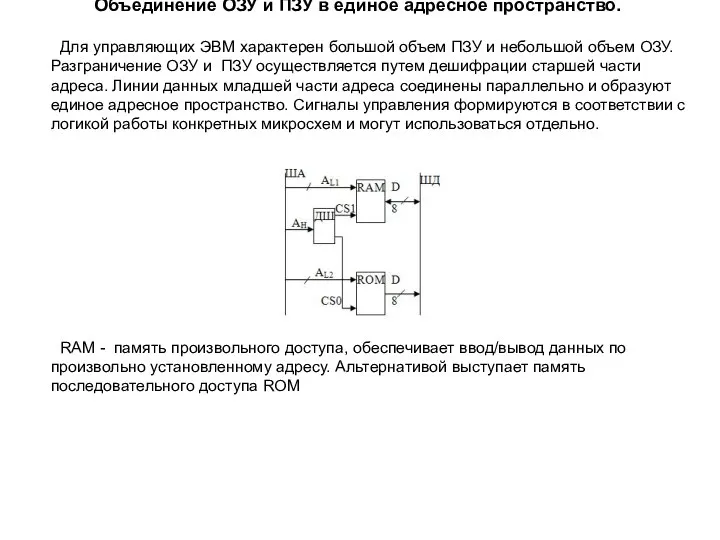

- 67. Объединение ОЗУ и ПЗУ в единое адресное пространство. Для управляющих ЭВМ характерен большой объем ПЗУ и

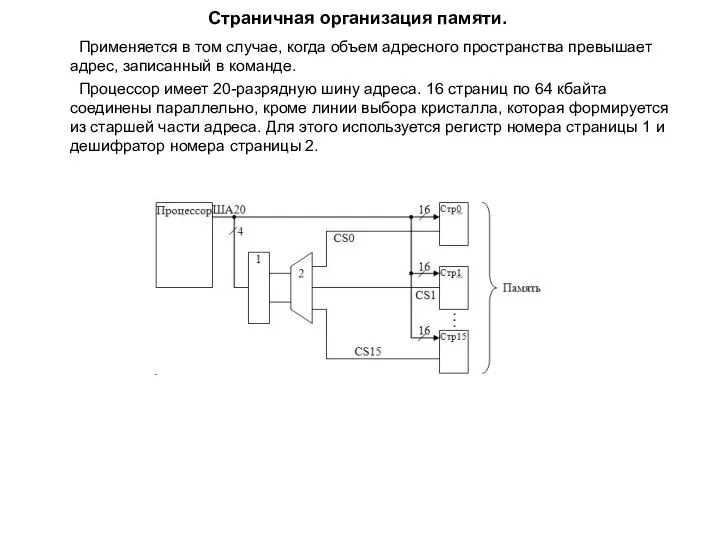

- 68. Страничная организация памяти. Применяется в том случае, когда объем адресного пространства превышает адрес, записанный в команде.

- 69. Микроконтроллеры. Средства вычислительной техники (СВТ) используются для управления и для вычислений. ОЭМ – однокристальные микро-ЭВМ (отечественное

- 70. Наибольшее распространение получили микроконтроллеры с системой команд 51-го кристалла. Условно это семейство микроконтроллеров называют MCS-51. Базовая

- 71. Усовершенствованный микропроцессор С517 имеет следующие отличия: АЦП (ADS); устройство быстрой арифметики с высокой разрядностью; увеличенное число

- 72. Семейство микроконтроллеров MSC-51. Организация памяти. Для микроконтроллеров семейства MSC-51 характерна структура с раздельной памятью программ и

- 73. Подключение внешней памяти к микроконтроллеру семейства MCS-51. Для разделения адреса и данных используется регистр-защелка. Сигнал ALE

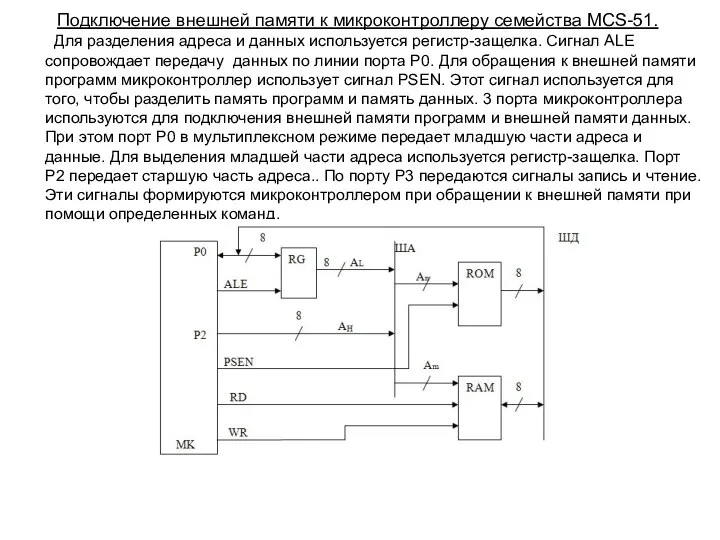

- 74. Объединение адресного пространства для MCS-51. При объединении памяти программ и памяти данных увеличивается гибкость программирования, появляется

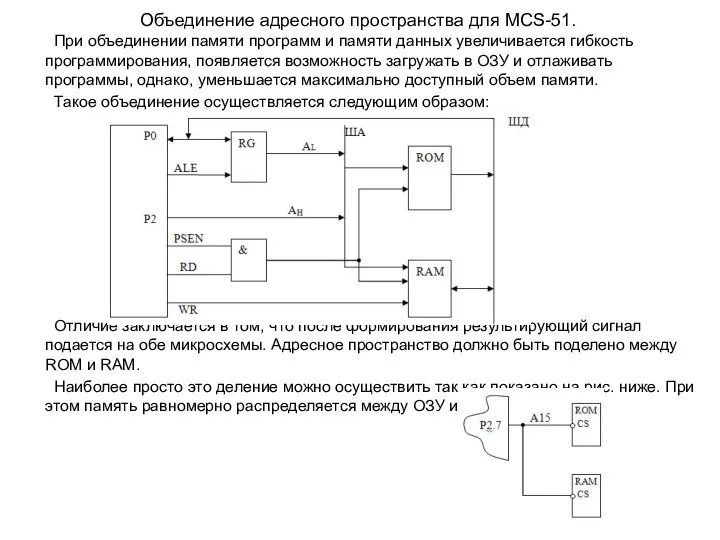

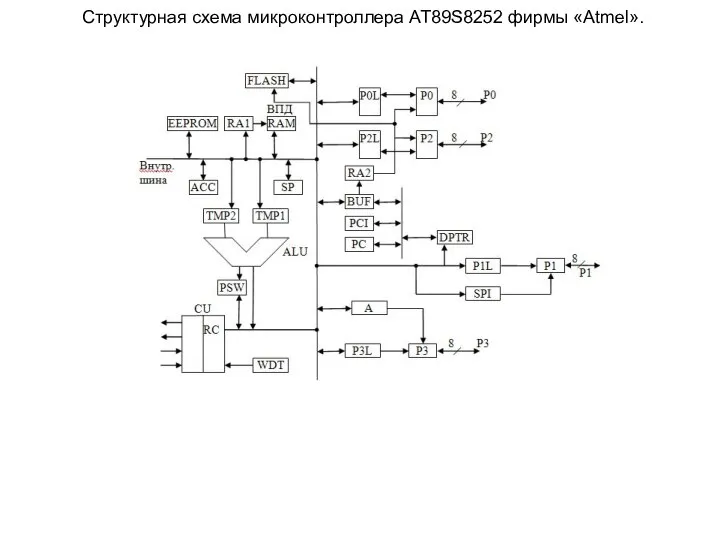

- 75. Структурная схема микроконтроллера семейства MCS-51. Рассмотрим структурную схему микроконтроллера AT89S8252 фирмы «Atmel». Микроконтроллер имеет встроенную Flash-память,

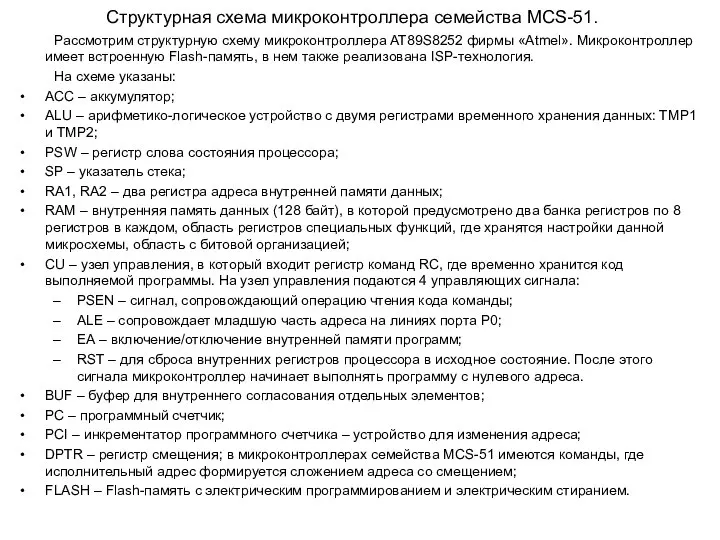

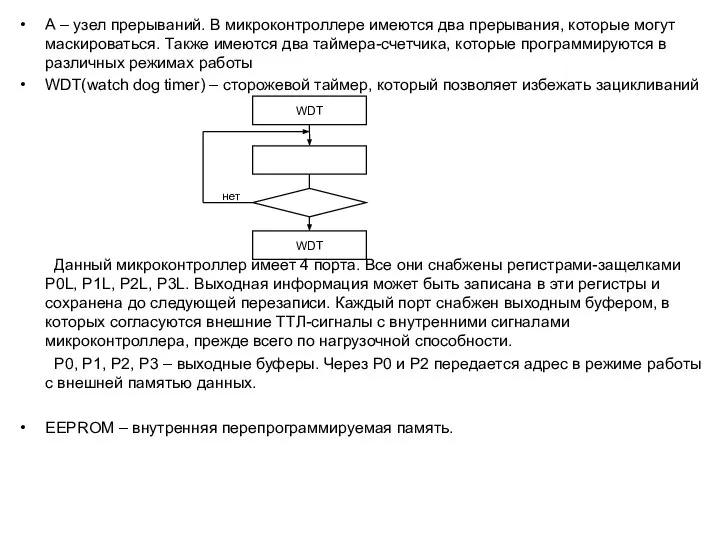

- 76. А – узел прерываний. В микроконтроллере имеются два прерывания, которые могут маскироваться. Также имеются два таймера-счетчика,

- 77. Структурная схема микроконтроллера AT89S8252 фирмы «Atmel».

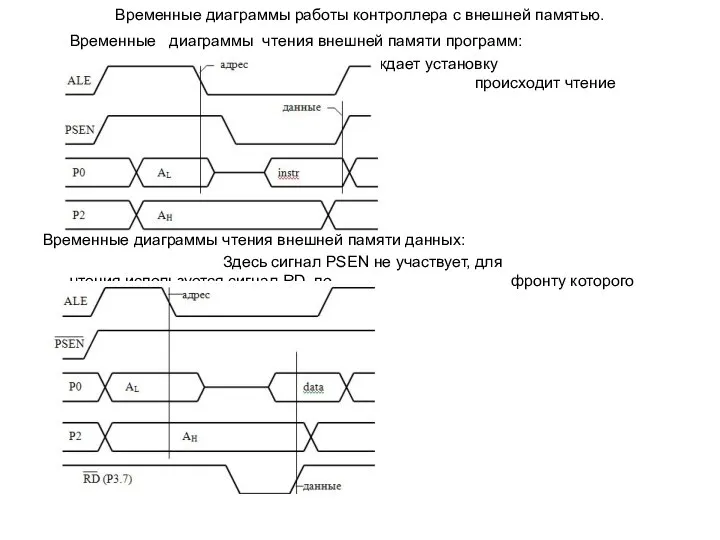

- 78. Временные диаграммы работы контроллера с внешней памятью. Временные диаграммы чтения внешней памяти программ: Сигнал ALE сопровождает

- 80. Скачать презентацию

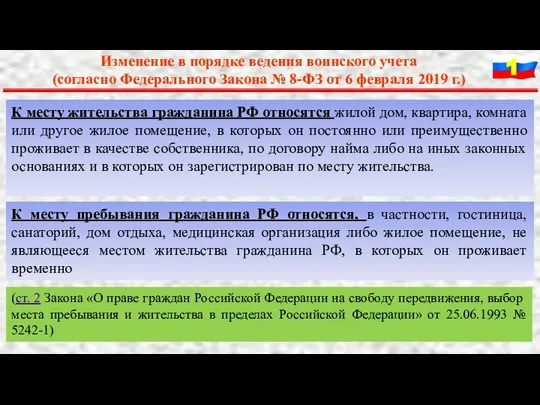

Изменение в порядке ведения воинского учета, согласно Федерального Закона № 8-ФЗ от 6 февраля 2019 года

Изменение в порядке ведения воинского учета, согласно Федерального Закона № 8-ФЗ от 6 февраля 2019 года Презентация Налог на имущество юридических лиц

Презентация Налог на имущество юридических лиц Презентация Юридическая ответственность за экологические правонарушения

Презентация Юридическая ответственность за экологические правонарушения  Использование СОТ на уроках русского языка и литературы Муниципальное общеобразовательное учреждение лицей 57 г. Тольятти. - презе

Использование СОТ на уроках русского языка и литературы Муниципальное общеобразовательное учреждение лицей 57 г. Тольятти. - презе Проект «Изумрудные острова». Благоустройство сквера на площади Ленина г. Заволжья

Проект «Изумрудные острова». Благоустройство сквера на площади Ленина г. Заволжья Информационная картина мира

Информационная картина мира Riscurile si potentialile dificultati la asamblarea si depanarea monitoarelor PC

Riscurile si potentialile dificultati la asamblarea si depanarea monitoarelor PC Шаблон для фотопрезентации (1)

Шаблон для фотопрезентации (1) Передвиборча програма кандидата на посаду голови студентської ради Полтавського національного педагогічного університету

Передвиборча програма кандидата на посаду голови студентської ради Полтавського національного педагогічного університету ФИЗКУЛЬТМИНУТКА

ФИЗКУЛЬТМИНУТКА Понятия государства

Понятия государства Сущность режима законности

Сущность режима законности Понятие модуля числа - презентация по Алгебре

Понятие модуля числа - презентация по Алгебре Тема: Необходимость дополнительного образования

Тема: Необходимость дополнительного образования Свободные механические колебания

Свободные механические колебания  Возникновение олимпийских игр

Возникновение олимпийских игр Мукополисахаридозы Подготовила Агеева А.В.

Мукополисахаридозы Подготовила Агеева А.В. Строительство общеобразовательной школы на территории округа «Город Калининград» в Восточном жилом районе

Строительство общеобразовательной школы на территории округа «Город Калининград» в Восточном жилом районе Автоматическое сопровождение электромагнитного луча вокруг электрической оси антенны

Автоматическое сопровождение электромагнитного луча вокруг электрической оси антенны Цветовая палитра интерьера ИМТ

Цветовая палитра интерьера ИМТ Язык программирования JAVA. Функции

Язык программирования JAVA. Функции Фольклорное направление в моде второй половины XX в

Фольклорное направление в моде второй половины XX в Право. Административное право. Задания для выполнения

Право. Административное право. Задания для выполнения Влияние системы учета преступлений на степень соответствия статистических данных действительного положения дела

Влияние системы учета преступлений на степень соответствия статистических данных действительного положения дела Подвесной потолок

Подвесной потолок Теоретическая физика твердого тела

Теоретическая физика твердого тела  Дозиметрические единицы и защита от радиоактивных излучений.

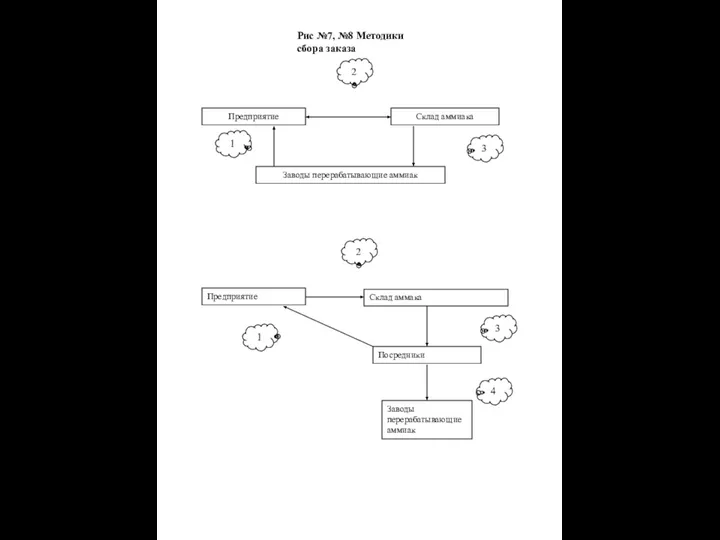

Дозиметрические единицы и защита от радиоактивных излучений. Методики сборки заказа

Методики сборки заказа