Содержание

- 2. Устройство Арифметико-логическое устройство предназначено для выполнения всех арифметических и логических операций над числовой и символьной информацией.

- 3. Функции Чтение и дешифрацию команд из основной памяти; Чтение данных из основной памяти и регистров адаптеров

- 4. Архитектура процессора Архитектура процессора —количественная составляющая компонентов микроархитектуры вычислительной машины (процессора компьютера) (например, регистр флагов или

- 5. CISC-архитектура CISC (англ. complex instruction set computing или complex instruction setcomputer) — тип процессорной архитектуры, которая

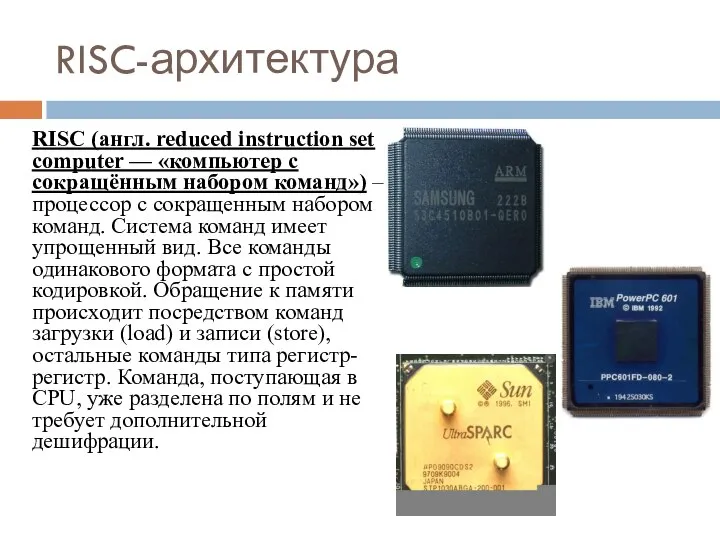

- 6. RISC-архитектура RISC (англ. reduced instruction set computer — «компьютер с сокращённым набором команд») – процессор с

- 7. VLIW-архитектура VLIW (англ. very long instruction word — «очень длинная машинная команда») — архитектура процессоров с

- 8. VLIW-архитектура Преимущества: Упрощение архитектуры процессора, снижение энергопотребления; Недостатки: Программирование вручную на уровне машинного кода является достаточно

- 9. MISC-архитектура MISC (англ. minimal instruction set computer — «компьютер с минимальным набором команд») — вид процессорной

- 11. Скачать презентацию

Технология управления требованиями с использованием IBM

Технология управления требованиями с использованием IBM ТСС РНП – Радионавигационные приборы РЛС -Радиолокационное оборудование

ТСС РНП – Радионавигационные приборы РЛС -Радиолокационное оборудование Цифровая схемотехника. Мультиплексоры и демультиплексоры. Аналоговые переключатели

Цифровая схемотехника. Мультиплексоры и демультиплексоры. Аналоговые переключатели London. It is the capital of the United Kingdom of Great Britain and Northern Ireland

London. It is the capital of the United Kingdom of Great Britain and Northern Ireland Когда мы станем взрослыми?

Когда мы станем взрослыми? Fitness aerobics

Fitness aerobics Классификация парогенераторов АЭС

Классификация парогенераторов АЭС Презентация Сборы за пользование объектами животного мира и водных биологических ресурсов

Презентация Сборы за пользование объектами животного мира и водных биологических ресурсов Комплекс ГТО как основа физического воспитания

Комплекс ГТО как основа физического воспитания Работа с файлами на паскале

Работа с файлами на паскале Виды передач движения

Виды передач движения Алгебраические поверхности в пространстве - презентация по Алгебре

Алгебраические поверхности в пространстве - презентация по Алгебре Основные цели разработки конслатингового проекта

Основные цели разработки конслатингового проекта  Этногенез народов среднего Поволжья. Культурные традиции народов Татарстана

Этногенез народов среднего Поволжья. Культурные традиции народов Татарстана Цветная металлургия Урала

Цветная металлургия Урала Детская школа искусств

Детская школа искусств Политические партии

Политические партии Презентация на тему "Комы при интоксикациях" - скачать презентации по Медицине

Презентация на тему "Комы при интоксикациях" - скачать презентации по Медицине Методы принятия управленческих решений Подготовила студентка группы МЭ-102 Швейкина Алёна

Методы принятия управленческих решений Подготовила студентка группы МЭ-102 Швейкина Алёна Деловая игра для педагогов дошкольного образования ФГТ в жизни нашего ДОУ

Деловая игра для педагогов дошкольного образования ФГТ в жизни нашего ДОУ  Брюлов Карл Павлович Жизнь творчество

Брюлов Карл Павлович Жизнь творчество  Биотическая структура биосферы по типам питания и функциям

Биотическая структура биосферы по типам питания и функциям Светодиодные лампы

Светодиодные лампы Прядок слов в предложении

Прядок слов в предложении  JavaBeans

JavaBeans  Обзор основных банковских информационных систем за рубежом

Обзор основных банковских информационных систем за рубежом отладчик ассемблера

отладчик ассемблера Многоуровневая система планирования в банке. Стратегическое планирование Курс «Банковский менеджмент» к.э.н., доц. Соколов

Многоуровневая система планирования в банке. Стратегическое планирование Курс «Банковский менеджмент» к.э.н., доц. Соколов