Содержание

- 2. Учебные вопросы: Назначение и структура центрального процессора (ЦП), состав устройств. Центральное устройство управления (УУ). Арифметико-логическое устройство

- 3. Назначение и структура центрального процессора (ЦП), состав устройств Процессором называется устройство, непосредственно осуществляющее процесс обработки данных

- 4. Центральное устройство управления (УУ) Устройство управления организует процесс выполнения программ и координирует взаимодействие всех устройств ЭВМ

- 5. Арифметико-логическое устройство (АЛУ): назначение, основные характеристики, обобщенная структурная схема Арифметико-логическое устройство процессора выполняет логические и арифметические

- 6. Арифметико-логическое устройство (АЛУ): назначение Арифметико-логическое устройство (АЛУ) - центральная часть процессора, выполняющая арифметические и логические операции.

- 7. Арифметико-логическое устройство (АЛУ): основные характеристики АЛУ состоит из регистров, сумматора с соответствующими логическими схемами и элемента

- 8. Арифметико-логическое устройство (АЛУ): обобщенная структурная схема

- 9. Структурная схема АЛУ Структурная схема АЛУ и его связь с другими блоками машины показаны на рисунке

- 10. Взаимодействие блоков АЛУ при выполнении различных арифметических и логических операций Обобщенная структура АЛУ ИПУ – Инженерный

- 11. Центральное Устройство Управления ЦУУ формирует управляющие сигналы для следующих функций: - выборки из ОЗУ (ПЗУ) кодов

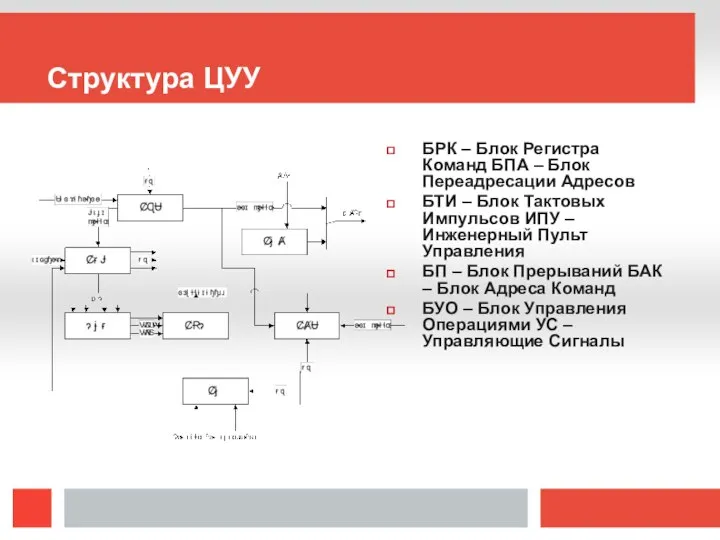

- 12. Структура ЦУУ БРК – Блок Регистра Команд БПА – Блок Переадресации Адресов БТИ – Блок Тактовых

- 13. ЦУУ Алгоритм: 1)код очередной команды программы принимается для расшифровки и исполнения в БРК, под воздействием УСов.

- 14. АЛУ Назначение – обработка информации (операции +, -, >, и т.д.) и логические операции. Кроме того

- 15. АЛУ (2) 1) Регистры для хранения кодов операндов на время выполнения действий над ними 2) Регистры

- 16. АЛУ 3 Алгоритм работы: 1) перед суммированием по шине сброс всех триггеров – уст. в 0

- 17. Назначение и классификация АЛУ Типы АЛУ: используемая система счисления по формам представления числовых данных – с

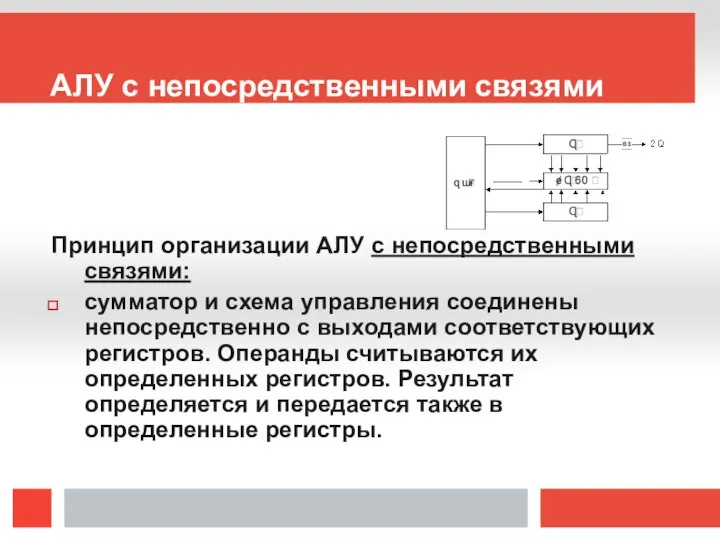

- 18. АЛУ с непосредственными связями Принцип организации АЛУ с непосредственными связями: сумматор и схема управления соединены непосредственно

- 19. АЛУ магистральной структуры Схемы для преобразования информации выделены в отдельные блоки, включающие в себя сумматор и

- 20. Структура АЛУ для сложения и вычитания чисел с фиксированной запятой При выполнении сложения положительные слагаемые представляются

- 21. Алгоритм сложения и вычитания чисел с фиксированной запятой Алгоритм работы: 1) Из памяти по входной информационной

- 22. Алгоритм сложения и вычитания чисел с фиксированной запятой (2) 6) Операция алгебраического вычитания Z=X-Y=X+(-Y) может быть

- 23. Структура АЛУ для умножения чисел с фиксированной запятой (сумматор частичных произведений) В ЭВМ операция умножения чисел

- 24. Арифметико-логическое устройство (АЛУ): назначение, основные характеристики, обобщенная структурная схема Обобщенная структурная схема АЛУ включает в себя

- 25. CISC против RISC Принципиально новое, что отличает RISC- от CISC-процессоров – это: отсутствие аппаратного стека –

- 26. Структура базового микропроцессора (МП) современных моделей для IMB-совместимых ПЭВМ, взаимодействие его узлов и блоков самостоятельно

- 27. Параметры микропроцессоров разрядность; рабочая тактовая частота; размер кэш-памяти; состав инструкций; конструктив; рабочее напряжение и т. д.

- 28. Параметры микропроцессоров Разрядность шины данных микропроцессора определяет количество разрядов, над которыми одновременно могут выполняться операции; разрядность

- 29. Параметры микропроцессоров Состав инструкций -- перечень, вид и тип команд, автоматически исполняемых МП. От типа команд

- 30. Кэш-память Кэш – память Это статическая память (Statiс RAM – SRAM), которая, в отличие от динамической

- 31. Конвейеризация Существенное повышение производительности МП 80286 по сравнению с базовой моделью семейства стало возможным благодаря внедрению

- 32. Конвейеризация в 286 Конвейеризация команд в МП 80286

- 33. Идея конвейеризации была развита в следующих моделях этого семейства. В МП Intel-486 реализован пятиступенчатый конвейер для

- 34. Конвейеризация в Pentium Блок-схема архитектуры МП Pentium

- 35. Конвейеризация в Pentium Новая микроархитектура процессоров Pentium и более поздних базируется на идее суперскалярной обработки. Под

- 36. Конвейеризация в Pentium Конвейеризация команд в МП Pentium

- 37. Динамическое (спекулятивное) исполнение Одной из главных особенностей шестого поколения микропроцессоров архитектуры IA32 является динамическое(спекулятивное) исполнение. Под

- 38. Особенности P6 Внутренняя организация МП P6 соответствует архитектуре RISC, поэтому блок выборки команд, считав поток инструкций

- 39. Особенности P6 Блок исполнительных устройств способен выбирать инструкции из пула в любом порядке. При этом благодаря

- 40. Разрядность Разрядность Первые процессорные регистры могли хранить лишь 4 – битные числа. Затем появились 8 –

- 41. Блок схема микропроцессора Pentium Pro

- 42. Технология производства МП Выращивание диоксида кремния и создание проводящих областей Тестирование Изготовление корпуса. Доставка.

- 43. Технология производства http://www.modlabs.net/articles/sovremennye-mikroprocessory

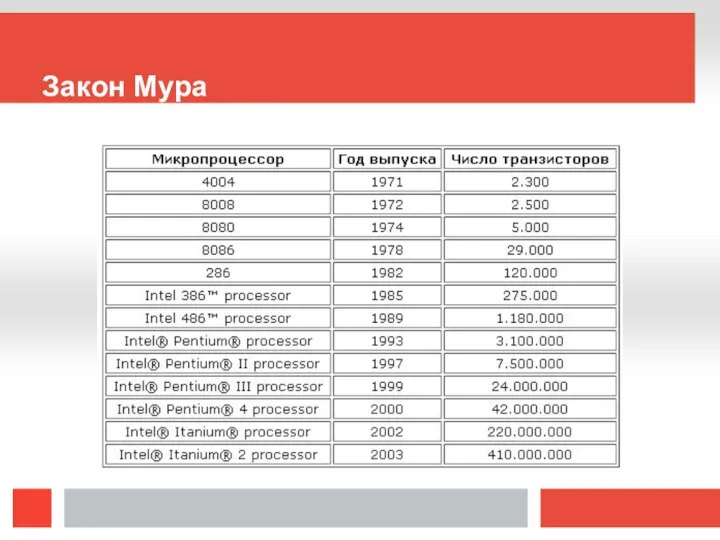

- 44. Закон Мура

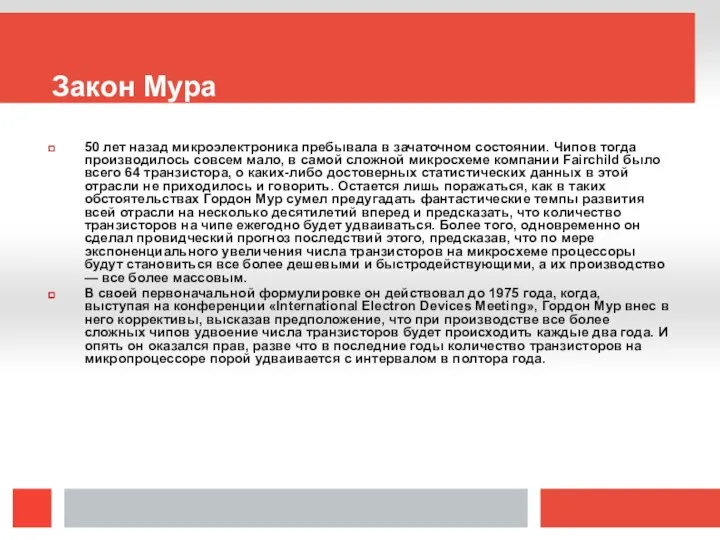

- 45. Закон Мура 50 лет назад микроэлектроника пребывала в зачаточном состоянии. Чипов тогда производилось совсем мало, в

- 47. Скачать презентацию

Мультипликация

Мультипликация Классицизм в искусстве

Классицизм в искусстве Атомная бомба

Атомная бомба Презентация Демография

Презентация Демография Презентация "Глобальная экономика" - скачать презентации по Экономике

Презентация "Глобальная экономика" - скачать презентации по Экономике Периодонтит у детей. Клиника. Диагностика. Дифференциальная диагностика. Принцип лечения.

Периодонтит у детей. Клиника. Диагностика. Дифференциальная диагностика. Принцип лечения.  Управляющие конструкции языка С

Управляющие конструкции языка С Я иду в ДВФУ!

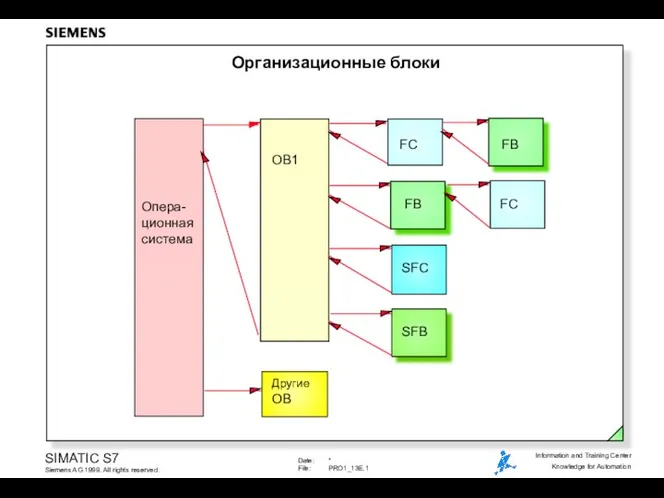

Я иду в ДВФУ! Организационные блоки

Организационные блоки Без названия

Без названия Петербургские замки

Петербургские замки ФЗ 83

ФЗ 83 00dc15975ec042b1acd17f85fb966815

00dc15975ec042b1acd17f85fb966815 Зарубежные справочно-правовые системы

Зарубежные справочно-правовые системы B-PACK

B-PACK Презентация Экономическое взаимодействие РФ в интеграционных процессах и международное сотрудничество таможенных органов

Презентация Экономическое взаимодействие РФ в интеграционных процессах и международное сотрудничество таможенных органов Электрическая система, датчики

Электрическая система, датчики Культура родного края

Культура родного края Подготовили: студенты 4 курса ФТД Т-114 Галибина Любовь и Карпенко Татьяна

Подготовили: студенты 4 курса ФТД Т-114 Галибина Любовь и Карпенко Татьяна  Загадки о насекомых Подготовила учитель начальных классов Чермошенцева Е.А.

Загадки о насекомых Подготовила учитель начальных классов Чермошенцева Е.А.  Религии Китая. Часть I

Религии Китая. Часть I Ouvrier en 1900

Ouvrier en 1900 Бинарные отношения

Бинарные отношения Средняя скорость

Средняя скорость The baseband bane

The baseband bane Реконструкция аккумуляторного участка

Реконструкция аккумуляторного участка Изречение и изказване BULB322 Добрият български език Есенен семестър 2008/09 г. Програма “Език и литература” НБУ © Б. Георгиев

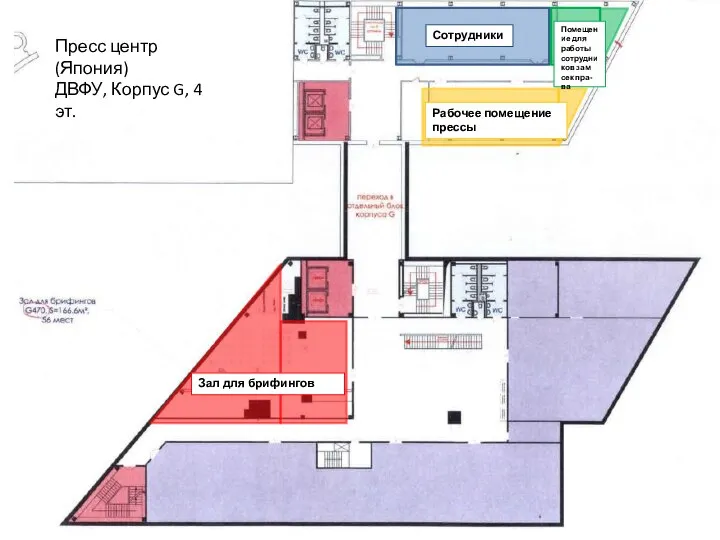

Изречение и изказване BULB322 Добрият български език Есенен семестър 2008/09 г. Програма “Език и литература” НБУ © Б. Георгиев Пресс центр (Япония)

Пресс центр (Япония)