Содержание

- 2. Назначение Кэш-память предназначена для хранения блоков данных и команд программы, выполняемой процессором в текущий момент времени

- 3. Назначение Кэш-память должна иметь средства: - реализующие процедуры обмена данными между оперативной памятью и кэш; -

- 4. Концепция обмена данными между ОП и кэшем В компьютере имеется относительно большая и медленная ОП вместе

- 5. Концепция обмена данными между ОП и кэшем Если слово находится в кэш, оно поступает в ЦП

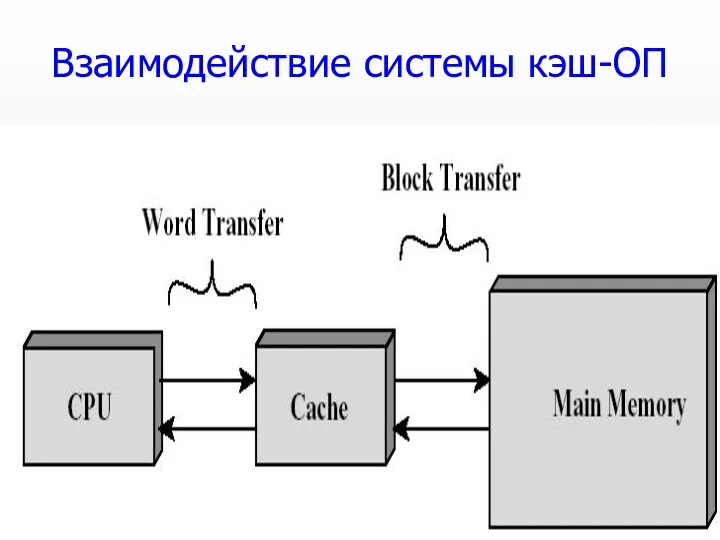

- 6. Взаимодействие системы кэш-ОП

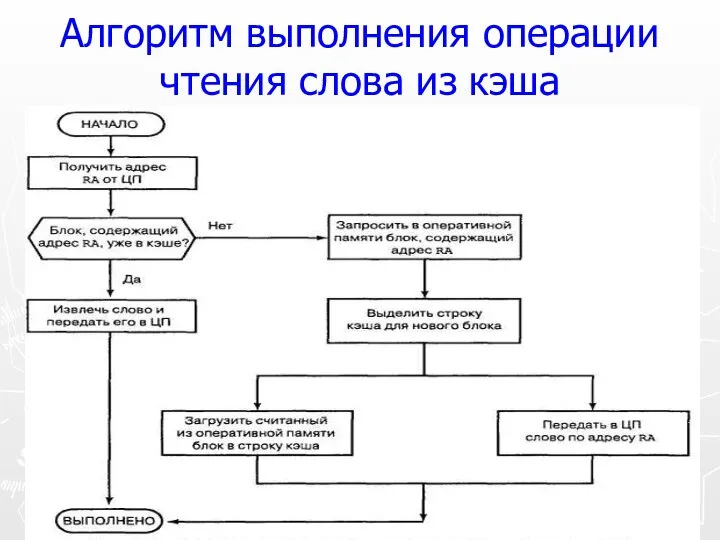

- 7. Алгоритм выполнения операции чтения слова из кэша

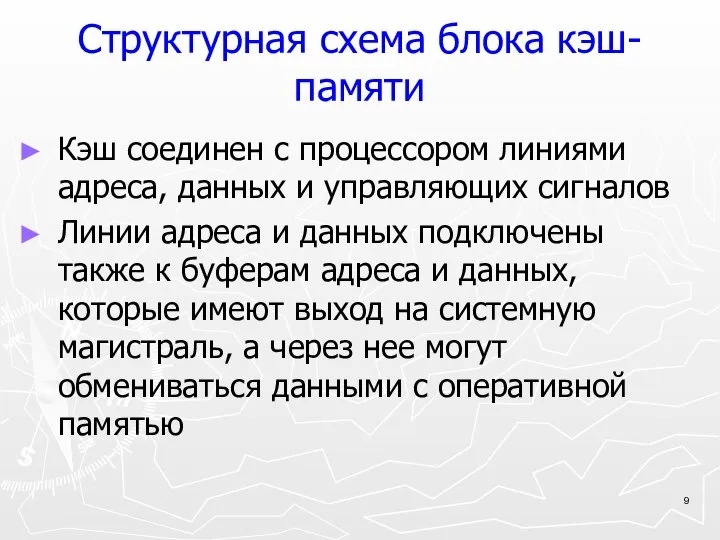

- 8. Структурная схема блока кэш-памяти

- 9. Структурная схема блока кэш-памяти Кэш соединен с процессором линиями адреса, данных и управляющих сигналов Линии адреса

- 10. Структурная схема блока кэш-памяти Если интересующие процессор данные уже находится в кэше, буферы адреса и данных

- 11. Понятие о локализации ссылок (locality reference) Обращения к памяти в процессе выполнения фрагмента программы имеют тенденцию

- 13. Оперативная память состоит из 2n адресуемых слов Каждое слово имеет уникальный адрес В системе кэш -

- 14. Логическая организация системы кэш - ОП Кэш состоит из К слотов (линий) по N слов каждый

- 15. Логическая организация системы кэш - ОП Производительность системы кэш - ОП и компьютера в целом возрастает,

- 16. Функционирование кэш Когда процессор формирует физический адрес обращения к памяти, этот адрес сначала посылается в кэш

- 17. Функционирование кэш Если процессор не находит адресуемого слова в кэше, блок ОП, содержащий затребованное процессором слово,

- 18. Стратегия замещения При возникновении промаха контроллер кэш-памяти должен выбрать подлежащий замещению блок Используются три основных стратегии,

- 19. Стратегия замещения Random -случайно выбранный блок ; LFU (least frequently used) - наименее используемый блок ;

- 20. Стратегия замещения Random -случайно выбранный блок Блок-кандидат на замещение выбирается случайно; происходит замещение этого блока новым,

- 21. Стратегия замещения LFU -наименее используемый блок Для замещения выбирается блок в КЭШе, к которому было наименьшее

- 22. Стратегия замещения LFU -наименее используемый блок Недостатки: - Блок, загруженный в кэш последним имеет, наименьшее число

- 23. Стратегия замещения LRU - наиболее давно использовавшийся блок Метод LRU уменьшает вероятность выбрасывания блоков данных, которые

- 24. Стратегия замещения LRU - наиболее давно использовавшийся блок Идея применения этого метода состоит в том, что

- 25. Стратегия замещения LRU - наиболее давно использовавшийся блок Одна из возможных реализаций этого механизма состоит в

- 26. Стратегия записи Когда процессор выполняет процедуру записи слова в память, то для обеспечения нормальной работы системы

- 27. Стратегия записи Write through - сквозная запись При сквозной записи слово одновременно изменяется как в кэш,

- 28. Стратегия записи Преимущество - содержимое слотов кэш-памяти всегда соответствует содержимому блоков ОП Недостаток - снижение производительности

- 29. Стратегия записи Write back - обратная запись При использовании стратегии обратной записи минимизируется количество обращений к

- 30. Write back В случае, если содержимое блока в кэше было изменено, бит модификации соответствующего слота устанавливается

- 31. Write back Лишь при выполнении алгоритма замещения слот, бит модификации которого установлен в единичное состояние, переписывается

- 32. Write back Преимущество - блок ОП может находится в кэш-памяти длительное время и процессор имеет возможность

- 33. Стратегия записи В современных процессорах наиболее часто используется механизм обратной записи, хотя многие из них могут

- 34. Функции отображения Так как количество строк кэша меньше, чем блоков ОП, необходим механизм отображения блоков ОП

- 35. Функции отображения Кэш прямого отображения Ассоциативная функция отображения Секционированная (наборно) ассоциативная функция отображения.

- 36. Исходные данные к рассматриваемым примерам Размер кэш-памяти составляет 16 Кбайт Обмен данными между ОП и кэш-памятью

- 37. Архитектура кэш-памяти прямого отображения В кэш прямого отображения (direct-mapping cache ) каждый блок ОП может размещаться

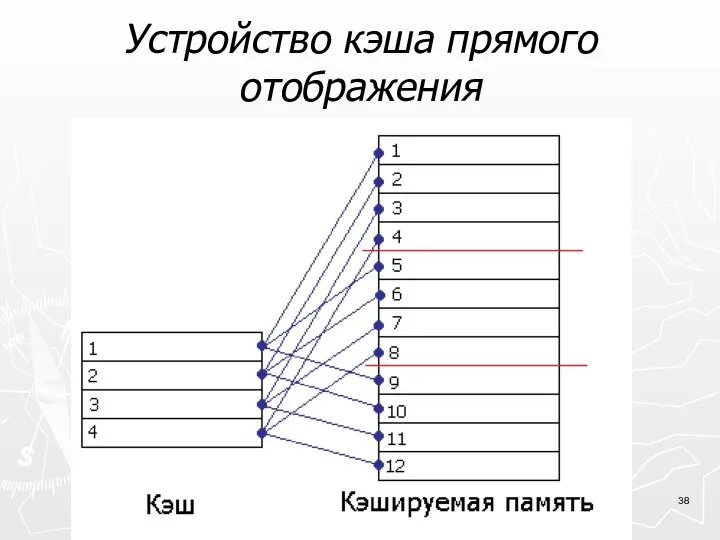

- 38. Устройство кэша прямого отображения

- 39. Кэш прямого отображения Кэшируемая оперативная память разбивается на фреймы Размер каждого фрейма соответствует емкости кэш-памяти Предположим,

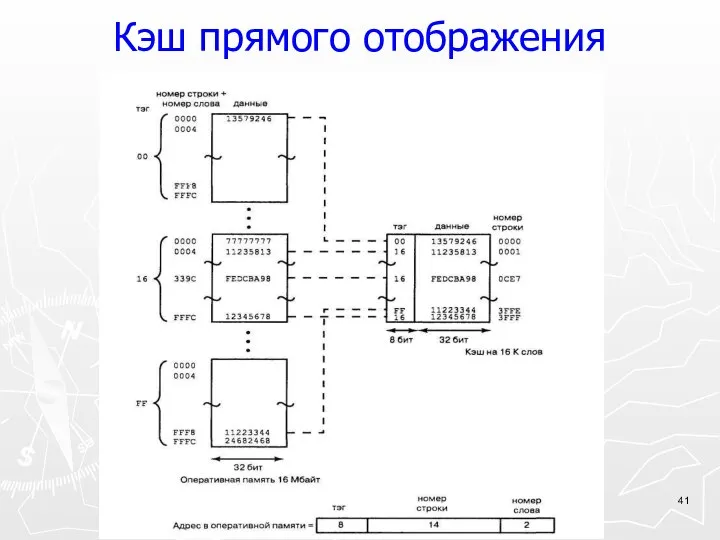

- 40. Кэш прямого отображения В рассматриваемом примере, когда размер кэш-памяти равен 16 Кбайт, а емкость ОП составляет

- 41. Кэш прямого отображения

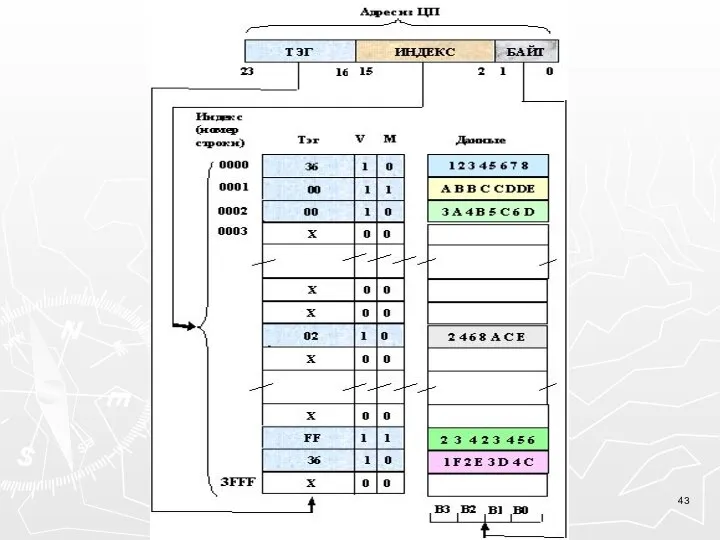

- 44. Кэш прямого отображения По индексу в кэш выбирается строка (слот) – 14 разрядов Происходит сравнение 8-разрядного

- 45. Кэш прямого отображения Кроме адресной части тега с каждым слотом связаны биты признаков действительности и модификации

- 46. Кэш прямого отображения При обращении к памяти процессор может сформировать два типа запросов: чтение и запись

- 47. Кэш прямого отображения Если произошло попадание по чтению, то запрашиваемый процессором байт данных загружается в процессор

- 48. Кэш прямого отображения Когда процессор генерирует запрос записи данных в память, то сначала происходит обращение к

- 49. Кэш прямого отображения Преимущества - Простая схемная реализация; - Невысокая стоимость по сравнению с другими архитектурами

- 50. Недостаток кэш прямого отображения Однако емкость КП при этом используется не в полной мере: несмотря на

- 51. Ассоциативный кэш В ассоциативном кэше (Associative-mapping cache) блок данных может загружаться в любой свободный слот Такая

- 52. Ассоциативный кэш В полностью ассоциативной кэш-памяти максимально используется весь ее объем: вытеснение сохраненной в КП информации

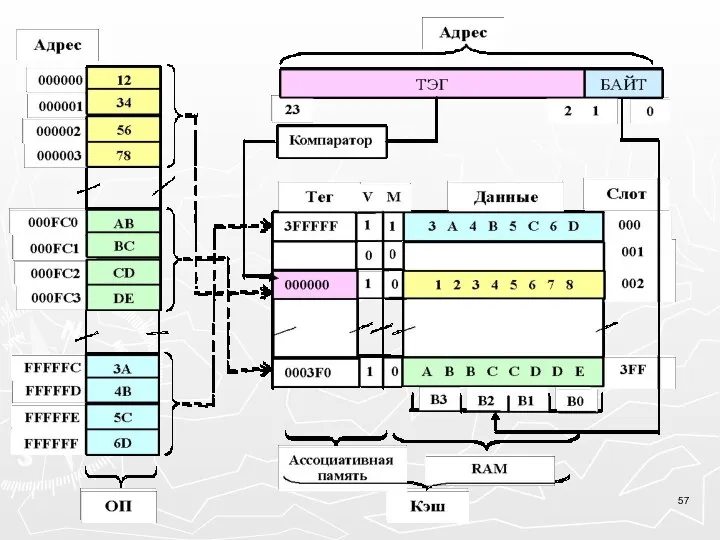

- 53. Ассоциативный кэш

- 54. Ассоциативный кэш Структурная схема ассоциативного кэша, представляет собой комбинацию ассоциативной памяти и памяти с произвольным доступом

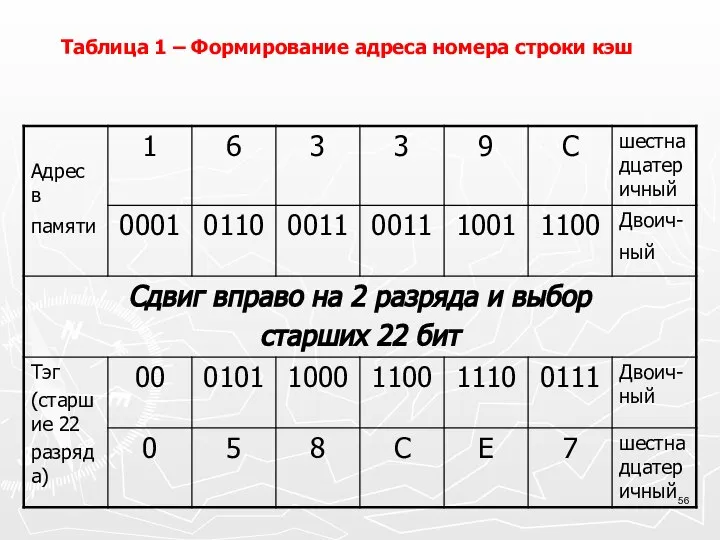

- 55. Ассоциативный кэш В каждой строке кэша нужно хранить помимо блока данных длиной в 4 байт (32

- 56. Таблица 1 – Формирование адреса номера строки кэш

- 58. Ассоциативный кэш Когда процессор формирует адрес обращения к памяти, то старшие 22 разряда этого адреса загружаются

- 59. Ассоциативный кэш Преимущество - Позволяют так организовать обновление строк, что вероятность обнаружения нужного слова данных в

- 60. Секционированный ассоциативный кэш Такой кэш является дальнейшим совершенствованием кэша прямого отображения Решение проблемы кэша прямого отображения

- 61. Секционированный ассоциативный кэш Например, секционированный ассоциативный кэш, имеющий w наборов памяти, может хранить w блоков данных

- 62. Архитектура двухканального секционно- ассоциативного кэша

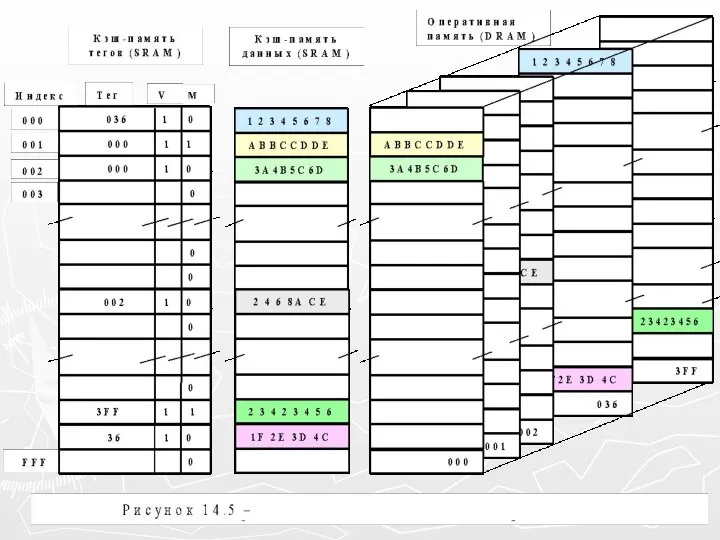

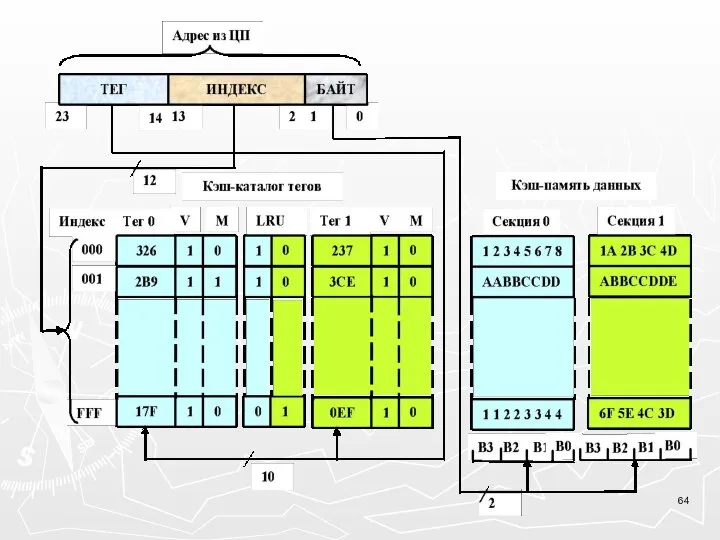

- 63. Секционированная ассоциативная функция отображения Для хранения данных в таком кэше используются две секции (секция 0 и

- 65. Секционированная ассоциативная функция отображения Такой кэш должен содержать два каталога тегов Каталог Тег 0 используется при

- 66. Секционированная ассоциативная функция отображения Для реализации алгоритма замещения используются два служебных бита, обозначенных на рисунке LRU

- 67. Секционированная ассоциативная функция отображения Значение индекса в адресе обращения процессора определяет две строки в каталоге тегов

- 68. Секционированная ассоциативная функция отображения В противном случае затребованный процессором блок данных загружается из ОП При загрузке

- 69. Секционированная ассоциативная функция отображения Замещаемый блок из кэша записывается в ОП, если он был модифицирован в

- 70. Секционированная ассоциативная функция отображения Если ЦП сформировал запрос по записи, то в случае кэш-попадания запись данных

- 71. Секционированный ассоциативный кэш Секционированная ассоциативная кэш-память широко используется в современных процессорах Так в процессорах Intel P6

- 72. Обеспечение согласованности кэш-памяти микропроцессоров в мультипроцессорных системах Рассмотрим особенности работы кэш-памяти в том случае, когда одновременно

- 73. Структура мультипроцессорной системы с общей оперативной памятью

- 74. Предположим, что МП А загрузил некоторую строку данных из ОЗУ в свою внутреннюю КП и изменил

- 75. сквозная запись, которая подразумевает, что как только изменилась информация во внутренней кэш-памяти, эта же информация копируется

- 76. Для обеспечения согласованности (когерентности) памяти в мультипроцессорных системах используются аппаратные механизмы, позволяющие решить эту проблему Такие

- 77. Существует два класса протоколов когерентности: протоколы на основе справочника (directory based): информация о состоянии блока физической

- 78. В мультипроцессорных системах с общей памятью наибольшей популярностью пользуются протоколы наблюдения, поскольку для опроса состояния кэшей

- 79. Протокол MESI Этот протокол использует 4 признака состояния строки кэш-памяти микропроцессора, по первым буквам которых и

- 80. Протокол MESI 2 исключительная копия (Exclusive): информация, содержащаяся в кэше А, содержится еще только в оперативной

- 81. Пусть блок кэш-памяти находится в состоянии Modified, то есть достоверная информация находится только в кэш-памяти данного

- 82. Если строка кэш-памяти находилась в состоянии Invalid, то есть информация в ней была недостоверной, то по

- 84. Скачать презентацию

Архитектура процессоров Intel и AMD

Архитектура процессоров Intel и AMD Нарушения углеводного обмена

Нарушения углеводного обмена Особливості складання основних видів службової документації

Особливості складання основних видів службової документації Геометрические параметры деталей. Основные понятия

Геометрические параметры деталей. Основные понятия Выполнила: Блинова Ксения ученица 8Бкласса Научный руководитель: Васильева Татьяна Николаевна

Выполнила: Блинова Ксения ученица 8Бкласса Научный руководитель: Васильева Татьяна Николаевна Контрактная система Тульской области

Контрактная система Тульской области ГУЗ «Пермский краевой онкологический диспансер» ГОУ ВПО «Пермская государственная медицинская академия им. академика Е.А. Вагне

ГУЗ «Пермский краевой онкологический диспансер» ГОУ ВПО «Пермская государственная медицинская академия им. академика Е.А. Вагне Разработала: преподаватель высшей категории Зеленкина Т.М.

Разработала: преподаватель высшей категории Зеленкина Т.М. Обязанности должностных лиц медицинской службы соединения по медицинскому снабжению

Обязанности должностных лиц медицинской службы соединения по медицинскому снабжению На Дне Презентацию от имени ученика выполнили Кулемина Д. и Романова А. ГОУ ВПО «Поволжская государственная социально-гуманитарн

На Дне Презентацию от имени ученика выполнили Кулемина Д. и Романова А. ГОУ ВПО «Поволжская государственная социально-гуманитарн Дроби. Зажжение олимпийского огня 7 февраля 2014 года, город Сочи

Дроби. Зажжение олимпийского огня 7 февраля 2014 года, город Сочи Кадастровое деление территории

Кадастровое деление территории Культура Месопотамии

Культура Месопотамии Основные направления в пм

Основные направления в пм Антибиотики

Антибиотики  Презентация на тему "Архитектура барокко"

Презентация на тему "Архитектура барокко" Жан-Батист Мольер (биография)

Жан-Батист Мольер (биография) Święty Łukasz Ewangelista

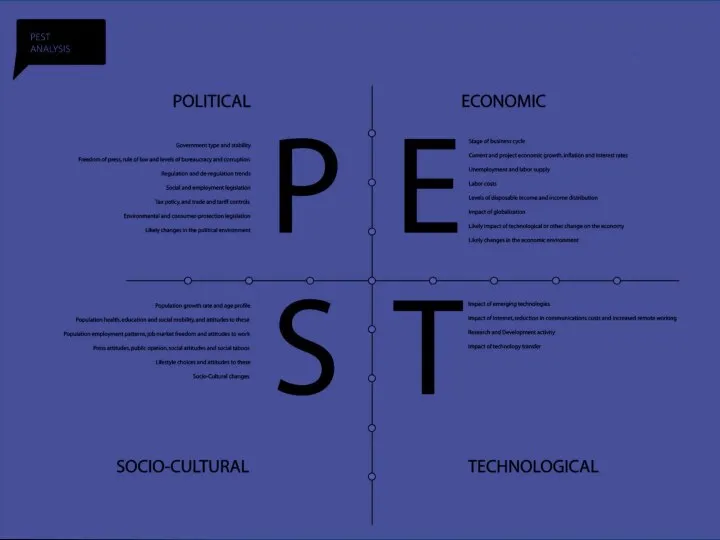

Święty Łukasz Ewangelista PEST Analysis

PEST Analysis Government of the Russian Federation

Government of the Russian Federation Устройство защитного отключения (УЗО)

Устройство защитного отключения (УЗО) Финансовая политика государства

Финансовая политика государства Помехи в каналах связи

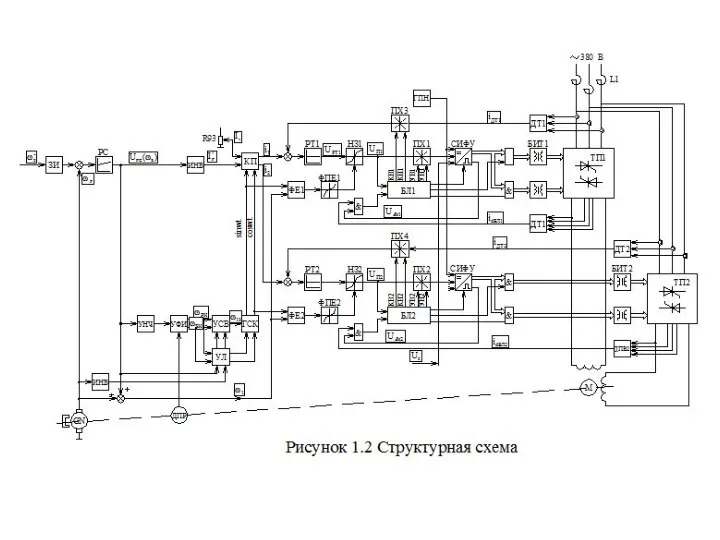

Помехи в каналах связи Структурная схема ЭТА1-02

Структурная схема ЭТА1-02 IDU0075 Veebiteenused

IDU0075 Veebiteenused Моя родина Армения

Моя родина Армения АРХИТЕКТУРА Архитектура г. Омска Приложение к хрестоматии «Музыка, театр, изобразительное искусство Омского Прииртышья»

АРХИТЕКТУРА Архитектура г. Омска Приложение к хрестоматии «Музыка, театр, изобразительное искусство Омского Прииртышья» Кратчайшие пути, максимальные потоки и минимальные разрезы на орграфах

Кратчайшие пути, максимальные потоки и минимальные разрезы на орграфах