Содержание

- 2. Два основных режима: Real Address Mode (реальный режим); Protected Virtual Address Mode (защищенный режим). Новые возможности

- 3. Добавлены новые флаги: ID Flag (ID, 21 бит) – Если возможно программно устанавливать и сбрасывать этот

- 4. Расположение дескрипторных таблиц определяется регистрами процессора: GDTR (Global Descriptor Table Register), IDTR (Interrupt Descriptor Table Register),

- 5. Сегментная адресация в защищенном режиме

- 7. Скачать презентацию

Два основных режима:

Real Address Mode (реальный режим);

Protected Virtual Address Mode (защищенный

Два основных режима:

Real Address Mode (реальный режим);

Protected Virtual Address Mode (защищенный

Новые возможности защищенного режима:

дополненный регистровый файл;

новые механизмы сегментации и страничной адресации;

режим виртуального процессора 8086 - Virtual 8086 Mode (V86);

добавления к системе команд.

Новый дополнительный режим - System Management Mode (режим системного управления)

Набор РОН включает в себя:

регистры 16-разрядных процессоров 8086/8088, но в 32 бита.

К обозначениям регистров добавлена приставка E (Extended - расширенный):

EAX, EBX, ECX, EDX, ESI, EDI, EBP, ESP.

Возможно обращение к младшим 16 разрядам – AX, BX,

а также отдельно к младшим и старшим байтам – AL, AH.

Регистр состояния процессора FLAGS расширен до 32 разрядов и обозначается – EFLAGS.

Флаги 16-разрядных процессоров с 0 по 11 разряд занимают такое же положение в EFLAGS.

Добавлены новые флаги:

ID Flag (ID, 21 бит) – Если возможно программно

Добавлены новые флаги:

ID Flag (ID, 21 бит) – Если возможно программно

Virtual Interrupt Pending (VIP, 20 бит) – Указывает на то, что остались прерывания, ожидающие обработку. Устанавливается и сбрасывается программно, процессор только считывает его значение.

Virtual Interrupt Flag (VIF, 19 бит) – Образ флага IF для режима V86.

Alignment Check (AC, 18 бит) – Флаг контроля выравнивания. При установке этого флага во время обращении к невыровненному операнду возникает исключение.

Virtual-8086 Mode (VM, 17 бит) – Включает/выключает режим V86 в защищенном режиме.

Resume Flag (RF, 16 бит) – Флаг возобновления исполнения при отладке.

Nested Task (NT, 14 бит) – Флаг вложенной задачи. Устанавливается, когда текущая задача связана с прерванной задачей, очищается, если такой связи нет.

I/O Privilege Level (IOPL, 12-13 биты) – определяет уровень привилегий ввода/вывода для текущей задачи.

Сегментные регистры – CS, SS, DS, ES – 16 бит.

FS и GS – дополнительные сегментные регистры данных.

В реальном режиме сегментные регистры определяют 64Кб сегменты.

В защищенном режиме сегментные регистры содержат указатели (т.н. селекторы) на описатели сегментов (64-разрядные дескрипторы), находящиеся в памяти в виде таблиц.

Дескриптор содержит:

базовый адрес,

предельный размер сегмента,

атрибуты сегмента (права доступа).

Существуют две обязательные дескрипторные таблицы:

глобальная (GDT),

дескрипторная таблица прерывания (IDT),

а также множество (до 8192) локальных дескрипторных таблиц (LDT), из которых в один момент времени процессору доступна только одна.

Расположение дескрипторных таблиц определяется регистрами процессора:

GDTR (Global Descriptor Table Register),

IDTR (Interrupt

Расположение дескрипторных таблиц определяется регистрами процессора:

GDTR (Global Descriptor Table Register),

IDTR (Interrupt

LDTR (Local Descriptor Table Register).

Регистры GDTR и IDTR - 6-байтные – содержат 32 бита линейного базового адреса дескрипторной таблицы и 16 бит предела таблицы.

Программно доступная часть регистра LDTR - 16 бит – селектор LDT.

Дескрипторы LDT находятся в GDT.

Но, чтобы не обращаться каждый раз к GDT, в процессоре имеется теневая (программно недоступная) часть регистра LDTR, в которую процессор помещает дескриптор LDT при каждой перегрузке селектора в регистре LDTR.

Значение сегментного регистра (селектор) содержит:

индекс дескриптора в дескрипторной таблице;

бит, определяющий, к какой дескрипторной таблице производится обращение (LDT или GDT);

запрашиваемые права доступа к сегменту.

селектор выбирает дескрипторную таблицу

↓

выбирает дескриптор из таблицы

↓

по дескриптору определяется положение сегмента в линейном пространстве памяти.

Обращение к дескрипторным таблицам происходит только при загрузке селектора в сегментный регистр

↓

процессор помещает дескриптор в теневую часть сегментного регистра.

При формировании линейного адреса дескриптор сегмента процессору уже известен.

Сегментная адресация в защищенном режиме

Сегментная адресация в защищенном режиме

Поговорим об ушедшем лете

Поговорим об ушедшем лете  Культура Руси XVII века

Культура Руси XVII века Проект «Региональный студенческий Центр боевых искусств в Республике Марий Эл»

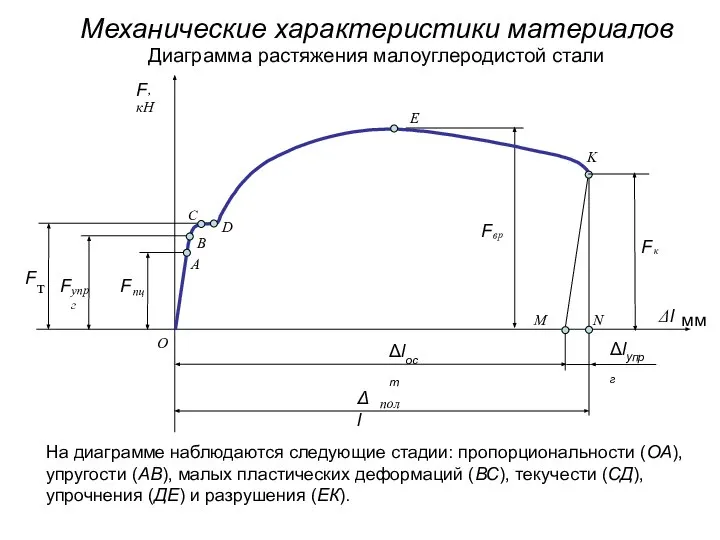

Проект «Региональный студенческий Центр боевых искусств в Республике Марий Эл» Механические характеристики материалов. Диаграмма растяжения малоуглеродистой стали

Механические характеристики материалов. Диаграмма растяжения малоуглеродистой стали Шахматные игры с ладьей. Часть 2

Шахматные игры с ладьей. Часть 2 Моделирование.pptx

Моделирование.pptx Патофизиология и ее место среди медико-биологических и клинических наук

Патофизиология и ее место среди медико-биологических и клинических наук Мы против СПИДа Подготовила: студентка 1го курса группы 444-к Моргун Марина

Мы против СПИДа Подготовила: студентка 1го курса группы 444-к Моргун Марина Программирование линейных алгоритмов

Программирование линейных алгоритмов Цыпленок - презентация для начальной школы

Цыпленок - презентация для начальной школы Презентация "Школа искусств" - скачать презентации по МХК

Презентация "Школа искусств" - скачать презентации по МХК Правовая охрана программ и данных

Правовая охрана программ и данных  УРОВНИ ОРГАНИЗАЦИИ ЖИЗНИ

УРОВНИ ОРГАНИЗАЦИИ ЖИЗНИ Усыновление. От знакомства до решения суда. Работа с родителями. Дом ребёнка № 20 г. Москва Воспитатель Антонова И.А.

Усыновление. От знакомства до решения суда. Работа с родителями. Дом ребёнка № 20 г. Москва Воспитатель Антонова И.А.  Здоровьесберегающие технологии на уроках изобразительного искусства

Здоровьесберегающие технологии на уроках изобразительного искусства Органы, осуществляющие предварительное следствие Выполнила Тарасенко Александра, студент группы Ю101

Органы, осуществляющие предварительное следствие Выполнила Тарасенко Александра, студент группы Ю101 Виды соединений

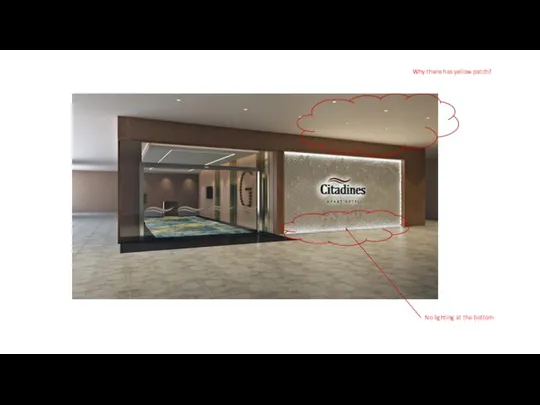

Виды соединений Public area mark up

Public area mark up Презентация на тему "Воспитательная система МБОУ «Каратузская СОШ»" - скачать презентации по Педагогике

Презентация на тему "Воспитательная система МБОУ «Каратузская СОШ»" - скачать презентации по Педагогике Турнир новичка 2015-16-01

Турнир новичка 2015-16-01 Идентификация контролируемых товаров и технологий Статья 24. Идентификация контролируемых товаров и технологий

Идентификация контролируемых товаров и технологий Статья 24. Идентификация контролируемых товаров и технологий   История становления и развития социологии

История становления и развития социологии Оптимизация и измерение производительности

Оптимизация и измерение производительности Основные термины и определения. Метод сечений

Основные термины и определения. Метод сечений Греческое: искусство украшать. Греческое: искусство украшать.

Греческое: искусство украшать. Греческое: искусство украшать. Theory of International Relations

Theory of International Relations фракталы, нелинейная динамика

фракталы, нелинейная динамика Основы SQL. Описание отношений, доменов, ограничений целостности, представлений данных.

Основы SQL. Описание отношений, доменов, ограничений целостности, представлений данных.