Обмен в режиме прерывания. Программные и аппаратные средства, обеспечивающие обмен в режиме прерывания

Содержание

- 2. Организация прерываний Одной из разновидностей программно-управляемого обмена данными с ВУ в микрокомпьютере является обмен с прерыванием

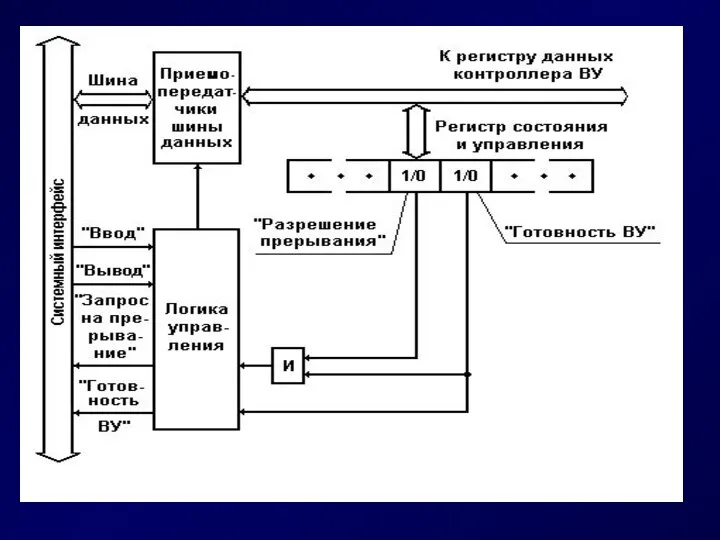

- 3. Действия, выполняемые при этом процессором, как правило, те же, что и при обращении к подпрограмме. Только

- 5. Обычно задача сохранения содержимого счетчика команд и регистра состояния процессора возлагается на аппаратные средства обработки прерывания.

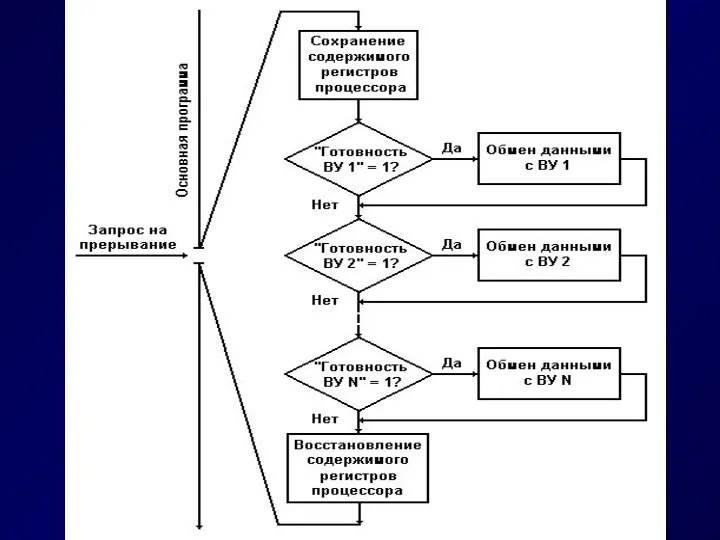

- 6. Существуют два основных способа идентификации ВУ, запросивших обслуживания: программный опрос регистров состояния (разряд «Готовность ВУ») контроллеров

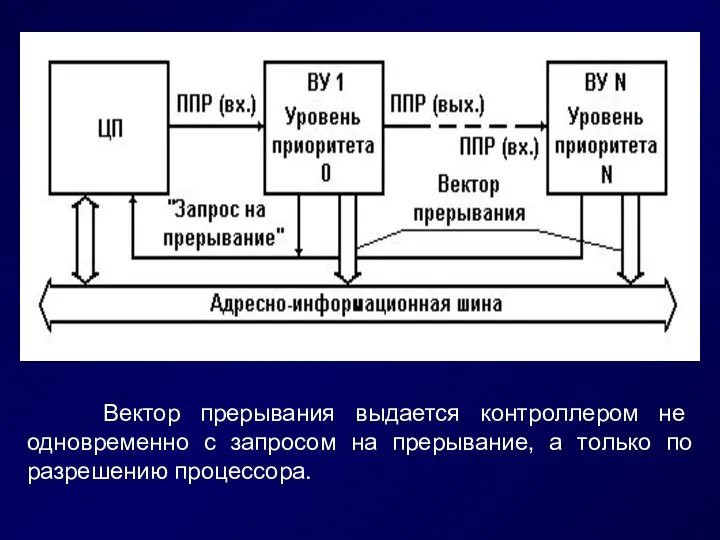

- 8. При организации системы прерываний с использованием векторов прерываний ВУ, запросившее обслуживания, само идентифицирует себя с помощью

- 9. Вектор прерывания выдается контроллером не одновременно с запросом на прерывание, а только по разрешению процессора.

- 10. Аппаратный опрос готовности ВУ производится гораздо быстрее, нежели программный. Но если обслуживания запросили одновременно два или

- 11. Маскируемые прерывания

- 12. БИС программируемого контроллера прерываний Intel 8259A Контроллер прерываний (ПКП) представляет собой устройство, реализующее до восьми уровней

- 13. Маскируемые прерывания

- 14. Маскируемые прерывания

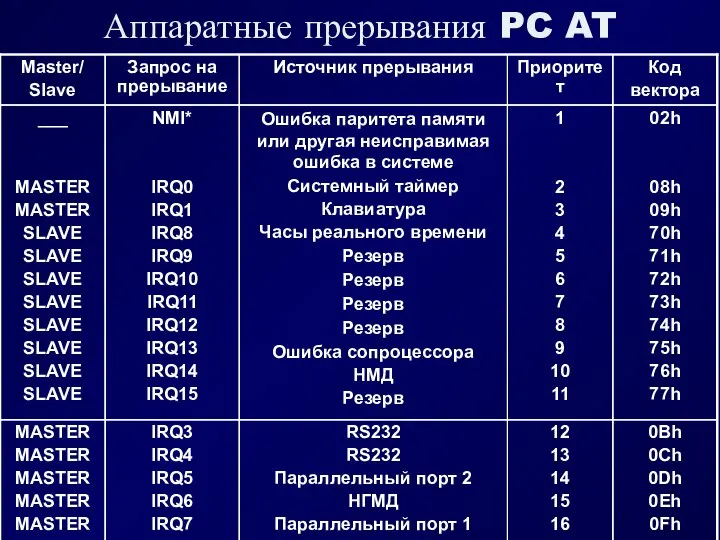

- 15. Аппаратные прерывания PC AT 0Bh 0Ch 0Dh 0Eh 0Fh 12 13 14 15 16 RS232 RS232

- 16. Маскируемые прерывания

- 17. Маскируемые прерывания

- 19. Маскируемые прерывания

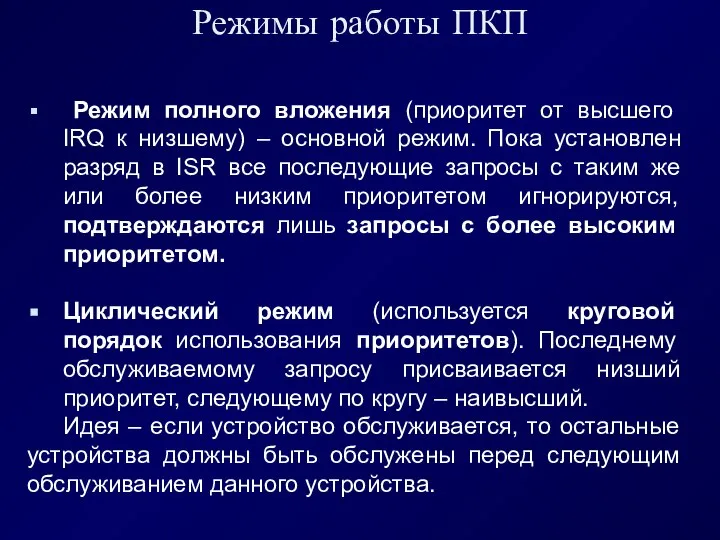

- 20. Режимы работы ПКП Режим полного вложения (приоритет от высшего IRQ к низшему) – основной режим. Пока

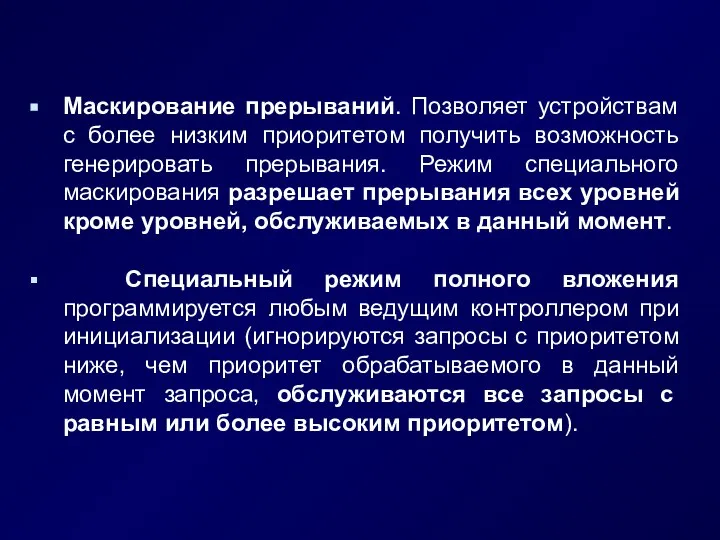

- 21. Маскирование прерываний. Позволяет устройствам с более низким приоритетом получить возможность генерировать прерывания. Режим специального маскирования разрешает

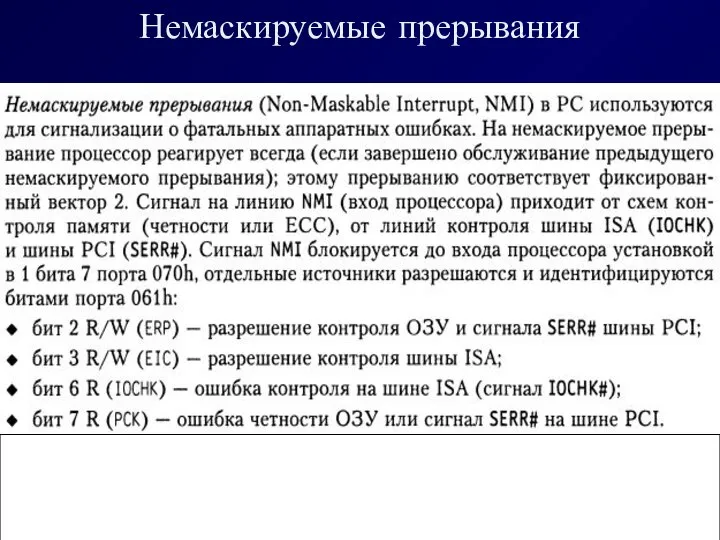

- 22. Немаскируемые прерывания

- 23. Прерывания могут быть внешними и внутренними. Внешние прерывания относятся, к непланируемым прерываниям. Внутренние прерывания возникают внутри

- 24. Таблица векторов прерываний (Таблица дескрипторов прерываний ) (англ.) (англ. Interrupt Descriptor Table, IDT) используется в x86

- 25. Организация прямого доступа к памяти Одним из способов обмена данными с ВУ является обмен в режиме

- 26. Организация прямого доступа к памяти Необходимость реализации в микрокомпьютере обмена данными в режиме ПДП вызывается двумя

- 27. В целях сокращения количества линий в шинах микрокомпьютера контроллер ПДП подключается к памяти посредством шин адреса

- 28. Наиболее распространенным является ПДП с «захватом цикла» и принудительным отключением процессора от шин системного интерфейса. Для

- 29. Применение в компьютере обмена данными с ВУ в режиме ПДП всегда требует предварительной подготовки, а именно:

- 31. Скачать презентацию

История развития телевидения как средства массовой информации

История развития телевидения как средства массовой информации Духовная культура

Духовная культура  Проектно-исследовательская работа «Народная кукла-мотанка»

Проектно-исследовательская работа «Народная кукла-мотанка» Гастрономический туризм

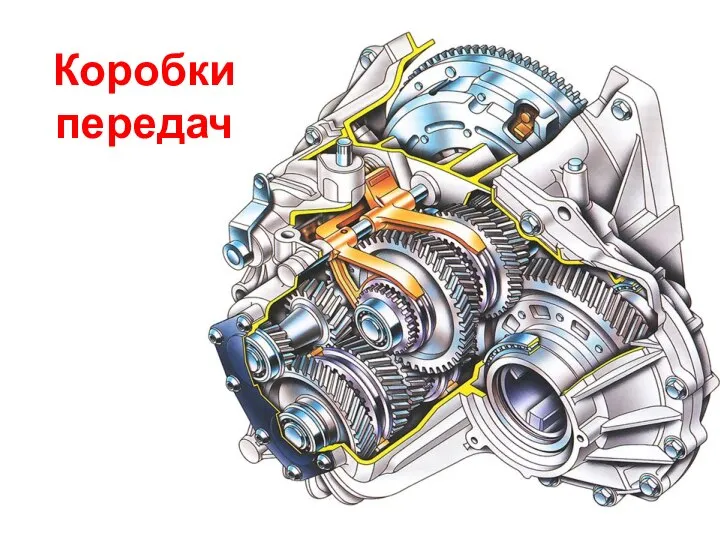

Гастрономический туризм Коробки передач

Коробки передач Презентация "Опера. Самый значительный жанр вокальной музыки" - скачать презентации по МХК

Презентация "Опера. Самый значительный жанр вокальной музыки" - скачать презентации по МХК Презентация к уроку математики Тема урока: Случаи сложения вида 37+53 Учитель Николаеве Е.В. МОУ СОШ сУрицкое

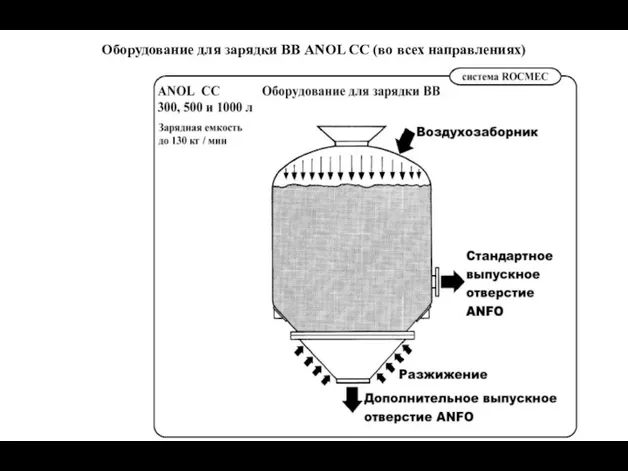

Презентация к уроку математики Тема урока: Случаи сложения вида 37+53 Учитель Николаеве Е.В. МОУ СОШ сУрицкое Оборудование для зарядки ВВ ANOL CC

Оборудование для зарядки ВВ ANOL CC Анализ и выбор методов построения базы знаний в целях идентификации и классификации товаров ТНВЭД ТС "Дерево вывода"

Анализ и выбор методов построения базы знаний в целях идентификации и классификации товаров ТНВЭД ТС "Дерево вывода" Русские народные промыслы

Русские народные промыслы Устное народное творчество

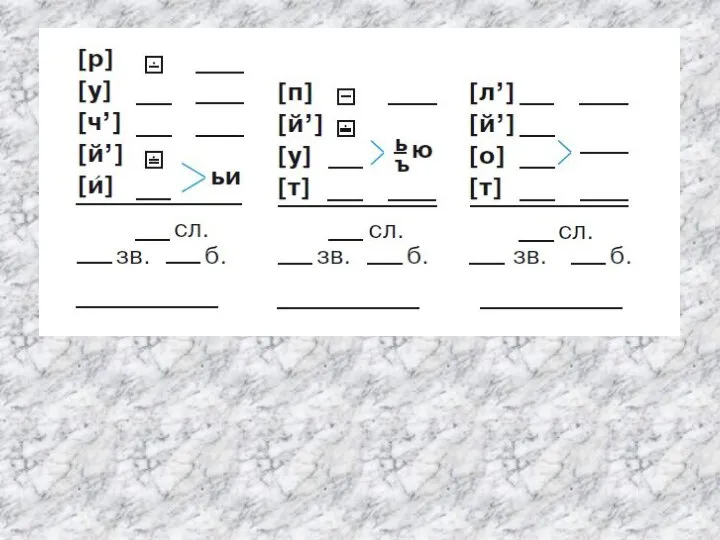

Устное народное творчество Формирование.

Формирование. Tipuri de realități in vizualizarea arhitecturală

Tipuri de realități in vizualizarea arhitecturală Управление формированием и развитием организационной культуры

Управление формированием и развитием организационной культуры Механіка

Механіка Wartość

Wartość Виды и формы бизнеса Подготовил: Ученик 8 класса В Аксёнов Григорий

Виды и формы бизнеса Подготовил: Ученик 8 класса В Аксёнов Григорий  Фазы развития и поражающие факторы чрезвычайных ситуаций природного дорожно-транспортного, взрыво- и пожароопасного характера

Фазы развития и поражающие факторы чрезвычайных ситуаций природного дорожно-транспортного, взрыво- и пожароопасного характера Основы дизайна в полиграфии и издательском деле. Роль цвета в полиграфии. Распространенные ошибки дизайнеров

Основы дизайна в полиграфии и издательском деле. Роль цвета в полиграфии. Распространенные ошибки дизайнеров Романский и готический стиль в архитектуре Западной Европы

Романский и готический стиль в архитектуре Западной Европы Презентация____

Презентация____ Нанотрубки и родственные структуры

Нанотрубки и родственные структуры Тасымалдаушы машиналар

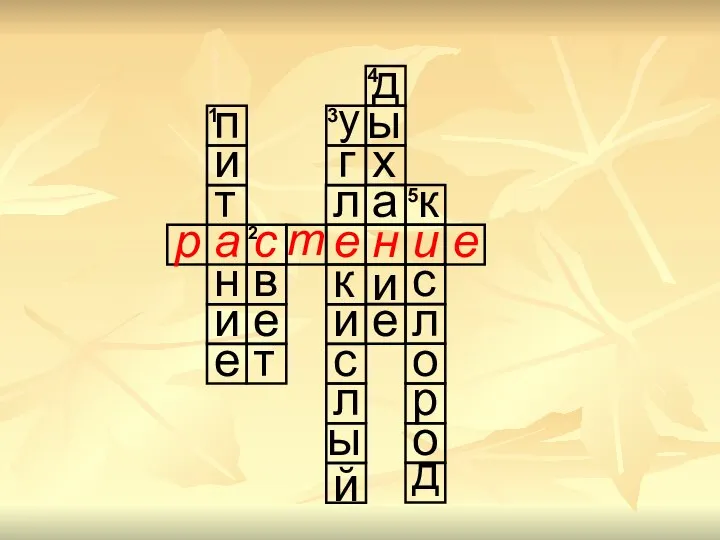

Тасымалдаушы машиналар Растения - презентация для начальной школы_

Растения - презентация для начальной школы_ Искусство учить Учитель истории и обществознания МБНОУ «Лицей №3 (искусств)» Хрупова Анастасия Викторовна

Искусство учить Учитель истории и обществознания МБНОУ «Лицей №3 (искусств)» Хрупова Анастасия Викторовна Китай

Китай Сравнительное правоведение. Чиркин Вениамин Евгеньевич

Сравнительное правоведение. Чиркин Вениамин Евгеньевич Фентези Лига чемпионов football

Фентези Лига чемпионов football