Содержание

- 2. 1. Реализуется обычно на микросхемах DRAM = Dynamic RAM, т.к. они имеют наилучшее сочетание объёма информации

- 3. При записи 1 – заряжаем, 0 – разряжаем При чтении – всегда разряжаем Если был 0,

- 4. Если постоянно читаем, то информация не теряется Иначе, нужна периодическая (раз в 0.01 с) регенерация –

- 5. 2. Производительность Это количество считанных или записанных байт в секунду Н-р, DDR2 SDRAM: до 8 ГБ/с

- 6. Для её роста повышают: быстродействие ячеек разрядность шины данных (до 256 бит!) объём и частоту буфера

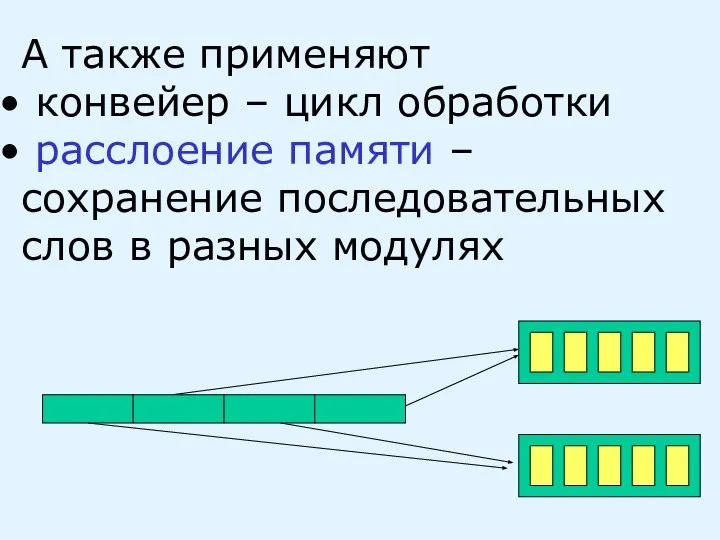

- 7. А также применяют конвейер – цикл обработки расслоение памяти – сохранение последовательных слов в разных модулях

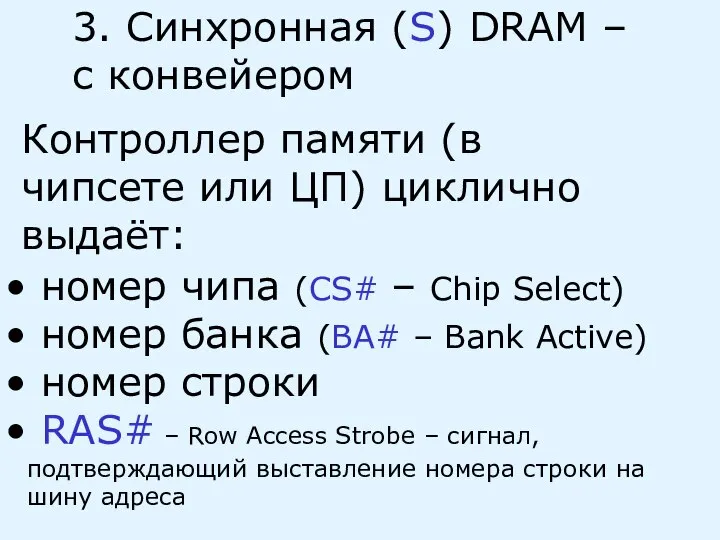

- 8. 3. Синхронная (S) DRAM – с конвейером Контроллер памяти (в чипсете или ЦП) циклично выдаёт: номер

- 9. строка целиком копируется в буфер номер столбца CAS# разрешение чтения или записи чтение ячейки из буфера

- 10. row column row data RAS# CAS# время доступа

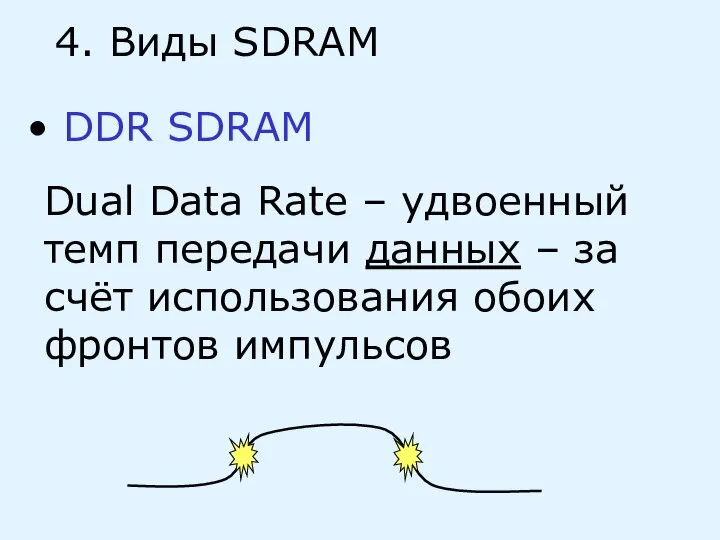

- 11. 4. Виды SDRAM DDR SDRAM Dual Data Rate – удвоенный темп передачи данных – за счёт

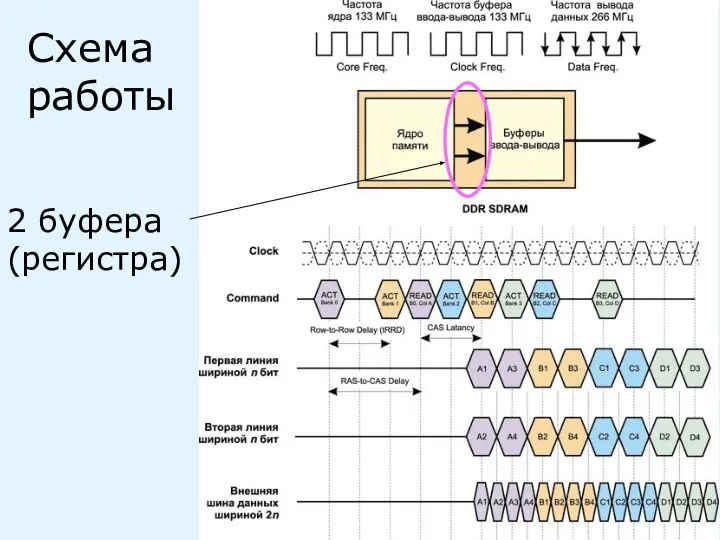

- 12. Схема работы 2 буфера (регистра)

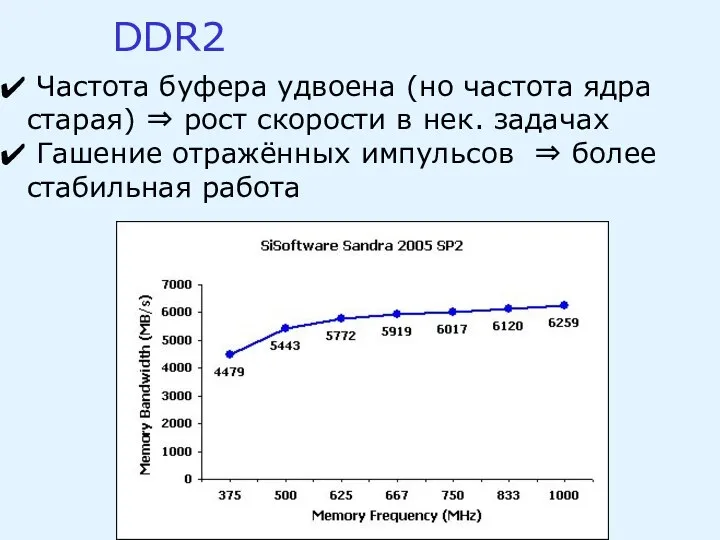

- 13. Частота буфера удвоена (но частота ядра старая) ⇒ рост скорости в нек. задачах Гашение отражённых импульсов

- 14. частота до 533 МГц шина 8 байт 2 канала 2*533*8*2 = 16.6 ГБ/с на систему

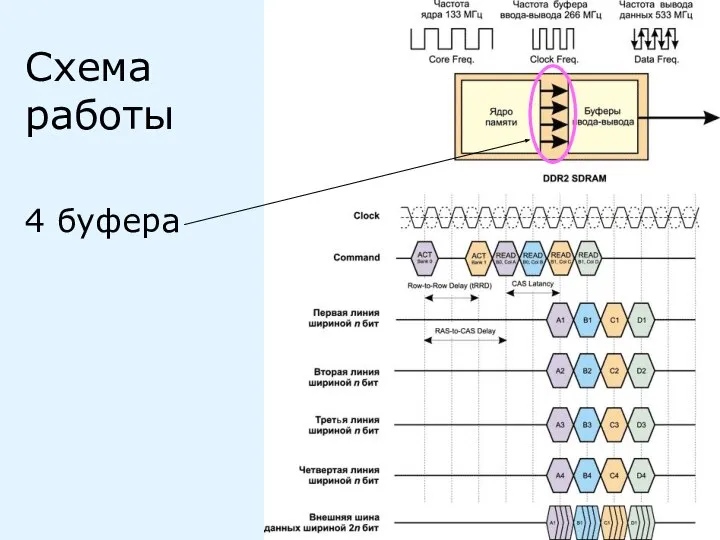

- 15. Схема работы 4 буфера

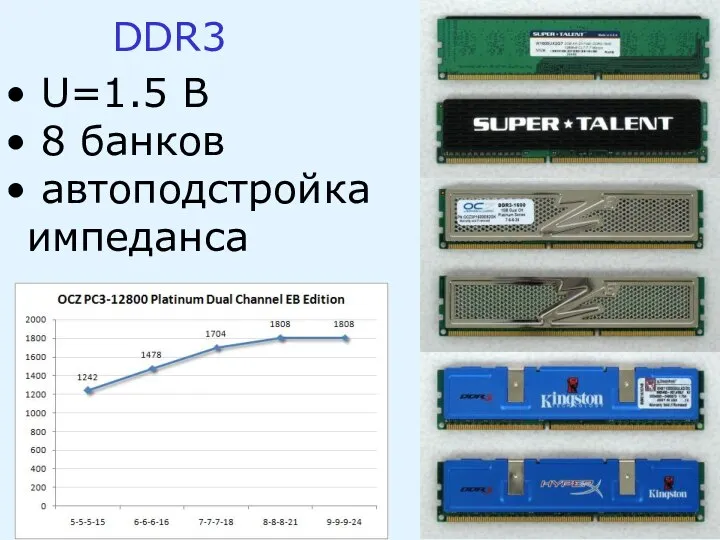

- 16. DDR3 U=1.5 В 8 банков автоподстройка импеданса

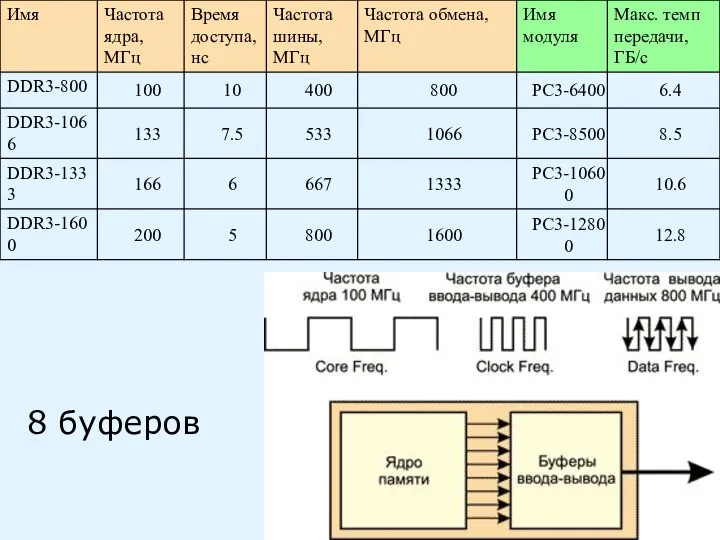

- 17. 8 буферов

- 19. GDDR – ОЗУ для видеокарт GDDR3 ≈ DDR2 GDDR4 ≈ DDR3

- 20. 5. Спецификации DRAM по частоте передачи данных (н-р, DDR2-800 = 2*400 МГц) по пропускной способности (н-р,

- 21. Тайминги (времена задержек в тактах шины памяти) CL (CAS# Latency) CAS# to data delay RAS# to

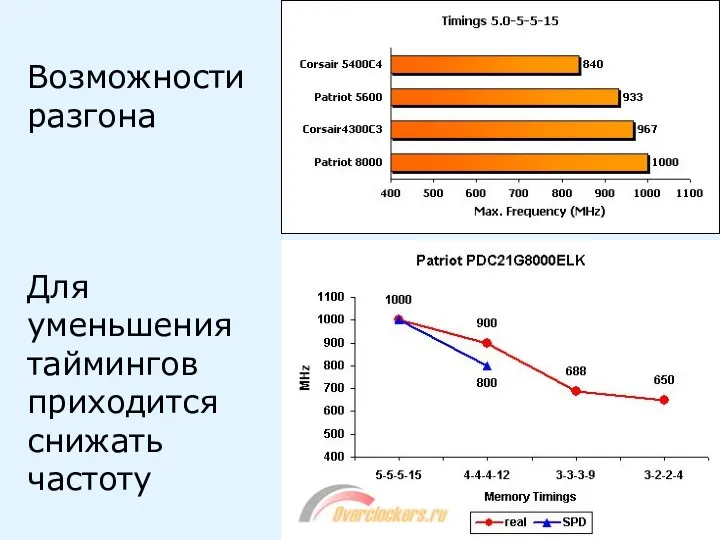

- 22. Возможности разгона Для уменьшения таймингов приходится снижать частоту

- 23. напряжение (1.5–5 В) диапазон температур (-40 – +85 оС) затраты на регенерацию ECC – коды коррекции

- 24. Регистровая – с мультиплексором между контроллером и банками – для роста объёма (н-р, до 24 ГБ).

- 25. 6. Неисправности DRAM неустранимые: сожгли, сломали устранимые: перегрев, окислы, грязь на контактах, отклонения в форме, амплитуде

- 26. Вентиляторы для модулей ОЗУ

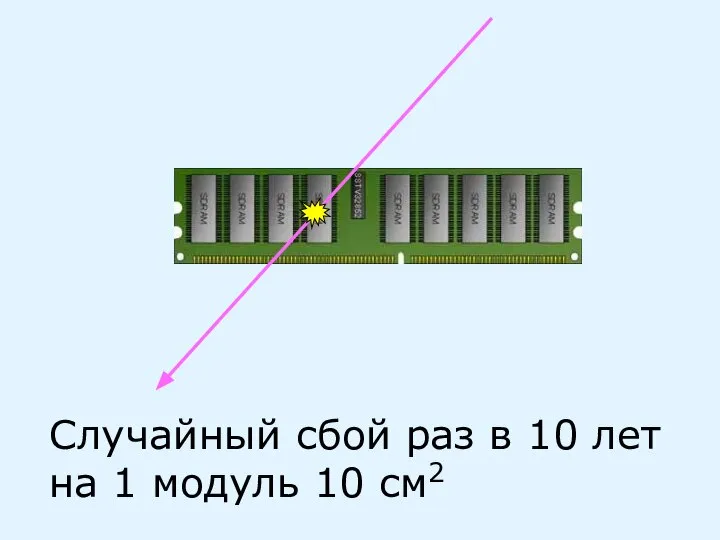

- 27. Труднее всего устранить КЛ. Для полной защиты нужно десятки см свинца и т. д. Обычные ЭВМ

- 28. Случайный сбой раз в 10 лет на 1 модуль 10 см2

- 29. Нужны ли контроль чётности или коррекция (ECC)? Для особо важных ЭВМ – да. При этом производительность

- 31. Скачать презентацию

МАТРЁШКИ Учитель: Стародубцева Р.В.

МАТРЁШКИ Учитель: Стародубцева Р.В. Формы непосредственного осуществления населением местного самоуправления

Формы непосредственного осуществления населением местного самоуправления Объектно-ориентированное программирование

Объектно-ориентированное программирование Презентация на тему "Кафедра холодильных установок" - скачать презентации по Педагогике

Презентация на тему "Кафедра холодильных установок" - скачать презентации по Педагогике Делимость чисел.

Делимость чисел.  Аффективные психические образования

Аффективные психические образования  Презентация по ОТК Тема: Формы и порядок проведения таможенного контроля Студент Юб 02/1403 З.Ф. Ташкыран

Презентация по ОТК Тема: Формы и порядок проведения таможенного контроля Студент Юб 02/1403 З.Ф. Ташкыран  Презентация способы фиксации результатов интервьюирования

Презентация способы фиксации результатов интервьюирования  Я і мая школа. Вучэбныя рэчы. (Тэма 3)

Я і мая школа. Вучэбныя рэчы. (Тэма 3) Motorola solutions learning. Network application interface (NAI). Radio management (RM)

Motorola solutions learning. Network application interface (NAI). Radio management (RM) Занятие 3 Виды и жанры изобразительного искусства

Занятие 3 Виды и жанры изобразительного искусства Согласные звуки З

Согласные звуки З ВЫПОЛНИЛА СТУДЕНТКА ЮРИДЮИЧЕСКОГО ФАКУЛЬТЕТА ГРУППЫ№1404 Микаилова Ламан

ВЫПОЛНИЛА СТУДЕНТКА ЮРИДЮИЧЕСКОГО ФАКУЛЬТЕТА ГРУППЫ№1404 Микаилова Ламан  Политическое участие

Политическое участие Олимпийские игры в древности

Олимпийские игры в древности Права человека

Права человека Презентация "Русская икона Иконописная техника" - скачать презентации по МХК

Презентация "Русская икона Иконописная техника" - скачать презентации по МХК Планирование и развитие карьеры в современной организации

Планирование и развитие карьеры в современной организации Презентация Жиры

Презентация Жиры Заглавная буква в именах, фамилиях, отчествах людей - презентация для начальной школы_

Заглавная буква в именах, фамилиях, отчествах людей - презентация для начальной школы_ РОЖДЕСТВО И НОВЫЙ ГОД в мировом изобразительном искусстве

РОЖДЕСТВО И НОВЫЙ ГОД в мировом изобразительном искусстве Бюджетний процес Виконала: ст. гр. УДФ-06 Власенко Ю.М.

Бюджетний процес Виконала: ст. гр. УДФ-06 Власенко Ю.М. Біблиотека MFC

Біблиотека MFC Трудовое право

Трудовое право  Архитектура XIX века

Архитектура XIX века My idol - Lionel Messi

My idol - Lionel Messi Понятие и виды мер уголовно-процессуального принуждения

Понятие и виды мер уголовно-процессуального принуждения  Инвестиционный проект фитнес центра «Zinch»

Инвестиционный проект фитнес центра «Zinch»