Содержание

- 2. Актуальность работы Постоянное совершенствование микроархитектуры процессоров Особенности новой микроархитектуры Intel Core Увеличение важности производительности front-end процессора

- 3. Результаты Разработаны идеи и эвристики для оптимизации линеаризации и выравнивания кода Опробована схема удаления ветвлений в

- 4. Apache Harmony Открытая реализация виртуальной машины Java JIT-компилятор Jitrino.OPT – оптимизирующий компилятор с возможностью профилировки и

- 5. Выравнивание кода Отсутствие trace cache по сравнению с микроархитектурой NetBurst Линия выборки (fetch line) 16 байт

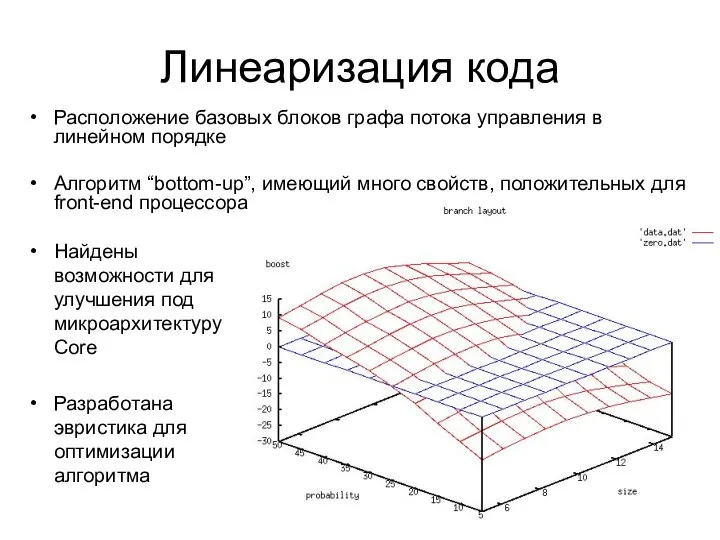

- 6. Линеаризация кода Расположение базовых блоков графа потока управления в линейном порядке Алгоритм “bottom-up”, имеющий много свойств,

- 8. Скачать презентацию

Архитектура Руси

Архитектура Руси  Детское служение

Детское служение Строение и свойства свободных радикалов

Строение и свойства свободных радикалов Презентация Таможенный перевозчик

Презентация Таможенный перевозчик Степенная функция

Степенная функция Углы

Углы Волейбол. Правила игры

Волейбол. Правила игры Презентация "Формирование толерантного сознания на уроках МХК" - скачать презентации по МХК

Презентация "Формирование толерантного сознания на уроках МХК" - скачать презентации по МХК Фильтрация и модуляция сигналов

Фильтрация и модуляция сигналов Конструкции одноэтажных промышленных зданий

Конструкции одноэтажных промышленных зданий Государство. Политическая система общества

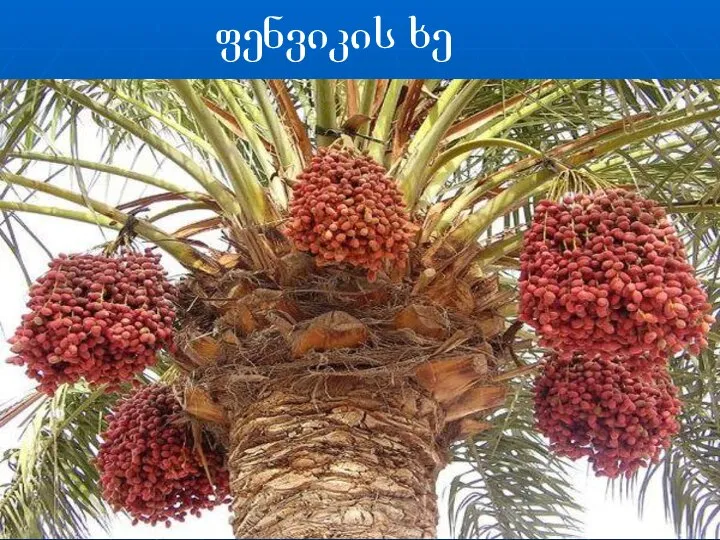

Государство. Политическая система общества ფენვიკის ხე

ფენვიკის ხე Расчет и проектирование элементов механического измельчения отходов

Расчет и проектирование элементов механического измельчения отходов Усиление железобетонных конструкций

Усиление железобетонных конструкций Английский стиль в одежде

Английский стиль в одежде СНЕГ И ЛЁД Урок окружающего мира 1 класс

СНЕГ И ЛЁД Урок окружающего мира 1 класс Житель Санкт-Петербурга: синтез культур

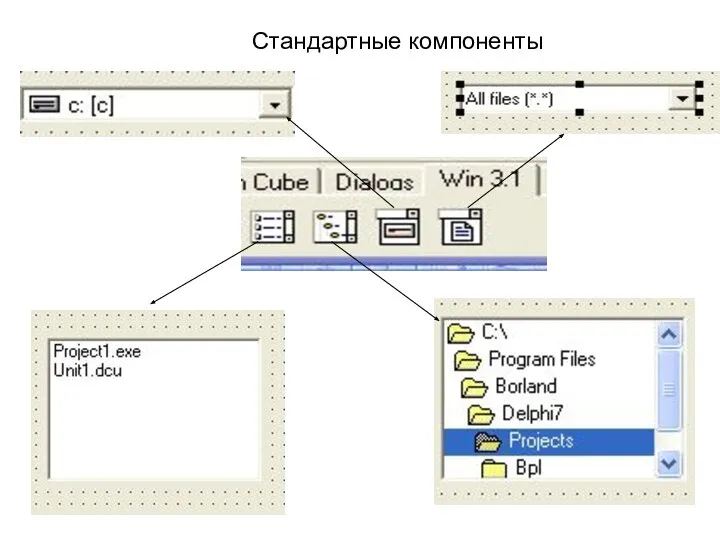

Житель Санкт-Петербурга: синтез культур диск директория файл

диск директория файл  Философия нового времени

Философия нового времени  Архитектура ЭВМ

Архитектура ЭВМ Математика 2 класс Тема: «Увеличение числа в несколько раз» Программа: «Перспективная начальная школа» Учитель начальных кл

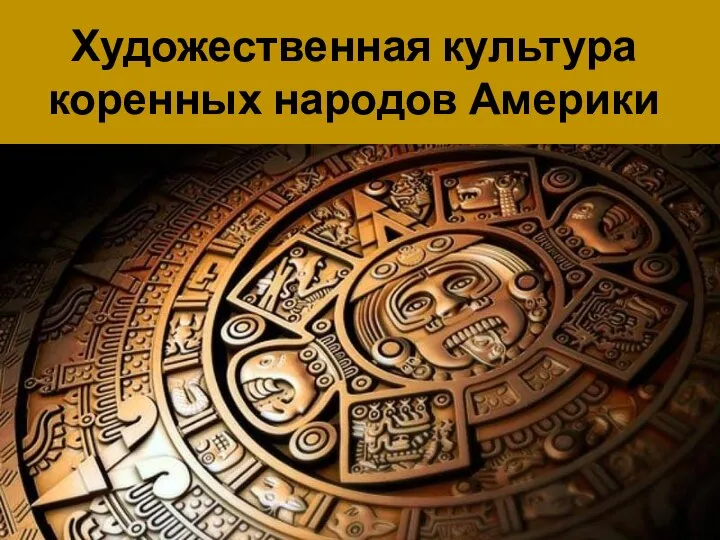

Математика 2 класс Тема: «Увеличение числа в несколько раз» Программа: «Перспективная начальная школа» Учитель начальных кл Художественная культура коренных народов Америки

Художественная культура коренных народов Америки Схематизация опор. Определение реакций

Схематизация опор. Определение реакций Принципы налогообложения Адама Смита

Принципы налогообложения Адама Смита Ch11(САдмП)

Ch11(САдмП)  Історія створення українського волейболу

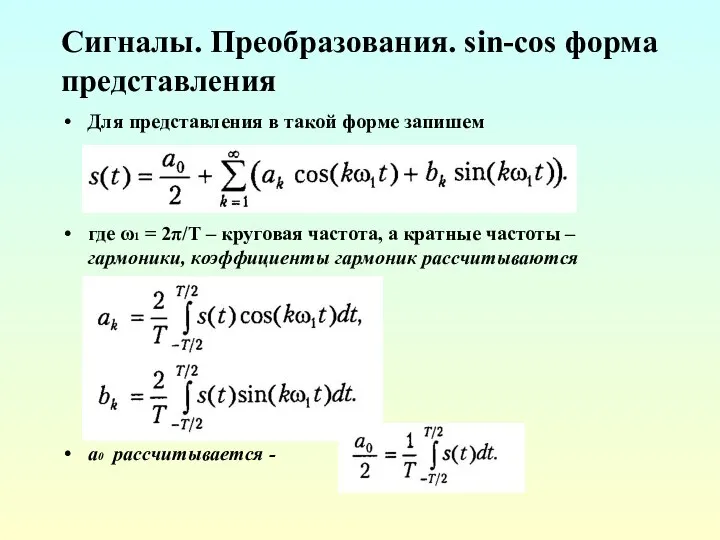

Історія створення українського волейболу Сигналы. Преобразования. Sin-cos форма представления

Сигналы. Преобразования. Sin-cos форма представления бундестаг

бундестаг