Physics Faculty, Electronic Computing Devices & Systems, 7th semester,2011 Dr.Mokhovikov Alexander

Yurievich

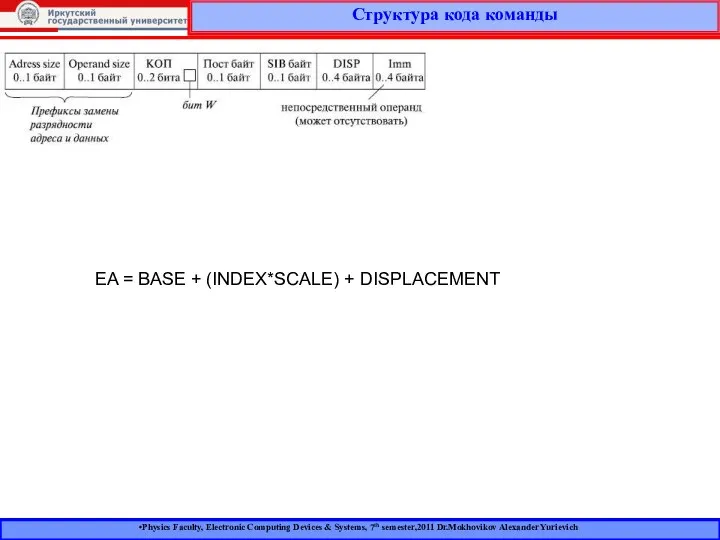

Структура кода команды

Команды в архитектуре IA-32 имеют большое разнообразие форматов, которые зависят от типа операции, режимов адресации операндов, длины используемых непосредственных операндов и смещений и ряда других факторов. Они имеют длину от 1 до 15 байт.

Формат двухоперандной команды общего вида:

Команда может начинаться с нескольких необязательных байтов (префиксов), которые определяют особенности выполнения команды.

Для операндов совместно с битом W, содержащимся в коде команды, префикс размера позволяет определить операнд длиной 8, 16 или 32 разряда.

В коде команды могут использоваться также дополнительные байты для:

● префикса замены сегментного регистра, установленного по умолчанию,

● префикса повторения операции,

● префикса, предотвращающего прерывание операции перемещения данных.

Поле КОП содержит код выполняемой команды, а также бит W размерности используемых операндов. Для команд, применяющих непосредственный операнд, код операции может также занимать часть постбайта.

Формат постбайта

Постбайт определяет местоположение операндов.

Основная часть команд микропроцессора с архитектурой IA-32 позволяет работать только с одним операндом, находящимся в оперативной памяти. Его режим адресации кодируется полями md и r/m постбайта.

Второй операнд либо извлекается из регистров общего назначения микропроцессора (его номер указывается в поле reg постбайта), либо кодируется в поле Imm самой команды (непосредственный операнд).

Байт масштабируемого индекса базы (SIB) служит для представления сложных структур памяти. На его наличие указывает код 100 в поле r/m постбайта.

Формат SIB-байта

Государственная служба в системе управления

Государственная служба в системе управления Структура поверхности и ее физические свойства

Структура поверхности и ее физические свойства  Археологічний музей Іракліону

Археологічний музей Іракліону Основы языка Visual Basic. Выражения

Основы языка Visual Basic. Выражения Франсиско де Гойя Биография и творчество художника

Франсиско де Гойя Биография и творчество художника Благотворительный забег "достигая цели!" В честь дня железнодорожника

Благотворительный забег "достигая цели!" В честь дня железнодорожника Профессиональная этика таможенника

Профессиональная этика таможенника Проект новых стандартов: компетентностный подход

Проект новых стандартов: компетентностный подход Спорт в СПбГУ

Спорт в СПбГУ Сортувальна Гірка. АССКРП

Сортувальна Гірка. АССКРП Торговые организации Башкортостана

Торговые организации Башкортостана Современные системы физического воспитания

Современные системы физического воспитания ФГОС СО

ФГОС СО Инструменты для продвижения и популяризации ВФСК ГТО на территории Красноярского края

Инструменты для продвижения и популяризации ВФСК ГТО на территории Красноярского края ДЕЙСТВИЯ И РЕШЕНИЯ ПРОКУРОРА

ДЕЙСТВИЯ И РЕШЕНИЯ ПРОКУРОРА Урок в соответствии с ФГОС Н.А. Разагатова, МОУ ДПО (ПК) «Центр развития образования г.о. Самара»

Урок в соответствии с ФГОС Н.А. Разагатова, МОУ ДПО (ПК) «Центр развития образования г.о. Самара»  Инновационная модель управления таможенными органами. Тема 10

Инновационная модель управления таможенными органами. Тема 10 Булки не растут на деревьях

Булки не растут на деревьях Воздействие электрического тока на организм человека Выполнила ученица 8 а класса МОУ «СОШ № 57», г. Оренбург Кисе

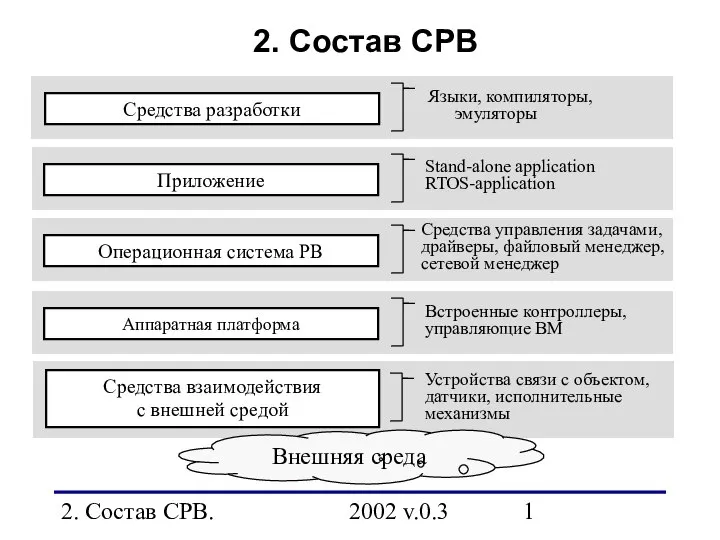

Воздействие электрического тока на организм человека Выполнила ученица 8 а класса МОУ «СОШ № 57», г. Оренбург Кисе Языки, компиляторы, эмуляторы

Языки, компиляторы, эмуляторы закалдованые цыфры - презентация для начальной школы

закалдованые цыфры - презентация для начальной школы Теория локальных цивилизаций Освальда Шпенглера

Теория локальных цивилизаций Освальда Шпенглера Острый коронарный синдром

Острый коронарный синдром Налогообложение природопользования Доц. Каширина М.В. Цель дисциплины – дать специальные знания в области системы налогообл

Налогообложение природопользования Доц. Каширина М.В. Цель дисциплины – дать специальные знания в области системы налогообл Язык C++

Язык C++ Реалізація державної політики у сфері державної реєстрації фізичних осіб, департаментом реєстраційних послуг Запорізької ради

Реалізація державної політики у сфері державної реєстрації фізичних осіб, департаментом реєстраційних послуг Запорізької ради Методические рекомендации по проведению мероприятий благоустройства дворовых территорий. Программа «Башкирские дворики»

Методические рекомендации по проведению мероприятий благоустройства дворовых территорий. Программа «Башкирские дворики» причины финансового кризиса 2008 года в РФ и пути выхода Карташова Галина Т-093

причины финансового кризиса 2008 года в РФ и пути выхода Карташова Галина Т-093