Содержание

- 2. Outline Переключения задач: ● межсегментные переключения задач; ● прямое переключение задач; ● переключение задач с использованием

- 3. Переключение задач. Общие понятия. Физический факультет, ЭВУ и системы, 7 семестр,2012 Доцент Моховиков А..Ю. Physics Faculty,

- 4. Механизмы реализации мультизадачности в Intel x86. Важнейшей особенностью защищенного режима является возможность «параллельного» выполнения нескольких программ.

- 5. Task Status Segment Для хранения информации о задачи существует специальная структура – TSS (Task State Segment)

- 6. Task Status Segment. Общие понятия. TSS описывается системным дескриптором, который может находиться только в GDT Поле

- 7. Пример обращения процессора к памяти Рассмотрим пример обращения процессора к памяти в сегмент (данных), описанный в

- 8. Пример обращения процессора к памяти Адрес сегмента, прочитанный из дескриптора, складывается с внутрисегментным смещением и при

- 9. Поля Task Status Segment Для каждой задачи (фрагмента кода), участвующей в переключении создается свой TSS Поля

- 10. Карта разрешения ввода/вывода Карта разрешения ввода-вывода (I/O Permission Bit Map), расположенная в конце TSS, имеет по

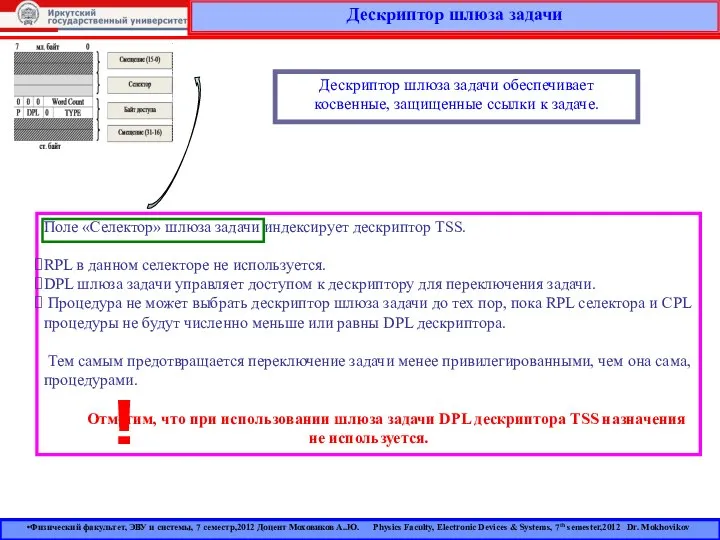

- 11. Дескриптор шлюза задачи Дескриптор шлюза задачи обеспечивает косвенные, защищенные ссылки к задаче. Поле «Селектор» шлюза задачи

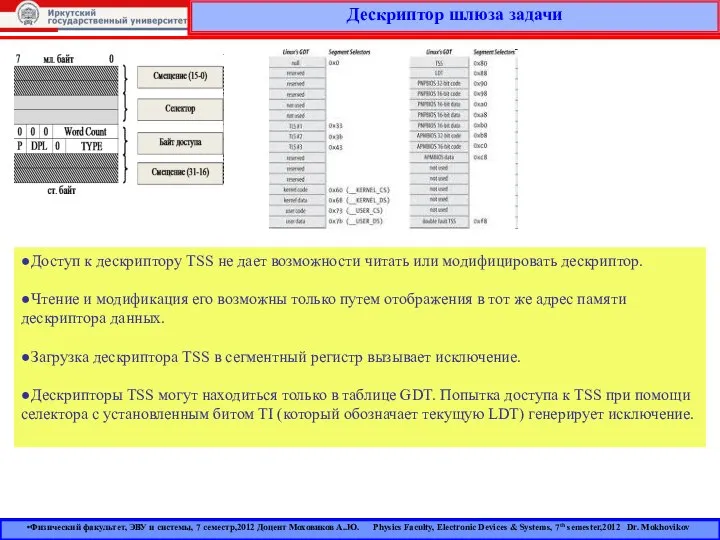

- 12. Дескриптор шлюза задачи ●Доступ к дескриптору TSS не дает возможности читать или модифицировать дескриптор. ●Чтение и

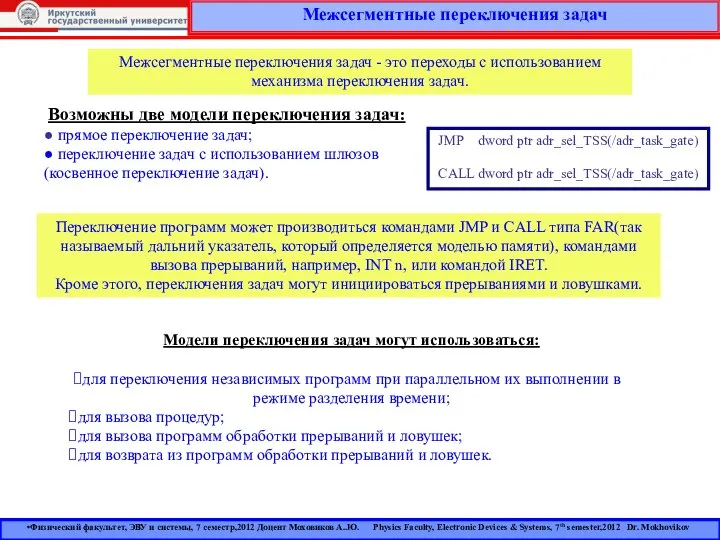

- 13. Межсегментные переключения задач Межсегментные переключения задач - это переходы с использованием механизма переключения задач. Возможны две

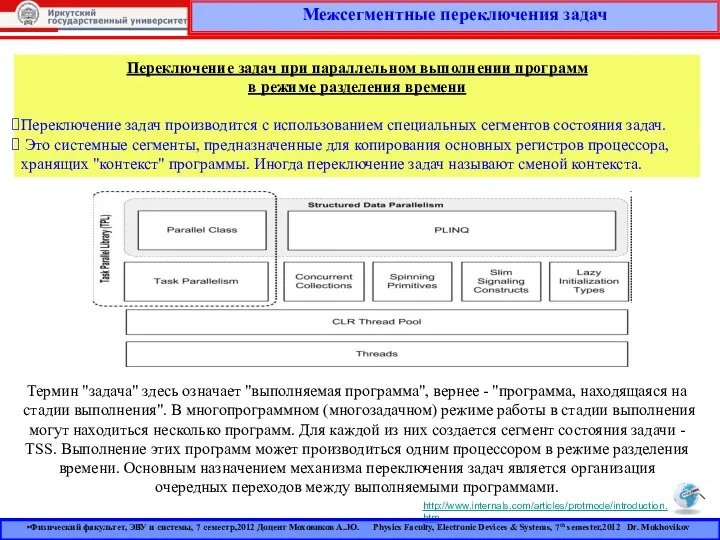

- 14. Межсегментные переключения задач Переключение задач при параллельном выполнении программ в режиме разделения времени Переключение задач производится

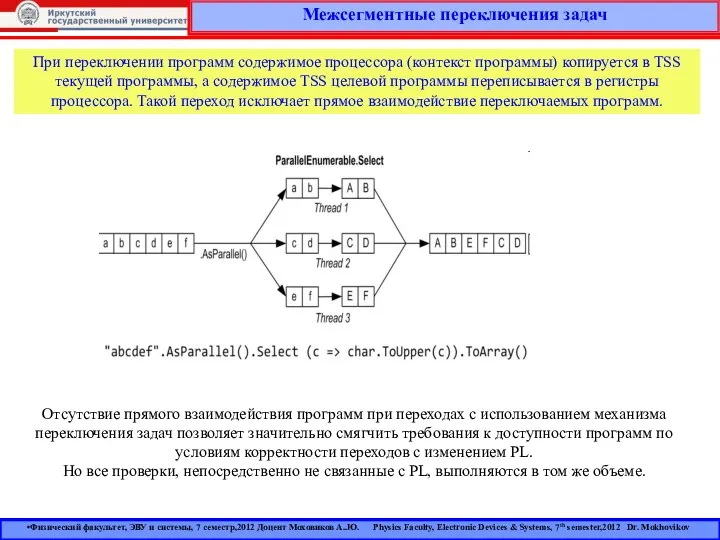

- 15. Межсегментные переключения задач При переключении программ содержимое процессора (контекст программы) копируется в TSS текущей программы, а

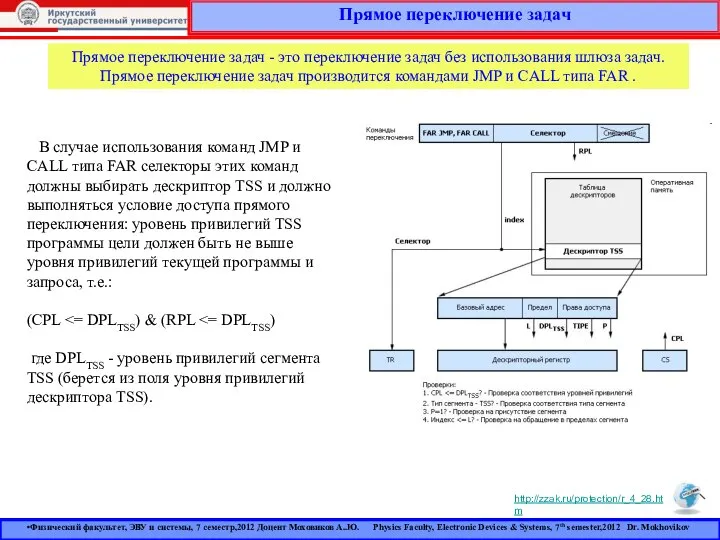

- 16. Прямое переключение задач Прямое переключение задач - это переключение задач без использования шлюза задач. Прямое переключение

- 17. Прямое переключение задач http://zzak.ru/protection/r_4_28.htm Перед обращением к таблице дескрипторов проверяется действительность селектора и соответствие индекса границам

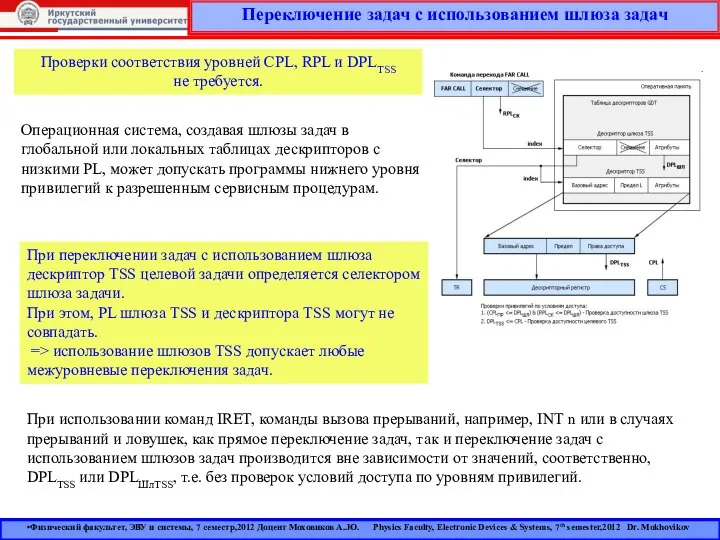

- 18. Переключение задач с использованием шлюза задач Любое переключение задач на программы более высокого уровня привилегий допускается

- 19. Переключение задач с использованием шлюза задач Проверки соответствия уровней CPL, RPL и DPLTSS не требуется. Операционная

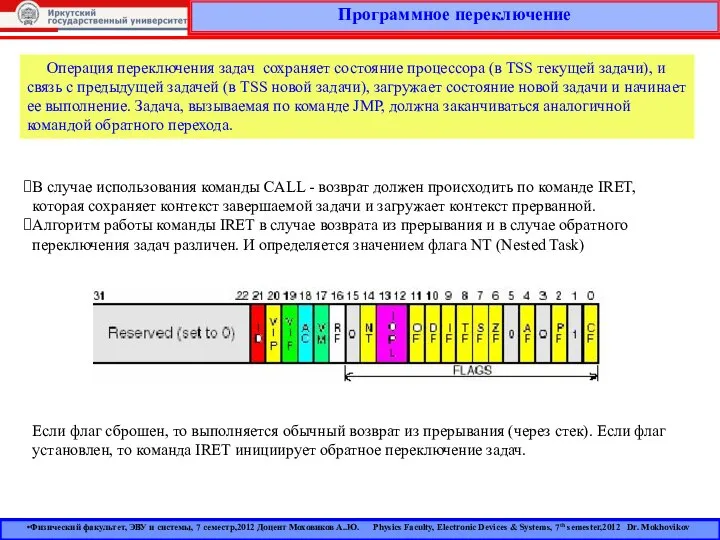

- 20. Программное переключение Операция переключения задач сохраняет состояние процессора (в TSS текущей задачи), и связь с предыдущей

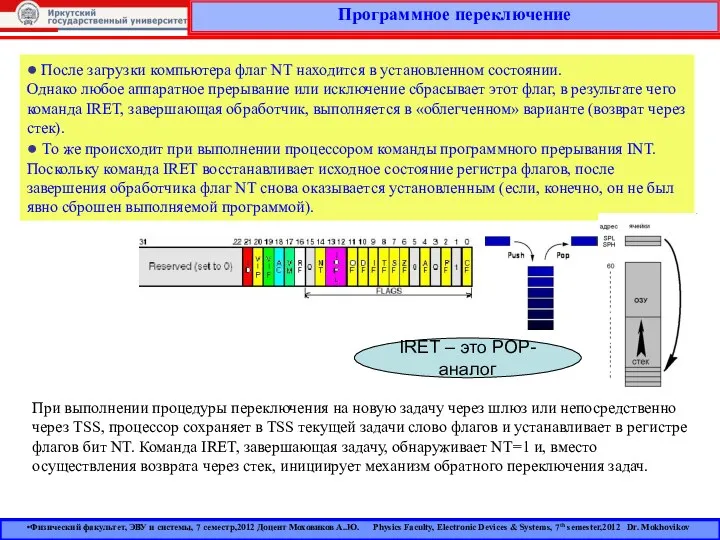

- 21. Программное переключение ● После загрузки компьютера флаг NT находится в установленном состоянии. Однако любое аппаратное прерывание

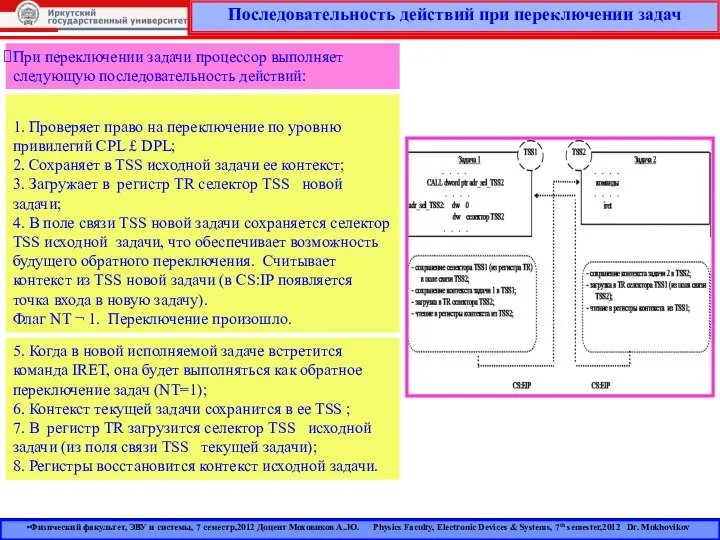

- 22. Последовательность действий при переключении задач 1. Проверяет право на переключение по уровню привилегий CPL £ DPL;

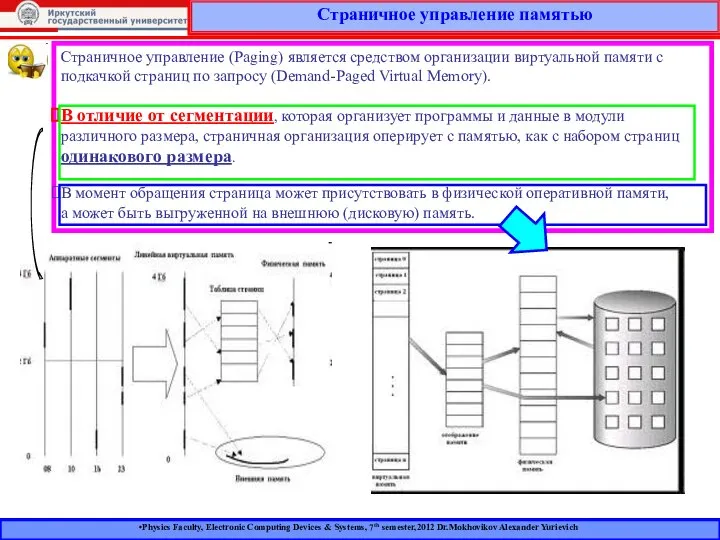

- 23. Страничное управление памятью Physics Faculty, Electronic Computing Devices & Systems, 7th semester,2012 Dr.Mokhovikov Alexander Yurievich Страничное

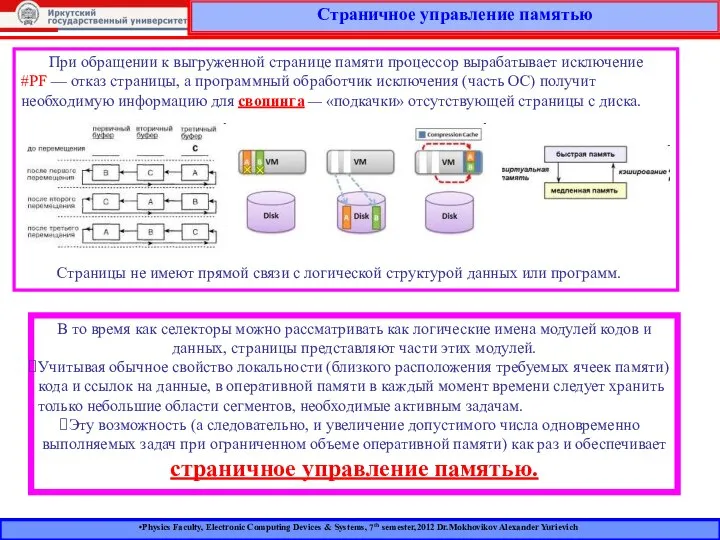

- 24. Страничное управление памятью При обращении к выгруженной странице памяти процессор вырабатывает исключение #PF — отказ страницы,

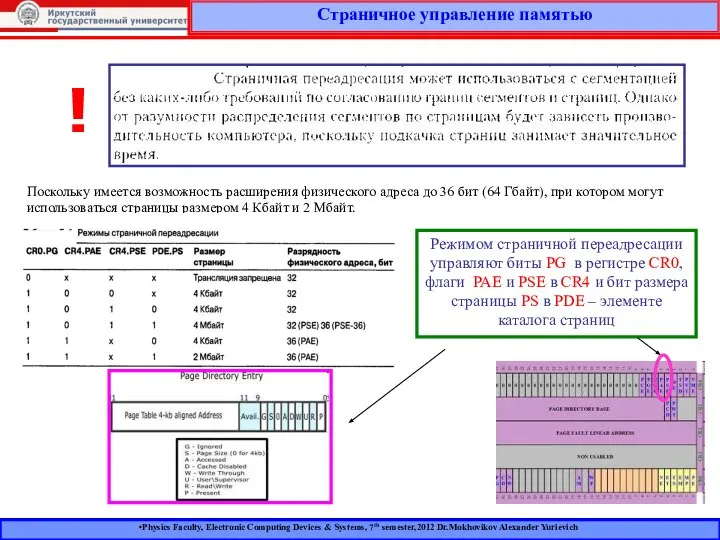

- 25. Страничное управление памятью ! Поскольку имеется возможность расширения физического адреса до 36 бит (64 Гбайт), при

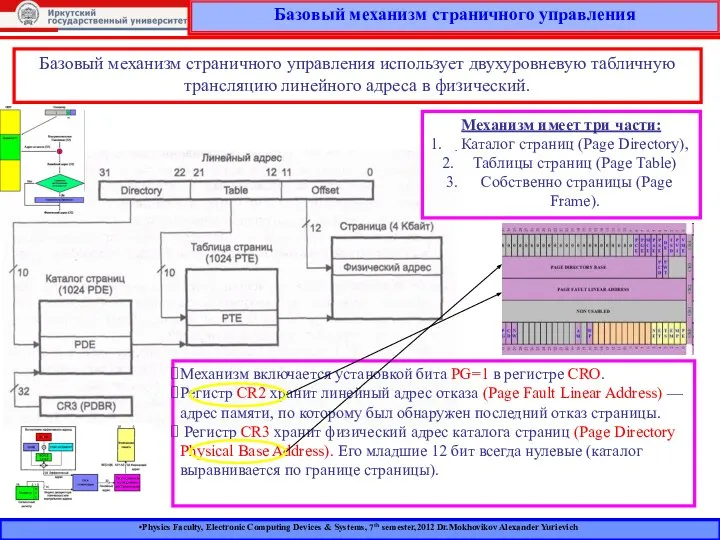

- 26. Базовый механизм страничного управления Базовый механизм страничного управления использует двухуровневую табличную трансляцию линейного адреса в физический.

- 27. Книга «Assembler. Учебник для ВУЗов», автор Юров Книга «Процессоры Pentium4, Athlon и Duron», авторы Михаил Гук,

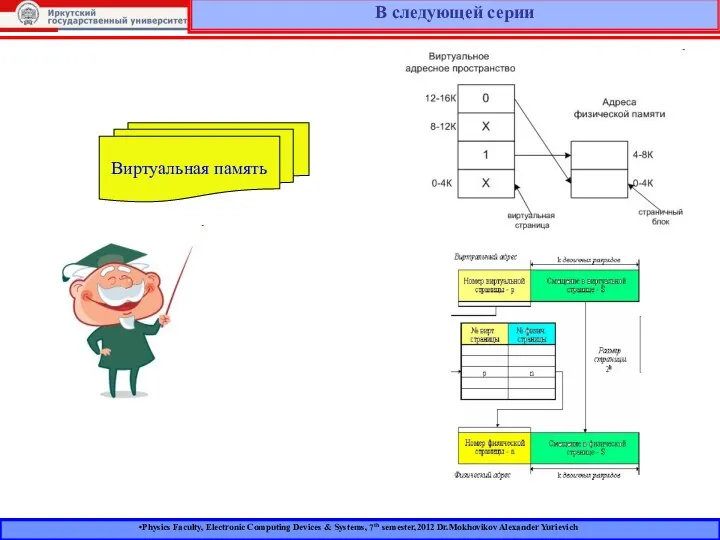

- 28. В следующей серии Виртуальная память Physics Faculty, Electronic Computing Devices & Systems, 7th semester,2012 Dr.Mokhovikov Alexander

- 30. Скачать презентацию

Outline

Переключения задач:

● межсегментные переключения задач;

● прямое переключение задач;

● переключение задач с

Outline

Переключения задач:

● межсегментные переключения задач;

● прямое переключение задач;

● переключение задач с

● последовательность действий при переключении задач.

Поля Task Status Segment:

● карта разрешения ввода/вывода;

● дескриптор шлюза задачи.

Резюме к лекции и список используемой литературы

Механизмы реализации мультизадачности :

● общие понятия;

● описание сегмента состояния задачи;

● обращения процессора к памяти .

Страничное управление памятью:

● понятия свопинга;

● базовый механизм страничного управления.

Физический факультет, ЭВУ и системы, 7 семестр,2012 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems, 7th semester,2012 Dr. Mokhovikov

Переключение задач. Общие понятия.

Физический факультет, ЭВУ и системы, 7 семестр,2012

Переключение задач. Общие понятия.

Физический факультет, ЭВУ и системы, 7 семестр,2012

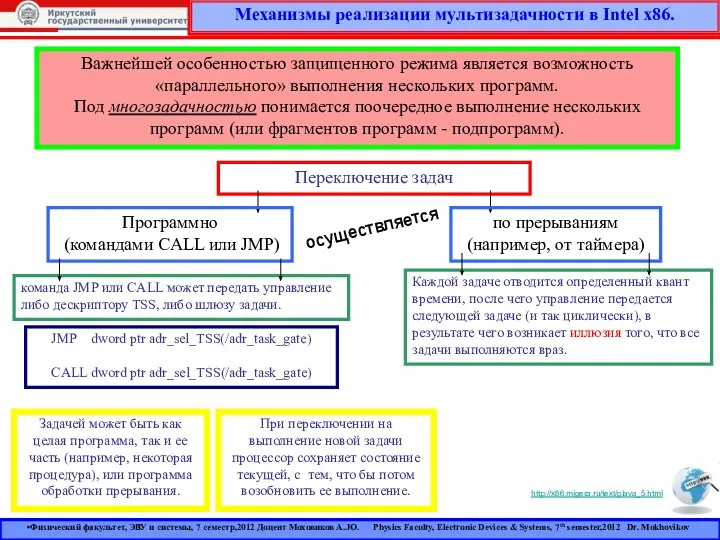

Механизмы реализации мультизадачности в Intel x86.

Важнейшей особенностью защищенного режима является возможность

Механизмы реализации мультизадачности в Intel x86.

Важнейшей особенностью защищенного режима является возможность

Под многозадачностью понимается поочередное выполнение нескольких программ (или фрагментов программ - подпрограмм).

Переключение задач

осуществляется

Программно

(командами CALL или JMP)

по прерываниям (например, от таймера)

Каждой задаче отводится определенный квант времени, после чего управление передается следующей задаче (и так циклически), в результате чего возникает иллюзия того, что все задачи выполняются враз.

http://x86.migera.ru/text/glava_5.html

команда JMP или CALL может передать управление либо дескриптору TSS, либо шлюзу задачи.

JMP dword ptr adr_sel_TSS(/adr_task_gate)

CALL dword ptr adr_sel_TSS(/adr_task_gate)

Задачей может быть как целая программа, так и ее часть (например, некоторая процедура), или программа обработки прерывания.

При переключении на выполнение новой задачи процессор сохраняет состояние текущей, с тем, что бы потом возобновить ее выполнение.

Физический факультет, ЭВУ и системы, 7 семестр,2012 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems, 7th semester,2012 Dr. Mokhovikov

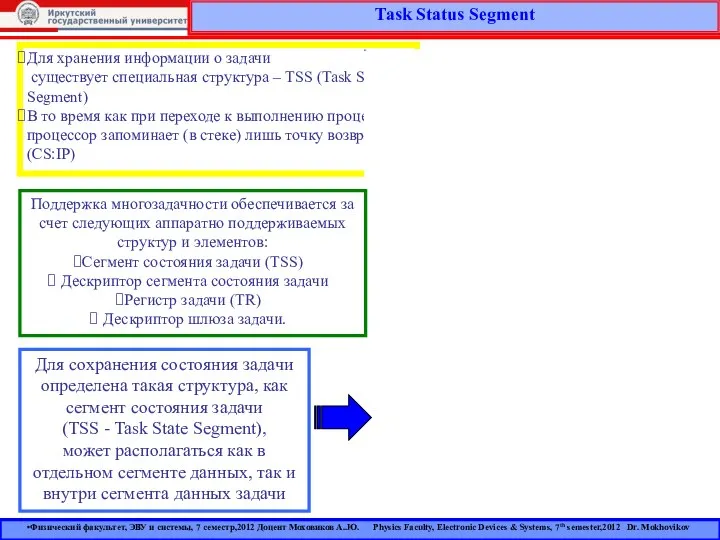

Task Status Segment

Для хранения информации о задачи

существует специальная структура –

Task Status Segment

Для хранения информации о задачи

существует специальная структура –

В то время как при переходе к выполнению процедуры, процессор запоминает (в стеке) лишь точку возврата (CS:IP)

Поддержка многозадачности обеспечивается за счет следующих аппаратно поддерживаемых структур и элементов:

Сегмент состояния задачи (TSS)

Дескриптор сегмента состояния задачи

Регистр задачи (TR)

Дескриптор шлюза задачи.

Для сохранения состояния задачи определена такая структура, как сегмент состояния задачи

(TSS - Task State Segment),

может располагаться как в отдельном сегменте данных, так и внутри сегмента данных задачи

Физический факультет, ЭВУ и системы, 7 семестр,2012 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems, 7th semester,2012 Dr. Mokhovikov

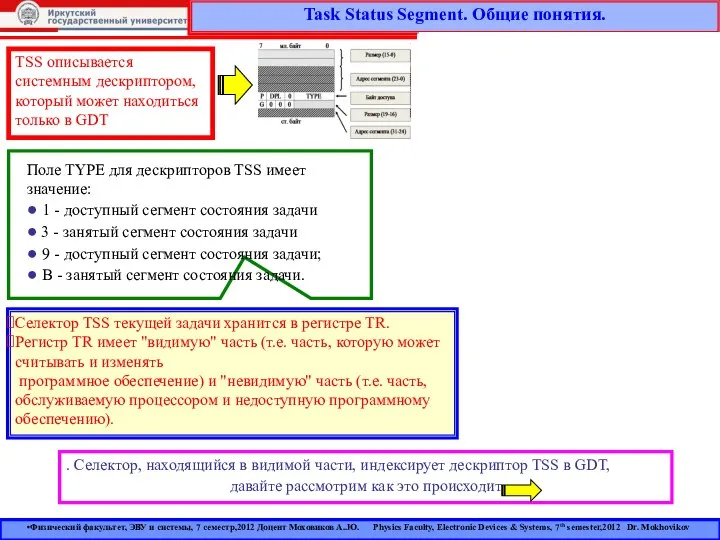

Task Status Segment. Общие понятия.

TSS описывается системным дескриптором, который может находиться

Task Status Segment. Общие понятия.

TSS описывается системным дескриптором, который может находиться

Поле TYPE для дескрипторов TSS имеет значение:

● 1 - доступный сегмент состояния задачи

● 3 - занятый сегмент состояния задачи

● 9 - доступный сегмент состояния задачи;

● B - занятый сегмент состояния задачи.

Селектор TSS текущей задачи хранится в регистре TR.

Регистр TR имеет "видимую" часть (т.е. часть, которую может считывать и изменять

программное обеспечение) и "невидимую" часть (т.е. часть, обслуживаемую процессором и недоступную программному обеспечению).

. Селектор, находящийся в видимой части, индексирует дескриптор TSS в GDT,

давайте рассмотрим как это происходит

Физический факультет, ЭВУ и системы, 7 семестр,2012 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems, 7th semester,2012 Dr. Mokhovikov

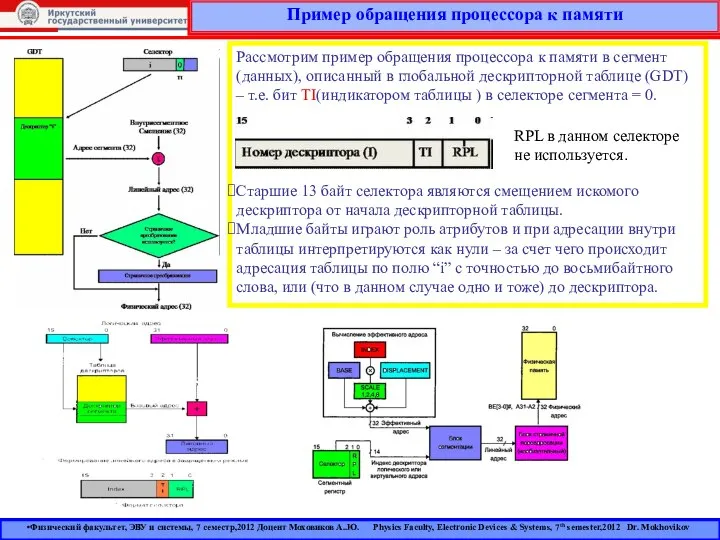

Пример обращения процессора к памяти

Рассмотрим пример обращения процессора к памяти

Пример обращения процессора к памяти

Рассмотрим пример обращения процессора к памяти

Старшие 13 байт селектора являются смещением искомого дескриптора от начала дескрипторной таблицы.

Младшие байты играют роль атрибутов и при адресации внутри таблицы интерпретируются как нули – за счет чего происходит адресация таблицы по полю “i” с точностью до восьмибайтного слова, или (что в данном случае одно и тоже) до дескриптора.

RPL в данном селекторе не используется.

Физический факультет, ЭВУ и системы, 7 семестр,2012 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems, 7th semester,2012 Dr. Mokhovikov

Пример обращения процессора к памяти

Адрес сегмента, прочитанный из дескриптора, складывается с

Пример обращения процессора к памяти

Адрес сегмента, прочитанный из дескриптора, складывается с

смещением и при отсутствии страничного преобразования адреса выставляется на адресную шину.

Если бит TI в селекторе сегмента = 1, то происходит выборка сегмента из локальной дескрипторной таблицы.

В этом случае регистр LDTR должен содержать селектор этой таблицы (индекс) – локальная дескрипторная таблица описывается дескриптором глобальной таблицы.

Сам же селектор (в котором TI=1) определяет дескриптор сегмента памяти, описанного в локальной дескрипторной таблице.

В регистре LDTR бит TI всегда нулевой – т.к. дескриптор-описатель локальной таблицы может находиться только в GDT.

Физический факультет, ЭВУ и системы, 7 семестр,2012 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems, 7th semester,2012 Dr. Mokhovikov

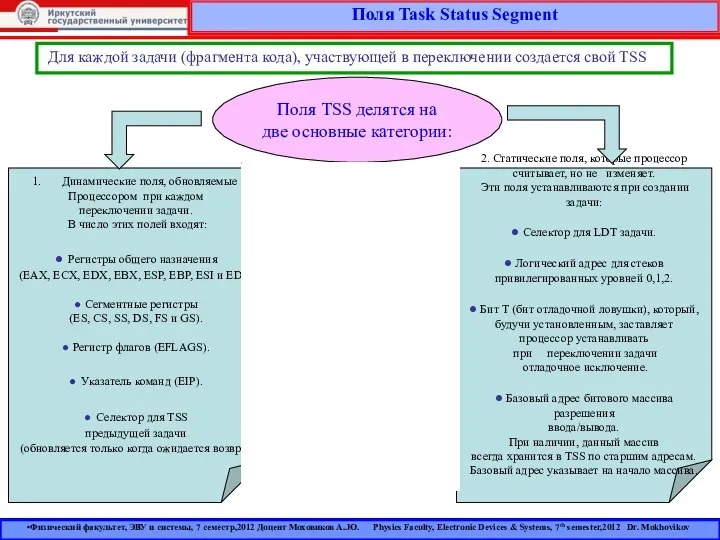

Поля Task Status Segment

Для каждой задачи (фрагмента кода), участвующей в

Поля Task Status Segment

Для каждой задачи (фрагмента кода), участвующей в

Поля TSS делятся на

две основные категории:

Динамические поля, обновляемые

Процессором при каждом

переключении задачи.

В число этих полей входят:

● Регистры общего назначения

(EAX, ECX, EDX, EBX, ESP, EBP, ESI и EDI).

● Сегментные регистры

(ES, CS, SS, DS, FS и GS).

● Регистр флагов (EFLAGS).

● Указатель команд (EIP).

● Селектор для TSS

предыдущей задачи

(обновляется только когда ожидается возврат).

2. Статические поля, которые процессор

считывает, но не изменяет.

Эти поля устанавливаются при создании задачи:

● Селектор для LDT задачи.

● Логический адрес для стеков

привилегированных уровней 0,1,2.

● Бит T (бит отладочной ловушки), который,

будучи установленным, заставляет

процессор устанавливать

при переключении задачи

отладочное исключение.

● Базовый адрес битового массива разрешения

ввода/вывода.

При наличии, данный массив

всегда хранится в TSS по старшим адресам.

Базовый адрес указывает на начало массива.

Физический факультет, ЭВУ и системы, 7 семестр,2012 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems, 7th semester,2012 Dr. Mokhovikov

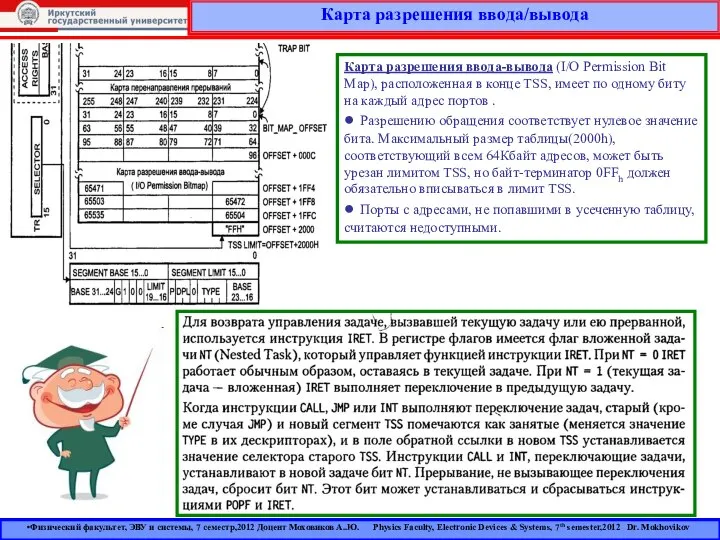

Карта разрешения ввода/вывода

Карта разрешения ввода-вывода (I/O Permission Bit Map), расположенная в

Карта разрешения ввода/вывода

Карта разрешения ввода-вывода (I/O Permission Bit Map), расположенная в

● Разрешению обращения соответствует нулевое значение бита. Максимальный размер таблицы(2000h), соответствующий всем 64Кбайт адресов, может быть урезан лимитом TSS, но байт-терминатор 0FFh должен обязательно вписываться в лимит TSS.

● Порты с адресами, не попавшими в усеченную таблицу, считаются недоступными.

Физический факультет, ЭВУ и системы, 7 семестр,2012 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems, 7th semester,2012 Dr. Mokhovikov

Дескриптор шлюза задачи

Дескриптор шлюза задачи обеспечивает косвенные, защищенные ссылки к задаче.

Поле

Дескриптор шлюза задачи

Дескриптор шлюза задачи обеспечивает косвенные, защищенные ссылки к задаче.

Поле

RPL в данном селекторе не используется.

DPL шлюза задачи управляет доступом к дескриптору для переключения задачи.

Процедура не может выбрать дескриптор шлюза задачи до тех пор, пока RPL селектора и CPL процедуры не будут численно меньше или равны DPL дескриптора.

Тем самым предотвращается переключение задачи менее привилегированными, чем она сама, процедурами.

Отметим, что при использовании шлюза задачи DPL дескриптора TSS назначения не используется.

!

Физический факультет, ЭВУ и системы, 7 семестр,2012 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems, 7th semester,2012 Dr. Mokhovikov

Дескриптор шлюза задачи

●Доступ к дескриптору TSS не дает возможности читать или

Дескриптор шлюза задачи

●Доступ к дескриптору TSS не дает возможности читать или

●Чтение и модификация его возможны только путем отображения в тот же адрес памяти дескриптора данных.

●Загрузка дескриптора TSS в сегментный регистр вызывает исключение.

●Дескрипторы TSS могут находиться только в таблице GDT. Попытка доступа к TSS при помощи селектора с установленным битом TI (который обозначает текущую LDT) генерирует исключение.

Физический факультет, ЭВУ и системы, 7 семестр,2012 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems, 7th semester,2012 Dr. Mokhovikov

Межсегментные переключения задач

Межсегментные переключения задач - это переходы с использованием механизма

Межсегментные переключения задач

Межсегментные переключения задач - это переходы с использованием механизма

Возможны две модели переключения задач:

● прямое переключение задач;

● переключение задач с использованием шлюзов (косвенное переключение задач).

Переключение программ может производиться командами JMP и CALL типа FAR(так называемый дальний указатель, который определяется моделью памяти), командами вызова прерываний, например, INT n, или командой IRET.

Кроме этого, переключения задач могут инициироваться прерываниями и ловушками.

Модели переключения задач могут использоваться:

для переключения независимых программ при параллельном их выполнении в режиме разделения времени;

для вызова процедур;

для вызова программ обработки прерываний и ловушек;

для возврата из программ обработки прерываний и ловушек.

JMP dword ptr adr_sel_TSS(/adr_task_gate)

CALL dword ptr adr_sel_TSS(/adr_task_gate)

Физический факультет, ЭВУ и системы, 7 семестр,2012 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems, 7th semester,2012 Dr. Mokhovikov

Межсегментные переключения задач

Переключение задач при параллельном выполнении программ

в режиме

Межсегментные переключения задач

Переключение задач при параллельном выполнении программ

в режиме

Переключение задач производится с использованием специальных сегментов состояния задач.

Это системные сегменты, предназначенные для копирования основных регистров процессора, хранящих "контекст" программы. Иногда переключение задач называют сменой контекста.

Термин "задача" здесь означает "выполняемая программа", вернее - "программа, находящаяся на стадии выполнения". В многопрограммном (многозадачном) режиме работы в стадии выполнения могут находиться несколько программ. Для каждой из них создается сегмент состояния задачи - TSS. Выполнение этих программ может производиться одним процессором в режиме разделения времени. Основным назначением механизма переключения задач является организация очередных переходов между выполняемыми программами.

http://www.internals.com/articles/protmode/introduction.htm

Физический факультет, ЭВУ и системы, 7 семестр,2012 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems, 7th semester,2012 Dr. Mokhovikov

Межсегментные переключения задач

При переключении программ содержимое процессора (контекст программы) копируется

Межсегментные переключения задач

При переключении программ содержимое процессора (контекст программы) копируется

Отсутствие прямого взаимодействия программ при переходах с использованием механизма переключения задач позволяет значительно смягчить требования к доступности программ по условиям корректности переходов с изменением PL.

Но все проверки, непосредственно не связанные с PL, выполняются в том же объеме.

Физический факультет, ЭВУ и системы, 7 семестр,2012 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems, 7th semester,2012 Dr. Mokhovikov

Прямое переключение задач

Прямое переключение задач - это переключение задач без использования

Прямое переключение задач

Прямое переключение задач - это переключение задач без использования

Прямое переключение задач производится командами JMP и CALL типа FAR .

В случае использования команд JMP и CALL типа FAR селекторы этих команд должны выбирать дескриптор TSS и должно выполняться условие доступа прямого переключения: уровень привилегий TSS программы цели должен быть не выше уровня привилегий текущей программы и запроса, т.е.:

(CPL <= DPLTSS) & (RPL <= DPLTSS)

где DPLTSS - уровень привилегий сегмента TSS (берется из поля уровня привилегий дескриптора TSS).

http://zzak.ru/protection/r_4_28.htm

Физический факультет, ЭВУ и системы, 7 семестр,2012 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems, 7th semester,2012 Dr. Mokhovikov

Прямое переключение задач

http://zzak.ru/protection/r_4_28.htm

Перед обращением к таблице дескрипторов проверяется действительность селектора

Прямое переключение задач

http://zzak.ru/protection/r_4_28.htm

Перед обращением к таблице дескрипторов проверяется действительность селектора

После выборки дескриптора TSS проверяется его тип, присутствие TSS в оперативной памяти и его доступность по уровням привилегий.

При положительных результатах проверок производится процедура переключения задач (сохранение

содержимого регистров процессора в старом TSS и загрузка селектора целевого TSS в регистр TR).

Загрузка селектора целевого TSS приводит к загрузке регистров процессора контекстом целевой задачи,

т.е. к переключению задач.

Физический факультет, ЭВУ и системы, 7 семестр,2012 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems, 7th semester,2012 Dr. Mokhovikov

Переключение задач с использованием шлюза задач

Любое переключение задач на программы более

Переключение задач с использованием шлюза задач

Любое переключение задач на программы более

Переключение задачи по команде JMP или CALL типа FAR допускается, если уровень привилегий шлюза TSS не выше текущего уровня привилегий и уровня привилегий запроса, т.е.:

(CPL <= DPLШлTSS) & (RPL <= DPLШлTSS)

где DPLШлTSS - уровень привилегий шлюза задачи.

Физический факультет, ЭВУ и системы, 7 семестр,2012 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems, 7th semester,2012 Dr. Mokhovikov

Переключение задач с использованием шлюза задач

Проверки соответствия уровней CPL, RPL и

Переключение задач с использованием шлюза задач

Проверки соответствия уровней CPL, RPL и

не требуется.

Операционная система, создавая шлюзы задач в глобальной или локальных таблицах дескрипторов с низкими PL, может допускать программы нижнего уровня привилегий к разрешенным сервисным процедурам.

При переключении задач с использованием шлюза дескриптор TSS целевой задачи определяется селектором шлюза задачи.

При этом, PL шлюза TSS и дескриптора TSS могут не совпадать.

=> использование шлюзов TSS допускает любые межуровневые переключения задач.

При использовании команд IRET, команды вызова прерываний, например, INT n или в случаях прерываний и ловушек, как прямое переключение задач, так и переключение задач с использованием шлюзов задач производится вне зависимости от значений, соответственно, DPLTSS или DPLШлTSS, т.е. без проверок условий доступа по уровням привилегий.

Физический факультет, ЭВУ и системы, 7 семестр,2012 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems, 7th semester,2012 Dr. Mokhovikov

Программное переключение

Операция переключения задач сохраняет состояние процессора (в TSS текущей

Программное переключение

Операция переключения задач сохраняет состояние процессора (в TSS текущей

Если флаг сброшен, то выполняется обычный возврат из прерывания (через стек). Если флаг установлен, то команда IRET инициирует обратное переключение задач.

В случае использования команды CALL - возврат должен происходить по команде IRET,

которая сохраняет контекст завершаемой задачи и загружает контекст прерванной.

Алгоритм работы команды IRET в случае возврата из прерывания и в случае обратного

переключения задач различен. И определяется значением флага NT (Nested Task)

Физический факультет, ЭВУ и системы, 7 семестр,2012 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems, 7th semester,2012 Dr. Mokhovikov

Программное переключение

● После загрузки компьютера флаг NT находится в установленном состоянии.

Программное переключение

● После загрузки компьютера флаг NT находится в установленном состоянии.

Однако любое аппаратное прерывание или исключение сбрасывает этот флаг, в результате чего команда IRET, завершающая обработчик, выполняется в «облегченном» варианте (возврат через стек).

● То же происходит при выполнении процессором команды программного прерывания INT. Поскольку команда IRET восстанавливает исходное состояние регистра флагов, после завершения обработчика флаг NT снова оказывается установленным (если, конечно, он не был явно сброшен выполняемой программой).

При выполнении процедуры переключения на новую задачу через шлюз или непосредственно через TSS, процессор сохраняет в TSS текущей задачи слово флагов и устанавливает в регистре флагов бит NT. Команда IRET, завершающая задачу, обнаруживает NT=1 и, вместо осуществления возврата через стек, инициирует механизм обратного переключения задач.

IRET – это POP-аналог

Физический факультет, ЭВУ и системы, 7 семестр,2012 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems, 7th semester,2012 Dr. Mokhovikov

Последовательность действий при переключении задач

1. Проверяет право на переключение по уровню

Последовательность действий при переключении задач

1. Проверяет право на переключение по уровню

2. Сохраняет в TSS исходной задачи ее контекст;

3. Загружает в регистр TR селектор TSS новой задачи;

4. В поле связи TSS новой задачи сохраняется селектор TSS исходной задачи, что обеспечивает возможность будущего обратного переключения. Считывает контекст из TSS новой задачи (в CS:IP появляется точка входа в новую задачу).

Флаг NT ¬ 1. Переключение произошло.

5. Когда в новой исполняемой задаче встретится команда IRET, она будет выполняться как обратное переключение задач (NT=1);

6. Контекст текущей задачи сохранится в ее TSS ;

7. В регистр TR загрузится селектор TSS исходной задачи (из поля связи TSS текущей задачи);

8. Регистры восстановится контекст исходной задачи.

При переключении задачи процессор выполняет следующую последовательность действий:

Физический факультет, ЭВУ и системы, 7 семестр,2012 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems, 7th semester,2012 Dr. Mokhovikov

Страничное управление памятью

Physics Faculty, Electronic Computing Devices & Systems, 7th semester,2012

Страничное управление памятью

Physics Faculty, Electronic Computing Devices & Systems, 7th semester,2012

Страничное управление (Paging) является средством организации виртуальной памяти с подкачкой страниц по запросу (Demand-Paged Virtual Memory).

В отличие от сегментации, которая организует программы и данные в модули различного размера, страничная организация оперирует с памятью, как с набором страниц одинакового размера.

В момент обращения страница может присутствовать в физической оперативной памяти,

а может быть выгруженной на внешнюю (дисковую) память.

Страничное управление памятью

При обращении к выгруженной странице памяти процессор вырабатывает

Страничное управление памятью

При обращении к выгруженной странице памяти процессор вырабатывает

Страницы не имеют прямой связи с логической структурой данных или программ.

В то время как селекторы можно рассматривать как логические имена модулей кодов и данных, страницы представляют части этих модулей.

Учитывая обычное свойство локальности (близкого расположения требуемых ячеек памяти) кода и ссылок на данные, в оперативной памяти в каждый момент времени следует хранить только небольшие области сегментов, необходимые активным задачам.

Эту возможность (а следовательно, и увеличение допустимого числа одновременно выполняемых задач при ограниченном объеме оперативной памяти) как раз и обеспечивает страничное управление памятью.

Physics Faculty, Electronic Computing Devices & Systems, 7th semester,2012 Dr.Mokhovikov Alexander Yurievich

Страничное управление памятью

!

Поскольку имеется возможность расширения физического адреса до 36 бит

Страничное управление памятью

!

Поскольку имеется возможность расширения физического адреса до 36 бит

Режимом страничной переадресации управляют биты PG в регистре CR0, флаги PAE и PSE в СR4 и бит размера страницы PS в PDE – элементе каталога страниц

Physics Faculty, Electronic Computing Devices & Systems, 7th semester,2012 Dr.Mokhovikov Alexander Yurievich

Базовый механизм страничного управления

Базовый механизм страничного управления использует двухуровневую табличную

Базовый механизм страничного управления

Базовый механизм страничного управления использует двухуровневую табличную

Механизм имеет три части:

Каталог страниц (Page Directory),

Таблицы страниц (Page Table)

Собственно страницы (Page Frame).

Механизм включается установкой бита PG=1 в регистре CRO.

Регистр CR2 хранит линейный адрес отказа (Page Fault Linear Address) — адрес памяти, по которому был обнаружен последний отказ страницы.

Регистр CR3 хранит физический адрес каталога страниц (Page Directory Physical Base Address). Его младшие 12 бит всегда нулевые (каталог выравнивается по границе страницы).

Physics Faculty, Electronic Computing Devices & Systems, 7th semester,2012 Dr.Mokhovikov Alexander Yurievich

Книга «Assembler. Учебник для ВУЗов», автор Юров

Книга «Процессоры Pentium4, Athlon и

Книга «Assembler. Учебник для ВУЗов», автор Юров

Книга «Процессоры Pentium4, Athlon и

Книга «Модернизация и ремонт ПК»,автор Скотт Мюллер

Книга «Архитектура ЭВМ», автор Танненбаум

Книга «Организация ЭВМ», автор Хамахер

Используемая литература:

ЭВУ SUPER!!!

Physics Faculty, Electronic Computing Devices & Systems, 7th semester,2012 Dr.Mokhovikov Alexander Yurievich

В следующей серии

Виртуальная память

Physics Faculty, Electronic Computing Devices & Systems, 7th

В следующей серии

Виртуальная память

Physics Faculty, Electronic Computing Devices & Systems, 7th

о финансовой системе

о финансовой системе Презентация на тему "Упевнений крок" - скачать презентации по Педагогике

Презентация на тему "Упевнений крок" - скачать презентации по Педагогике E-learning как часть системы управления знаниями

E-learning как часть системы управления знаниями Пример воздействия агрессивной среды на неметаллические конструкции

Пример воздействия агрессивной среды на неметаллические конструкции Лекция 5. Тип Круглые черви Nemathelminthes – паразиты человека и животных.

Лекция 5. Тип Круглые черви Nemathelminthes – паразиты человека и животных.  Политические партии, партийные системы и общественно - политические движения

Политические партии, партийные системы и общественно - политические движения Прогнозирование конфликта

Прогнозирование конфликта Применение метода стабилизации связей к задачам неголономной механики

Применение метода стабилизации связей к задачам неголономной механики Технология разработки программного обеспечения. (Лекция 8.5)

Технология разработки программного обеспечения. (Лекция 8.5) Пятничные размышления на волнующие темы

Пятничные размышления на волнующие темы  Ти - зірка (пісня)

Ти - зірка (пісня) Тест по программированию

Тест по программированию Власть как политический институт

Власть как политический институт Экологические основы природопользования

Экологические основы природопользования Презентация "Макроэкономика структуры капитала" - скачать презентации по Экономике

Презентация "Макроэкономика структуры капитала" - скачать презентации по Экономике Теоретические основы электротехники (практика 1)

Теоретические основы электротехники (практика 1) Презентация на тему "Проектная деятельность в детском саду" - скачать презентации по Педагогике

Презентация на тему "Проектная деятельность в детском саду" - скачать презентации по Педагогике Национальный Музей Австралии Серия «Музеи мира»

Национальный Музей Австралии Серия «Музеи мира»  Улаштування та технічне обслуговування кривошипно-шатунного механізму. Влаштування та ТО газорозподільного механізму (1)

Улаштування та технічне обслуговування кривошипно-шатунного механізму. Влаштування та ТО газорозподільного механізму (1) Цветы. Доставка

Цветы. Доставка Харис Якупов (Харис Габдрахман улы Якупов) (1919—2010)

Харис Якупов (Харис Габдрахман улы Якупов) (1919—2010) Процессы управления: целеполагание и оценка ситуации

Процессы управления: целеполагание и оценка ситуации Таблицы … - контейнер для элементов таблиц

Таблицы … - контейнер для элементов таблиц Волны

Волны П.А. Федотов (1815-1852)

П.А. Федотов (1815-1852) Студенттің өзіндік жұмысы. Қазақстандағы діни ағымдар

Студенттің өзіндік жұмысы. Қазақстандағы діни ағымдар Розвиток системи безпечного поводження з відпрацьованим ядерним паливом та радіоактивними відходами АЕС України

Розвиток системи безпечного поводження з відпрацьованим ядерним паливом та радіоактивними відходами АЕС України Канонические диаграммы языка UML 2.х

Канонические диаграммы языка UML 2.х