Содержание

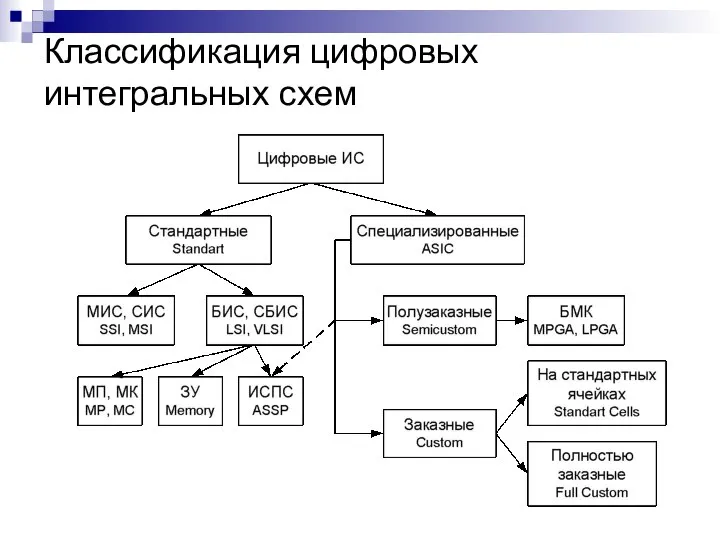

- 2. Классификация цифровых интегральных схем

- 3. МИС, СИС, БИС, СБИС – микросхемы малого, среднего, большого и сверхбольшого уровня интеграции. МП – микропроцессоры

- 4. ИСПС – интегральные схемы с программируемой структурой или ПЛИС – программируемые логические интегральные схемы SSI, MSI,

- 5. Стандартные ИС – это готовые изделия, производимые массовыми тиражами, затраты на проектирование мало влияют на конечную

- 6. Стандартные цифровые ИС МИС и СИС используются и сейчас для отдельных задач, но сложные устройства делать

- 7. Стандартные ЦИС (прод.) ИСПС – дают возможность использовать ИС высокого уровня интеграции не только в массовых

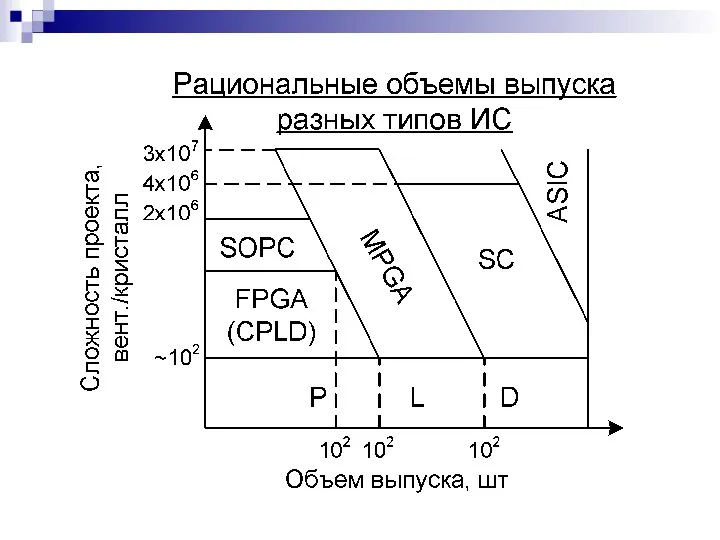

- 8. До создания ПЛИС специализирован-ные проекты, в зависимости от сложности проекта, его тиражности, требований к техническим и

- 9. Полностью заказные схемы целиком проектируются под требования конкретного заказчика. Проектировщик имеет полную свободу действий, определяя схему

- 10. Схемы на стандартных ячейках разрабатываются на основе разработанной ранее библиотеки стандартных ячеек, которая представляет собой набор

- 11. БМК представляют собой стандартный полуфабрикат, который доводится до готового изделия с помощью разработки индивидуальных межсоединений. Для

- 12. Проектирование на ПЛИС стало более дешевой альтернативой методам проектирования с использованием специализированных ИС и БМК. В

- 13. Сравнительная таблица вариантов создания специализированных проектов на ИС

- 14. Базовые Матричные Кристаллы БМК – полузаказная ИС. БМК – кристалл, на прямоугольной поверхности которого размещены внутренняя

- 15. В БМК канальной структуры между строками и столбцами базовых ячеек или их компактных групп оставляются горизонтальные

- 16. Структура БМК

- 17. Классификация логических схем программируемой логики по уровню интеграции и связанной с ним логической сложности; по архитектуре

- 18. Классификация логических схем программируемой логики Рассмотрим классификацию по 3-м основным признакам: архитектуре уровню интеграции и однородности/гибридности

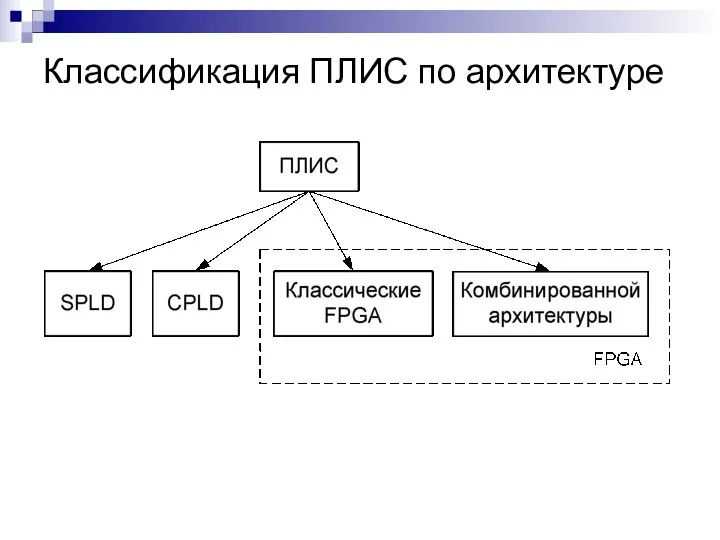

- 19. Классификация ПЛИС по архитектуре

- 20. SPLD – Simple Programmable Logic Device, простые программируемые устройства. ПЛМ, PLA – программируемые логические матрицы, Programmable

- 21. SPLD реализуют дизъюнктивные нормальные формы (ДНФ) переключательных функций. Структура: Включенные последовательно две матрицы элементов: И, ИЛИ.

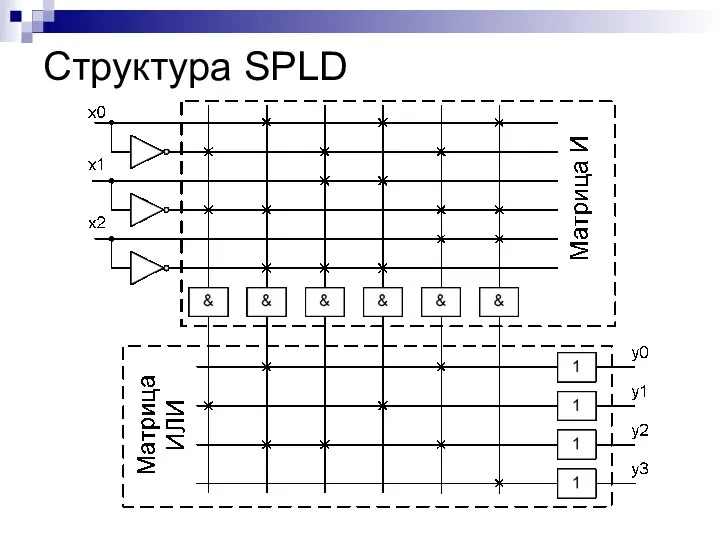

- 22. Структура SPLD

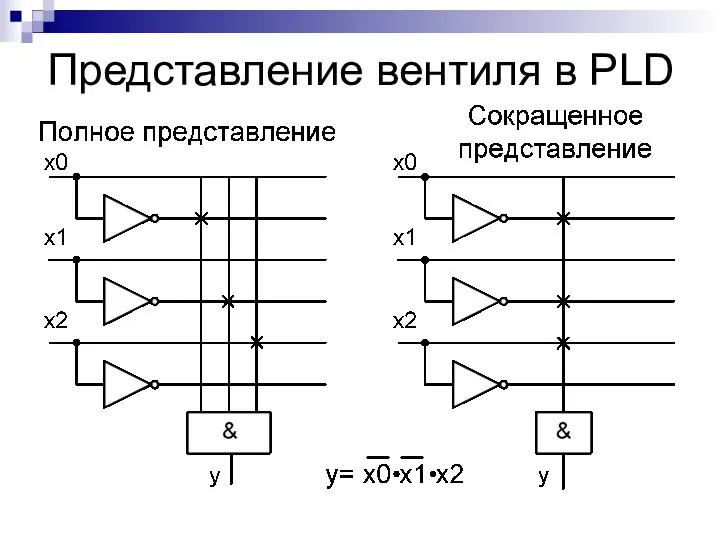

- 23. Представление вентиля в PLD

- 24. CPLD – состоят из нескольких блоков, подобных ПМЛ, которые объединяются с помощью программируемой коммутационной матрицы. Фирмы

- 25. Классические FPGA FPGA – состоят из большого числа конфигурируемых логических блоков (ЛБ), расположенных по строкам и

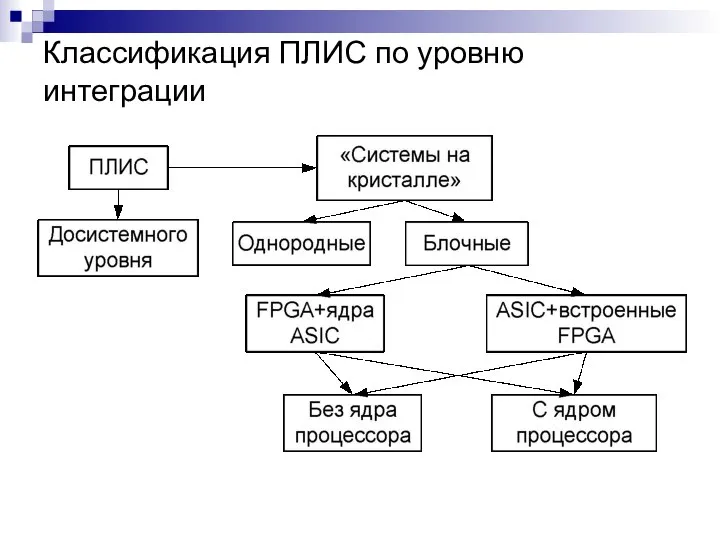

- 26. Классификация ПЛИС по уровню интеграции

- 27. Классификация ПЛИС по кратности программирования

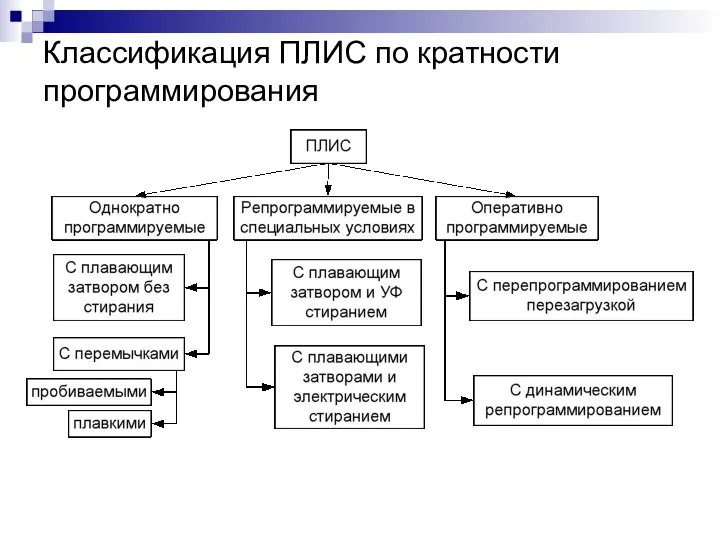

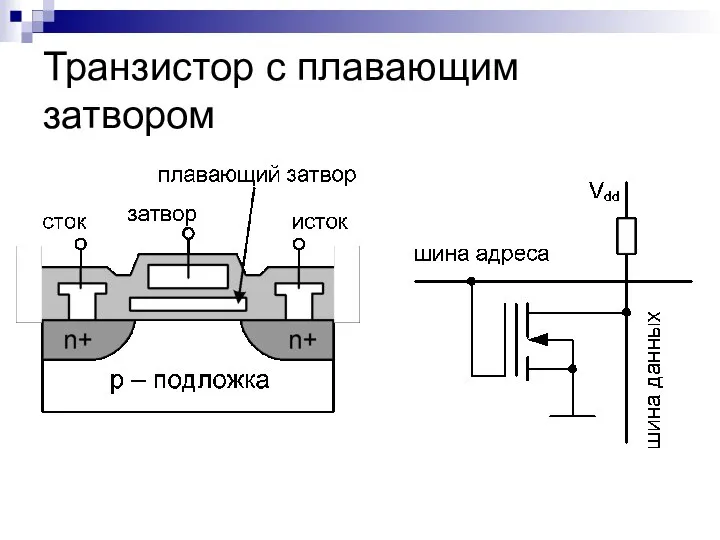

- 28. Транзистор с плавающим затвором

- 29. ПЛИС с динамическим репрограммированием Такие ПЛИС открывают ряд новых возможностей в области построения устройств и систем

- 30. Общие (системные) свойства микросхем программируемой логики Универсальность и связанные с нею высокий спрос со стороны потребителей,

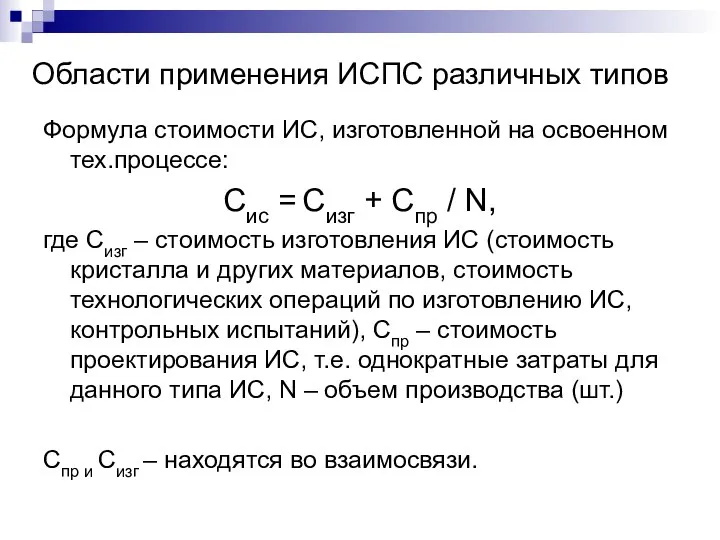

- 31. Области применения ИСПС различных типов Формула стоимости ИС, изготовленной на освоенном тех.процессе: Сис = Сизг +

- 33. Место ИСПС в процессе создания современной аппаратуры Львиной долей инженерных разработок в современной России является использование

- 35. Скачать презентацию

Комплексная система контроля доступа и видеонаблюдения на базе программного обеспечения TRASSIR и Sphinx

Комплексная система контроля доступа и видеонаблюдения на базе программного обеспечения TRASSIR и Sphinx Презентация Своя игра по технологии

Презентация Своя игра по технологии  Мерцательная аритмия: вопросы патогенеза, клиническая значимость, стратегии лечения Голицын С.П.

Мерцательная аритмия: вопросы патогенеза, клиническая значимость, стратегии лечения Голицын С.П.  Арес – неукротимый бог войны

Арес – неукротимый бог войны War for Independence

War for Independence ОПЕРАЦИОННАЯ СИСТЕМА КОМПЬЮТЕРА

ОПЕРАЦИОННАЯ СИСТЕМА КОМПЬЮТЕРА Геометрические построения. Деление окружности

Геометрические построения. Деление окружности Ловкость. Характеристика двигательно-координационных способностей

Ловкость. Характеристика двигательно-координационных способностей Проблемный урок алгебры в 7 классе По теме «Действия со степенями» Подготовил: учитель математики МБОУ «Красноярская СОШ» Учите

Проблемный урок алгебры в 7 классе По теме «Действия со степенями» Подготовил: учитель математики МБОУ «Красноярская СОШ» Учите Философия образования: основные этапы развития

Философия образования: основные этапы развития Двигатель внутреннего сгорания на марку автомобиля ВАЗ

Двигатель внутреннего сгорания на марку автомобиля ВАЗ Спутниковое тв в мире

Спутниковое тв в мире Проектирование анкеты

Проектирование анкеты Презентация "религия" - скачать презентации по МХК

Презентация "религия" - скачать презентации по МХК Морфология микроорганизмов

Морфология микроорганизмов  Правовое обеспечение бизнеса

Правовое обеспечение бизнеса  Метод Мерцалова

Метод Мерцалова Игрушка-дергунчик Дед Мороз

Игрушка-дергунчик Дед Мороз Сочинение по картине К.Н. Успенской-Кологривовой «Не взяли на рыбалку»

Сочинение по картине К.Н. Успенской-Кологривовой «Не взяли на рыбалку» «Понятие риторического идеала» Подготовила студентка Житкова Екатерина 1 курса экономического факультета группа Э123б

«Понятие риторического идеала» Подготовила студентка Житкова Екатерина 1 курса экономического факультета группа Э123б Исправь стихотворение

Исправь стихотворение  Терроризм в современном мире и в России

Терроризм в современном мире и в России Cultural awareness

Cultural awareness Взаимодействие общества и природы

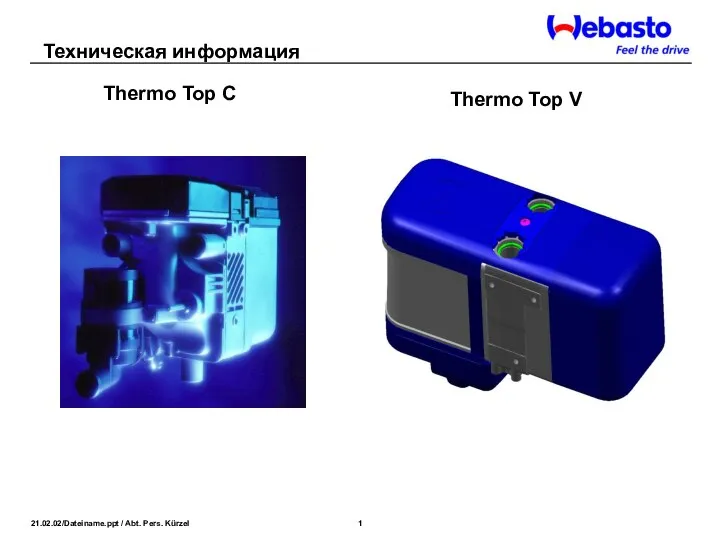

Взаимодействие общества и природы Техническая информация Thermo Top C, Thermo Top V

Техническая информация Thermo Top C, Thermo Top V Правила оформления документов (практические задания)

Правила оформления документов (практические задания) Prezentatsia2

Prezentatsia2 Табиғи консервілерді метрологиялық қамтамасыз ету. Жасыл бұршақ консервісі

Табиғи консервілерді метрологиялық қамтамасыз ету. Жасыл бұршақ консервісі