Содержание

- 2. Цели и задачи Изучение функционирования цифровых КМДП-схем на примере КМДП-инвертора. Изучение статических и динамических характеристик. Передаточная

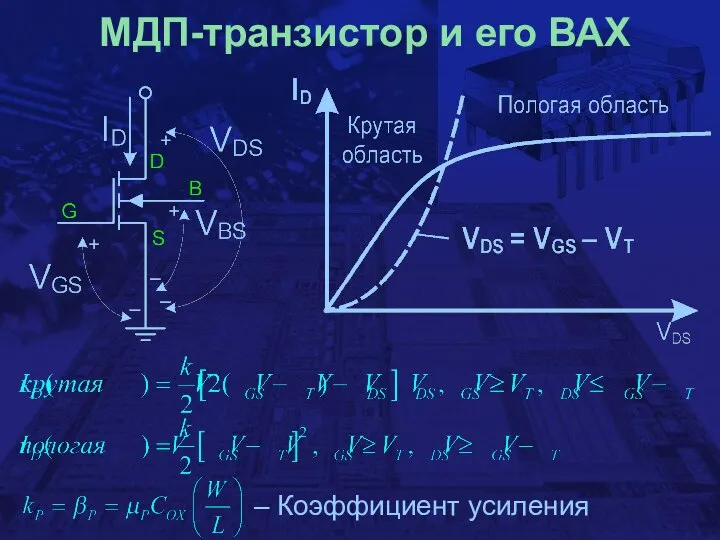

- 3. МДП-транзистор и его ВАХ – Коэффициент усиления

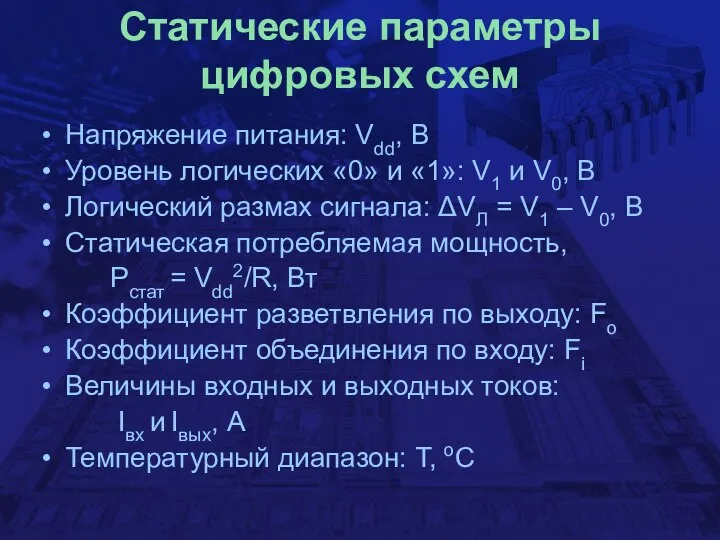

- 4. Статические параметры цифровых схем Напряжение питания: Vdd, В Уровень логических «0» и «1»: V1 и V0,

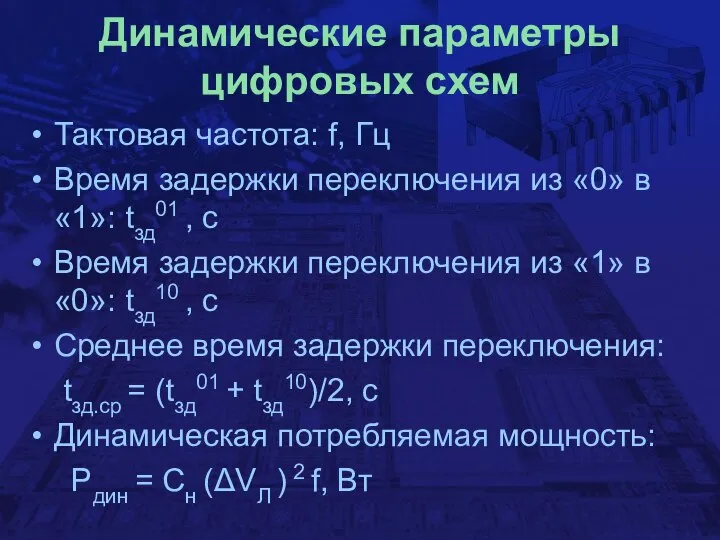

- 5. Динамические параметры цифровых схем Тактовая частота: f, Гц Время задержки переключения из «0» в «1»: tзд01

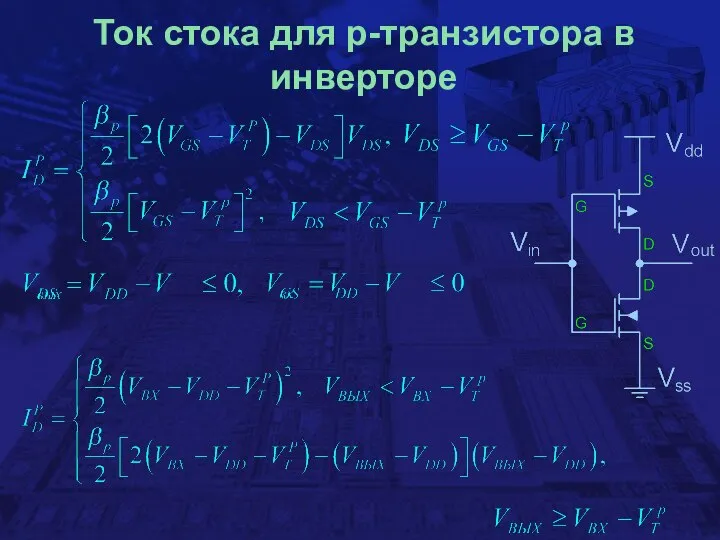

- 6. Ток стока для p-транзистора в инверторе

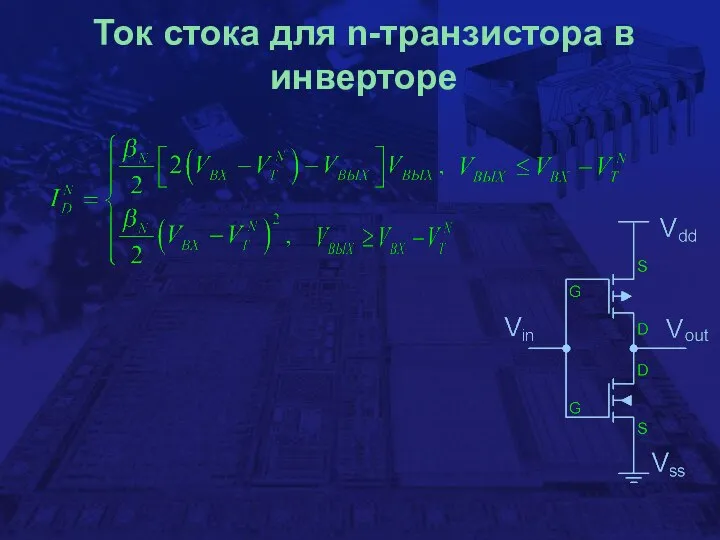

- 7. Ток стока для n-транзистора в инверторе

- 8. ВАХ инвертора

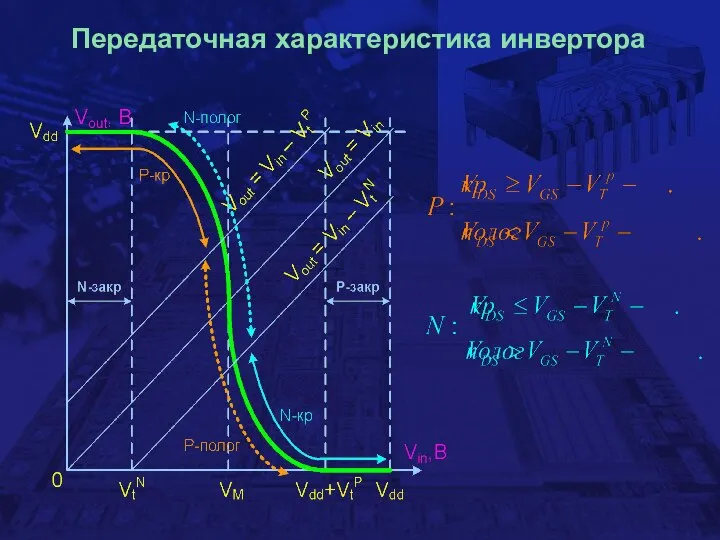

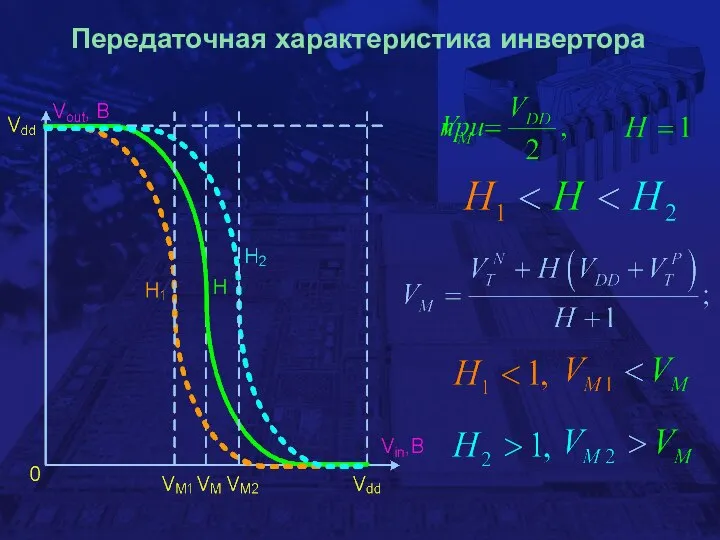

- 9. Передаточная характеристика инвертора

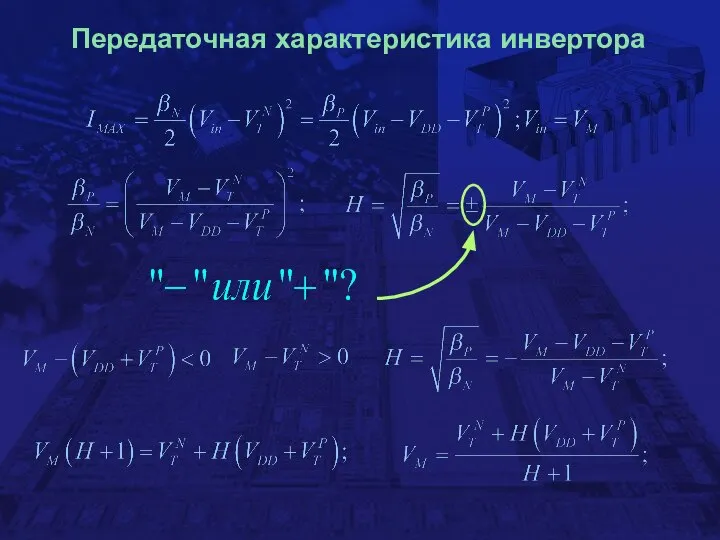

- 10. Передаточная характеристика инвертора

- 11. Передаточная характеристика инвертора

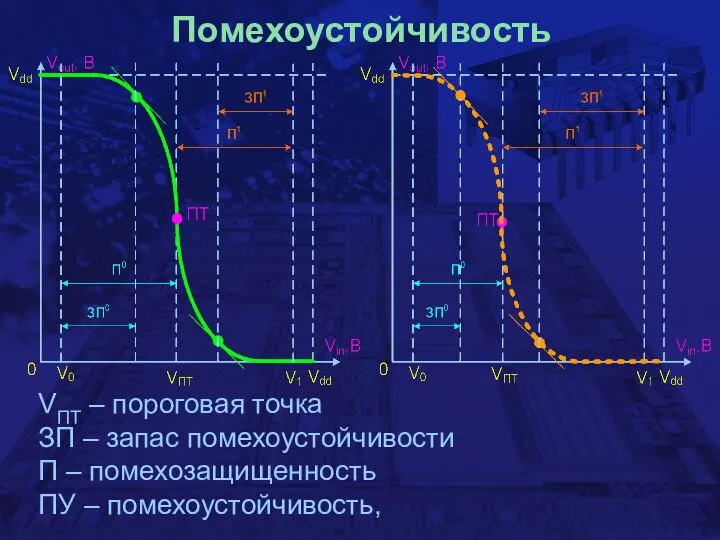

- 12. Помехоустойчивость VПТ – пороговая точка ЗП – запас помехоустойчивости П – помехозащищенность ПУ – помехоустойчивость,

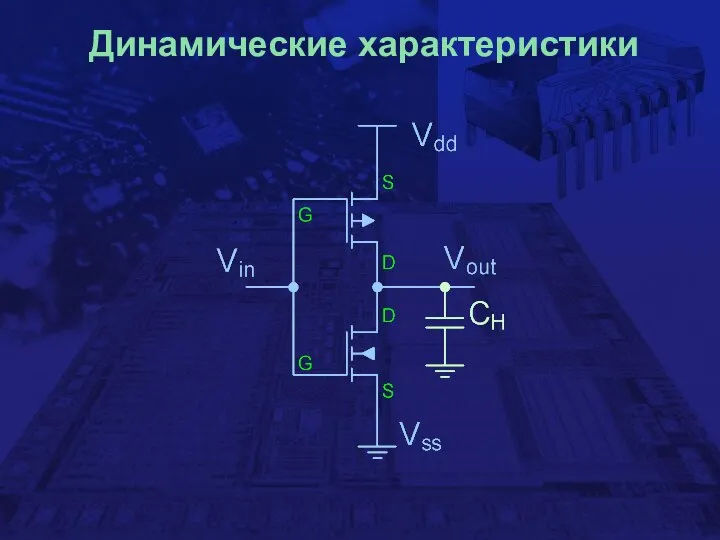

- 13. Динамические характеристики

- 14. Динамические характеристики

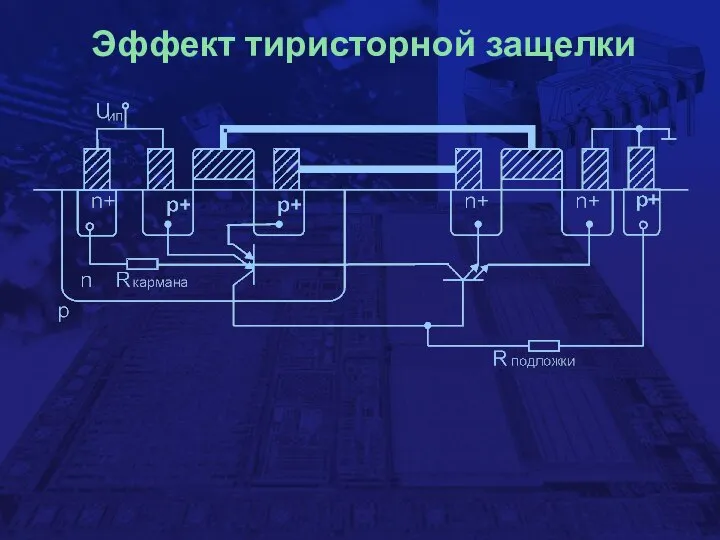

- 15. Эффект тиристорной защелки

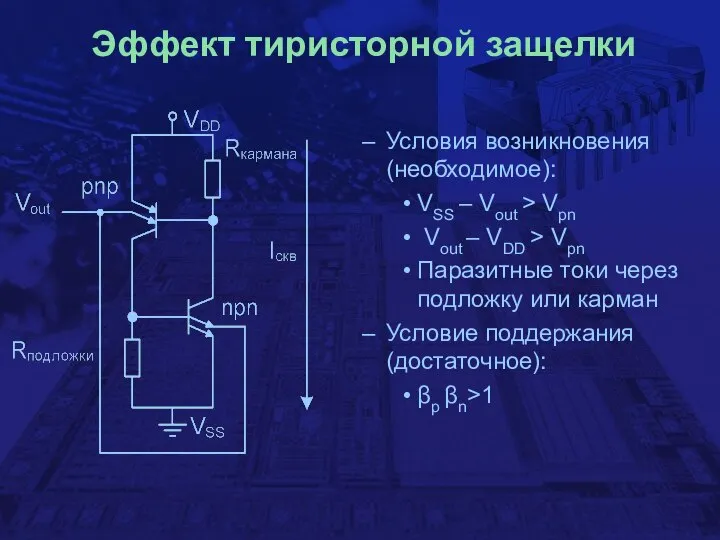

- 16. Эффект тиристорной защелки Условия возникновения (необходимое): VSS – Vout > Vpn Vout – VDD > Vpn

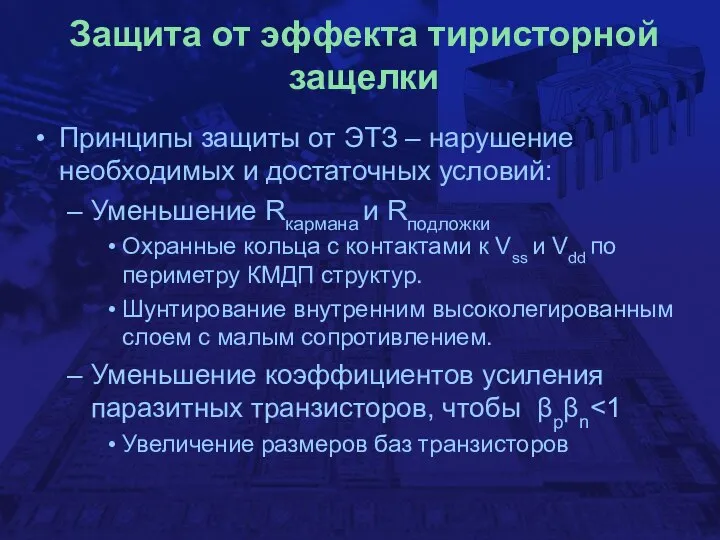

- 17. Защита от эффекта тиристорной защелки Принципы защиты от ЭТЗ – нарушение необходимых и достаточных условий: Уменьшение

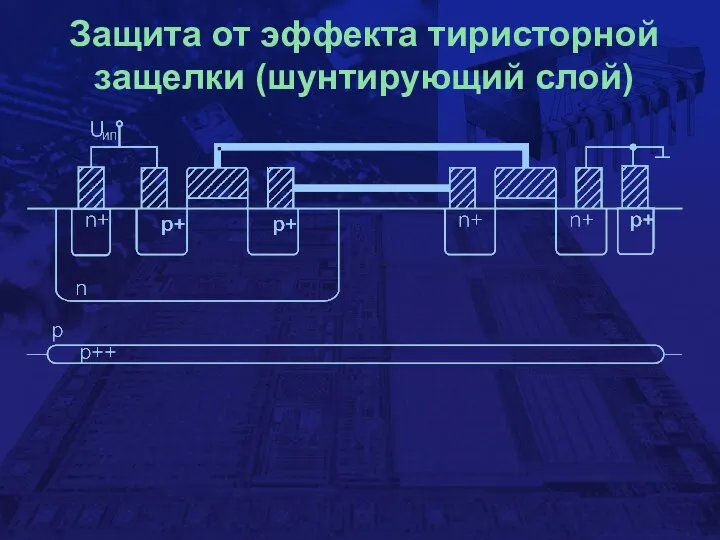

- 18. Защита от эффекта тиристорной защелки (шунтирующий слой)

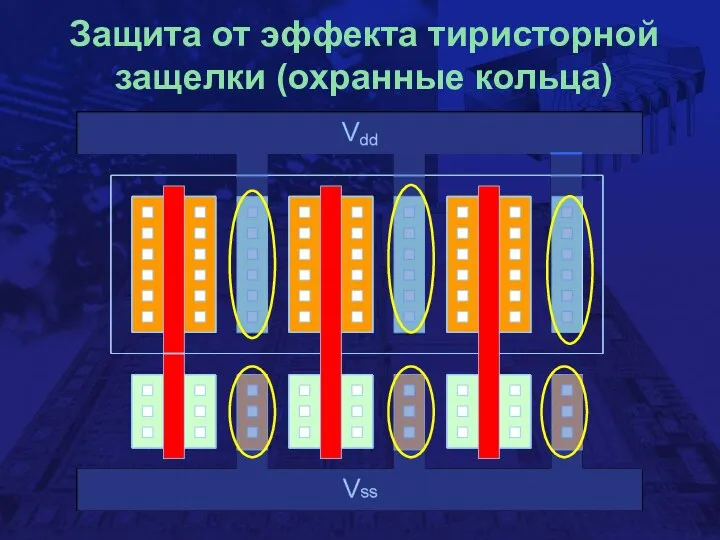

- 19. Защита от эффекта тиристорной защелки (охранные кольца)

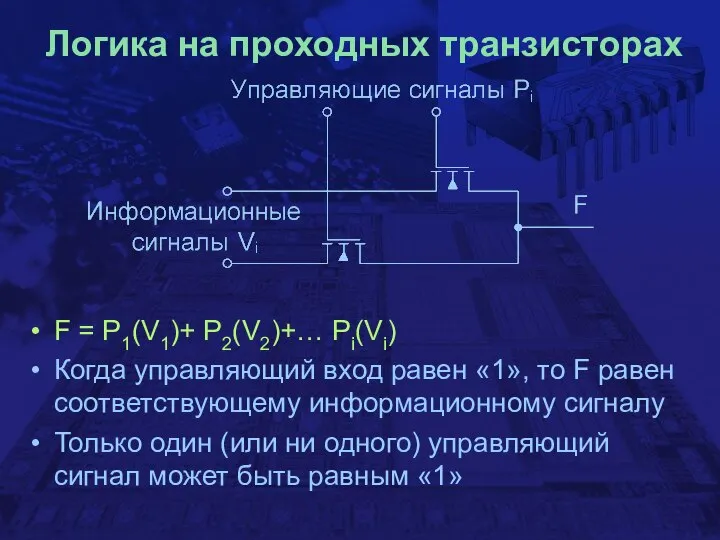

- 20. Логика на проходных транзисторах F = P1(V1)+ P2(V2)+… Pi(Vi) Когда управляющий вход равен «1», то F

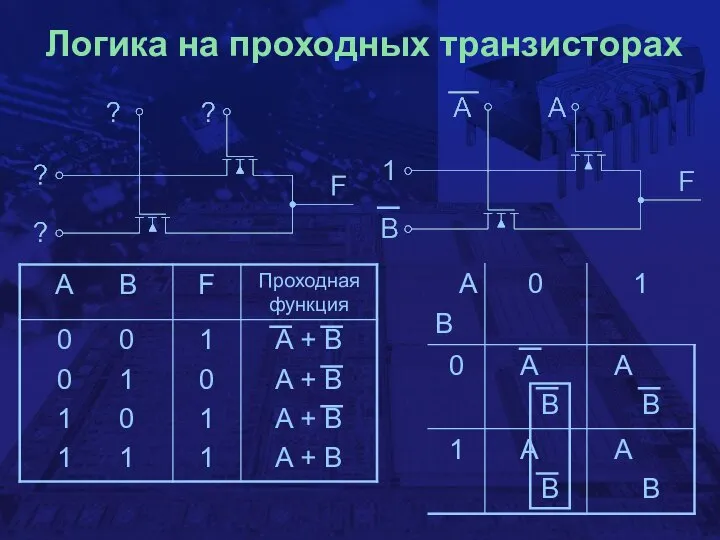

- 21. Логика на проходных транзисторах

- 23. Скачать презентацию

Работа с файлами. Программирование на языке Паскаль

Работа с файлами. Программирование на языке Паскаль Введение в экономическую теорию

Введение в экономическую теорию Специальная психология Задержка психического развития (ЗПР).

Специальная психология Задержка психического развития (ЗПР). Британский парламентский формат

Британский парламентский формат .Case Champ 2012..Case Champ 2012.ITT – універсальна інвестиційна група Структура Інвестиційної Групи ІТТ Брокерідж та інвестбанкінг (ІТТ- Інвест)

.Case Champ 2012..Case Champ 2012.ITT – універсальна інвестиційна група Структура Інвестиційної Групи ІТТ Брокерідж та інвестбанкінг (ІТТ- Інвест) П. А. Муханов - Русский литератор, историк, декабрист

П. А. Муханов - Русский литератор, историк, декабрист Здоровье

Здоровье Геополитика исламского мира

Геополитика исламского мира Народные промыслы Юго-Восточной Азии

Народные промыслы Юго-Восточной Азии Болезнь Альцгеймера (сенильная деменция альцгеймеровского типа)

Болезнь Альцгеймера (сенильная деменция альцгеймеровского типа)  Венеціанський карнавал

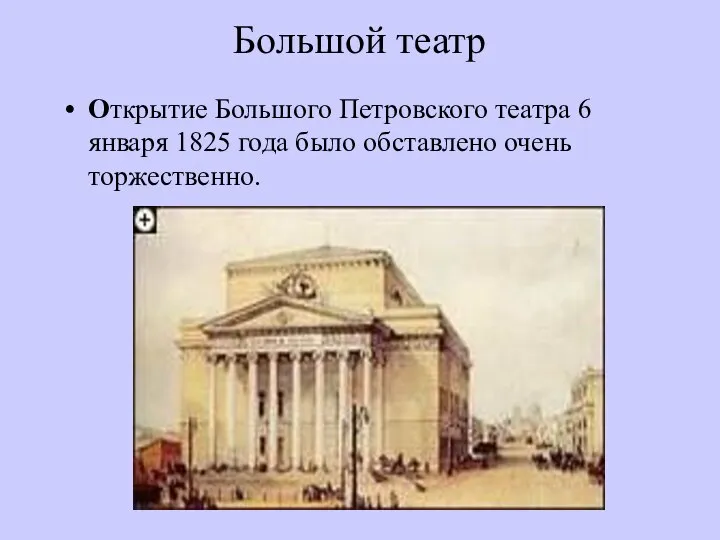

Венеціанський карнавал Большой театр Открытие Большого Петровского театра 6 января 1825 года было обставлено очень торжественно.

Большой театр Открытие Большого Петровского театра 6 января 1825 года было обставлено очень торжественно. Оптовая торговля. Современные тенденции развития оптовой торговли. Подготовил группа

Оптовая торговля. Современные тенденции развития оптовой торговли. Подготовил группа Справочные правовые системы

Справочные правовые системы Презентация "История русского народного костюма." - скачать презентации по МХК

Презентация "История русского народного костюма." - скачать презентации по МХК Презентация Основные тенденции развития российской налоговой политики

Презентация Основные тенденции развития российской налоговой политики Особенности закупок строительных работ

Особенности закупок строительных работ Богословие III века. Святой Григорий Неокесарийский, Триадологические ериси III века. Священомученник Мефодий Патраский

Богословие III века. Святой Григорий Неокесарийский, Триадологические ериси III века. Священомученник Мефодий Патраский Физические упражнения, рекомендуемые сочетать с силовыми упражнениями

Физические упражнения, рекомендуемые сочетать с силовыми упражнениями Довольство Аллаха – в довольстве родителей

Довольство Аллаха – в довольстве родителей Презентация Обзор (краткое описание) сайта организации ОПЭК (OPEC)

Презентация Обзор (краткое описание) сайта организации ОПЭК (OPEC)  Социальная политика государства в ближайшей и долгосрочной перспективе

Социальная политика государства в ближайшей и долгосрочной перспективе  Методи об'єктно-орієнтованого програмування

Методи об'єктно-орієнтованого програмування Лингвистика на пути преобразований

Лингвистика на пути преобразований CRM для турагенств

CRM для турагенств Глава 3_2

Глава 3_2 Паскаль. Циклические вычисления

Паскаль. Циклические вычисления Циклы

Циклы