Содержание

- 2. Структура простой МПС Магистрально-модульная структура Принстонская архитектура

- 3. Характеристики микропроцессора Тип корпуса Назначение выводов Архитектура Год выпуска Кодовое название Количество транзисторов Ядро Кэш L1

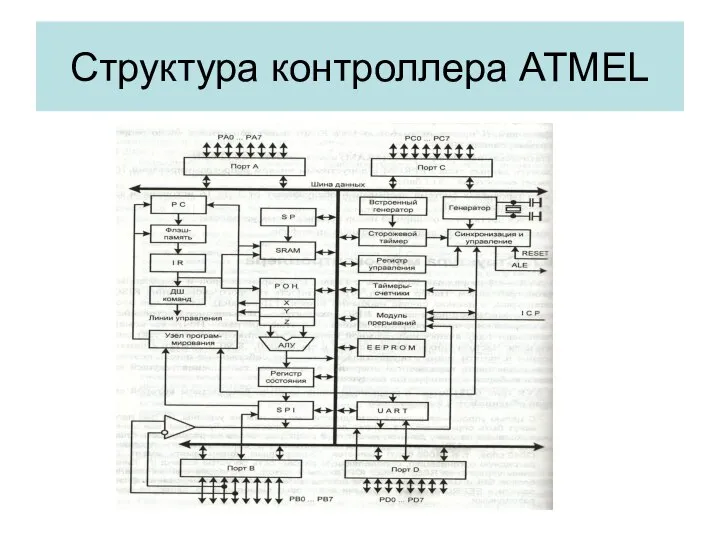

- 4. Структура контроллера ATMEL

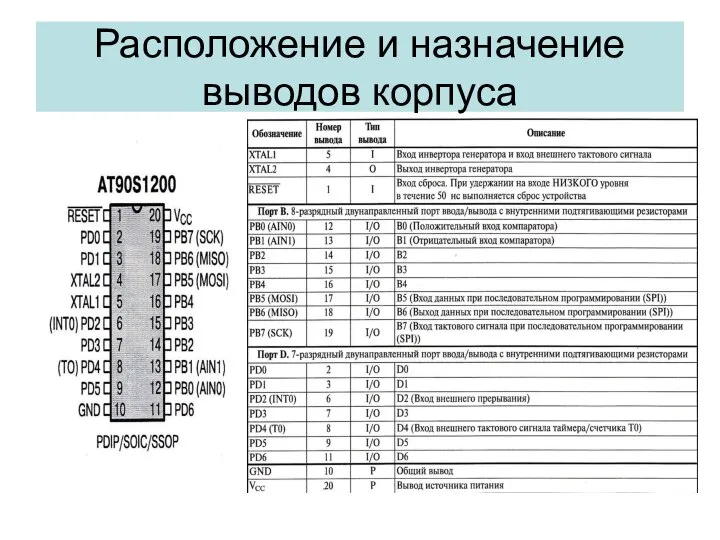

- 5. Расположение и назначение выводов корпуса

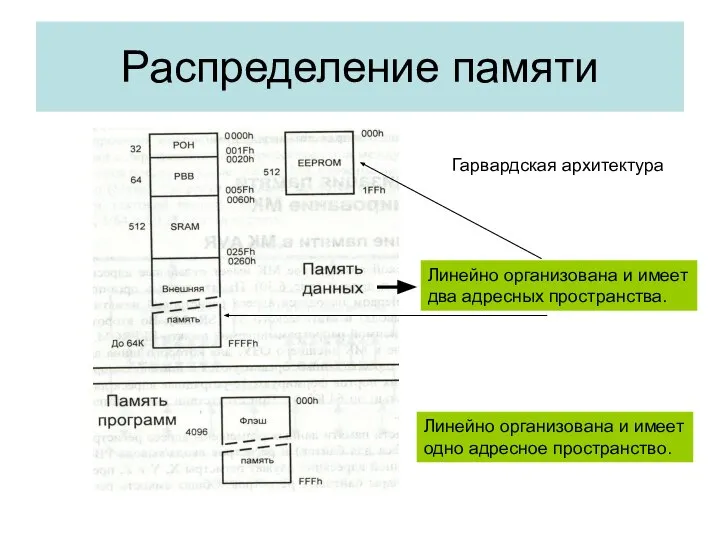

- 6. Распределение памяти Гарвардская архитектура Линейно организована и имеет два адресных пространства. Линейно организована и имеет одно

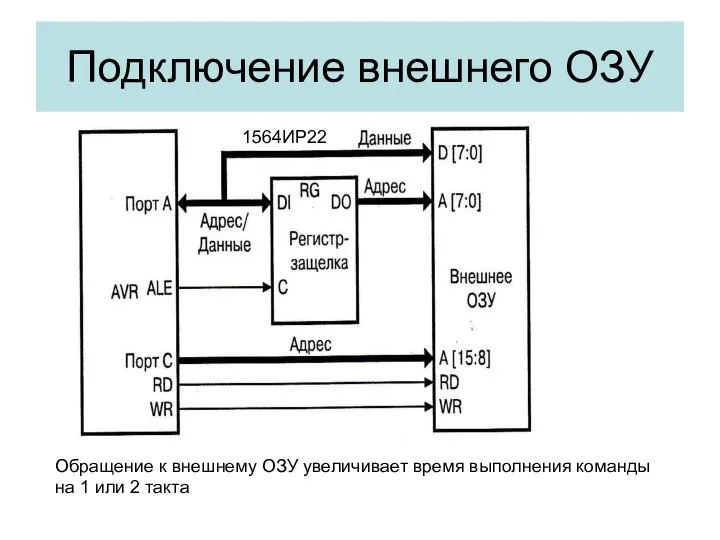

- 7. Подключение внешнего ОЗУ 1564ИР22 Обращение к внешнему ОЗУ увеличивает время выполнения команды на 1 или 2

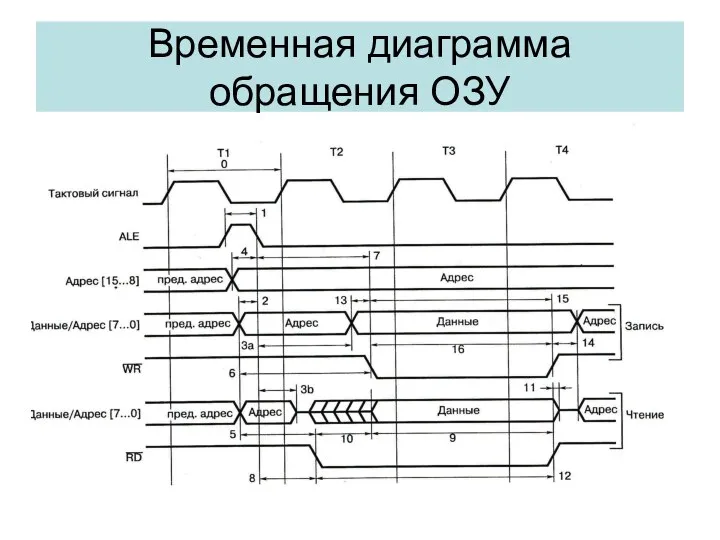

- 8. Временная диаграмма обращения ОЗУ

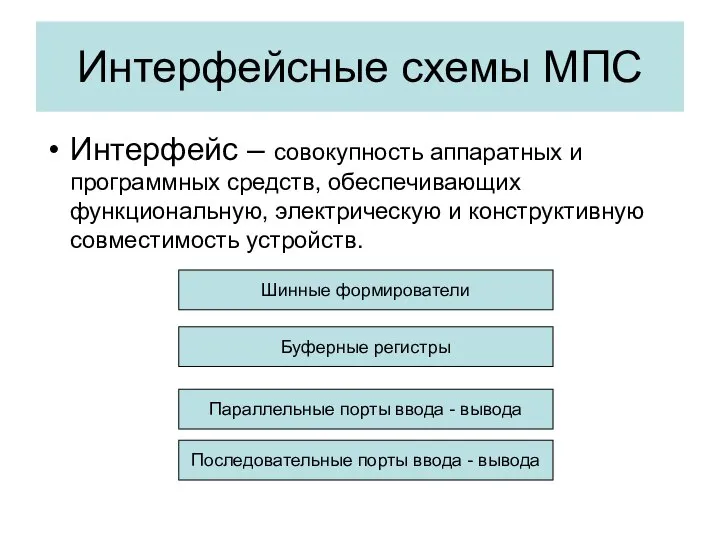

- 9. Интерфейсные схемы МПС Интерфейс – совокупность аппаратных и программных средств, обеспечивающих функциональную, электрическую и конструктивную совместимость

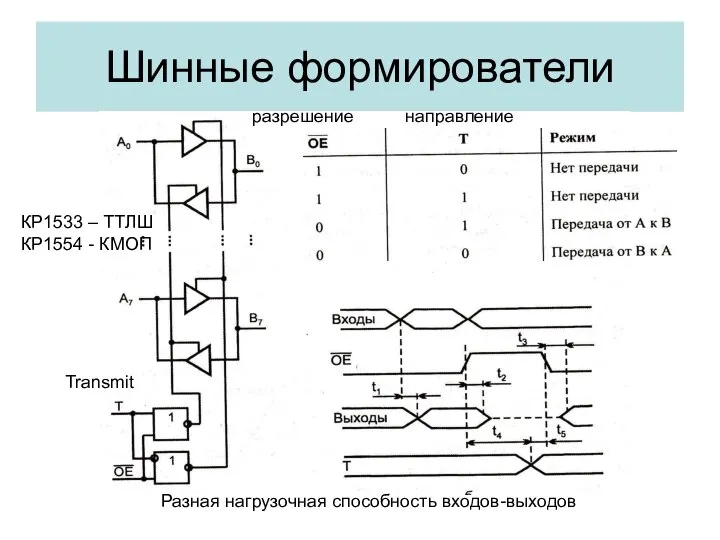

- 10. Шинные формирователи Transmit направление разрешение Разная нагрузочная способность входов-выходов КР1533 – ТТЛШ КР1554 - КМОП

- 11. Буферные регистры Временное хранение данных

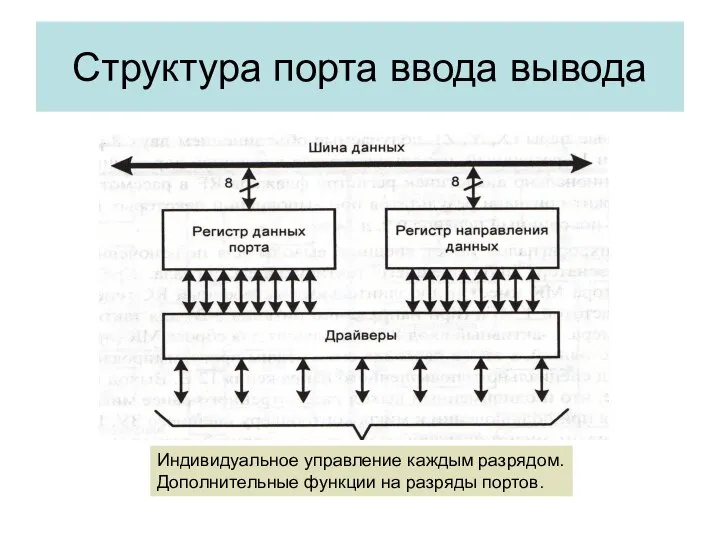

- 12. Структура порта ввода вывода Индивидуальное управление каждым разрядом. Дополнительные функции на разряды портов.

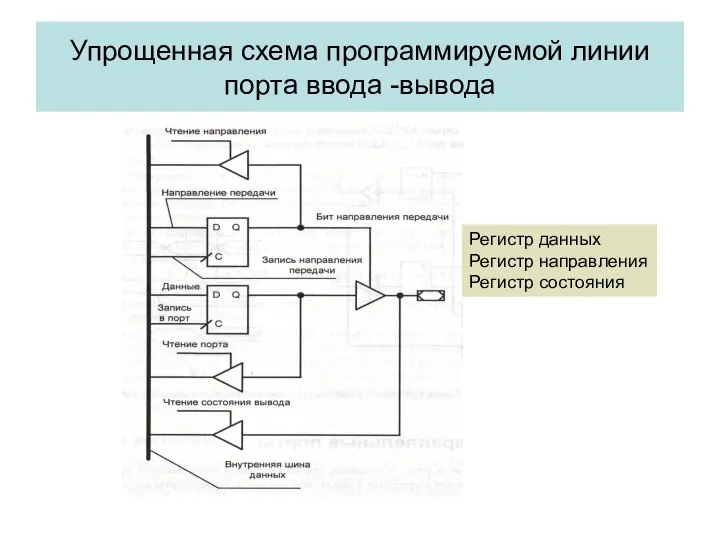

- 13. Упрощенная схема программируемой линии порта ввода -вывода Регистр данных Регистр направления Регистр состояния

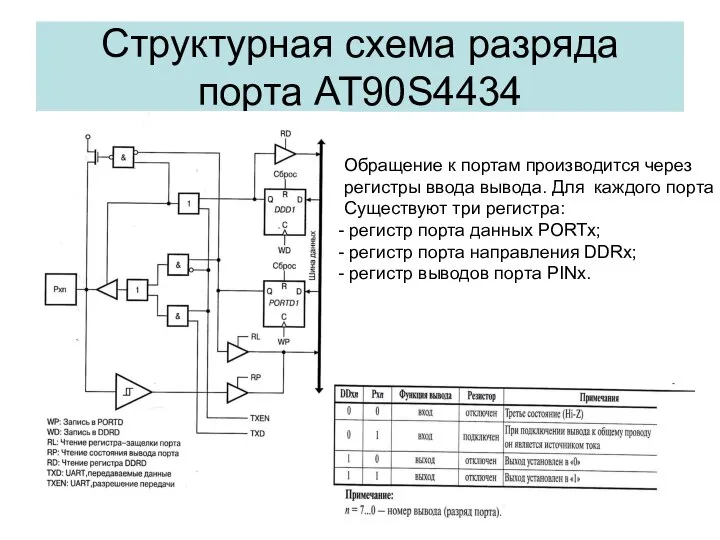

- 14. Структурная схема разряда порта AT90S4434 Обращение к портам производится через регистры ввода вывода. Для каждого порта

- 16. Скачать презентацию

Австралия

Австралия Презентация на тему "Образовательные технологии как способ развития качества образования" - скачать презентации по Педагоги

Презентация на тему "Образовательные технологии как способ развития качества образования" - скачать презентации по Педагоги Психолого-педагогическое сопровождение развития детей с особыми образовательными потребностями Подготовила материал :

Психолого-педагогическое сопровождение развития детей с особыми образовательными потребностями Подготовила материал :  Бейнеролик тамашалап, талдау қажет

Бейнеролик тамашалап, талдау қажет Международные конфликты: причины и сущность

Международные конфликты: причины и сущность Расширение ассортимента свежемороженной рыбной продукции

Расширение ассортимента свежемороженной рыбной продукции Отчет о выполнении работ по благоустройству общественной территории. Вельский район деревня Никифорово , дом 47

Отчет о выполнении работ по благоустройству общественной территории. Вельский район деревня Никифорово , дом 47 Хімічна промисловість в Україні

Хімічна промисловість в Україні Эквивалентность норм в конечномерных пространствах

Эквивалентность норм в конечномерных пространствах Современные методы обработки статистических данных в области спорта. Корреляция

Современные методы обработки статистических данных в области спорта. Корреляция Социолингвистика в США

Социолингвистика в США Новый год по-соседски

Новый год по-соседски Алгоритмы и структуры данных. Сортировка обменом Pump. Тема 5

Алгоритмы и структуры данных. Сортировка обменом Pump. Тема 5 Пермское РО Союза садоводов России. Дом садовода – опора семьи

Пермское РО Союза садоводов России. Дом садовода – опора семьи Рыночная экономика Цель – изучить понятия деньги, функции денег, виды денег, денежная масса, разделение труда, специализация, основы рыночной экономики, спрос, предложение для: • освоения системы знаний об экономической деятельности и об экономик

Рыночная экономика Цель – изучить понятия деньги, функции денег, виды денег, денежная масса, разделение труда, специализация, основы рыночной экономики, спрос, предложение для: • освоения системы знаний об экономической деятельности и об экономик Основы коммуникативной компетентности педагогов Бурбенцова О.В. учитель английского языка МБОУ Видновская СОШ №1 Ленинского р

Основы коммуникативной компетентности педагогов Бурбенцова О.В. учитель английского языка МБОУ Видновская СОШ №1 Ленинского р Повний факторний експеримент Виконала: студентка групи СНм-51 Гуменюк Ірина

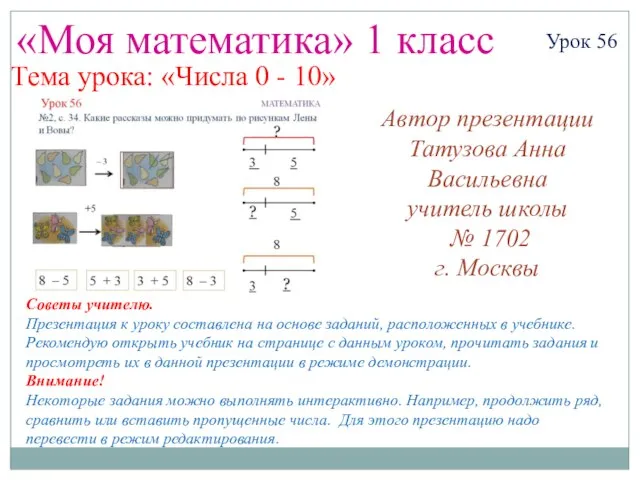

Повний факторний експеримент Виконала: студентка групи СНм-51 Гуменюк Ірина Автор презентации Татузова Анна Васильевна учитель школы 1702 г. Москвы «Моя математика» 1 класс Урок 56 Тема урока: «Числа 0 - 10» Совет

Автор презентации Татузова Анна Васильевна учитель школы 1702 г. Москвы «Моя математика» 1 класс Урок 56 Тема урока: «Числа 0 - 10» Совет Трудовые права несовершеннолетних по российскому законодательству

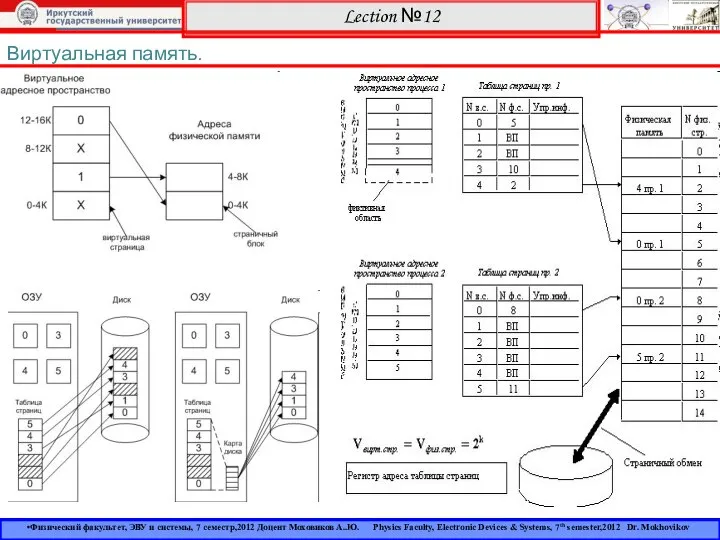

Трудовые права несовершеннолетних по российскому законодательству Виртуальная память

Виртуальная память Обратная связь как регулятор эффективности подчинённых

Обратная связь как регулятор эффективности подчинённых Денежные потоки

Денежные потоки Масленица. Пятница

Масленица. Пятница Презентация Понятие методологии ценообразования

Презентация Понятие методологии ценообразования  . Электрические цепи переменного тока

. Электрические цепи переменного тока ҚР неке және отбасы құқығын қорғау дәрежесі

ҚР неке және отбасы құқығын қорғау дәрежесі Тренинг «Базовые Навыки Руководителя» О чем это?

Тренинг «Базовые Навыки Руководителя» О чем это?  Дымковская игрушка

Дымковская игрушка