Содержание

- 2. Общая структура описания проекта системы Система предназначена для выполнения заданных преобразований, для чего она должна: -

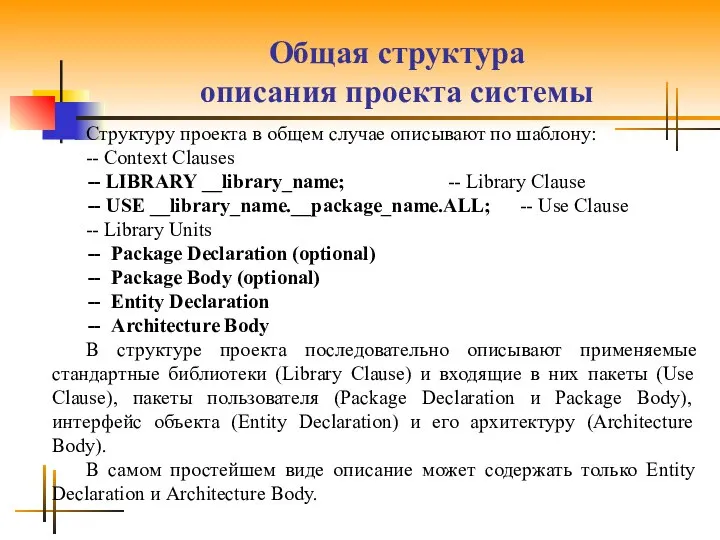

- 3. Общая структура описания проекта системы Структуру проекта в общем случае описывают по шаблону: -- Context Clauses

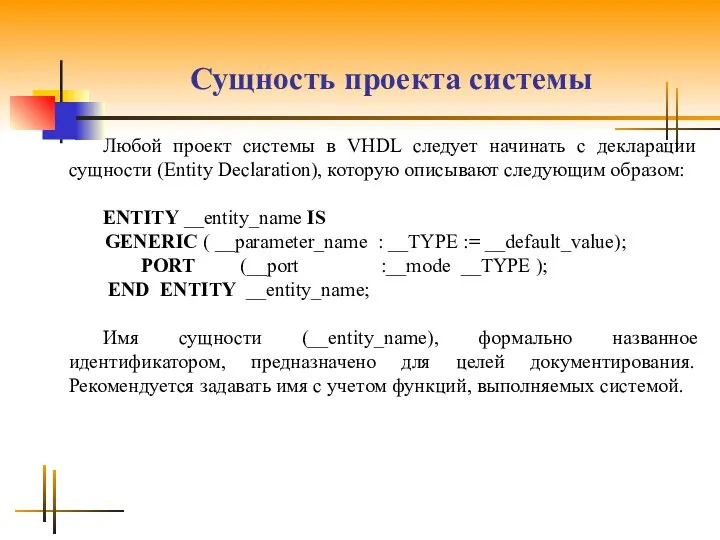

- 4. Сущность проекта системы Любой проект системы в VHDL следует начинать с декларации сущности (Entity Declaration), которую

- 5. Сущность проекта системы Сущность обеспечивает спецификацию интерфейса системы и обычно включает в себя два элемента: -

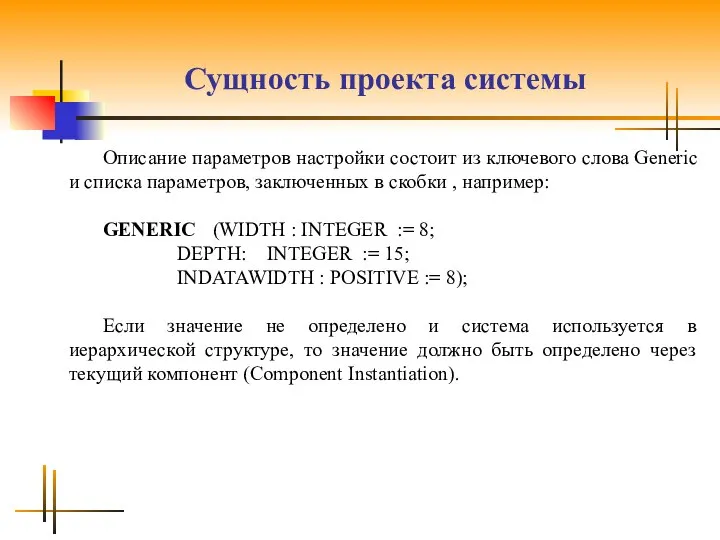

- 6. Сущность проекта системы Описание параметров настройки состоит из ключевого слова Generic и списка параметров, заключенных в

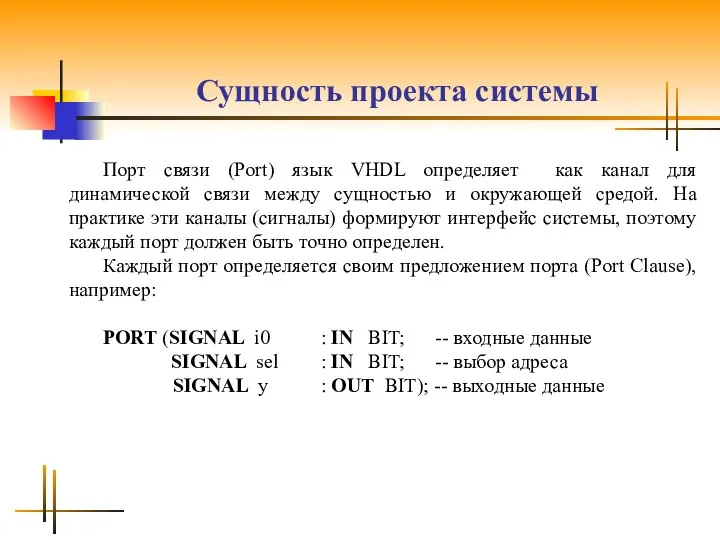

- 7. Сущность проекта системы Порт связи (Port) язык VHDL определяет как канал для динамической связи между сущностью

- 8. Сущность проекта системы Port Clause состоит из следующих элементов: - ключевое слово Signal (необязательно); -имя порта;

- 9. Режимы порта Имеется пять доступных режимов: In, Out, Inout, Buffer, Linkage. Режим In - интерфейсный объект

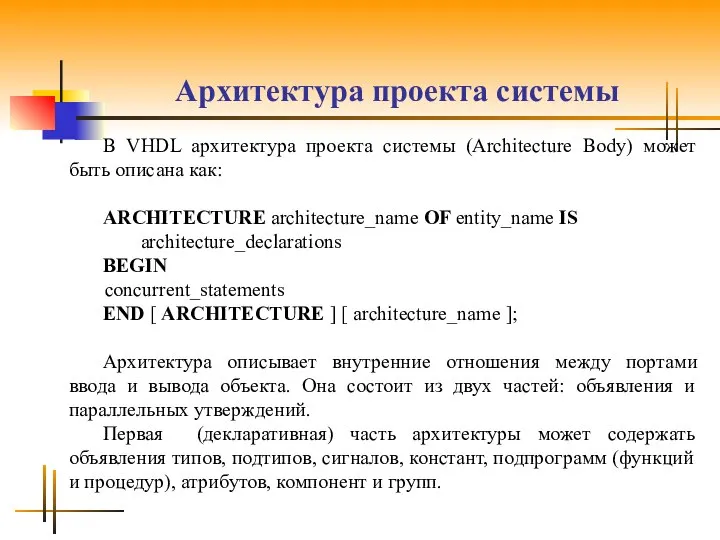

- 10. Архитектура проекта системы В VHDL архитектура проекта системы (Architecture Body) может быть описана как: ARCHITECTURE architecture_name

- 11. Архитектура проекта системы Параллельные утверждения в теле архитектуры определяют отношения (связи) между входами и выходами. Эти

- 12. Предложения VHDL Рассмотрим рекомендуемую структуру проекта с учетом применяемых основных параллельных и последовательных предложений и места

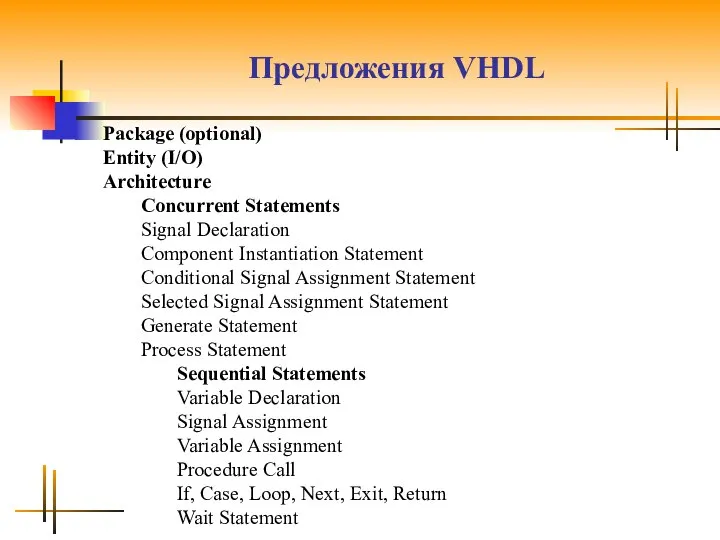

- 13. Предложения VHDL Package (optional) Entity (I/O) Architecture Concurrent Statements Signal Declaration Component Instantiation Statement Conditional Signal

- 14. Предопределенные атрибуты В языке VHDL на некоторые характеристики объектов могут быть даны ссылки в выражениях в

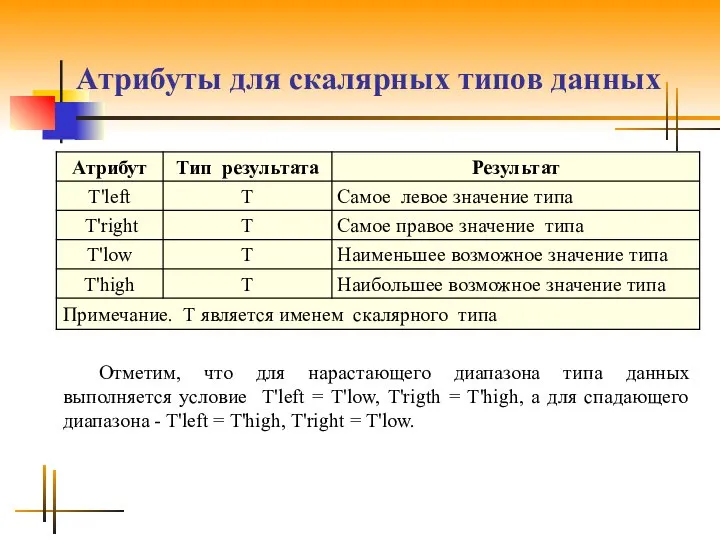

- 15. Атрибуты для скалярных типов данных Отметим, что для нарастающего диапазона типа данных выполняется условие Т'left =

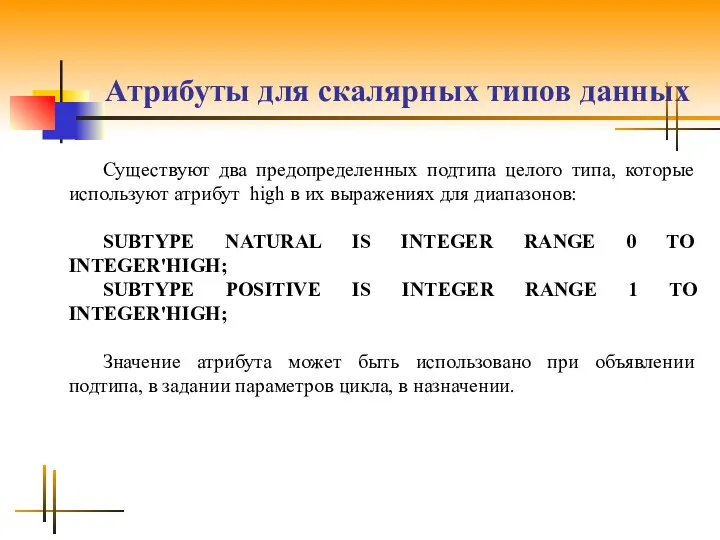

- 16. Атрибуты для скалярных типов данных Существуют два предопределенных подтипа целого типа, которые используют атрибут high в

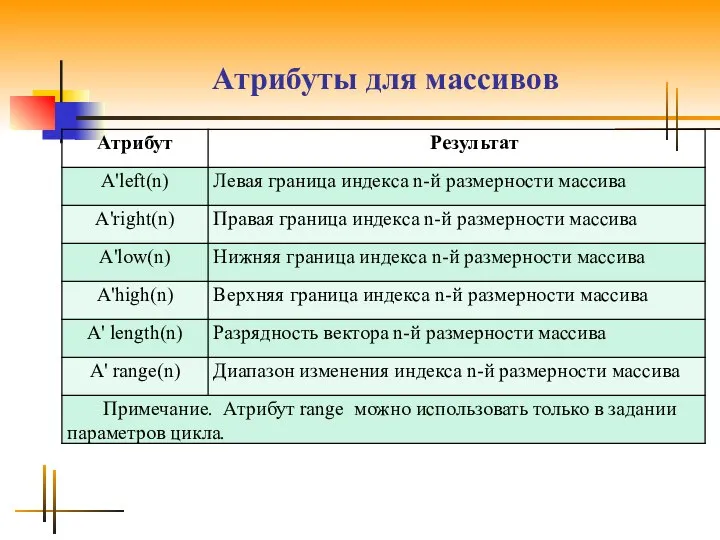

- 17. Атрибуты для массивов

- 19. Скачать презентацию

Инфраструктура рынка. Рынок труда. Интегрированный урок обществознания и информационных технологий 9 класс

Инфраструктура рынка. Рынок труда. Интегрированный урок обществознания и информационных технологий 9 класс  Презентация Создание оберегов из природных материалов урок технологии 3 класс

Презентация Создание оберегов из природных материалов урок технологии 3 класс Таймшер. (Лекция 4.3)

Таймшер. (Лекция 4.3) Открытка – «открытое письмо с картинкой». Основные преимущества электронной открытки

Открытка – «открытое письмо с картинкой». Основные преимущества электронной открытки Выдающиеся выпускники КемГУ

Выдающиеся выпускники КемГУ ERP-терапия в условиях финансового кризиса

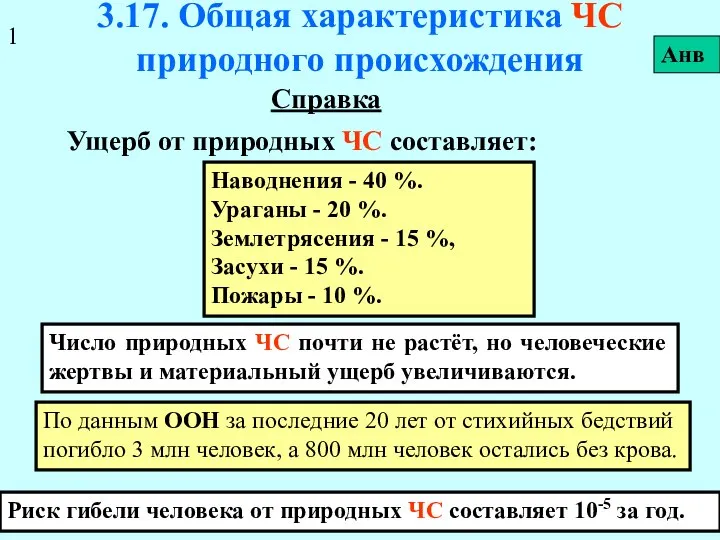

ERP-терапия в условиях финансового кризиса Общая характеристика ЧС природного происхождения

Общая характеристика ЧС природного происхождения Социальные, психологические, экономические и политические предпосылки трансформации предпринимательского потенциала населе

Социальные, психологические, экономические и политические предпосылки трансформации предпринимательского потенциала населе Презентация "Святой Георгий Победоносец" - скачать презентации по МХК

Презентация "Святой Георгий Победоносец" - скачать презентации по МХК Była sobie wyspa

Była sobie wyspa Развитие политического знания в Новое время. Политология как самостоятельная дисциплина

Развитие политического знания в Новое время. Политология как самостоятельная дисциплина Техническое обеспечение информационных технологий. (Лекция 3)

Техническое обеспечение информационных технологий. (Лекция 3) Берёзовоё царство- хорошее лекарство Автор проекта : обучающийся 2 класса Клишин Владислав МОУ «Старосеславинская средняя общ

Берёзовоё царство- хорошее лекарство Автор проекта : обучающийся 2 класса Клишин Владислав МОУ «Старосеславинская средняя общ Абсолютные величины и их значения

Абсолютные величины и их значения Введение в менеджмент

Введение в менеджмент кухня

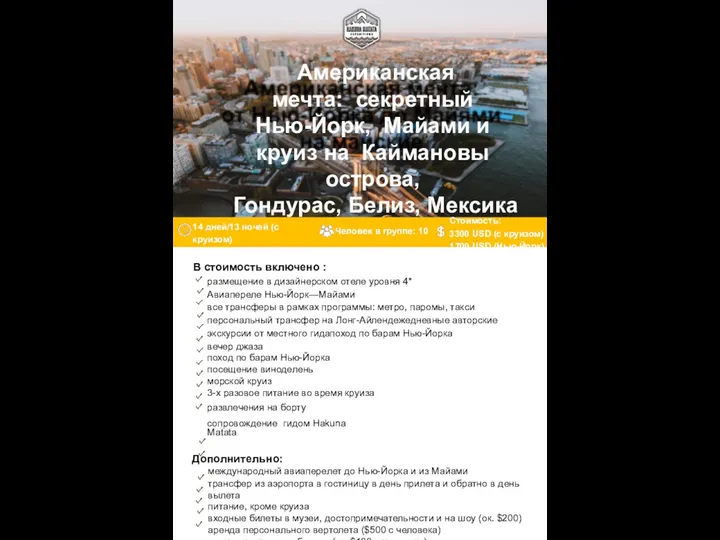

кухня Американская мечта: секретный Нью-Йорк, Майами и круиз на Каймановы острова, Гондурас, Белиз, Мексика

Американская мечта: секретный Нью-Йорк, Майами и круиз на Каймановы острова, Гондурас, Белиз, Мексика Устное народное творчество. Русские народные загадки

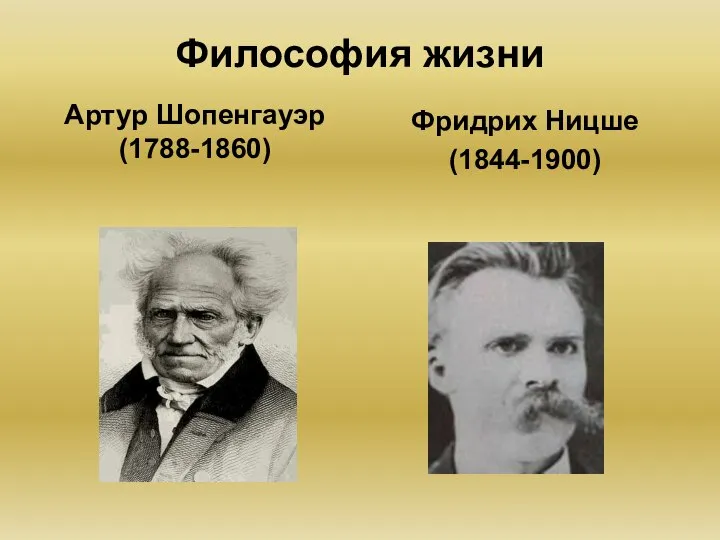

Устное народное творчество. Русские народные загадки Философия жизни

Философия жизни Федерализм

Федерализм Формирование системы государственного управления в россии в современный период Выполнили студенты 1 курса ФТД группы Т-116

Формирование системы государственного управления в россии в современный период Выполнили студенты 1 курса ФТД группы Т-116  Процесс обучения сетевого и системного администратора

Процесс обучения сетевого и системного администратора Режим дня в жизни первоклассника - презентация для начальной школы

Режим дня в жизни первоклассника - презентация для начальной школы Физиология терморегуляции

Физиология терморегуляции Татарское землячество РУДН

Татарское землячество РУДН Оборудование учебного класса робототехникой

Оборудование учебного класса робототехникой Культура и образование в древнем Риме

Культура и образование в древнем Риме Аттестационная работа. Организация этнографической экспедиции школьников по изучению темы «Народная художественная культуры»

Аттестационная работа. Организация этнографической экспедиции школьников по изучению темы «Народная художественная культуры»