Содержание

- 2. Организации занимающиеся стандартизацией в САПР СТАНДАРТИ-ЗАЦИЯ ПОСАДОЧНЫХ МЕСТ

- 3. Стандарт IPC 7351 Определяет размеры контактных площадок для стандартных типов корпусов чип-резисторов, чип-кондекнсаторов, диодов, транзисторов, индуктивностей

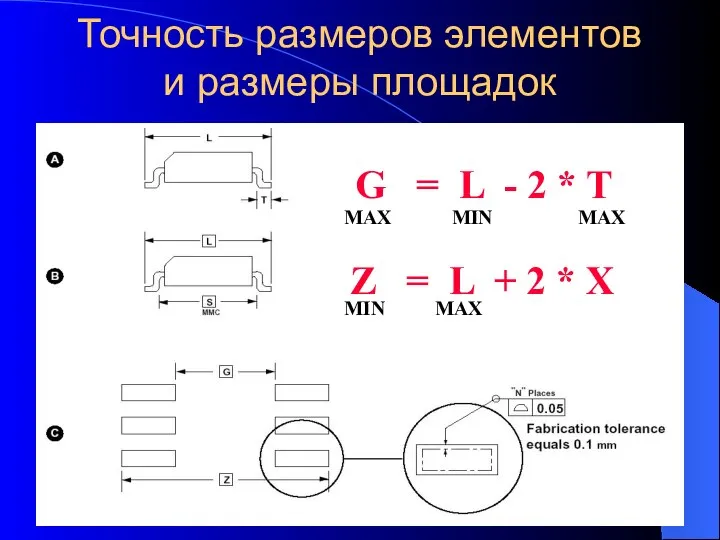

- 4. Точность размеров элементов и размеры площадок G = L - 2 * T MAX MIN MAX

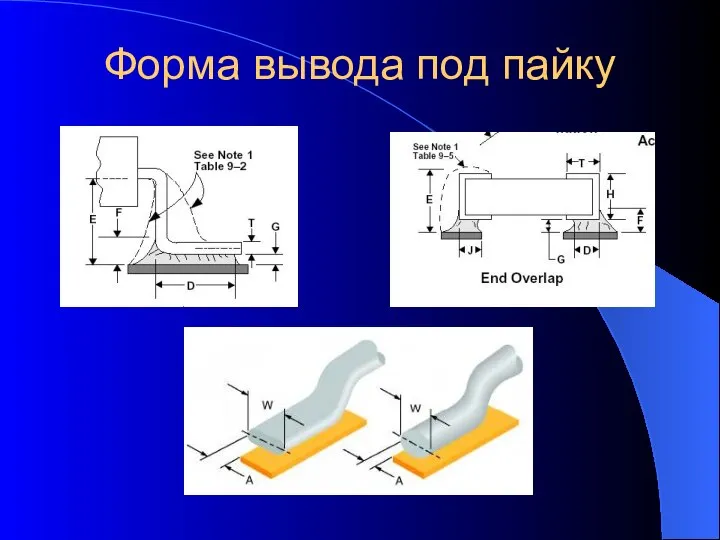

- 5. Форма вывода под пайку

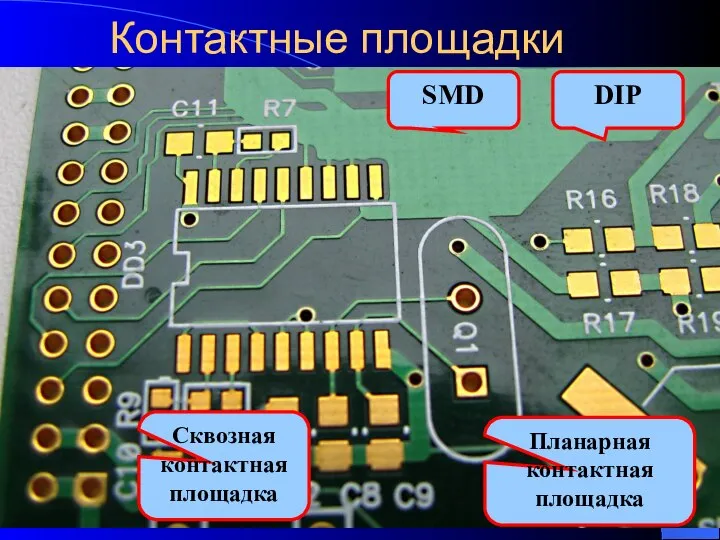

- 6. Контактные площадки SMD DIP Планарная контактная площадка Сквозная контактная площадка

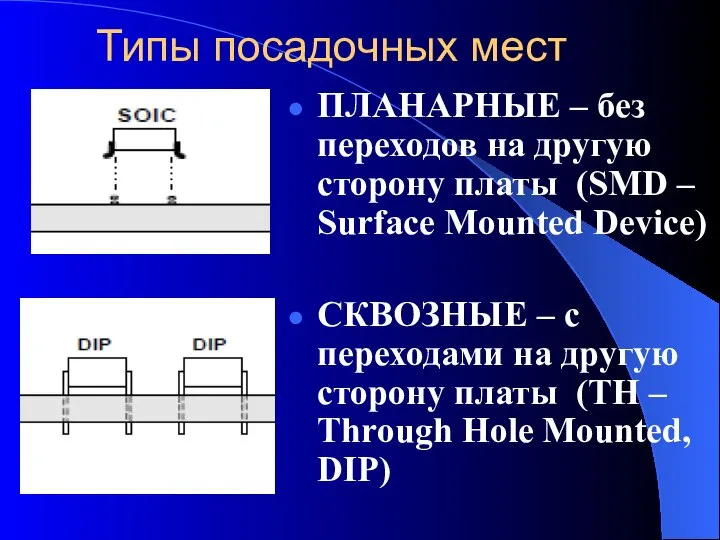

- 7. Типы посадочных мест ПЛАНАРНЫЕ – без переходов на другую сторону платы (SMD – Surface Mounted Device)

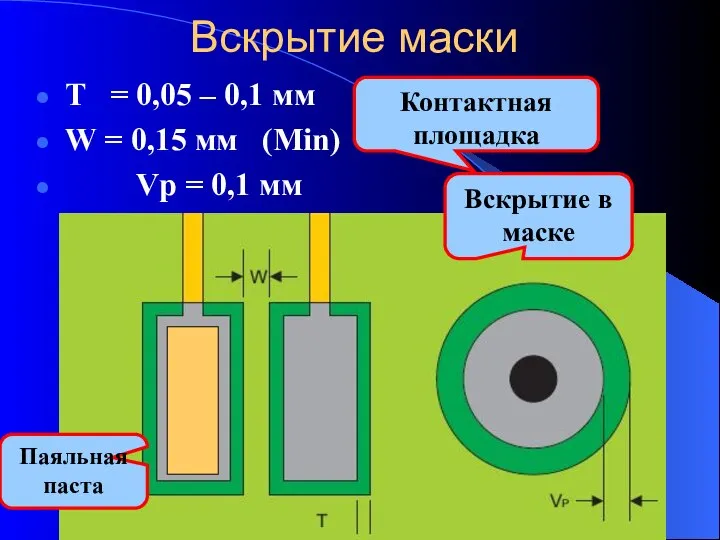

- 8. Вскрытие маски Т = 0,05 – 0,1 мм W = 0,15 мм (Min) Vp = 0,1

- 9. Чип резисторы 0402 ? 0,04” x 0,02” 1” = 25, 4 mm

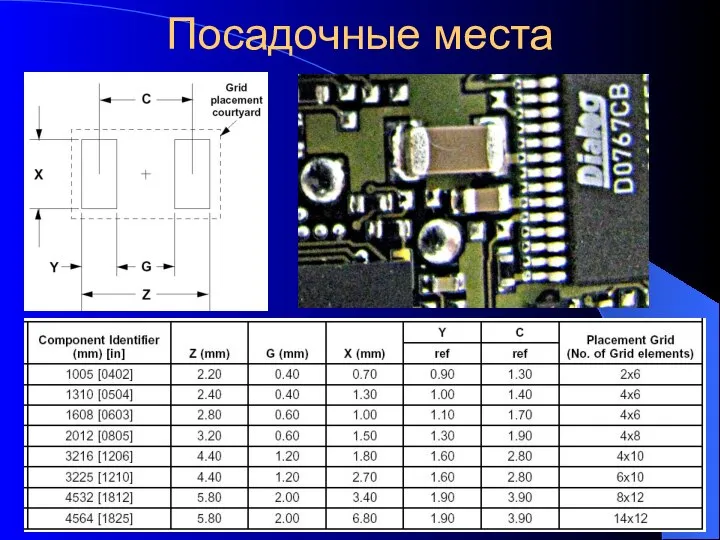

- 10. Посадочные места

- 11. Чип-Конденсаторы

- 12. Посадочные места

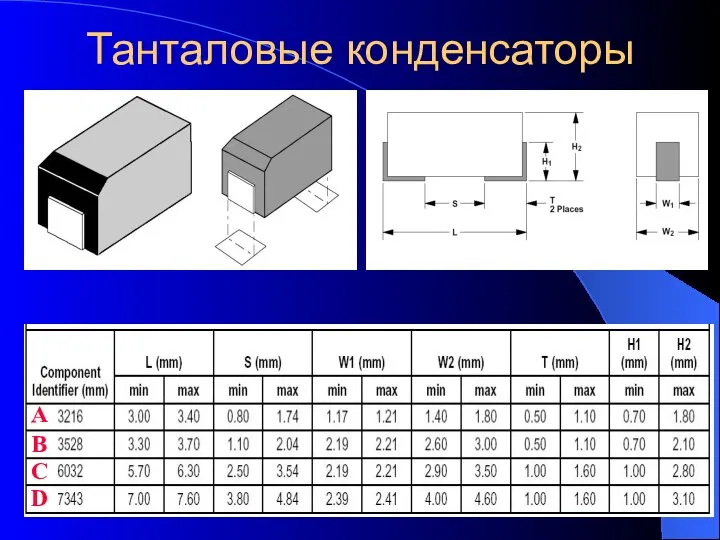

- 13. Танталовые конденсаторы A B C D

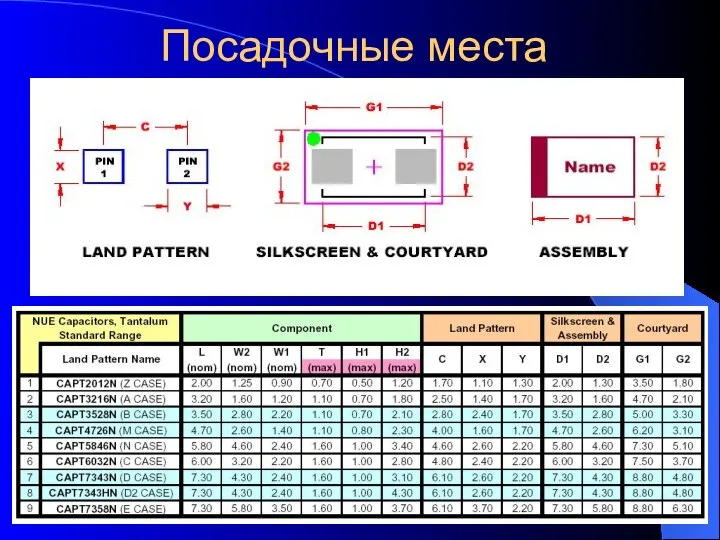

- 14. Посадочные места

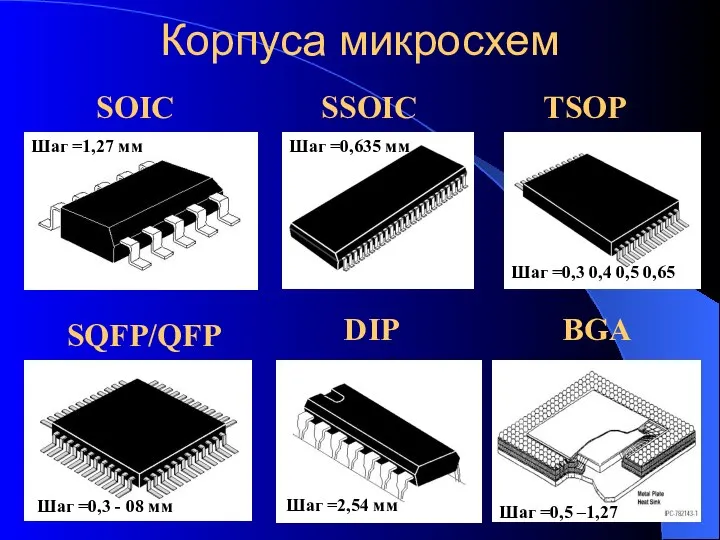

- 15. Корпуса микросхем SOIC TSOP SSOIC Шаг =1,27 мм Шаг =0,635 мм Шаг =0,3 0,4 0,5 0,65

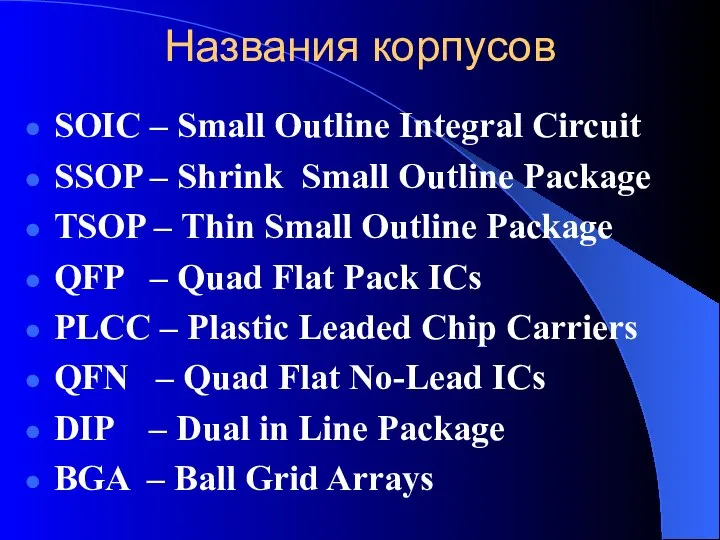

- 16. Названия корпусов SOIC – Small Outline Integral Circuit SSOP – Shrink Small Outline Package TSOP –

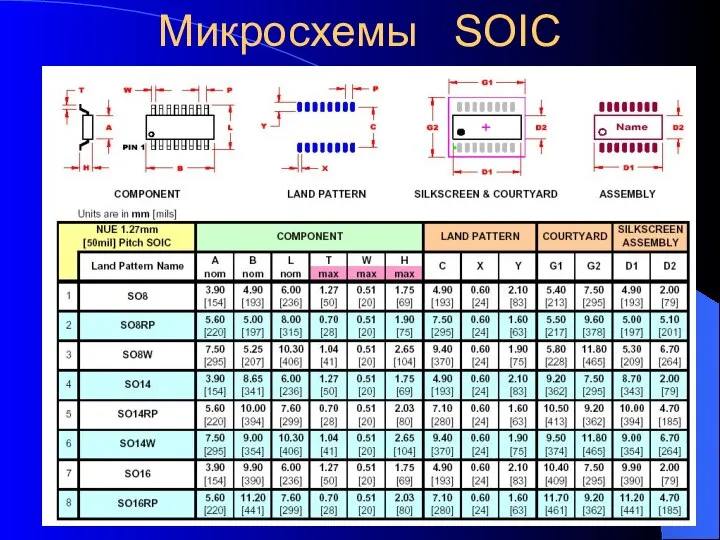

- 17. Микросхемы SOIC

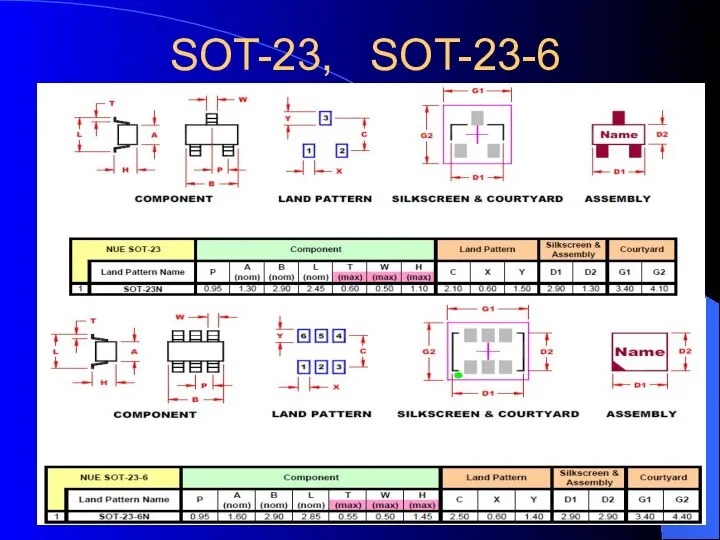

- 18. SOT-23, SOT-23-6

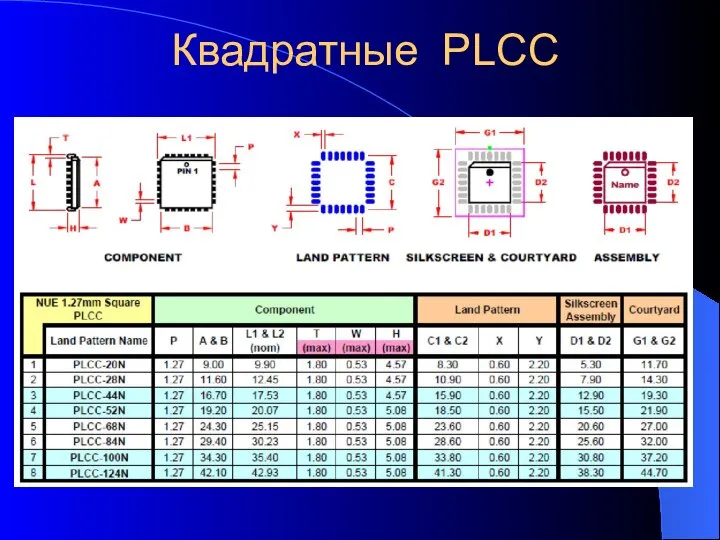

- 19. Квадратные PLCC

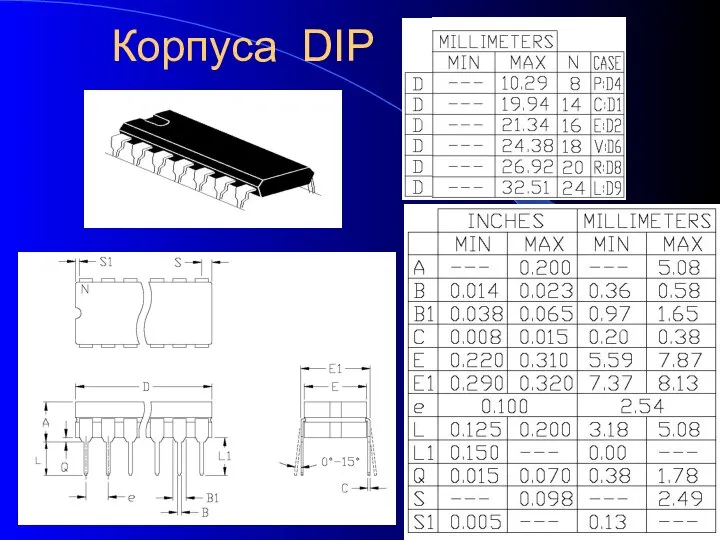

- 20. Корпуса DIP

- 21. Посадочное место стандартный (узкий) DIP Слой Top Assy Остальные слои Шелкография линия 0,25мм

- 22. Plastic Ball Grid Array (PBGA) 357 выводов (19х19)

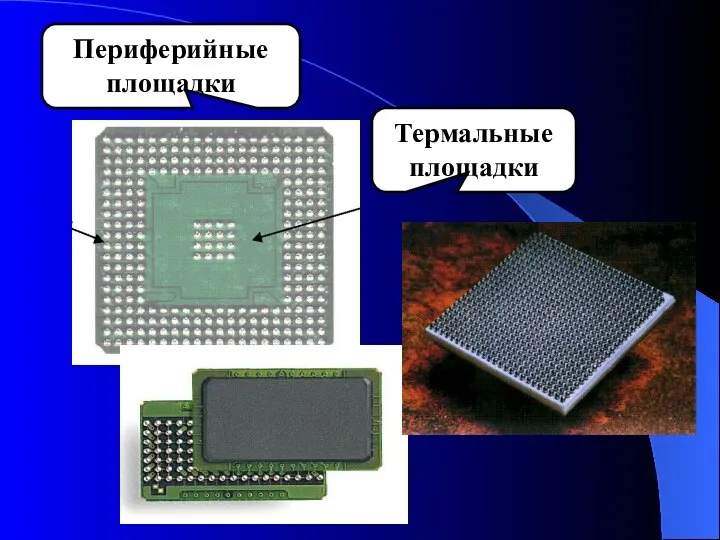

- 23. Термальные площадки Периферийные площадки

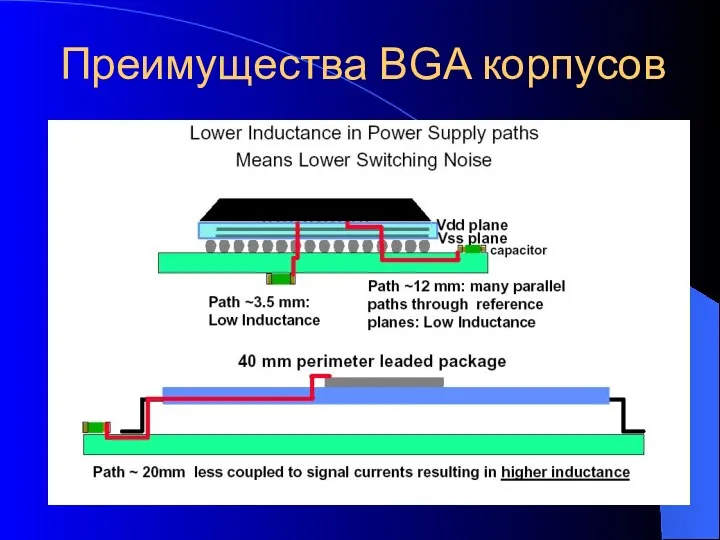

- 24. Преимущества BGA корпусов

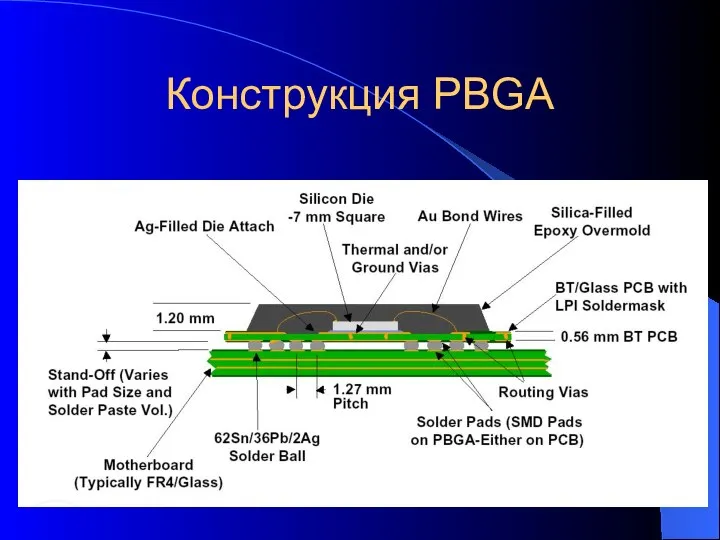

- 25. Конструкция PBGA

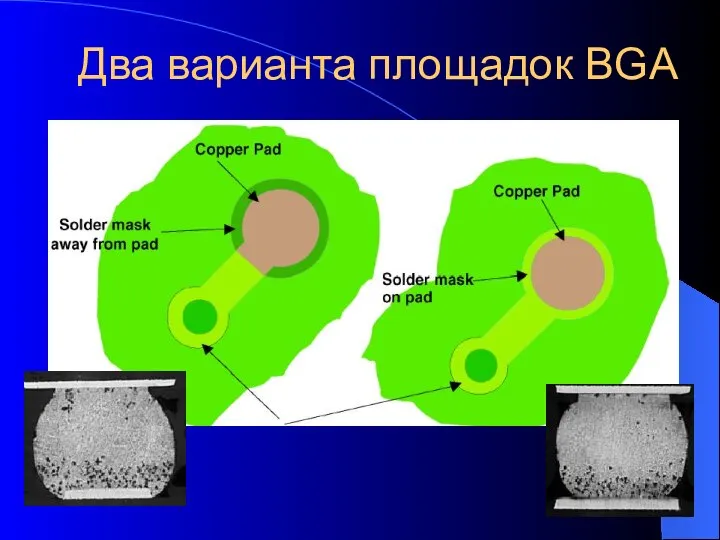

- 26. Два варианта площадок BGA

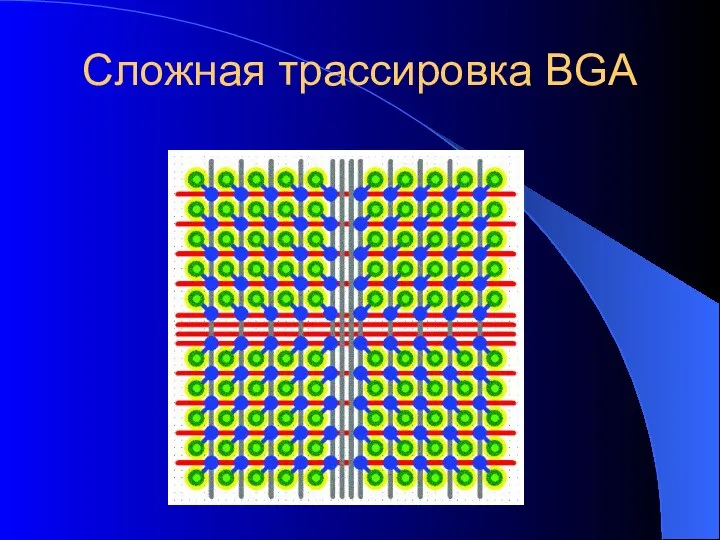

- 27. Сложная трассировка BGA

- 28. Конструктивные особенности Сложная форма вывода или площадки Слияние выводов на топологии 1 2 3 4

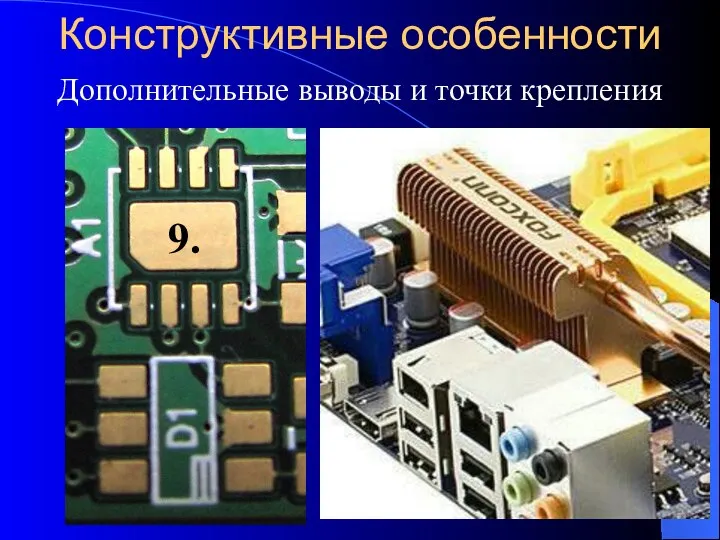

- 29. Дополнительные выводы и точки крепления Конструктивные особенности 9.

- 30. Пропущенные выводы Конструктивные особенности 1 2 3 4 5 Pin Num 1 2 4 5 6

- 31. CPLD, FPGA FPGA - field-programmable gate array (ПЛМ – программируемая логическая матрица) CPLD -complex programmable logic

- 32. Архитектура ПЛИС Virtex

- 33. BGA Корпус 1148 выводов БАНК 1 БАНК 2 БАНК 3 БАНК 4 БАНК 5 БАНК 6

- 35. Скачать презентацию

Классный час: «Дети в ...Интернете»

Классный час: «Дети в ...Интернете» Презентация "Автоматизированная банковская система" - скачать презентации по Экономике

Презентация "Автоматизированная банковская система" - скачать презентации по Экономике Современный взгляд на традиционную деятельность Комиссии по делам несовершеннолетних и защите их прав

Современный взгляд на традиционную деятельность Комиссии по делам несовершеннолетних и защите их прав Международный день борьбы с коррупцией

Международный день борьбы с коррупцией Современные культурологические теории (часть 2)

Современные культурологические теории (часть 2) Обществознание. Довузовская подготовка (1)

Обществознание. Довузовская подготовка (1) Современный состав Архивного фонда РФ и его классификации

Современный состав Архивного фонда РФ и его классификации Цитокины. Обзор.

Цитокины. Обзор. Маннергейм Карл Густав Эмиль

Маннергейм Карл Густав Эмиль Свойства выборочных харрактеристик

Свойства выборочных харрактеристик Direct Shift Gearbox. Коробки передач

Direct Shift Gearbox. Коробки передач Topspeed Sponsorship - Гонки на ускорение

Topspeed Sponsorship - Гонки на ускорение Классификация операций ювелирного производства. Основные инструменты и приспособления, используемые в ювелиром производстве

Классификация операций ювелирного производства. Основные инструменты и приспособления, используемые в ювелиром производстве Графическое оформление чертежа

Графическое оформление чертежа Технологические циклы

Технологические циклы Народные промыслы: Золотая хохлома. 3 класс

Народные промыслы: Золотая хохлома. 3 класс Современный терроризм и его особенности

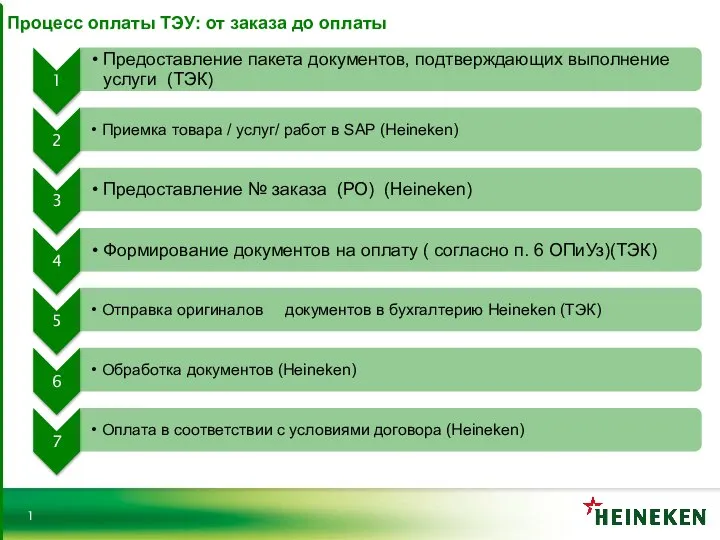

Современный терроризм и его особенности 8_OPL+PtP+for+LSP's_v3_21-09-2017

8_OPL+PtP+for+LSP's_v3_21-09-2017 Математические модели и методы теории систем массового обслуживания, используемые в САПР КЭС. Лекция 4

Математические модели и методы теории систем массового обслуживания, используемые в САПР КЭС. Лекция 4 Деньги. Виды и функции денег

Деньги. Виды и функции денег Графика в Visual Basic. 10 классе

Графика в Visual Basic. 10 классе Роль водного фактора в инфекционной заболеваемости населения

Роль водного фактора в инфекционной заболеваемости населения k_lektsii_1_vvedenie

k_lektsii_1_vvedenie 17 сентября

17 сентября Понятие предприятия и его основные характеристики

Понятие предприятия и его основные характеристики Свобода в деятельности человека

Свобода в деятельности человека компьютерное моделирование человеческих рассуждений

компьютерное моделирование человеческих рассуждений Приложение в программе DELPHI в виде теста

Приложение в программе DELPHI в виде теста