Содержание

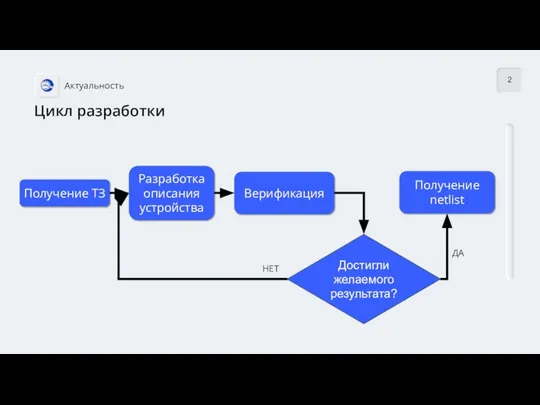

- 2. 2 Актуальность Цикл разработки Получение ТЗ Разработка описания устройства Верификация Получение netlist Достигли желаемого результата? ДА

- 3. 3 Актуальность Цифровое устройство – система из модулей

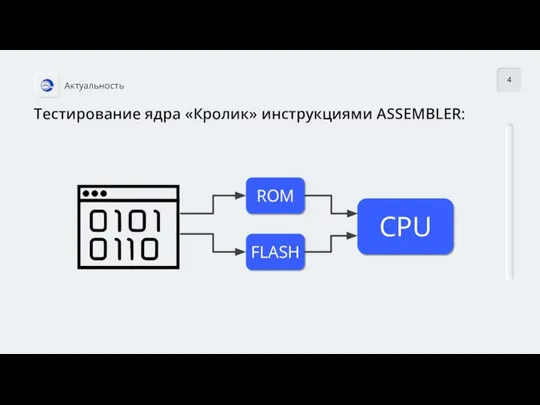

- 4. 4 Актуальность Тестирование ядра «Кролик» инструкциями ASSEMBLER: ROM FLASH CPU

- 5. 5 Актуальность Ядро как система из модулей INT OAB MEMARB MMU Кролик PSW ALU PC COMDEC

- 6. 6 Цель: Верифицировать модули микроконтроллерного ядра «Кролик» Задачи: 1. Разработать архитектуру тестового окружения, позволяющую: - Генерировать

- 7. 7 SEQUENCER DRIVER MONITOR DUT SCOREBOARD SUBSCRIBER AGENT ENV TEST seqi UVM окружение Ход работы

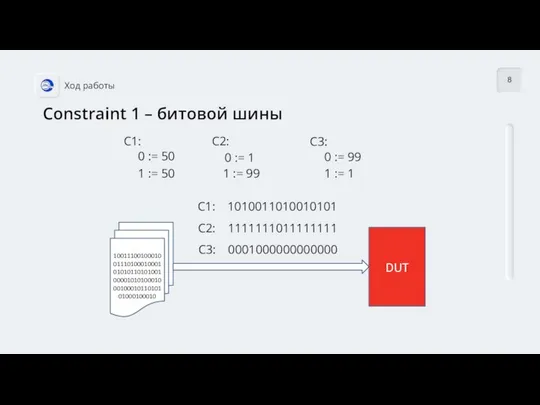

- 8. 8 Constraint 1 – битовой шины 100111001000100111010001000101010110101001000010101000100010001011010101000100010 DUT С1: 1010011010010101 C2: 1111111011111111 C3: 0001000000000000 0 :=

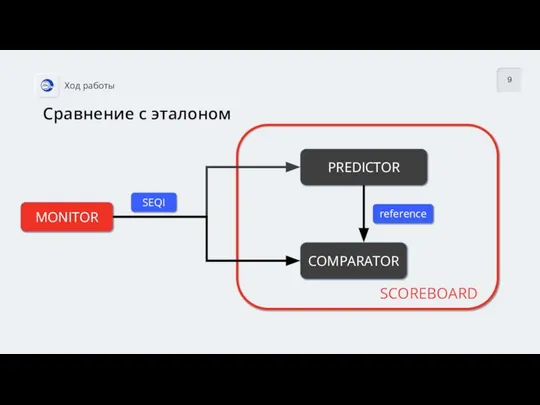

- 9. 9 MONITOR SCOREBOARD COMPARATOR PREDICTOR SEQI reference Сравнение с эталоном Ход работы

- 10. 10 Кодовое покрытие Функциональное покрытие FULL FULL BLOCK STATE BRANCH FSM BIN1 BIN2 0% 100% 0%

- 11. 11 Ход работы covergroup zeros = 00000000 ones = FFFFFFFF others = [00000001 : FFFFFFFE] Функциональное

- 12. Верификация модулей 12

- 13. Верификация модулей 13

- 14. Верификация модулей 14

- 15. Верификация модулей 15

- 16. Верификация модулей 16

- 17. Верификация модулей 17

- 18. Верификация модулей 18

- 19. Верификация модулей 19

- 21. Скачать презентацию

Мультимедиа и области его применения

Мультимедиа и области его применения Информация и знания Маркелова О.В. учитель информатики высшей квалификационной категории, г. Красноярск, МОУ СОШ 150

Информация и знания Маркелова О.В. учитель информатики высшей квалификационной категории, г. Красноярск, МОУ СОШ 150  Обработка информации

Обработка информации Система управления умным домом

Система управления умным домом Алгоритмы и модели трассировки проводных соединений в ЭА

Алгоритмы и модели трассировки проводных соединений в ЭА Слова «НЕ», «И», «ИЛИ» на карте множеств 3-4 классы

Слова «НЕ», «И», «ИЛИ» на карте множеств 3-4 классы  Три пингвина

Три пингвина Ресурсы и управление ими в операционных системах. Тема 5

Ресурсы и управление ими в операционных системах. Тема 5 Устройство ЭВМ

Устройство ЭВМ Создание слайдов с триггерами

Создание слайдов с триггерами Аттестационная работа. Формирование ИКТ-компетентности обучающихся посредством проектной деятельности по химии

Аттестационная работа. Формирование ИКТ-компетентности обучающихся посредством проектной деятельности по химии Основные понятия баз данных

Основные понятия баз данных Современные тенденции развития ИТ в менеджменте

Современные тенденции развития ИТ в менеджменте Ціль сталого розвитку №8. Гідне працевлаштування. Сайт Моя кар’єра

Ціль сталого розвитку №8. Гідне працевлаштування. Сайт Моя кар’єра Аттестационная работа. Элективный курс по информатике Исследование информационных моделей

Аттестационная работа. Элективный курс по информатике Исследование информационных моделей Виды информации

Виды информации Библиографические ресурсы: история и современное состояние. Российские библиографические стандарты

Библиографические ресурсы: история и современное состояние. Российские библиографические стандарты Презентация "MSC.Dytran - 13" - скачать презентации по Информатике

Презентация "MSC.Dytran - 13" - скачать презентации по Информатике Информационная безопасность. Методы защиты информации

Информационная безопасность. Методы защиты информации Персональный компьютер

Персональный компьютер Цели и направления внедрения средств ИКТ в образование

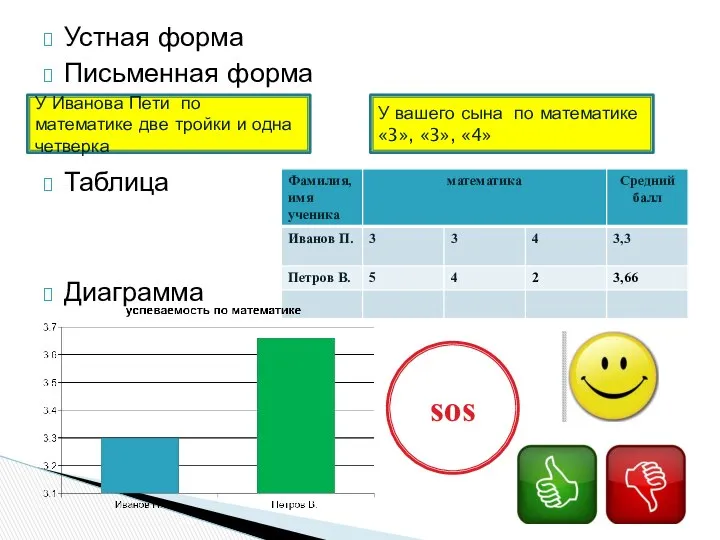

Цели и направления внедрения средств ИКТ в образование Представление информации

Представление информации Tipuri de realități in vizualizarea arhitecturală

Tipuri de realități in vizualizarea arhitecturală Безопасность данных и информационная защита

Безопасность данных и информационная защита DOI Digital Object Identifier

DOI Digital Object Identifier Аттестационная работа. Образовательная программа факультатива. Основы программирования на языке программирования Паскаль

Аттестационная работа. Образовательная программа факультатива. Основы программирования на языке программирования Паскаль Защита от вирусов

Защита от вирусов Форматирование текстового документа Абзацные отступы и интервалы

Форматирование текстового документа Абзацные отступы и интервалы