Содержание

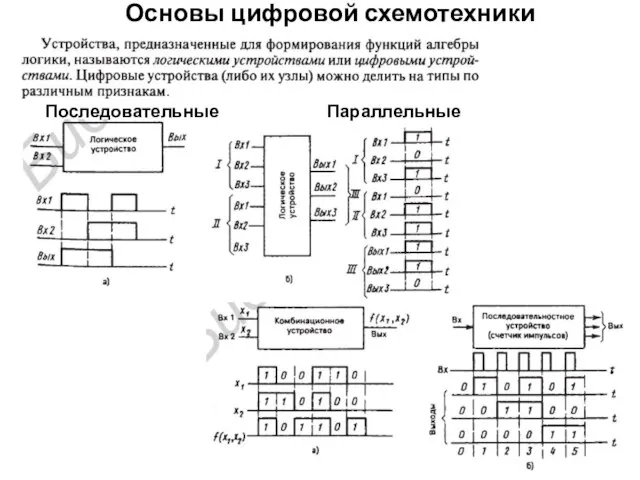

- 2. Основы цифровой схемотехники Последовательные Параллельные

- 3. Логические элементы Синтез КУ в базисе ИЛИ_НЕ и И-НЕ КНФ - формула имеет вид конъюнкции дизъюнкций

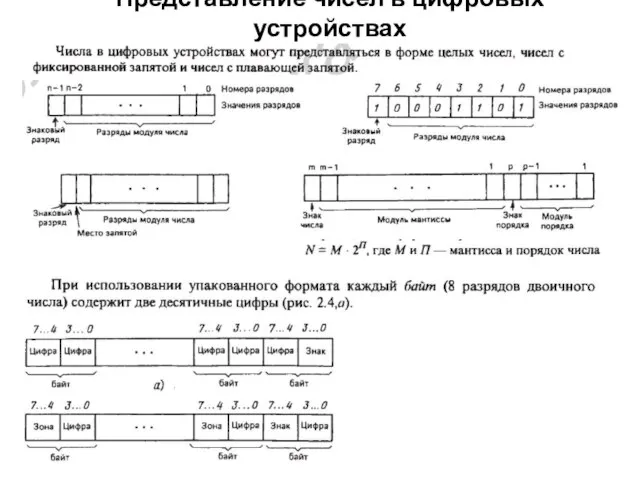

- 4. Представление чисел в цифровых устройствах

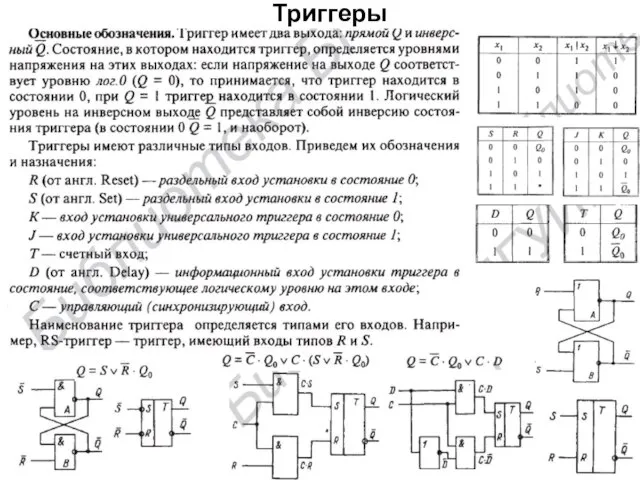

- 5. Триггеры

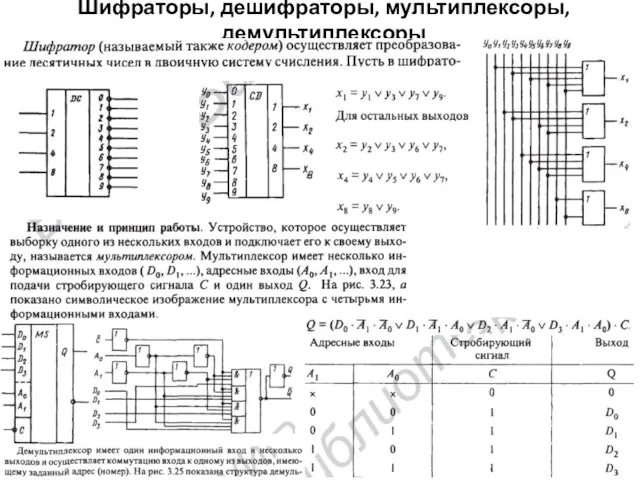

- 6. Шифраторы, дешифраторы, мультиплексоры, демультиплексоры

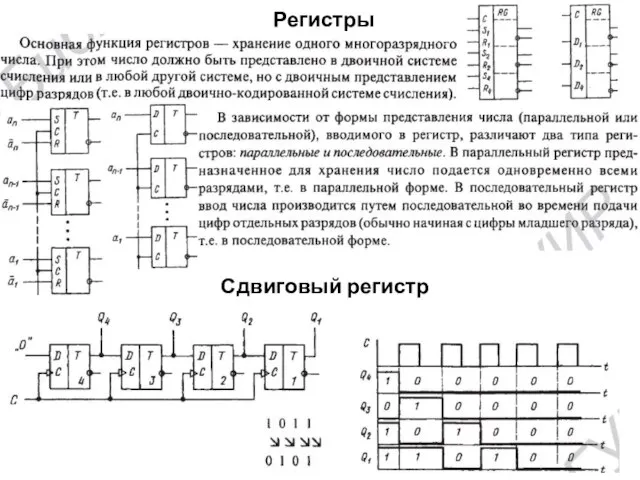

- 7. Регистры Сдвиговый регистр

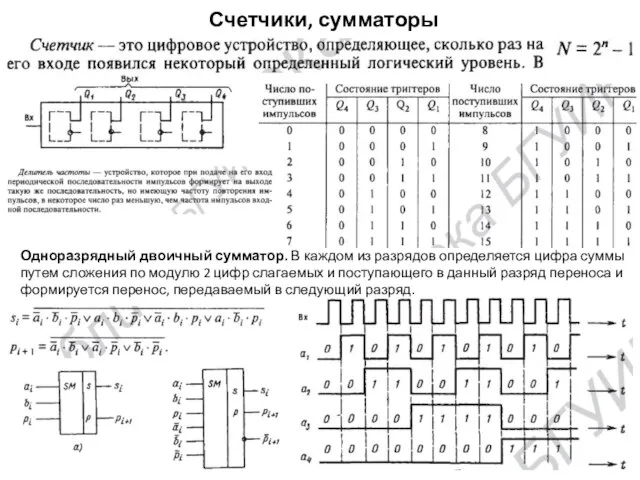

- 8. Счетчики, сумматоры Одноразрядный двоичный сумматор. В каждом из разрядов определяется цифра суммы путем сложения по модулю

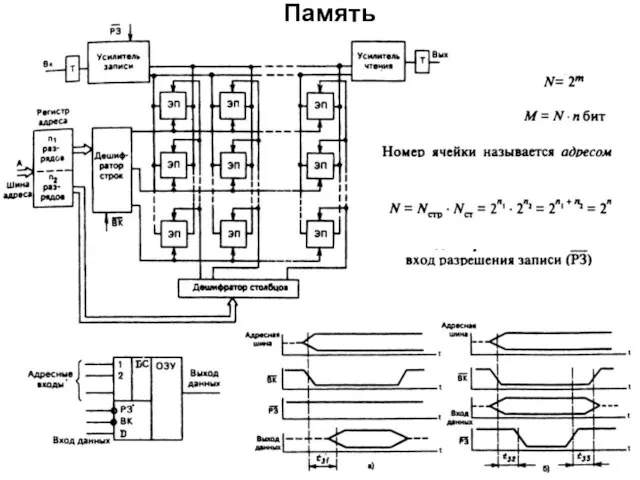

- 9. Память

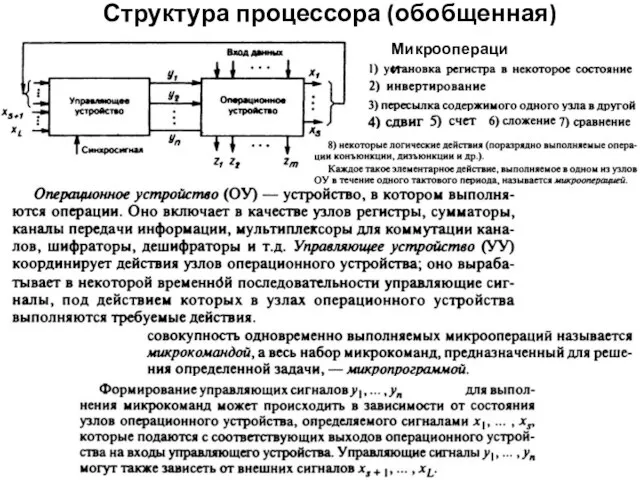

- 10. Структура процессора (обобщенная) Микрооперации

- 11. Структура процессора в составе ЭВМ Команда – вид операции, подлежащей к исполнению в процессоре.

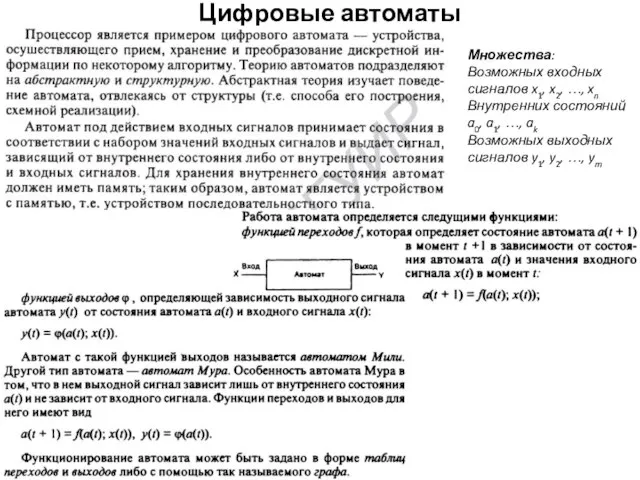

- 12. Цифровые автоматы Множества: Возможных входных сигналов x1, x2, …, xn Внутренних состояний a0, a1, …, ak

- 13. Цифровые автоматы (пример)

- 14. Принцип микропрограммного управления Управляющая память хранит кодовые комбинации микрокоманд и выдает их в ОУ ПА Пример

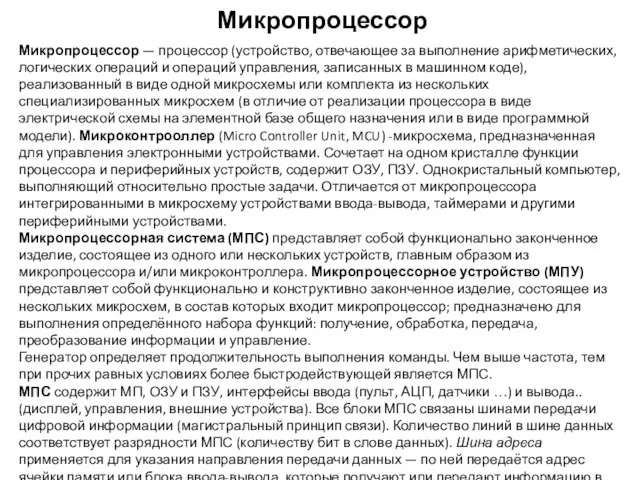

- 15. Микропроцессор Микропроцессор — процессор (устройство, отвечающее за выполнение арифметических, логических операций и операций управления, записанных в

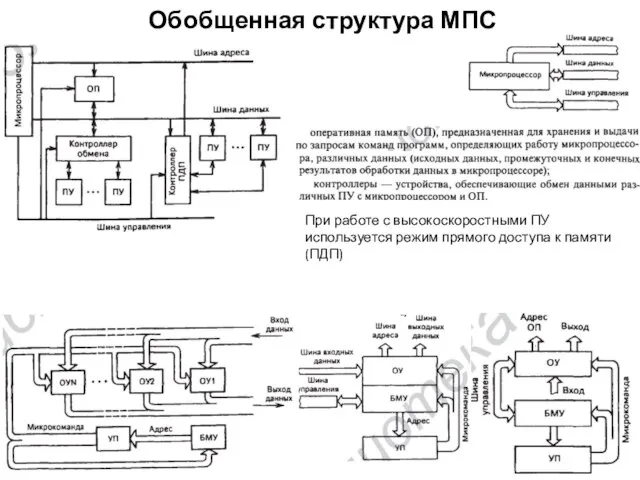

- 16. Обобщенная структура МПС При работе с высокоскоростными ПУ используется режим прямого доступа к памяти (ПДП)

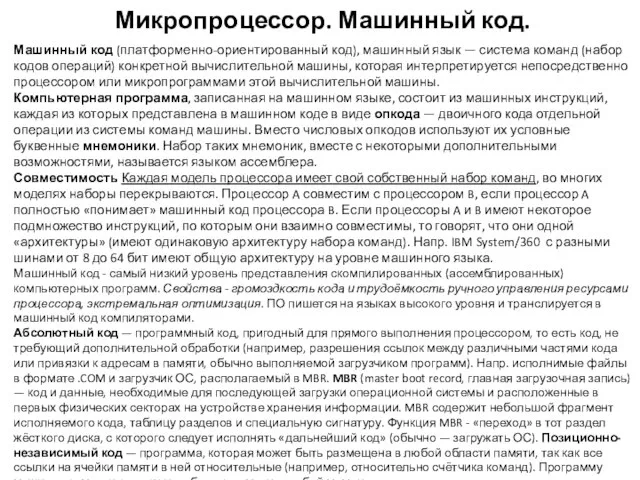

- 17. Микропроцессор. Машинный код. Машинный код (платформенно-ориентированный код), машинный язык — система команд (набор кодов операций) конкретной

- 18. Прерывания процессора Прерывание (interrupt) — сигнал, сообщающий процессору о наступлении какого-либо события, выполнение текущей последовательности команд

- 19. Стек процессора Стек - регистр хранящий информацию для возврата управления из подпрограмм (процедур) в программу и/или

- 20. Архитектура процессора Архитектура процессора — количественная составляющая компонентов микроархитектуры (регистр флагов или регистры процессора), рассматриваемая IT-специалистами

- 21. Архитектуры

- 22. Архитектура Фон Неймана Однородная память микропроцессора. В память могут записываться различные программы. При этом специальная программа-загрузчик

- 23. Гарвардская архитектура Два вида памяти микропроцессора: Память программ (для хранения инструкций микропроцессора); память данных (для временного

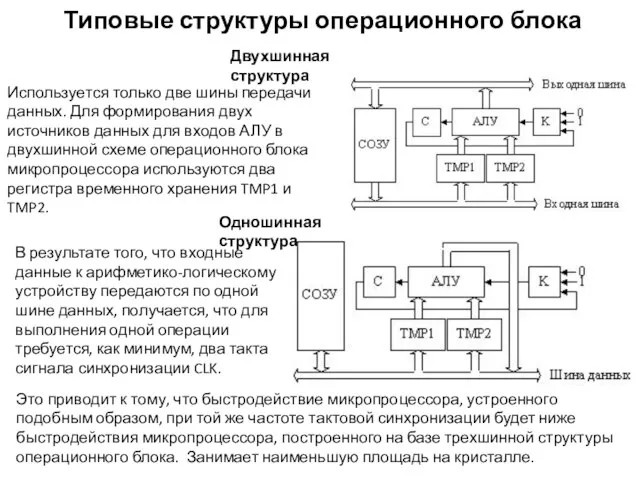

- 24. Типовые структуры операционного блока Двухшинная структура Одношинная структура В результате того, что входные данные к арифметико-логическому

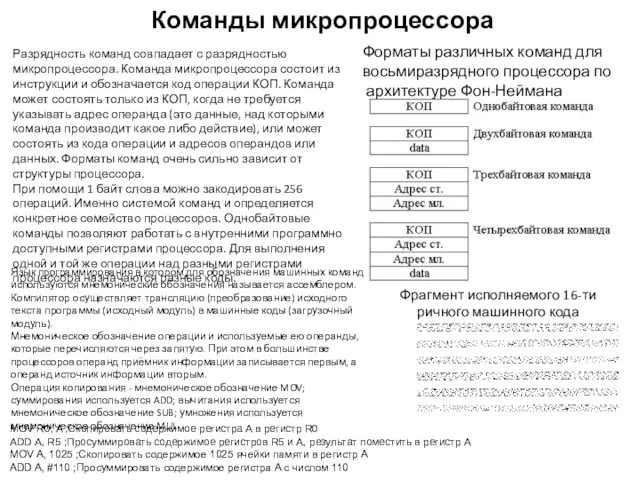

- 25. Команды микропроцессора Разрядность команд совпадает с разрядностью микропроцессора. Команда микропроцессора состоит из инструкции и обозначается код

- 26. 32-разрядная архитектура ARM На RISC-архитектуре, отклонения от принципов RISC: Переменное количество циклов выполнения для простых инструкций.

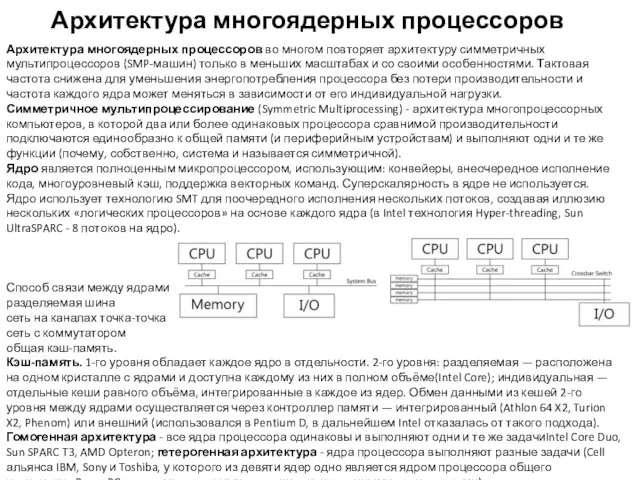

- 27. Архитектура многоядерных процессоров Архитектура многоядерных процессоров во многом повторяет архитектуру симметричных мультипроцессоров (SMP-машин) только в меньших

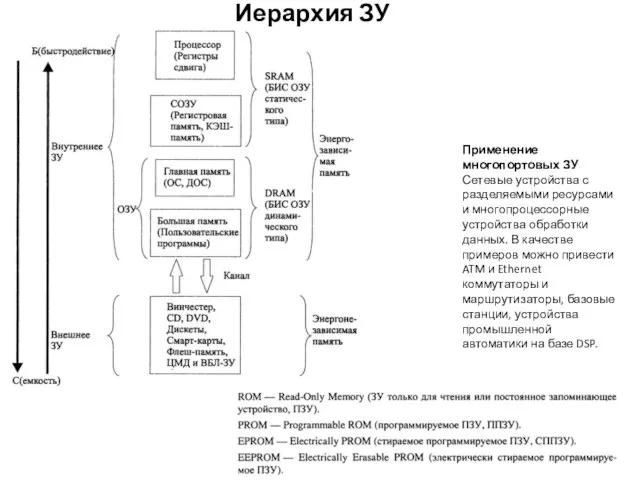

- 28. Иерархия ЗУ Применение многопортовых ЗУ Сетевые устройства с разделяемыми ресурсами и многопроцессорные устройства обработки данных. В

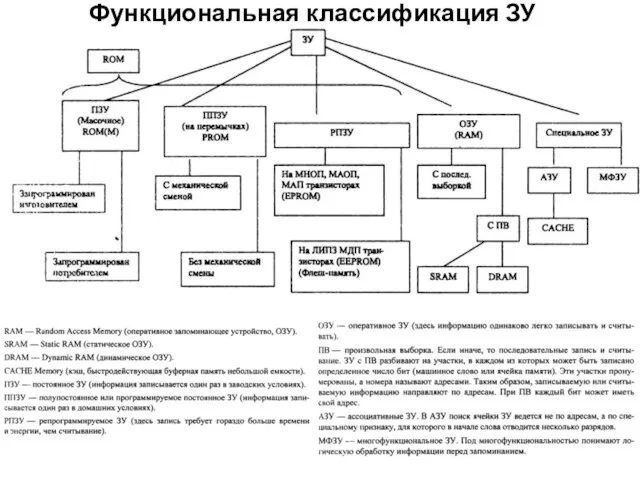

- 29. Функциональная классификация ЗУ

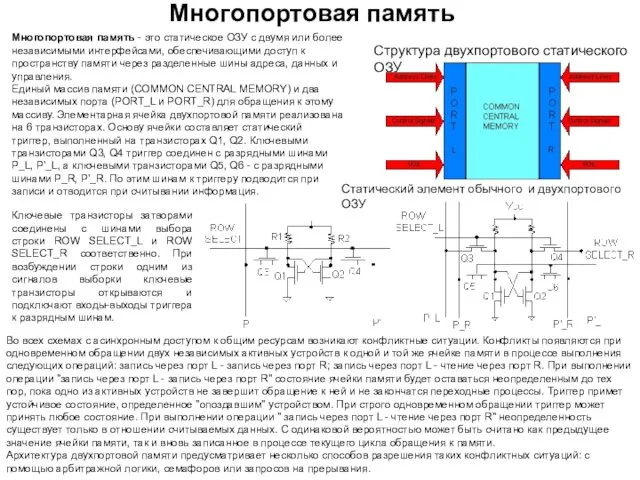

- 30. Многопортовая память Многопортовая память - это статическое ОЗУ с двумя или более независимыми интерфейсами, обеспечивающими доступ

- 31. Принцип работы асинхронного двухпортового ОЗУ BUSY' удерживается все время, пока не закончится операция обращения к памяти.

- 32. Принцип работы асинхронного двухпортового ОЗУ Прерывания. Интерфейс системы прерываний асинхронных двухпортовых ОЗУ содержит буфер сообщений и

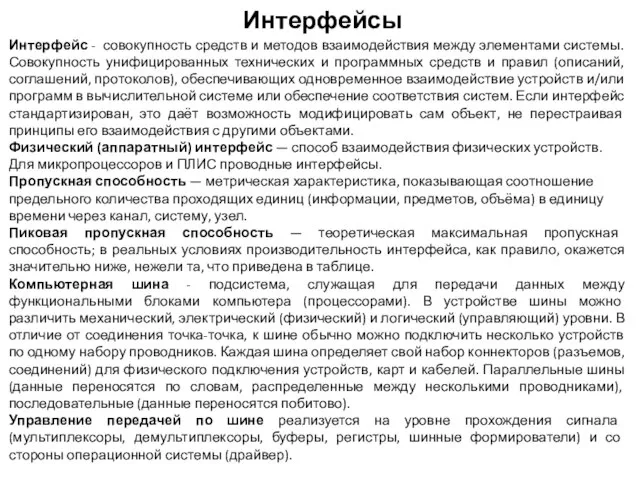

- 33. Интерфейсы Интерфейс - совокупность средств и методов взаимодействия между элементами системы. Совокупность унифицированных технических и программных

- 34. Интерфейсы микропроцессора

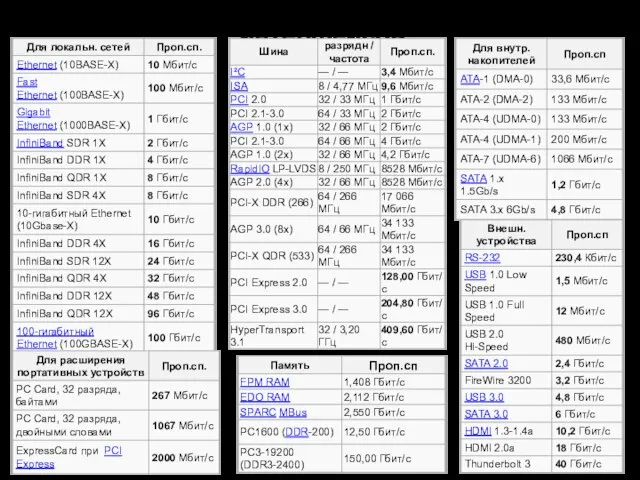

- 35. Пропускные способности проводных интерфейсов

- 36. Интерфейс UART UART (Universal Asynchronous Receiver/Transmitter) - универсальный асинхронный приёмопередатчик, интерфейс для связи цифровых устройств, предназначенный

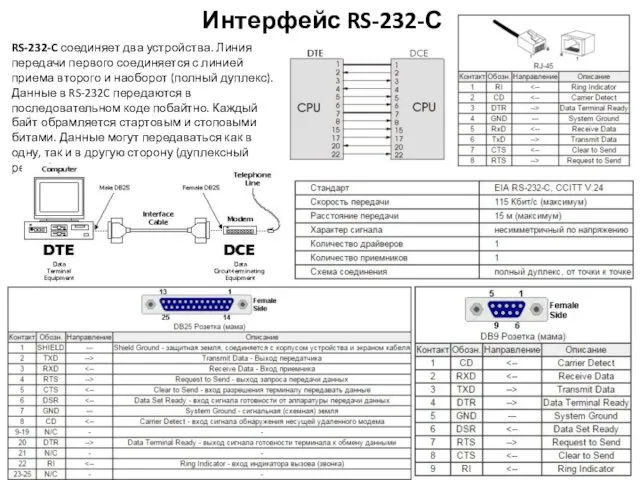

- 37. Интерфейс RS-232-С RS-232-C соединяет два устройства. Линия передачи первого соединяется с линией приема второго и наоборот

- 38. Интерфейс RS-232-С Схема 4-проводной линии связи FG - заземление -TxD - данные, передаваемые компьютером в последовательном

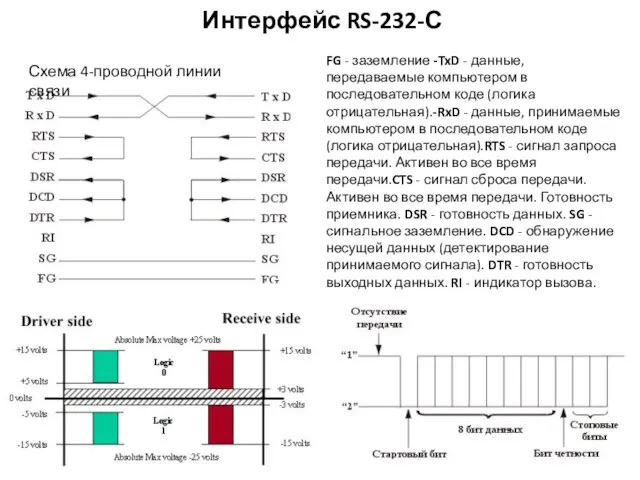

- 39. Интерфейс RS-485 RS-485 — TIA/EIA-485 Electrical Characteristics of Generators and Receivers for Use in Balanced Digital

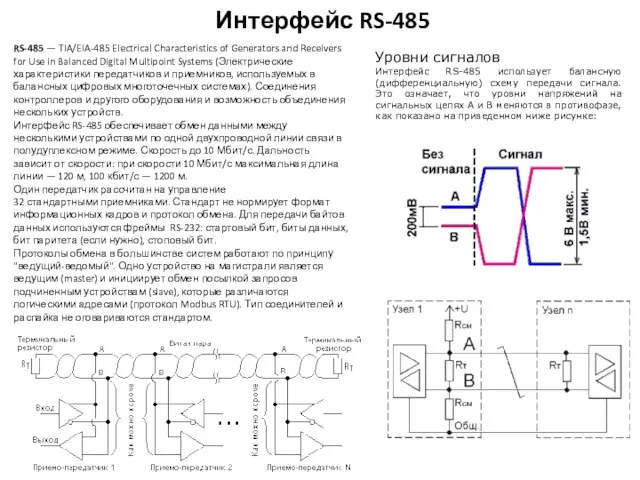

- 40. Дифференциальная передача сигналов

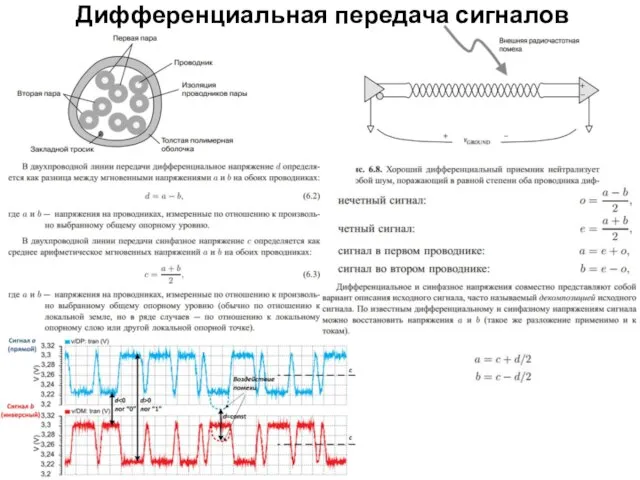

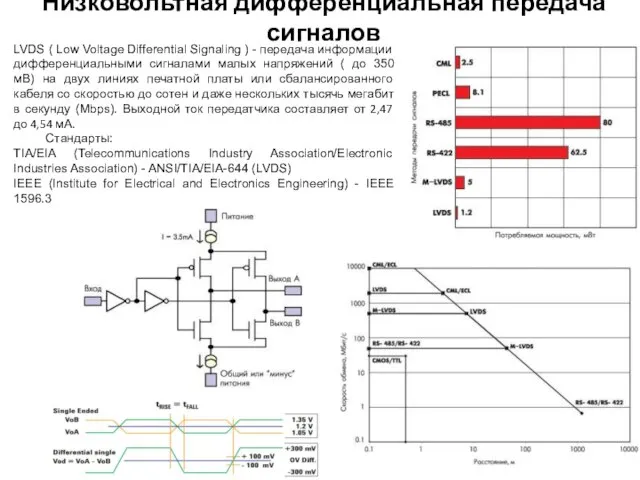

- 41. LVDS ( Low Voltage Differential Signaling ) - передача информации дифференциальными сигналами малых напряжений ( до

- 42. Низковольтная дифференциальная передача сигналов Подключения Применение Параметры трансивера (пример)

- 43. MOSI — выход ведущего, вход ведомого (Master Out Slave In) для передачи данных от ведущего устройства

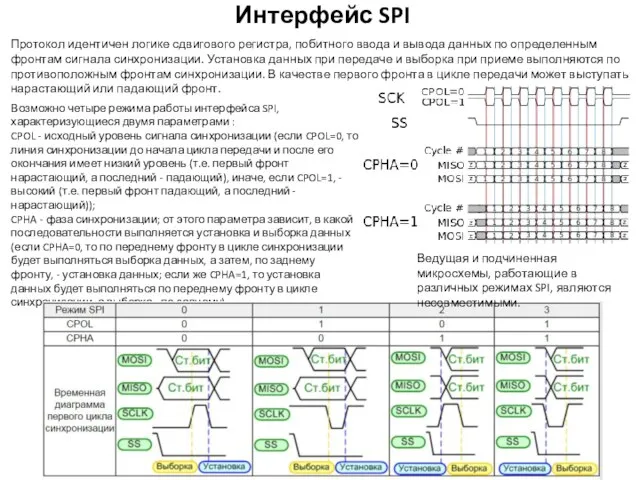

- 44. Интерфейс SPI Возможно четыре режима работы интерфейса SPI, характеризующиеся двумя параметрами : CPOL - исходный уровень

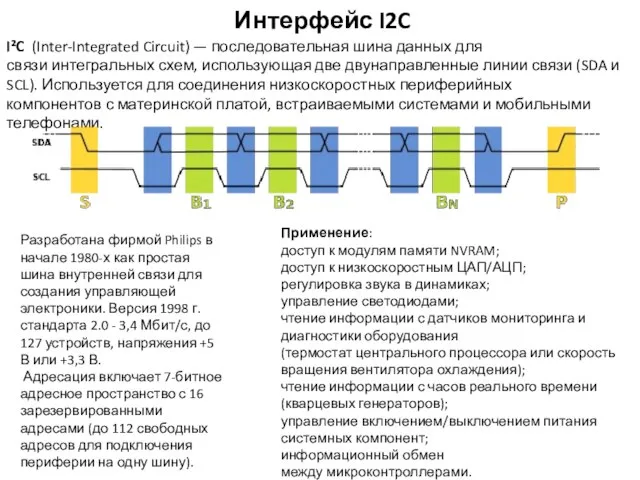

- 45. Интерфейс I2C I²C (Inter-Integrated Circuit) — последовательная шина данных для связи интегральных схем, использующая две двунаправленные

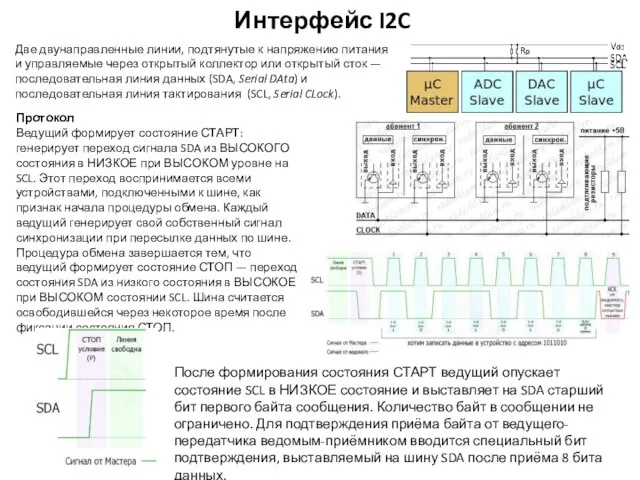

- 46. Интерфейс I2C Две двунаправленные линии, подтянутые к напряжению питания и управляемые через открытый коллектор или открытый

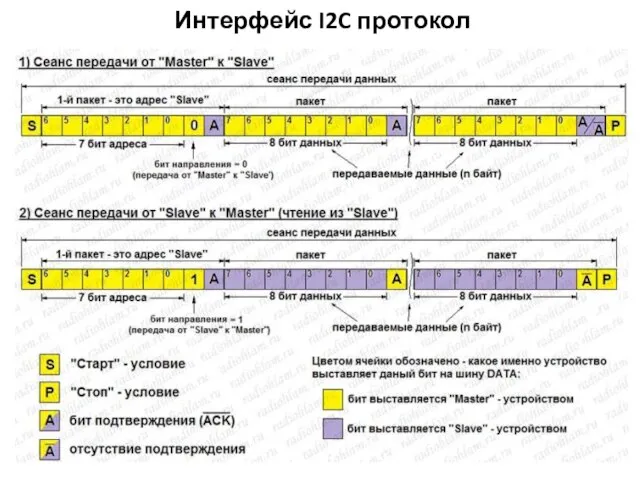

- 47. Интерфейс I2C протокол

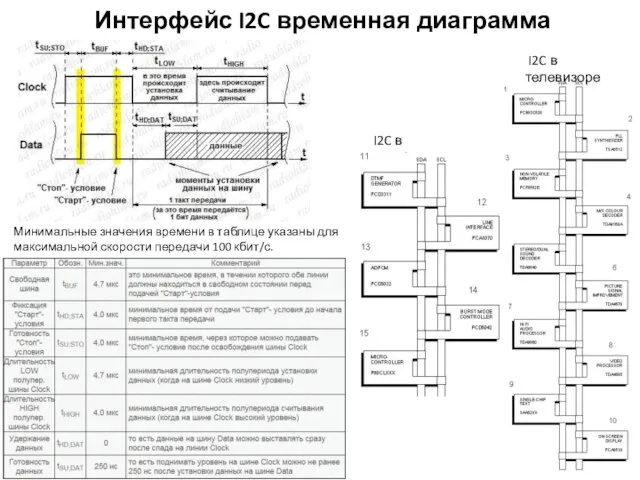

- 48. Интерфейс I2C временная диаграмма Минимальные значения времени в таблице указаны для максимальной скорости передачи 100 кбит/с.

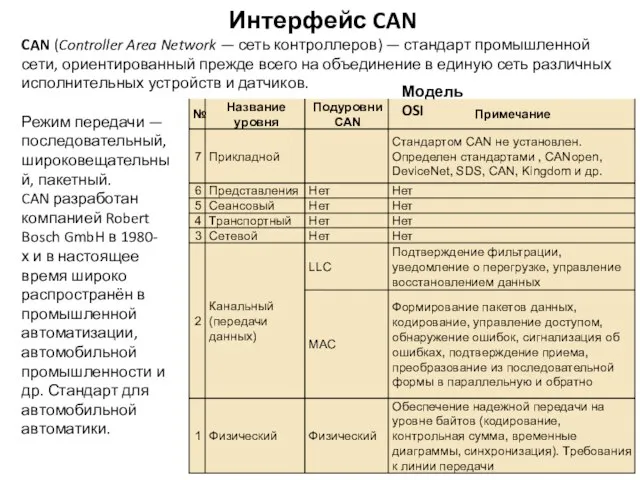

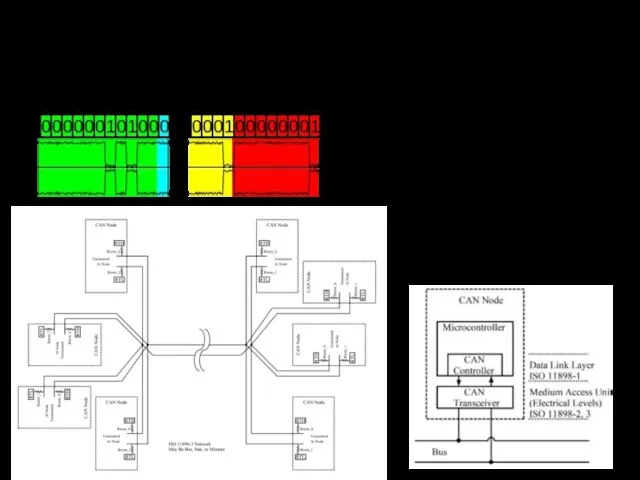

- 49. Интерфейс CAN Режим передачи — последовательный, широковещательный, пакетный. CAN разработан компанией Robert Bosch GmbH в 1980-х

- 50. Интерфейс CAN Cвойства: каждому сообщению (не устройству) устанавливается свой приоритет; гарантированная величина паузы между двумя актами

- 51. Интерфейс CAN. Трансивер " доминантное состояние" состояние линии для обозначения состояния линии с током, "рецессивное состояние"

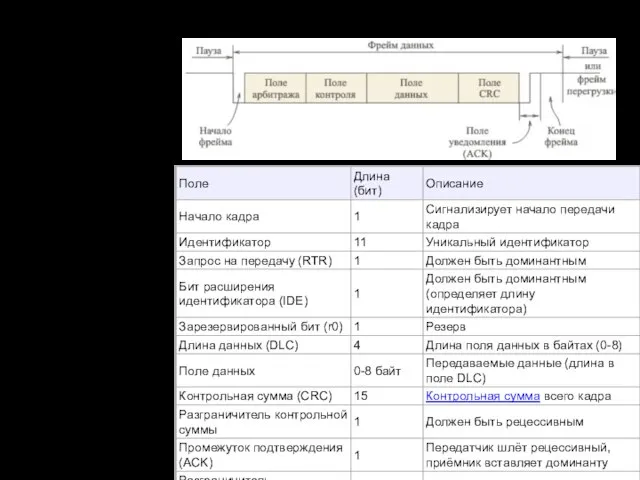

- 52. Интерфейс CAN. Протокол Виды кадров Кадр данных (data frame) — передаёт данные; Кадр удаленного запроса (remote

- 53. Интерфейс CAN. Протокол

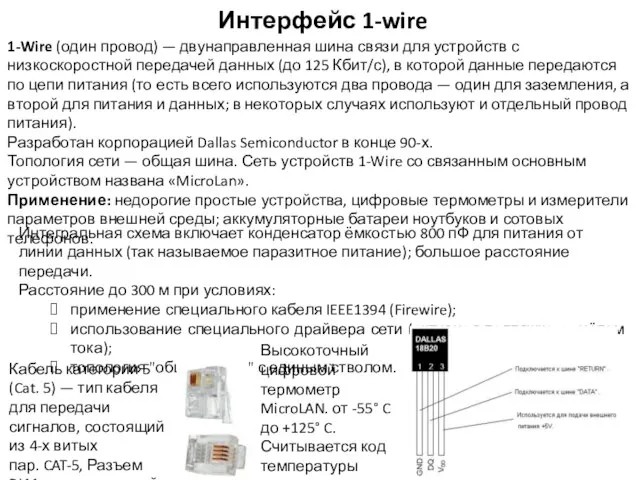

- 54. Интерфейс 1-wire 1-Wire (один провод) — двунаправленная шина связи для устройств с низкоскоростной передачей данных (до

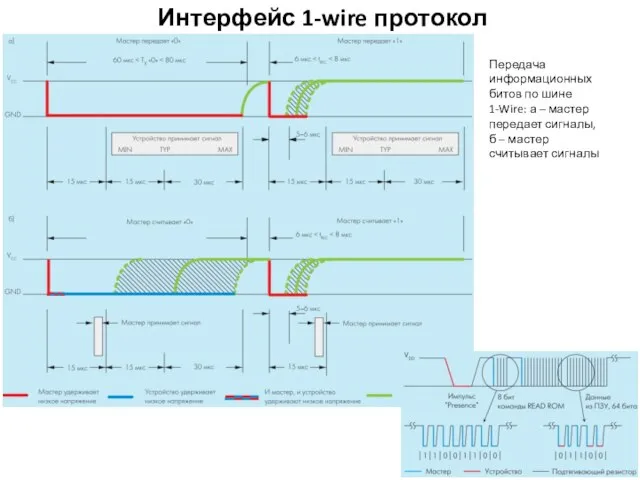

- 55. Интерфейс 1-wire протокол Передача информационных битов по шине 1-Wire: а – мастер передает сигналы, б –

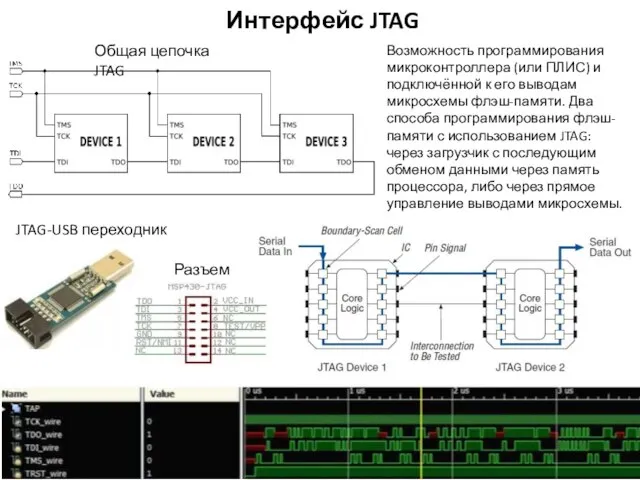

- 56. Интерфейс JTAG JTAG (Joint Test Action Group) — рабочая группа по разработке cтандарта IEEE 1149 (

- 57. Интерфейс JTAG Возможность программирования микроконтроллера (или ПЛИС) и подключённой к его выводам микросхемы флэш-памяти. Два способа

- 58. Проектирование МПС. Уровни представления МПС В начальной стадии проектирования МПС на концептуальном уровне. В процессе разработки

- 59. Этапы проектирование МПС 1. Формализация требований к системе (составляются внешние спецификации, перечисляются функции системы, формализуется техническое

- 60. Операционная система МПС. Общие сведения. Операционная система - комплекс взаимосвязанных программ, предназначенных для управления ресурсами МПС

- 61. Операционная система МПС. Функции. Основные функции: Исполнение запросов программ (ввод и вывод данных, запуск и остановка

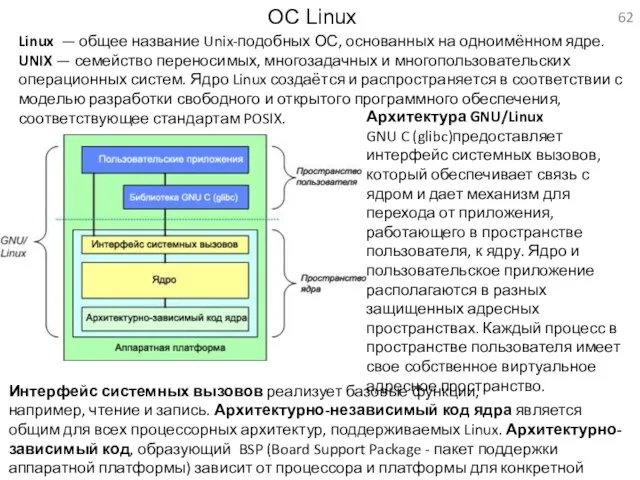

- 62. ОС Linux Linux — общее название Unix-подобных ОС, основанных на одноимённом ядре. UNIX — семейство переносимых,

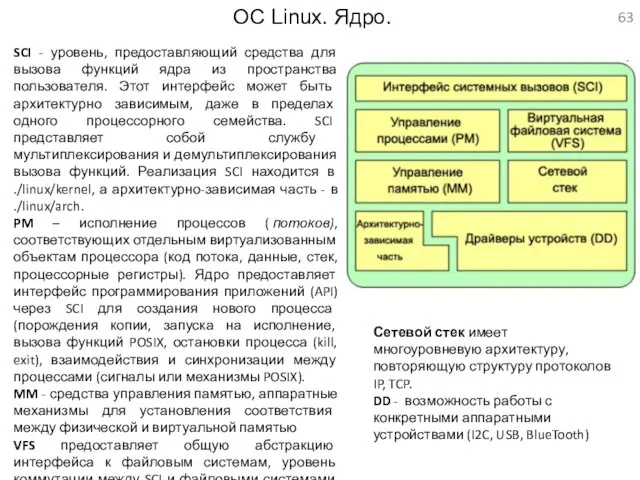

- 63. ОС Linux. Ядро. SCI - уровень, предоставляющий средства для вызова функций ядра из пространства пользователя. Этот

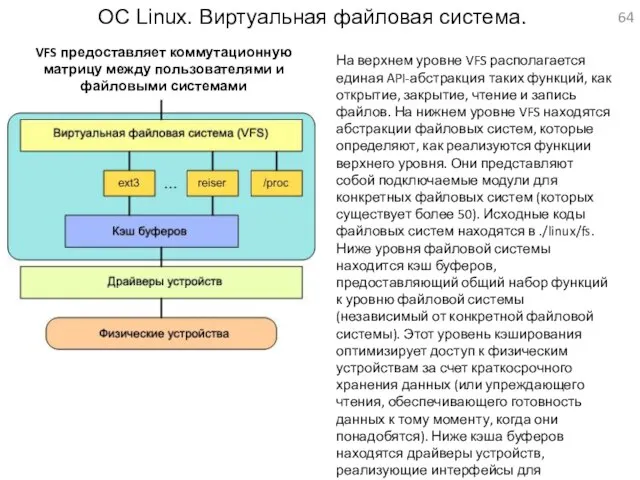

- 64. ОС Linux. Виртуальная файловая система. VFS предоставляет коммутационную матрицу между пользователями и файловыми системами На верхнем

- 65. Структура и состав ОС Android для смартфона Приложению предоставляются уже реализованные возможности других приложений, к которым

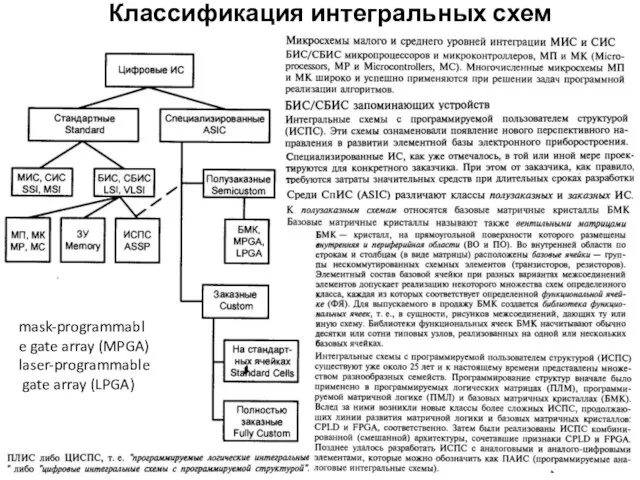

- 66. Классификация интегральных схем mask-programmable gate array (MPGA) laser-programmable gate array (LPGA)

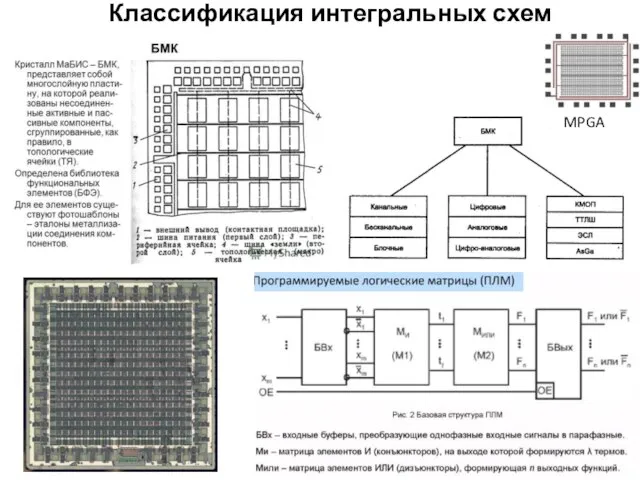

- 67. Классификация интегральных схем MPGA

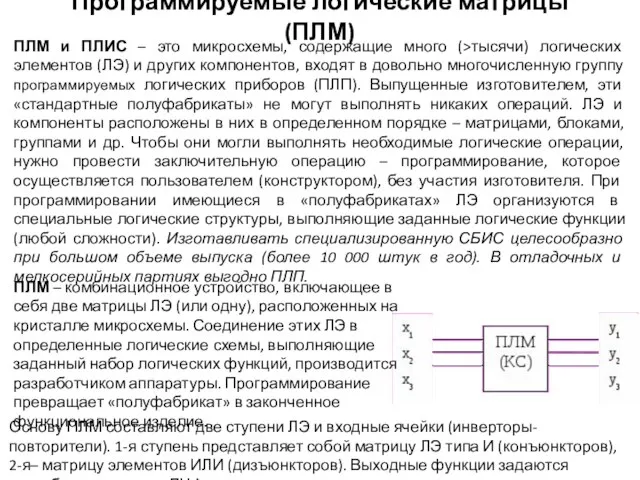

- 68. Программируемые логические матрицы (ПЛМ) ПЛМ и ПЛИС – это микросхемы, содержащие много (>тысячи) логических элементов (ЛЭ)

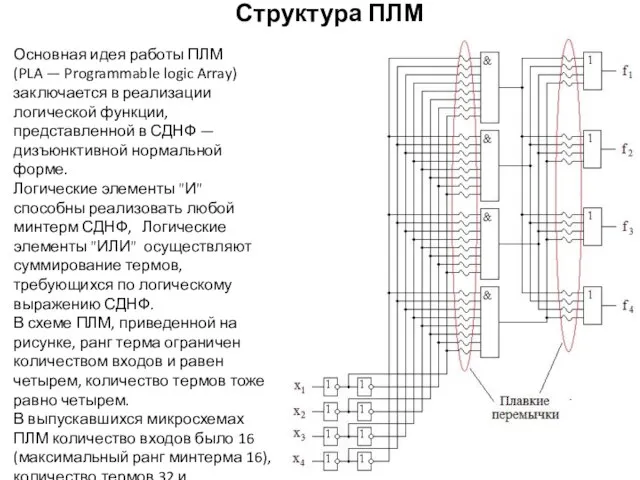

- 69. Структура ПЛМ Основная идея работы ПЛМ (PLA — Programmable logic Array) заключается в реализации логической функции,

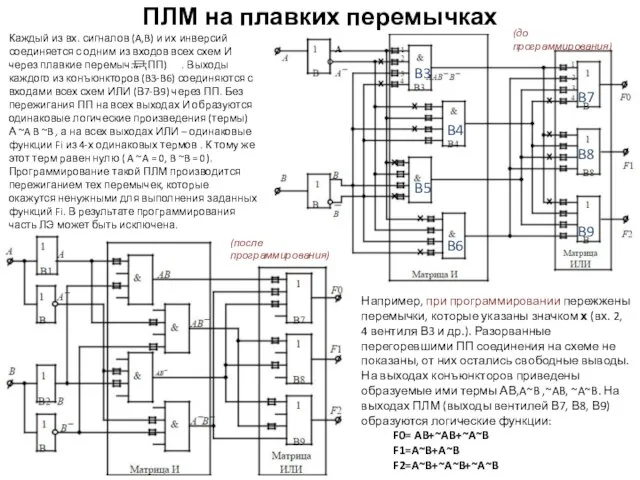

- 70. ПЛМ на плавких перемычках Каждый из вх. сигналов (A,B) и их инверсий соединяется с одним из

- 71. ПЛМ, разновидности Некоторые ПЛМ включают в себя до 10000 эквивалентных вентилей (двухвходовых И-НЕ или ИЛИ-НЕ). Число

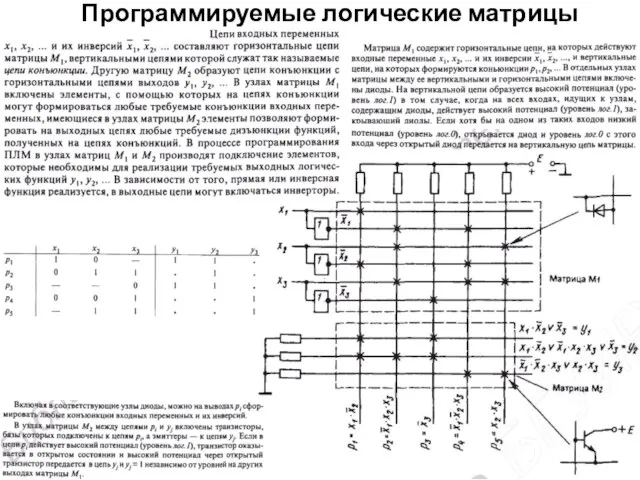

- 72. Программируемые логические матрицы Программируемая логическая матрица (ПЛМ) – это универсальная структура, позволяющая запрограммировать систему булевых функций

- 73. Программируемые логические матрицы

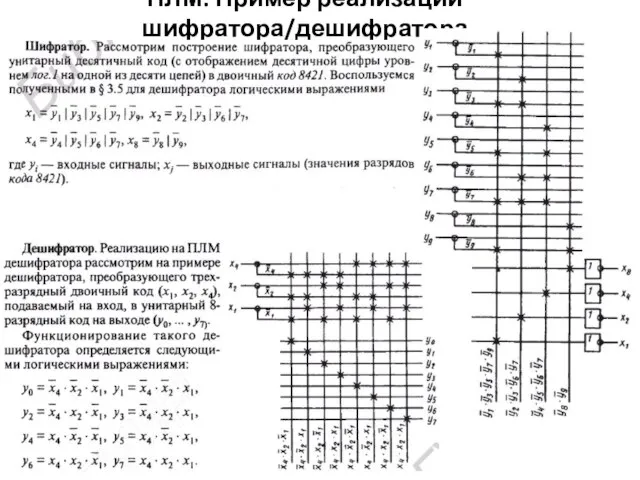

- 74. ПЛМ. Пример реализации шифратора/дешифратора

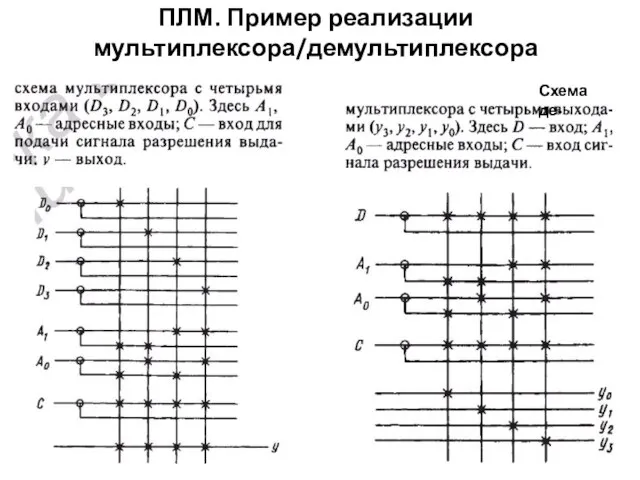

- 75. ПЛМ. Пример реализации мультиплексора/демультиплексора Схема де-

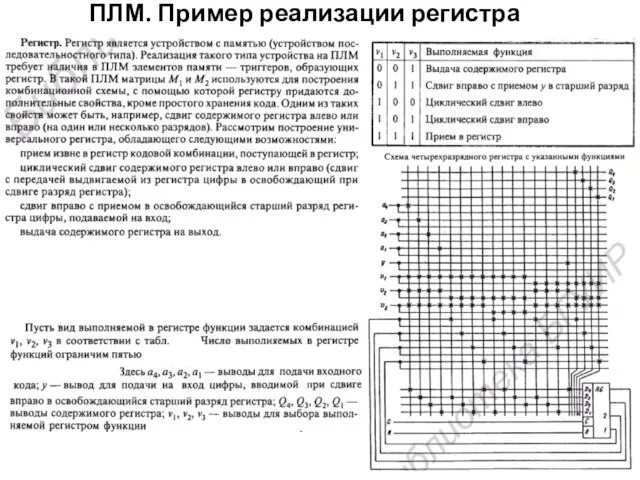

- 76. ПЛМ. Пример реализации регистра

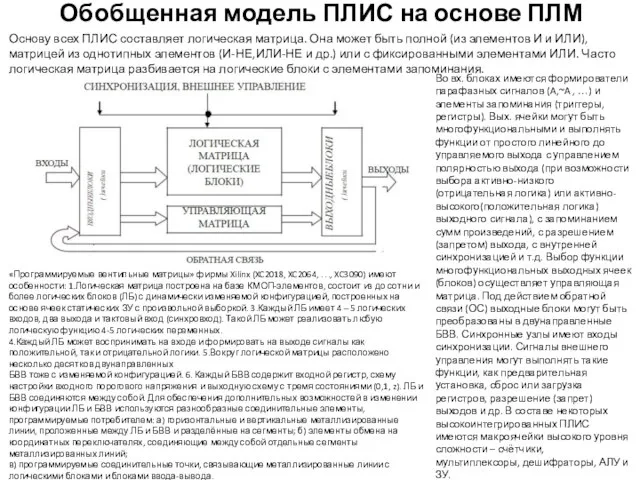

- 77. Обобщенная модель ПЛИС на основе ПЛМ Основу всех ПЛИС составляет логическая матрица. Она может быть полной

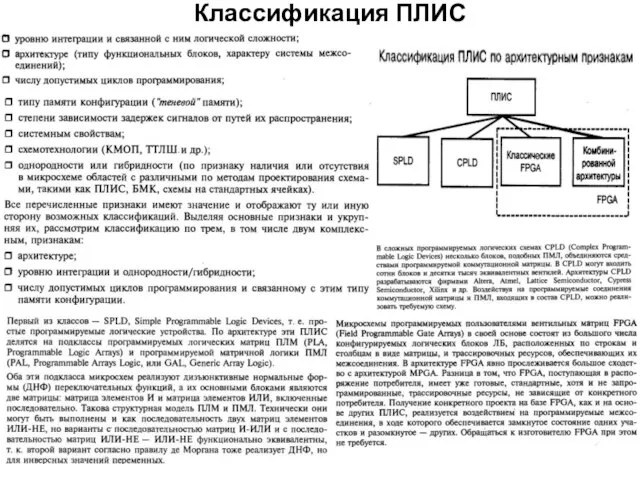

- 78. Классификация ПЛИС

- 79. Свойства и преимущества ПЛИС

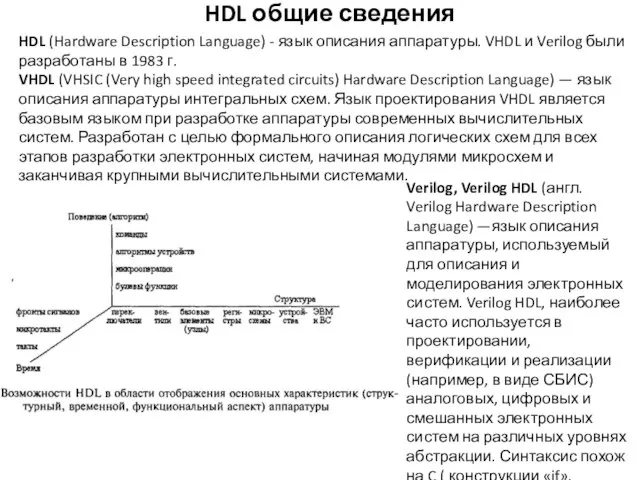

- 80. HDL общие сведения HDL (Hardware Description Language) - язык описания аппаратуры. VHDL и Verilog были разработаны

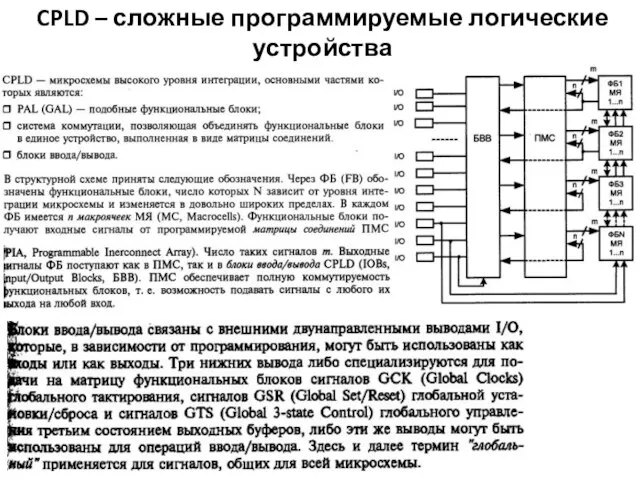

- 81. CPLD – сложные программируемые логические устройства

- 82. Блоки ввода/вывода CPLD

- 83. Программируемая матрица соединений Передача сигналов от ПМС в ФБ

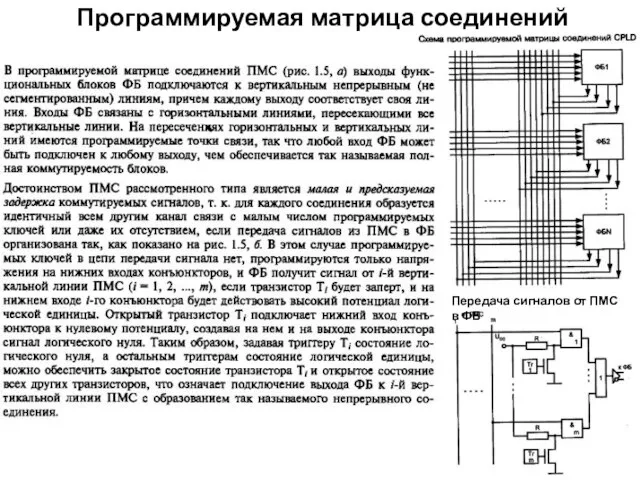

- 84. Функциональные блоки CPLD Структура ФБ

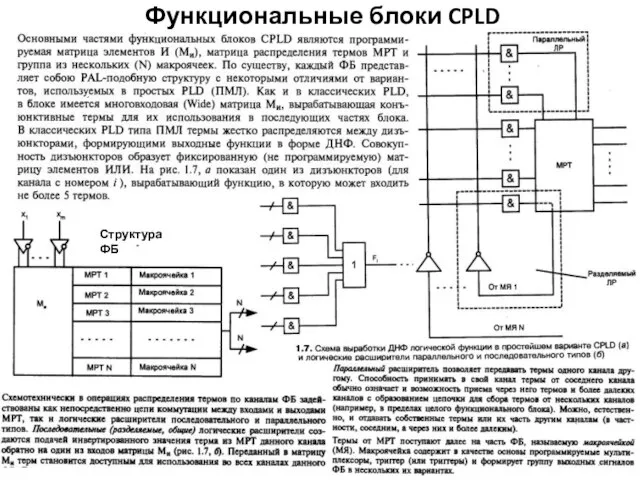

- 85. Макроячейка ФБ CPLD

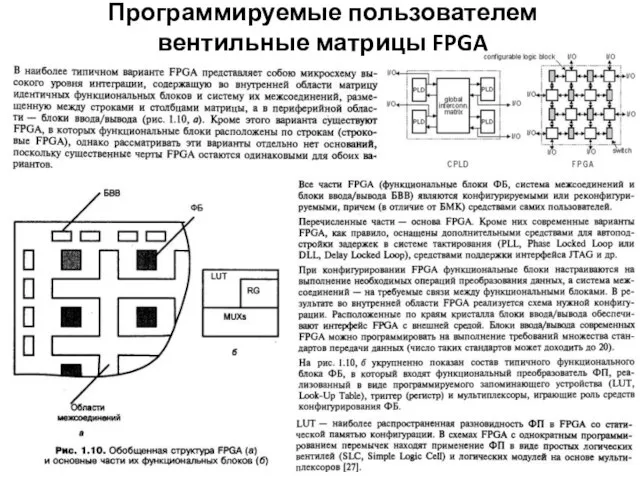

- 86. Программируемые пользователем вентильные матрицы FPGA

- 87. Блоки ввода/вывода FPGA

- 88. Межсоединения FPGA

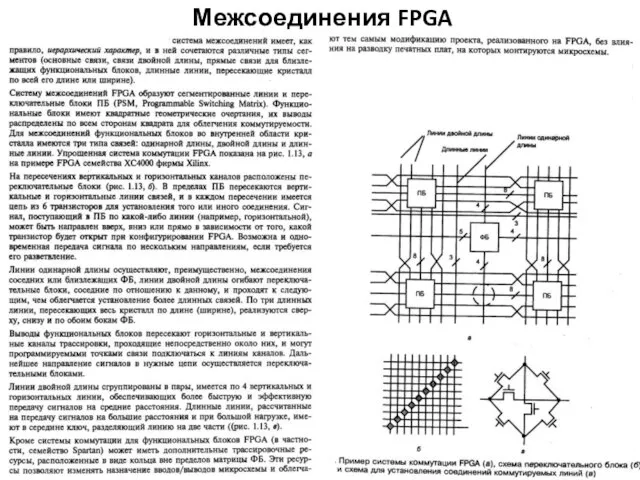

- 89. Функциональные блоки FPGA Через верх. вх. MUX1 и нижн. вх. MUX2 ф-ции G и F могут

- 90. ПЛИС с комбинированной архитектурой Семейство FLEX

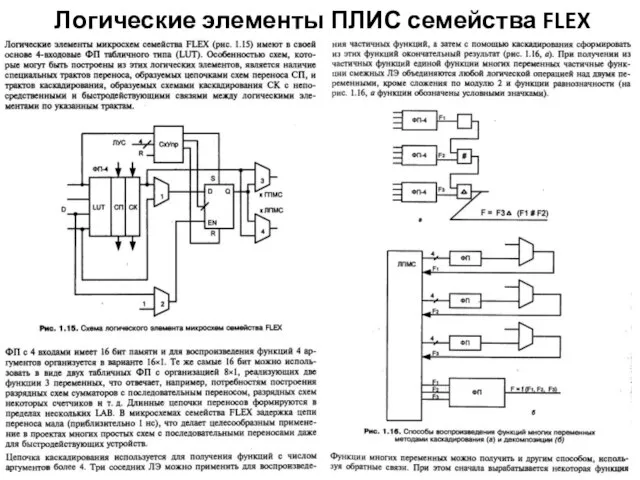

- 91. Логические элементы ПЛИС семейства FLEX

- 92. Блоки памяти ПЛИС семейства FLEX

- 93. HDL модульность

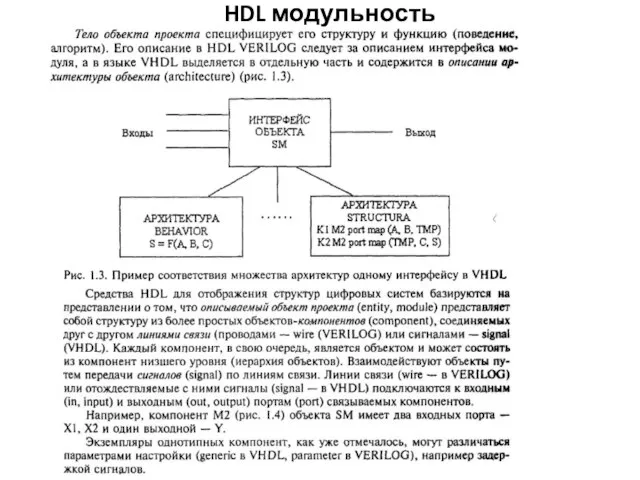

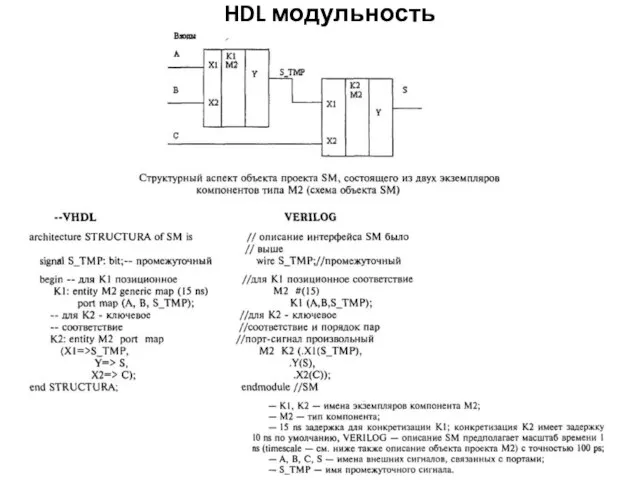

- 94. HDL модульность

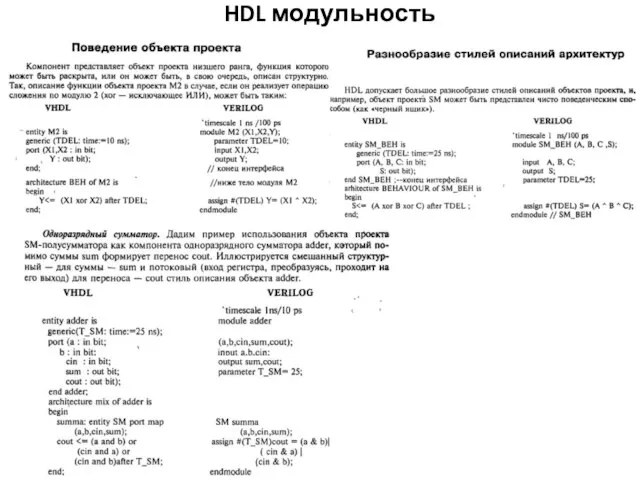

- 95. HDL модульность

- 96. HDL модульность

- 97. HDL тестирующая программа

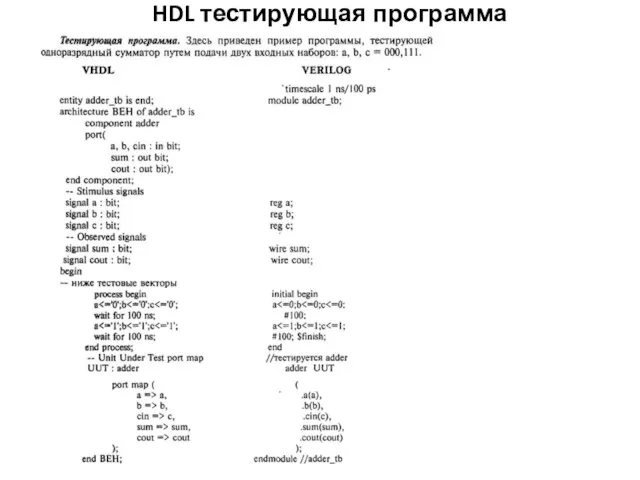

- 98. HDL программирование

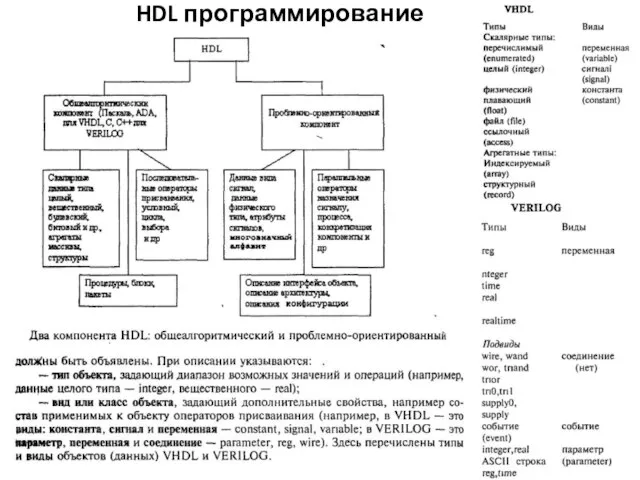

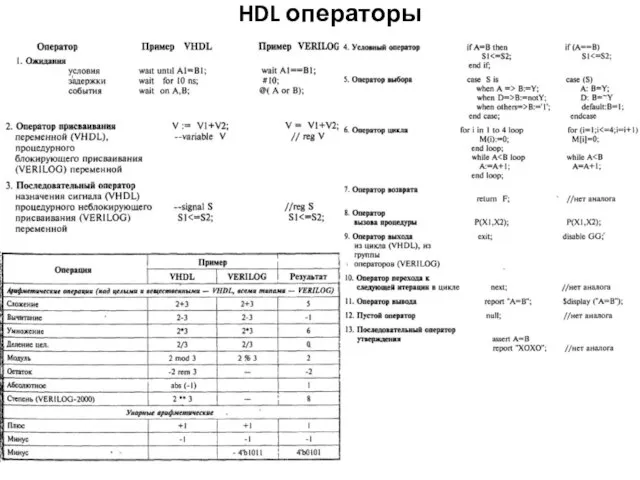

- 99. HDL операторы

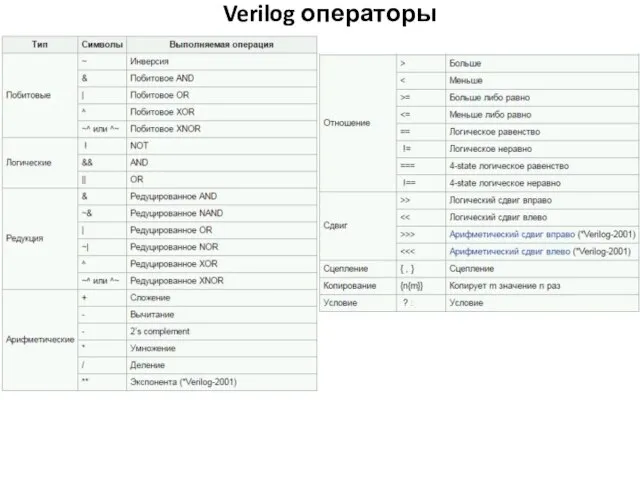

- 100. Verilog операторы

- 102. Скачать презентацию

Основы цифровой схемотехники

Последовательные Параллельные

Основы цифровой схемотехники

Последовательные Параллельные

Логические элементы

Синтез КУ в базисе ИЛИ_НЕ и И-НЕ

КНФ - формула имеет

Логические элементы

Синтез КУ в базисе ИЛИ_НЕ и И-НЕ

КНФ - формула имеет

ДНФ

СДНФ - это такая ДНФ, которая удовлетворяет трём условиям:

в ней нет одинаковых элементарных конъюнкций; в каждой конъюнкции нет одинаковых пропозициональных букв

каждая элементарная конъюнкция содержит каждую

пропозициональную букву из входящих в данную ДНФ пропозициональных букв, причём в одинаковом порядке.

СКНФ

Таблица истинности

Минимизация методами Петрика, Карно, Вейча и др.

Представление чисел в цифровых устройствах

Представление чисел в цифровых устройствах

Триггеры

Триггеры

Шифраторы, дешифраторы, мультиплексоры, демультиплексоры

Шифраторы, дешифраторы, мультиплексоры, демультиплексоры

Регистры

Сдвиговый регистр

Регистры

Сдвиговый регистр

Счетчики, сумматоры

Одноразрядный двоичный сумматор. В каждом из разрядов определяется цифра суммы

Счетчики, сумматоры

Одноразрядный двоичный сумматор. В каждом из разрядов определяется цифра суммы

Память

Память

Структура процессора (обобщенная)

Микрооперации

Структура процессора (обобщенная)

Микрооперации

Структура процессора в составе ЭВМ

Команда – вид операции, подлежащей к исполнению

Структура процессора в составе ЭВМ

Команда – вид операции, подлежащей к исполнению

Цифровые автоматы

Множества:

Возможных входных сигналов x1, x2, …, xn

Внутренних состояний

a0, a1, …,

Цифровые автоматы

Множества:

Возможных входных сигналов x1, x2, …, xn

Внутренних состояний

a0, a1, …,

Возможных выходных сигналов y1, y2, …, ym

Цифровые автоматы (пример)

Цифровые автоматы (пример)

Принцип микропрограммного управления

Управляющая память хранит кодовые комбинации микрокоманд и выдает их

Принцип микропрограммного управления

Управляющая память хранит кодовые комбинации микрокоманд и выдает их

ПА

Пример построения микропрограммы

Микропроцессор

Микропроцессор — процессор (устройство, отвечающее за выполнение арифметических, логических операций и

Микропроцессор

Микропроцессор — процессор (устройство, отвечающее за выполнение арифметических, логических операций и

Микропроцессорная система (МПС) представляет собой функционально законченное изделие, состоящее из одного или нескольких устройств, главным образом из микропроцессора и/или микроконтроллера. Микропроцессорное устройство (МПУ) представляет собой функционально и конструктивно законченное изделие, состоящее из нескольких микросхем, в состав которых входит микропроцессор; предназначено для выполнения определённого набора функций: получение, обработка, передача, преобразование информации и управление.

Генератор определяет продолжительность выполнения команды. Чем выше частота, тем при прочих равных условиях более быстродействующей является МПС.

МПС содержит МП, ОЗУ и ПЗУ, интерфейсы ввода (пульт, АЦП, датчики …) и вывода.. (дисплей, управления, внешние устройства). Все блоки МПС связаны шинами передачи цифровой информации (магистральный принцип связи). Количество линий в шине данных соответствует разрядности МПС (количеству бит в слове данных). Шина адреса применяется для указания направления передачи данных — по ней передаётся адрес ячейки памяти или блока ввода-вывода, которые получают или передают информацию в данный момент. Шина управления служит для передачи сигналов, синхронизирующих работу МПС.

Обобщенная структура МПС

При работе с высокоскоростными ПУ используется режим прямого доступа

Обобщенная структура МПС

При работе с высокоскоростными ПУ используется режим прямого доступа

Микропроцессор. Машинный код.

Машинный код (платформенно-ориентированный код), машинный язык — система команд

Микропроцессор. Машинный код.

Машинный код (платформенно-ориентированный код), машинный язык — система команд

Компьютерная программа, записанная на машинном языке, состоит из машинных инструкций, каждая из которых представлена в машинном коде в виде опкода — двоичного кода отдельной операции из системы команд машины. Вместо числовых опкодов используют их условные буквенные мнемоники. Набор таких мнемоник, вместе с некоторыми дополнительными возможностями, называется языком ассемблера.

Совместимость Каждая модель процессора имеет свой собственный набор команд, во многих моделях наборы перекрываются. Процессор A совместим с процессором B, если процессор A полностью «понимает» машинный код процессора B. Если процессоры A и B имеют некоторое подмножество инструкций, по которым они взаимно совместимы, то говорят, что они одной «архитектуры» (имеют одинаковую архитектуру набора команд). Напр. IBM System/360 с разными шинами от 8 до 64 бит имеют общую архитектуру на уровне машинного языка.

Машинный код - самый низкий уровень представления скомпилированных (ассемблированных) компьютерных программ. Свойства - громоздкость кода и трудоёмкость ручного управления ресурсами процессора, экстремальная оптимизация. ПО пишется на языках высокого уровня и транслируется в машинный код компиляторами.

Абсолютный код — программный код, пригодный для прямого выполнения процессором, то есть код, не требующий дополнительной обработки (например, разрешения ссылок между различными частями кода или привязки к адресам в памяти, обычно выполняемой загрузчиком программ). Напр. исполнимые файлы в формате .COM и загрузчик ОС, располагаемый в MBR. MBR (master boot record, главная загрузочная запись) — код и данные, необходимые для последующей загрузки операционной системы и расположенные в первых физических секторах на устройстве хранения информации. MBR содержит небольшой фрагмент исполняемого кода, таблицу разделов и специальную сигнатуру. Функция MBR - «переход» в тот раздел жёсткого диска, с которого следует исполнять «дальнейший код» (обычно — загружать ОС). Позиционно-независимый код — программа, которая может быть размещена в любой области памяти, так как все ссылки на ячейки памяти в ней относительные (например, относительно счётчика команд). Программу можно переместить в другую область памяти в любой момент.

Прерывания процессора

Прерывание (interrupt) — сигнал, сообщающий процессору о наступлении какого-либо события,

Прерывания процессора

Прерывание (interrupt) — сигнал, сообщающий процессору о наступлении какого-либо события,

В зависимости от источника возникновения сигнала, прерывания делятся на: асинхронные, или внешние (аппаратные) — события, которые исходят от внешних источников (например, периферийных устройств) и могут произойти в любой произвольный момент: сигнал от таймера, сетевой карты или дискового накопителя, нажатие клавиш клавиатуры, движение мыши. Запрос на прерывание (Interrupt request, IRQ); синхронные, или внутренние — события в самом процессоре как результат нарушения каких-то условий при исполнении машинного кода: деление на ноль или переполнение стека, обращение к недопустимым адресам памяти или недопустимый код операции; программные (частный случай внутреннего прерывания) — инициируются исполнением специальной инструкции в коде программы. Программные прерывания, как правило, используются для обращения к функциям встроенного программного обеспечения (firmware), драйверов и операционной системы.

Внешние прерывания в зависимости от возможности запрета делятся на: маскируемые — прерывания, которые можно запрещать установкой соответствующих битов в регистре маскирования прерываний; немаскируемые (Non-maskable interrupt, NMI) — обрабатываются всегда, независимо от запретов на другие прерывания (например сбой в микросхеме памяти).

Приоритизация разделяет все источники прерываний на классы и каждому классу назначается свой уровень приоритета запроса на прерывание. Относительное обслуживание прерываний -если во время обработки прерывания поступает более приоритетное прерывание, то это прерывание будет обработано только после завершения текущей процедуры обработки прерывания. Абсолютное - текущая процедура обработки прерывания вытесняется, и процессор начинает выполнять обработку вновь поступившего более приоритетного прерывания. После этого процессор возвращается к выполнению вытесненной процедуры.

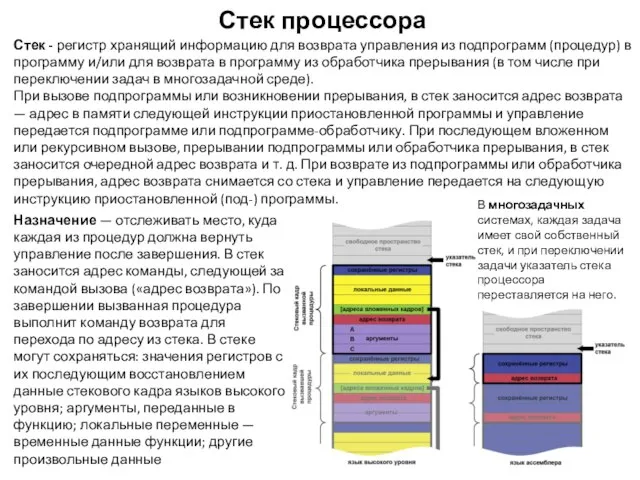

Стек процессора

Стек - регистр хранящий информацию для возврата управления из подпрограмм

Стек процессора

Стек - регистр хранящий информацию для возврата управления из подпрограмм

При вызове подпрограммы или возникновении прерывания, в стек заносится адрес возврата — адрес в памяти следующей инструкции приостановленной программы и управление передается подпрограмме или подпрограмме-обработчику. При последующем вложенном или рекурсивном вызове, прерывании подпрограммы или обработчика прерывания, в стек заносится очередной адрес возврата и т. д. При возврате из подпрограммы или обработчика прерывания, адрес возврата снимается со стека и управление передается на следующую инструкцию приостановленной (под-) программы.

Назначение — отслеживать место, куда каждая из процедур должна вернуть управление после завершения. В стек заносится адрес команды, следующей за командой вызова («адрес возврата»). По завершении вызванная процедура выполнит команду возврата для перехода по адресу из стека. В стеке могут сохраняться: значения регистров с их последующим восстановлением

данные стекового кадра языков высокого уровня; аргументы, переданные в функцию; локальные переменные — временные данные функции; другие произвольные данные

В многозадачных системах, каждая задача имеет свой собственный стек, и при переключении задачи указатель стека процессора переставляется на него.

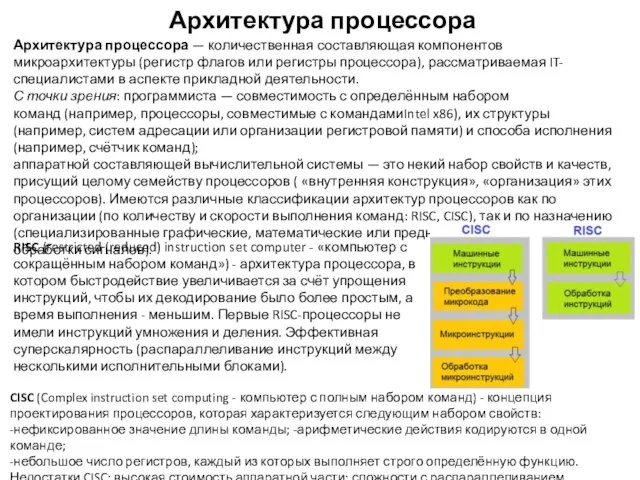

Архитектура процессора

Архитектура процессора — количественная составляющая компонентов микроархитектуры (регистр флагов или регистры процессора), рассматриваемая IT-специалистами в

Архитектура процессора

Архитектура процессора — количественная составляющая компонентов микроархитектуры (регистр флагов или регистры процессора), рассматриваемая IT-специалистами в

С точки зрения: программиста — совместимость с определённым набором команд (например, процессоры, совместимые с командамиIntel x86), их структуры (например, систем адресации или организации регистровой памяти) и способа исполнения (например, счётчик команд);

аппаратной составляющей вычислительной системы — это некий набор свойств и качеств, присущий целому семейству процессоров ( «внутренняя конструкция», «организация» этих процессоров). Имеются различные классификации архитектур процессоров как по организации (по количеству и скорости выполнения команд: RISC, CISC), так и по назначению (специализированные графические, математические или предназначенные для цифровой обработки сигналов).

CISC (Complex instruction set computing - компьютер с полным набором команд) - концепция проектирования процессоров, которая характеризуется следующим набором свойств:

-нефиксированное значение длины команды; -арифметические действия кодируются в одной команде;

-небольшое число регистров, каждый из которых выполняет строго определённую функцию.

Недостатки CISC: высокая стоимость аппаратной части; сложности с распараллеливанием вычислений.

RISC (restricted (reduced) instruction set computer - «компьютер с сокращённым набором команд») - архитектура процессора, в котором быстродействие увеличивается за счёт упрощения инструкций, чтобы их декодирование было более простым, а время выполнения - меньшим. Первые RISC-процессоры не имели инструкций умножения и деления. Эффективная суперскалярность (распараллеливание инструкций между несколькими исполнительными блоками).

Архитектуры

Архитектуры

Архитектура Фон Неймана

Однородная память микропроцессора. В память могут записываться различные программы.

Архитектура Фон Неймана

Однородная память микропроцессора. В память могут записываться различные программы.

+ Достигается максимальная гибкость микропроцессорной системы.

- Возможность непреднамеренного нарушения работоспособности системы (программные ошибки) и преднамеренное уничтожение ее работы (вирусные атаки).

Принцип однородности памяти. Совместное хранение команд и данных в памяти. Над командами можно выполнять такие же действия, как и над данными.

Принцип адресуемости памяти. Структурно основная память состоит из пронумерованных ячеек; процессору в произвольный момент времени доступна любая.

Принцип последовательного программного управления. Программа состоит из набора команд, которые выполняются процессором автоматически друг за другом в определенной последовательности.

Принцип жесткости архитектуры. Неизменяемость в процессе работы топологии, архитектуры, списка команд.

Принцип двоичного кодирования.

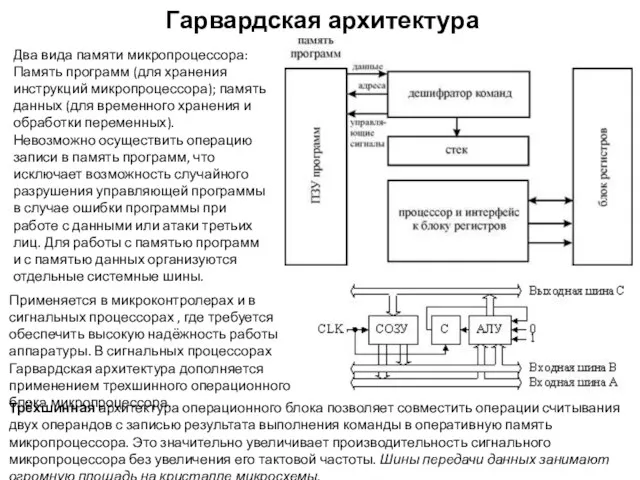

Гарвардская архитектура

Два вида памяти микропроцессора:

Память программ (для хранения инструкций микропроцессора); память

Гарвардская архитектура

Два вида памяти микропроцессора:

Память программ (для хранения инструкций микропроцессора); память

Невозможно осуществить операцию записи в память программ, что исключает возможность случайного разрушения управляющей программы в случае ошибки программы при работе с данными или атаки третьих лиц. Для работы с памятью программ и с памятью данных организуются отдельные системные шины.

Применяется в микроконтролерах и в сигнальных процессорах , где требуется обеспечить высокую надёжность работы аппаратуры. В сигнальных процессорах Гарвардская архитектура дополняется применением трехшинного операционного блока микропроцессора.

Трёхшинная архитектура операционного блока позволяет совместить операции считывания двух операндов с записью результата выполнения команды в оперативную память микропроцессора. Это значительно увеличивает производительность сигнального микропроцессора без увеличения его тактовой частоты. Шины передачи данных занимают огромную площадь на кристалле микросхемы.

Типовые структуры операционного блока

Двухшинная структура

Одношинная структура

В результате того, что входные данные

Типовые структуры операционного блока

Двухшинная структура

Одношинная структура

В результате того, что входные данные

Используется только две шины передачи данных. Для формирования двух источников данных для входов АЛУ в двухшинной схеме операционного блока микропроцессора используются два регистра временного хранения TMP1 и TMP2.

Это приводит к тому, что быстродействие микропроцессора, устроенного подобным образом, при той же частоте тактовой синхронизации будет ниже быстродействия микропроцессора, построенного на базе трехшинной структуры операционного блока. Занимает наименьшую площадь на кристалле.

Команды микропроцессора

Разрядность команд совпадает с разрядностью микропроцессора. Команда микропроцессора состоит из

Команды микропроцессора

Разрядность команд совпадает с разрядностью микропроцессора. Команда микропроцессора состоит из

При помощи 1 байт слова можно закодировать 256 операций. Именно системой команд и определяется конкретное семейство процессоров. Однобайтовые команды позволяют работать с внутренними программно доступными регистрами процессора. Для выполнения одной и той же операции над разными регистрами процессора назначаются разные коды.

Форматы различных команд для восьмиразрядного процессора по

архитектуре Фон-Неймана

Фрагмент исполняемого 16-ти ричного машинного кода

MOV R0, A ;Скопировать содержимое регистра A в регистр R0

ADD A, R5 ;Просуммировать содержимое регистров R5 и A, результат поместить в регистр A

MOV A, 1025 ;Скопировать содержимое 1025 ячейки памяти в регистр A

ADD A, #110 ;Просуммировать содержимое регистра A с числом 110

Язык программирования в котором для обозначения машинных команд используются мнемонические обозначения называется ассемблером. Компилятор осуществляет трансляцию (преобразование) исходного текста программы (исходный модуль) в машинные коды (загрузочный модуль).

Мнемоническое обозначение операции и используемые ею операнды, которые перечисляются через запятую. При этом в большинстве процессоров операнд приёмник информации записывается первым, а операнд источник информации вторым.

Операция копирования - мнемоническое обозначение MOV; суммирования используется ADD; вычитания используется мнемоническое обозначение SUB; умножения используется мнемоническое обозначение MUL.

32-разрядная архитектура ARM

На RISC-архитектуре, отклонения от принципов RISC:

Переменное количество циклов выполнения

32-разрядная архитектура ARM

На RISC-архитектуре, отклонения от принципов RISC:

Переменное количество циклов выполнения

Возможность соединять команды сдвига и вращения с командами обработки информации.

Условное выполнение – инструкция выполняется только в том случае, если выполняется конкретное условие. Это увеличивает производительность и позволяет избавиться от операторов ветвления.

Улучшенные инструкции – процессоры ARM поддерживают улучшенные DSP-инструкции для операций с цифровыми сигналами.

Программист может рассматривать ядро ARM как набор функциональных блоков – ALU, MMU и др., – соединенных шиной данных. Данные поступают в процессор через шину данных. Декодер инструкций обрабатывает инструкции перед их выполнением. ARM могут работать только с данными, которые записаны в регистрах, поэтому перед выполнением инструкций в регистры записываются данные для их выполнения. ALU считывает данные из регистров, выполняет необходимые операции и записывает результат обратно в регистр, откуда его можно записать во внешнюю память.

Процессоры ARM содержат до 18 регистров: 16 регистров данных и 2 регистра процессов. Все регистры содержат 32 бита и именуются от R0 до R15. Регистры R13, R14, R15 используются для выполнения определенных специфических задач: R13 используется в качестве указателя стека;

R14 используется как связывающий регистр;

R15 играет роль счетчика.

В зависимости от контекста эти регистры могут использоваться как регистры общего назначения. Также имеется два программных регистра, которые называются CPSR (Current Program Status Register) и SPSR (Saved Program Status Register), которые используются для сохранения состояния процессора и программы.

Cortex-M4 предназначены для использования в цифровой обработке сигналов (Digital Signal Processing, DSP). В общем виде микроконтроллеры, основанные на базе ARM Cortex-M4 имеют следующие внутренние: Микроконтроллер, установленный на рассматриваемой плате, STM32F407VG, в качестве основы использует именно решение ARM Cortex-M4.

Архитектура многоядерных процессоров

Архитектура многоядерных процессоров во многом повторяет архитектуру симметричных мультипроцессоров

Архитектура многоядерных процессоров

Архитектура многоядерных процессоров во многом повторяет архитектуру симметричных мультипроцессоров

Симметричное мультипроцессирование (Symmetric Multiprocessing) - архитектура многопроцессорных компьютеров, в которой два или более одинаковых процессора сравнимой производительности подключаются единообразно к общей памяти (и периферийным устройствам) и выполняют одни и те же функции (почему, собственно, система и называется симметричной).

Ядро является полноценным микропроцессором, использующим: конвейеры, внеочередное исполнение кода, многоуровневый кэш, поддержка векторных команд. Суперскалярность в ядре не используется. Ядро использует технологию SMT для поочередного исполнения нескольких потоков, создавая иллюзию нескольких «логических процессоров» на основе каждого ядра (в Intel технология Hyper-threading, Sun UltraSPARC - 8 потоков на ядро).

Способ связи между ядрами:

разделяемая шина

сеть на каналах точка-точка

сеть с коммутатором

общая кэш-память.

Кэш-память. 1-го уровня обладает каждое ядро в отдельности. 2-го уровня: разделяемая — расположена на одном кристалле с ядрами и доступна каждому из них в полном объёме(Intel Core); индивидуальная — отдельные кеши равного объёма, интегрированные в каждое из ядер. Обмен данными из кешей 2-го уровня между ядрами осуществляется через контроллер памяти — интегрированный (Athlon 64 X2, Turion X2, Phenom) или внешний (использовался в Pentium D, в дальнейшем Intel отказалась от такого подхода).

Гомогенная архитектура - все ядра процессора одинаковы и выполняют одни и те же задачиIntel Core Duo, Sun SPARC T3, AMD Opteron; гетерогенная архитектура - ядра процессора выполняют разные задачи (Cell альянса IBM, Sony и Toshiba, у которого из девяти ядер одно является ядром процессора общего назначения PowerPC, а восемь остальных — специализированными процессорами).

Иерархия ЗУ

Применение многопортовых ЗУ

Сетевые устройства с разделяемыми ресурсами и многопроцессорные

Иерархия ЗУ

Применение многопортовых ЗУ

Сетевые устройства с разделяемыми ресурсами и многопроцессорные

Функциональная классификация ЗУ

Функциональная классификация ЗУ

Многопортовая память

Многопортовая память - это статическое ОЗУ с двумя или более

Многопортовая память

Многопортовая память - это статическое ОЗУ с двумя или более

Единый массив памяти (COMMON CENTRAL MEMORY) и два независимых порта (PORT_L и PORT_R) для обращения к этому массиву. Элементарная ячейка двухпортовой памяти реализована на 6 транзисторах. Основу ячейки составляет статический триггер, выполненный на транзисторах Q1, Q2. Ключевыми транзисторами Q3, Q4 триггер соединен с разрядными шинами P_L, P'_L, а ключевыми транзисторами Q5, Q6 - с разрядными шинами P_R, P'_R. По этим шинам к триггеру подводится при записи и отводится при считывании информация.

Ключевые транзисторы затворами соединены с шинами выбора строки ROW SELECT_L и ROW SELECT_R соответственно. При возбуждении строки одним из сигналов выборки ключевые транзисторы открываются и подключают входы-выходы триггера к разрядным шинам.

Структура двухпортового статического ОЗУ

Статический элемент обычного и двухпортового ОЗУ

Во всех схемах с асинхронным доступом к общим ресурсам возникают конфликтные ситуации. Конфликты появляются при одновременном обращении двух независимых активных устройств к одной и той же ячейке памяти в процессе выполнения следующих операций: запись через порт L - запись через порт R; запись через порт L - чтение через порт R. При выполнении операции "запись через порт L - запись через порт R" состояние ячейки памяти будет оставаться неопределенным до тех пор, пока одно из активных устройств не завершит обращение к ней и не закончатся переходные процессы. Триггер примет устойчивое состояние, определенное "опоздавшим" устройством. При строго одновременном обращении триггер может принять любое состояние. При выполнении операции " запись через порт L - чтение через порт R" неопределенность существует только в отношении считываемых данных. С одинаковой вероятностью может быть считано как предыдущее значение ячейки памяти, так и вновь записанное в процессе текущего цикла обращения к памяти.

Архитектура двухпортовой памяти предусматривает несколько способов разрешения таких конфликтных ситуаций: с помощью арбитражной логики, семафоров или запросов на прерывания.

Принцип работы асинхронного двухпортового ОЗУ

BUSY' удерживается все время, пока не закончится

Принцип работы асинхронного двухпортового ОЗУ

BUSY' удерживается все время, пока не закончится

Семафоры - это программные арбитры, регулирующие очередность обращения двух или более независимых активных устройств к общему ресурсу. Несколько ячеек памяти, не входящих в рабочее пространство, используются как указатели занятости определенных сегментов (банков) памяти. "0" код в семафоре соответствует занятому банку, а не "0" - свободному.

Арбитр содержит элементы задержки DELAY, схему сравнения адресных линий ADD_COMP, логические элементы 3И-НЕ, соединенные по схеме триггера, логические элементы для формирования сигналов занятости (рис.3). Сигналы CE_L=0 и CE_R=0 вызывают формирование сигналов BUSY_L'=1 и BUSY_R'=1, что соответствует отсутствию запрета доступа к ОЗУ со стороны обоих активных устройств.

Схема формирования сигналов занятости банка

Арбитражная логика. Арбитр двухпортового ОЗУ устраняет конфликты. Сигналы адресных линий портов ADDRESS_L и ADDRESS_R поступают с двух направлений и, если их значения совпадают, то арбитр посылает одному из активных устройств сигнал BUSY' ("запрет доступа"). BUSY' поступает в опоздавшее к моменту арбитража активное устройство, а при строго одновременных обращениях - в устройство, выбранное случайным образом.

Алгоритм программного арбитража: активное устройство формирует запрос на обращение к банку памяти путем записи "0" в соответствующую ячейку, используемую как семафор; активное устройство считывает состояние семафора, сравнивает полученный код с "0" кодом и, если банк занят (код не "0") переходит в состояние ожидания; если банк свободен, активное устройство получает доступ к его содержимому; активное устройство заканчивает обмен и освобождает занимаемый банк памяти путем записи "1" в соответствующий семафор. Семафорная логика содержит два триггера-защелки и логические элементы 2И-НЕ, соединенные по схеме триггера для формирования сигналов занятости банка GRANT'.

Принцип работы асинхронного двухпортового ОЗУ

Прерывания. Интерфейс системы прерываний асинхронных двухпортовых ОЗУ

Принцип работы асинхронного двухпортового ОЗУ

Прерывания. Интерфейс системы прерываний асинхронных двухпортовых ОЗУ

Система ведущий/ведомый. Наращивание емкости двухпортовых ОЗУ достигается путем соединения всех одноименных выводов микросхем, кроме CE' ("выбор кристалла"). Выводы сигналов занятости BUSY в этом случае соединяются по схеме "монтажное ИЛИ". Наращивание разрядности шин данных осуществляется путем соединения всех одноименных входов микросхем, кроме информационных, и характеризуется одной особенностью: c целью предотвращения тупиковых ситуаций (одновременная выдача сигналов занятости для обоих портов) используется система "ведущий/ведомый", предусматривающая применение микросхем двухпортовых статических ОЗУ с различной реализацией арбитражной логики.

Схема формирования сигналов запросов на прерывания

Наращивание разрядности двухпортовых ОЗУ

Первый тип арбитражной логики носит название "MASTER" и обеспечивает возможность работы микросхем памяти в режимах "обычный" или "ведущий" (формирует сигналы BUSY'_L, BUSY'_R). Второй тип носит название "SLAVE" и обеспечивает возможность работы только в режиме "ведомый" (принимает сигналы занятости, сформированные ведущим устройством).

Интерфейсы

Интерфейс - совокупность средств и методов взаимодействия между элементами системы. Совокупность

Интерфейсы

Интерфейс - совокупность средств и методов взаимодействия между элементами системы. Совокупность

Физический (аппаратный) интерфейс — способ взаимодействия физических устройств.

Для микропроцессоров и ПЛИС проводные интерфейсы.

Пропускная способность — метрическая характеристика, показывающая соотношение предельного количества проходящих единиц (информации, предметов, объёма) в единицу времени через канал, систему, узел.

Пиковая пропускная способность — теоретическая максимальная пропускная способность; в реальных условиях производительность интерфейса, как правило, окажется значительно ниже, нежели та, что приведена в таблице.

Компьютерная шина - подсистема, служащая для передачи данных между функциональными блоками компьютера (процессорами). В устройстве шины можно различить механический, электрический (физический) и логический (управляющий) уровни. В отличие от соединения точка-точка, к шине обычно можно подключить несколько устройств по одному набору проводников. Каждая шина определяет свой набор коннекторов (разъемов, соединений) для физического подключения устройств, карт и кабелей. Параллельные шины (данные переносятся по словам, распределенные между несколькими проводниками), последовательные (данные переносятся побитово).

Управление передачей по шине реализуется на уровне прохождения сигнала (мультиплексоры, демультиплексоры, буферы, регистры, шинные формирователи) и со стороны операционной системы (драйвер).

Интерфейсы микропроцессора

Интерфейсы микропроцессора

Пропускные способности проводных интерфейсов

Пропускные способности проводных интерфейсов

Интерфейс UART

UART (Universal Asynchronous Receiver/Transmitter) - универсальный асинхронный приёмопередатчик, интерфейс для

Интерфейс UART

UART (Universal Asynchronous Receiver/Transmitter) - универсальный асинхронный приёмопередатчик, интерфейс для

Управление потоком данных

Контроль состояния вх CTS - передатчик перед отправкой очередного фрейма проверяет: Если CTS=0, передача происходит, иначе - нет. Если сигнал CTS=1 во время передачи фрейма, текущая передача будет завершена. Приёмник, устанавливает на вых RTS значение лог. 0, если он готов принимать данные и лог. 1, требуя от передатчика остановить передачу.

Интерфейс RS-232-С

RS-232-C соединяет два устройства. Линия передачи первого соединяется с линией

Интерфейс RS-232-С

RS-232-C соединяет два устройства. Линия передачи первого соединяется с линией

Интерфейс RS-232-С

Схема 4-проводной линии связи

FG - заземление -TxD - данные, передаваемые компьютером в

Интерфейс RS-232-С

Схема 4-проводной линии связи

FG - заземление -TxD - данные, передаваемые компьютером в

Интерфейс RS-485

RS-485 — TIA/EIA-485 Electrical Characteristics of Generators and Receivers for Use in

Интерфейс RS-485

RS-485 — TIA/EIA-485 Electrical Characteristics of Generators and Receivers for Use in

Интерфейс RS-485 обеспечивает обмен данными между несколькими устройствами по одной двухпроводной линии связи в полудуплексном режиме. Скорость до 10 Мбит/с. Дальность зависит от скорости: при скорости 10 Мбит/с максимальная длина линии — 120 м, 100 кбит/с — 1200 м.

Один передатчик рассчитан на управление 32 стандартными приемниками. Стандарт не нормирует формат информационных кадров и протокол обмена. Для передачи байтов данных используются фреймы RS-232: стартовый бит, биты данных, бит паритета (если нужно), стоповый бит.

Протоколы обмена в большинстве систем работают по принципу "ведущий-ведомый". Одно устройство на магистрали является ведущим (master) и инициирует обмен посылкой запросов подчиненным устройствам (slave), которые различаются логическими адресами (протокол Modbus RTU). Тип соединителей и распайка не оговариваются стандартом.

Уровни сигналов

Интерфейс RS-485 использует балансную (дифференциальную) схему передачи сигнала. Это означает, что уровни напряжений на сигнальных цепях А и В меняются в противофазе, как показано на приведенном ниже рисунке:

Дифференциальная передача сигналов

Дифференциальная передача сигналов

LVDS ( Low Voltage Differential Signaling ) - передача информации дифференциальными

LVDS ( Low Voltage Differential Signaling ) - передача информации дифференциальными

Стандарты:

TIA/EIA (Telecommunications Industry Association/Electronic Industries Association) - ANSI/TIA/EIA-644 (LVDS)

IEEE (Institute for Electrical and Electronics Engineering) - IEEE 1596.3

Низковольтная дифференциальная передача сигналов

Низковольтная дифференциальная передача сигналов

Подключения

Применение

Параметры трансивера (пример)

Низковольтная дифференциальная передача сигналов

Подключения

Применение

Параметры трансивера (пример)

MOSI — выход ведущего, вход ведомого (Master Out Slave In) для передачи

MOSI — выход ведущего, вход ведомого (Master Out Slave In) для передачи

MISO — вход ведущего, выход ведомого

(Master In Slave Out) для передачи

данных от ведомого устройства ведущему;

SCLK — последовательный тактовый

сигнал (Serial Clock) для передачи

тактового сигнала для ведомых устройств.

CS или SS — выбор микросхемы, выбор

ведомого (Chip Select, Slave Select)

Интерфейс SPI

SPI (Serial Peripheral Interface, последовательный периферийный интерфейс) — последовательный синхронный стандарт передачи данных в режиме полного дуплекса, предназначенный для обеспечения простого и недорогого сопряжения микроконтроллеров и периферии.

Любая передача синхронизирована с общим тактовым сигналом, генерируемым ведущим устройством (процессором). Принимающая (ведомая) периферия синхронизирует получение битовой последовательности с тактовым сигналом. К одному последовательному периферийному интерфейсу ведущего устройства-микросхемы может присоединяться несколько микросхем. Ведущее устройство выбирает ведомое для передачи, активируя сигнал «выбор кристалла» (chip select) на ведомой микросхеме. Периферия, не выбранная процессором, не принимает участия в передаче по SPI.

Простейшее подключение

Независимое подключение

Каскадное подключение

Интерфейс SPI

Возможно четыре режима работы интерфейса SPI, характеризующиеся двумя параметрами :

CPOL

Интерфейс SPI

Возможно четыре режима работы интерфейса SPI, характеризующиеся двумя параметрами :

CPOL

CPHA - фаза синхронизации; от этого параметра зависит, в какой последовательности выполняется установка и выборка данных (если CPHA=0, то по переднему фронту в цикле синхронизации будет выполняться выборка данных, а затем, по заднему фронту, - установка данных; если же CPHA=1, то установка данных будет выполняться по переднему фронту в цикле синхронизации, а выборка - по заднему).

Ведущая и подчиненная микросхемы, работающие в различных режимах SPI, являются несовместимыми.

Протокол идентичен логике сдвигового регистра, побитного ввода и вывода данных по определенным фронтам сигнала синхронизации. Установка данных при передаче и выборка при приеме выполняются по противоположным фронтам синхронизации. В качестве первого фронта в цикле передачи может выступать нарастающий или падающий фронт.

Интерфейс I2C

I²C (Inter-Integrated Circuit) — последовательная шина данных для связи интегральных схем, использующая две двунаправленные

Интерфейс I2C

I²C (Inter-Integrated Circuit) — последовательная шина данных для связи интегральных схем, использующая две двунаправленные

Применение:

доступ к модулям памяти NVRAM;

доступ к низкоскоростным ЦАП/АЦП;

регулировка звука в динамиках;

управление светодиодами;

чтение информации с датчиков мониторинга и диагностики оборудования (термостат центрального процессора или скорость вращения вентилятора охлаждения);

чтение информации с часов реального времени (кварцевых генераторов);

управление включением/выключением питания системных компонент;

информационный обмен между микроконтроллерами.

Разработана фирмой Philips в начале 1980-х как простая шина внутренней связи для создания управляющей электроники. Версия 1998 г. стандарта 2.0 - 3,4 Мбит/с, до 127 устройств, напряжения +5 В или +3,3 В.

Адресация включает 7-битное адресное пространство с 16 зарезервированными адресами (до 112 свободных адресов для подключения периферии на одну шину).

Интерфейс I2C

Две двунаправленные линии, подтянутые к напряжению питания и управляемые через

Интерфейс I2C

Две двунаправленные линии, подтянутые к напряжению питания и управляемые через

Протокол

Ведущий формирует состояние СТАРТ: генерирует переход сигнала SDA из ВЫСОКОГО состояния в НИЗКОЕ при ВЫСОКОМ уровне на SCL. Этот переход воспринимается всеми устройствами, подключенными к шине, как признак начала процедуры обмена. Каждый ведущий генерирует свой собственный сигнал синхронизации при пересылке данных по шине. Процедура обмена завершается тем, что ведущий формирует состояние СТОП — переход состояния SDA из низкого состояния в ВЫСОКОЕ при ВЫСОКОМ состоянии SCL. Шина считается освободившейся через некоторое время после фиксации состояния СТОП.

После формирования состояния СТАРТ ведущий опускает состояние SCL в НИЗКОЕ состояние и выставляет на SDA старший бит первого байта сообщения. Количество байт в сообщении не ограничено. Для подтверждения приёма байта от ведущего-передатчика ведомым-приёмником вводится специальный бит подтверждения, выставляемый на шину SDA после приёма 8 бита данных.

Интерфейс I2C протокол

Интерфейс I2C протокол

Интерфейс I2C временная диаграмма

Минимальные значения времени в таблице указаны для максимальной

Интерфейс I2C временная диаграмма

Минимальные значения времени в таблице указаны для максимальной

I2C в телевизоре

I2C в телефоне

Интерфейс CAN

Режим передачи — последовательный, широковещательный, пакетный.

CAN разработан компанией Robert Bosch GmbH в 1980-х и

Интерфейс CAN

Режим передачи — последовательный, широковещательный, пакетный.

CAN разработан компанией Robert Bosch GmbH в 1980-х и

CAN (Controller Area Network — сеть контроллеров) — стандарт промышленной сети, ориентированный прежде всего на объединение в единую сеть различных исполнительных устройств и датчиков.

Модель OSI

Интерфейс CAN

Cвойства:

каждому сообщению (не устройству) устанавливается свой приоритет; гарантированная величина паузы между двумя актами

Интерфейс CAN

Cвойства:

каждому сообщению (не устройству) устанавливается свой приоритет; гарантированная величина паузы между двумя актами

допустимость нескольких ведущих устройств в сети;

обнаружение ошибок и их сигнализация;

автоматический повтор передачи сообщений с

ошибкой; автоматическое различение сбоев и

отказов с отключением отказавших модулей.

Если один из передатчиков устанавливает в сети логический ноль, а второй - логическую единицу, то это состояние не является аварийным - линия остается в состоянии логической единицы

Интерфейс CAN. Трансивер

" доминантное состояние" состояние линии для обозначения состояния линии с

Интерфейс CAN. Трансивер

" доминантное состояние" состояние линии для обозначения состояния линии с

Интерфейс CAN. Протокол

Виды кадров

Кадр данных (data frame) — передаёт данные;

Кадр удаленного запроса (remote

Интерфейс CAN. Протокол

Виды кадров

Кадр данных (data frame) — передаёт данные;

Кадр удаленного запроса (remote

Кадр перегрузки (overload frame) — обеспечивает промежуток между кадрами данных или запроса;

Кадр ошибки (error frame) — передаётся узлом, обнаружившим в сети ошибку.

Кадры данных и запроса отделяются от предыдущих кадров межкадровым промежутком.

Интерфейс CAN. Протокол

Интерфейс CAN. Протокол

Интерфейс 1-wire

1-Wire (один провод) — двунаправленная шина связи для устройств с низкоскоростной передачей данных (до 125 Кбит/с),

Интерфейс 1-wire

1-Wire (один провод) — двунаправленная шина связи для устройств с низкоскоростной передачей данных (до 125 Кбит/с),

Разработан корпорацией Dallas Semiconductor в конце 90-х.

Топология сети — общая шина. Сеть устройств 1-Wire со связанным основным устройством названа «MicroLan».

Применение: недорогие простые устройства, цифровые термометры и измерители параметров внешней среды; аккумуляторные батареи ноутбуков и сотовых телефонов.

Интегральная схема включает конденсатор ёмкостью 800 пФ для питания от линии данных (так называемое паразитное питание); большое расстояние передачи.

Расстояние до 300 м при условиях:

применение специального кабеля IEEE1394 (Firewire);

использование специального драйвера сети (активная подтяжка с учётом тока);

топология "общая шина" с единым стволом.

Кабель категории 5 (Cat. 5) — тип кабеля для передачи сигналов, состоящий из 4-х витых пар. CAT-5, Разъем RJ11 двухпроводный.

Высокоточный цифровой термометр MicroLAN. от -55° C до +125° C. Считывается код температуры

Интерфейс 1-wire протокол

Передача информационных битов по шине 1-Wire: а –

Интерфейс 1-wire протокол

Передача информационных битов по шине 1-Wire: а –

Интерфейс JTAG

JTAG (Joint Test Action Group) — рабочая группа по разработке cтандарта IEEE 1149 (

Интерфейс JTAG

JTAG (Joint Test Action Group) — рабочая группа по разработке cтандарта IEEE 1149 (

Порт тестирования (TAP — Test Access Port) имеет 4 или 5 выводов

TDI (test data input — «вход тестовых данных») — вход последовательных данных периферийного сканирования. Команды и данные вводятся в микросхему с этого вывода по переднему фронту сигнала TCK;

TDO (test data output — «выход тестовых данных») — выход последовательных данных. Команды и данные выводятся из микросхемы с этого вывода по заднему фронту сигнала TCK;

TCK (test clock — «тестовое тактирование») — тактирует работу встроенного автомата управления периферийным сканированием. Максимальная частота сканирования периферийных ячеек зависит от используемой аппаратной части и на данный момент ограничена 25…40 МГц;

TMS (test mode select — «выбор режима тестирования») — обеспечивает переход схемы в/из режима тестирования и переключение между разными режимами тестирования.

В некоторых случаях к перечисленным сигналам добавляется сигнал TRST для инициализации порта тестирования, что необязательно, так как инициализация возможна путём подачи определённой последовательности сигналов на вход TMS. TRST ( опционально) - сброс.

Предназначен для: выходного контроля микросхем при производстве; тестирования собранных печатных плат; прошивки микросхем с памятью; отладочных работ при проектировании аппаратуры и программного обеспечения. Метод тестирования Boundary Scan (граничное сканирование) - в микросхеме выделяются функциональные блоки, входы которых можно отсоединить от остальной схемы, подать заданные комбинации сигналов и оценить состояние выходов каждого блока. Весь процесс производится специальными JTAG командами (Boundary Scan Description Language (BSDL)), никакого физического вмешательства не требуется. Возможно подключение большого количества устройств (микросхем) через один физический порт (разъем).

Интерфейс JTAG

Возможность программирования микроконтроллера (или ПЛИС) и подключённой к его выводам микросхемы флэш-памяти. Два

Интерфейс JTAG

Возможность программирования микроконтроллера (или ПЛИС) и подключённой к его выводам микросхемы флэш-памяти. Два

Общая цепочка JTAG

JTAG-USB переходник

Разъем

Проектирование МПС. Уровни представления МПС

В начальной стадии проектирования МПС на концептуальном

Проектирование МПС. Уровни представления МПС

В начальной стадии проектирования МПС на концептуальном

Уровни абстрактного представления МПС:

1) "черный ящик” (внешние спецификации; внешние характеристики);

2) Структурный – компоненты МПС: микропроцессорами, ЗУ, УВВ, внешние ЗУ, каналы связи; создается МПС, описывается функциями отдельных устройств и их взаимосвязью, информационными потоками.

3) Программный разделяется на два подуровня: команд процессора и языковой. МПС интерпретируется как последовательность операторов или команд, вызывающих то или иное действие над некоторой структурой данных;

4) Логический, присущ дискретным системам. Подуровень переключательных схем образуется вентилями и построенными на их основе операторами обработки данных. Переключательные схемы подразделяются на комбинационные и последовательностные (с памятью). Поведение системы описывается алгеброй логики, моделью конечного автомата, входными/выходными последовательностями 1 и 0. Комбинационные схемы представляются таблицей истинности. Последовательностные схемы могут описываться диаграммами или таблицами входов/выходов, в которых определены взаимно однозначные соответствия между входами схемы, внутренними состояниями (комбинациями значений элементов памяти) и выходами.

Подуровень регистровых пересылок характеризуется более высокой степенью абстрагирования и представляет собой описание регистров и передачу данных между ними. Информационная часть образуется регистрами, операторами и путями передачи данных. Управляющая определяет зависящие от времени сигналы, инициирующие пересылку данных между регистрами.

5) Схемный - резисторы и конденсаторы. Показателями поведения системы на этом уровне служат напряжение и ток, представляемые в функции времени или частоты. Этот уровень описания дискретной системы широко используется в описаниях аналоговых систем.

Этапы проектирование МПС

1. Формализация требований к системе (составляются внешние спецификации,

Этапы проектирование МПС

1. Формализация требований к системе (составляются внешние спецификации,

2. Разработка структуры и архитектуры системы (определяются функции отдельных устройств и программных средств, выбираются микропроцессорные наборы, на базе которых будет реализована система, определяются взаимодействие между аппаратными и программными средствами, временные характеристики отдельных устройств и программ).

3. Разработка и изготовление аппаратных средств и программного обеспечения системы (после определения функций, реализуемых аппаратурой, и функций, реализуемых программами, схемотехники и программисты одновременно приступают к разработке и изготовлению соответственно опытного образца и программных средств. Разработка и изготовление аппаратуры состоят из разработки структурных и принципиальных схем, изготовления прототипа, автономной отладки. Разработка программ состоит из разработки алгоритмов; написания текста исходных программ; трансляции исходных программ в объектные программы; автономной отладки.

4. Комплексная отладка и приемосдаточные испытания.

Основные приемы:

1) останов функционирования системы при возникновении определенного события;

2) чтение (изменение) содержимого памяти или регистров системы;

3) пошаговое отслеживание поведения системы;

4) отслеживание поведения системы в реальном времени;

5) временное согласование программ.

Комплексная отладка завершается приемосдаточными испытаниями, показывающими соответствие спроектированной системы техническому заданию. Для проведения комплексной отладки МПС используют логические анализаторы и комплексы: оценочные, отладочные, развития микропроцессоров, диагностирования, средств отладки.

Операционная система МПС. Общие сведения.

Операционная система - комплекс взаимосвязанных программ, предназначенных

Операционная система МПС. Общие сведения.

Операционная система - комплекс взаимосвязанных программ, предназначенных

Драйвер - компьютерное ПО, с помощью которого ОС получает доступ к аппаратному обеспечению некоторого устройства.

Разработчикам ПО ОС позволяет абстрагироваться от деталей реализации и функционирования устройств, предоставляя минимально необходимый набор функций. В сложных вычислительных МПС ОС является основной, наиболее важной (а иногда и единственной) частью системного программного обеспечения.

Ядро (kernel) — центральная часть ОС, обеспечивающая приложениям координированный доступ к ресурсам МПС, таким как процессорное время, память, внешнее аппаратное обеспечение, внешнее устройство ввода и вывода информации. Также обычно ядро предоставляет сервисы файловой системы и сетевых протоколов.

API (интерфейс программирования приложений, интерфейс прикладного программирования)— набор готовых классов, процедур, функций, структури констант, предоставляемых приложением (библиотекой, сервисом) или операционной системой для использования во внешних программных продуктах. Используется программистами при написании всевозможных приложений.

Операционная система МПС. Функции.

Основные функции:

Исполнение запросов программ (ввод и вывод данных,

Операционная система МПС. Функции.

Основные функции:

Исполнение запросов программ (ввод и вывод данных,

Загрузка программ в оперативную память и их выполнение.

Стандартизованный доступ к периферийным устройствам (устройства ввода-вывода).

Управление оперативной памятью (распределение между процессами, организация виртуальной памяти).

Управление доступом к данным на энергонезависимых носителях (таких как НЖМД, SSD, оптические диски и др.), организованным в той или иной файловой системе.

Обеспечение пользовательского интерфейса.

Сохранение информации об ошибках системы.

Дополнительные функции:

Параллельное или псевдопараллельное выполнение задач (многозадачность). Эффективное распределение ресурсов вычислительной системы между процессами.

Разграничение доступа различных процессов к ресурсам.

Организация надёжных вычислений (невозможности одного вычислительного процесса намеренно или по ошибке повлиять на вычисления в другом процессе), основана на разграничении доступа к ресурсам.

Взаимодействие между процессами: обмен данными, взаимная синхронизация.

Защита самой системы, а также пользовательских данных и программ от действий пользователей (злонамеренных или по незнанию) или приложений.

Многопользовательский режим работы и разграничение прав доступа.

ОС Linux

Linux — общее название Unix-подобных ОС, основанных на одноимённом ядре. UNIX —

ОС Linux

Linux — общее название Unix-подобных ОС, основанных на одноимённом ядре. UNIX —

Архитектура GNU/Linux

GNU C (glibc)предоставляет интерфейс системных вызовов, который обеспечивает связь с ядром и дает механизм для перехода от приложения, работающего в пространстве пользователя, к ядру. Ядро и пользовательское приложение располагаются в разных защищенных адресных пространствах. Каждый процесс в пространстве пользователя имеет свое собственное виртуальное адресное пространство.

Интерфейс системных вызовов реализует базовые функции, например, чтение и запись. Архитектурно-независимый код ядра является общим для всех процессорных архитектур, поддерживаемых Linux. Архитектурно-зависимый код, образующий BSP (Board Support Package - пакет поддержки аппаратной платформы) зависит от процессора и платформы для конкретной архитектуры.

ОС Linux. Ядро.

SCI - уровень, предоставляющий средства для вызова функций ядра

ОС Linux. Ядро.

SCI - уровень, предоставляющий средства для вызова функций ядра

PM – исполнение процессов ( потоков), соответствующих отдельным виртуализованным объектам процессора (код потока, данные, стек, процессорные регистры). Ядро предоставляет интерфейс программирования приложений (API) через SCI для создания нового процесса (порождения копии, запуска на исполнение, вызова функций POSIX, остановки процесса (kill, exit), взаимодействия и синхронизации между процессами (сигналы или механизмы POSIX).

MM - средства управления памятью, аппаратные механизмы для установления соответствия между физической и виртуальной памятью

VFS предоставляет общую абстракцию интерфейса к файловым системам, уровень коммутации между SCI и файловыми системами, поддерживаемыми ядром

Сетевой стек имеет многоуровневую архитектуру, повторяющую структуру протоколов IP, TCP.

DD - возможность работы с конкретными аппаратными устройствами (I2C, USB, BlueTooth)

ОС Linux. Виртуальная файловая система.

VFS предоставляет коммутационную матрицу между пользователями и

ОС Linux. Виртуальная файловая система.

VFS предоставляет коммутационную матрицу между пользователями и

На верхнем уровне VFS располагается единая API-абстракция таких функций, как открытие, закрытие, чтение и запись файлов. На нижнем уровне VFS находятся абстракции файловых систем, которые определяют, как реализуются функции верхнего уровня. Они представляют собой подключаемые модули для конкретных файловых систем (которых существует более 50). Исходные коды файловых систем находятся в ./linux/fs.

Ниже уровня файловой системы находится кэш буферов, предоставляющий общий набор функций к уровню файловой системы (независимый от конкретной файловой системы). Этот уровень кэширования оптимизирует доступ к физическим устройствам за счет краткосрочного хранения данных (или упреждающего чтения, обеспечивающего готовность данных к тому моменту, когда они понадобятся). Ниже кэша буферов находятся драйверы устройств, реализующие интерфейсы для конкретных физических устройств.

Структура и состав ОС Android для смартфона

Приложению предоставляются уже реализованные возможности

Структура и состав ОС Android для смартфона

Приложению предоставляются уже реализованные возможности

Фреймворк лишь выполняет написанный для него код приложения, в отличие от библиотек, которые исполняются сами. Фреймворк содержит в себе большое количество библиотек с разной функциональностью и назначением, в то время как библиотеки объединяют в себе наборы функций, близких по логике.

Библиотеки предназначены для обеспечения базового функционала приложений: предоставление реализованных алгоритмов для вышележащих уровней, поддержку файловых форматов, осуществление кодирования и декодирования информации (мультимедийные кодеки), отрисовку графики и др. Библиотеки реализованы на C/C++ и скомпилированы под конкретное аппаратное обеспечение устройства.

LINUX-ядро обеспечивает функционирование системы и отвечает за безопасность, управление памятью, энергосистемой и процессами, а также предоставляет сетевой стек и модель драйверов. Ядро также действует как уровень абстракции между аппаратным обеспечением и программным стеком.

Классификация интегральных схем

mask-programmable gate array (MPGA)

laser-programmable gate array (LPGA)

Классификация интегральных схем

mask-programmable gate array (MPGA)

laser-programmable gate array (LPGA)

Классификация интегральных схем

MPGA

Классификация интегральных схем

MPGA

Программируемые логические матрицы (ПЛМ)

ПЛМ и ПЛИС – это микросхемы, содержащие много

Программируемые логические матрицы (ПЛМ)

ПЛМ и ПЛИС – это микросхемы, содержащие много

ПЛМ – комбинационное устройство, включающее в себя две матрицы ЛЭ (или одну), расположенных на кристалле микросхемы. Соединение этих ЛЭ в определенные логические схемы, выполняющие заданный набор логических функций, производится разработчиком аппаратуры. Программирование превращает «полуфабрикат» в законченное функциональное изделие.

Основу ПЛМ составляют две ступени ЛЭ и входные ячейки (инверторы-повторители). 1-я ступень представляет собой матрицу ЛЭ типа И (конъюнкторов), 2-я– матрицу элементов ИЛИ (дизъюнкторов). Выходные функции задаются потребителем в виде ДНФ.

Структура ПЛМ

Основная идея работы ПЛМ (PLA — Programmable logic Array)

заключается в реализации

Структура ПЛМ

Основная идея работы ПЛМ (PLA — Programmable logic Array)

заключается в реализации

Логические элементы "И" способны реализовать любой минтерм СДНФ, Логические элементы "ИЛИ" осуществляют суммирование термов, требующихся по логическому выражению СДНФ.

В схеме ПЛМ, приведенной на рисунке, ранг терма ограничен количеством входов и равен четырем, количество термов тоже равно четырем.

В выпускавшихся микросхемах ПЛМ количество входов было 16 (максимальный ранг минтерма 16), количество термов 32 и количество выходов микросхемы 8.

ПЛМ на плавких перемычках

Каждый из вх. сигналов (A,B) и их инверсий

ПЛМ на плавких перемычках

Каждый из вх. сигналов (A,B) и их инверсий

Программирование такой ПЛМ производится пережиганием тех перемычек, которые окажутся ненужными для выполнения заданных функций Fi. В результате программирования часть ЛЭ может быть исключена.

(до программирования)

Например, при программировании пережжены перемычки, которые указаны значком х (вх. 2, 4 вентиля В3 и др.). Разорванные перегоревшими ПП соединения на схеме не показаны, от них остались свободные выводы. На выходах конъюнкторов приведены образуемые ими термы АВ,A~B ,~AB, ~A~B. На выходах ПЛМ (выходы вентилей В7, В8, В9) образуются логические функции:

F0= AB+~AB+~A~B

F1=A~B+A~B

F2=A~B+~A~B+~A~B

(после программирования)

B3

B4

B5

B6

B7

B8

B9

ПЛМ, разновидности

Некоторые ПЛМ включают в себя до 10000 эквивалентных вентилей

ПЛМ, разновидности

Некоторые ПЛМ включают в себя до 10000 эквивалентных вентилей

Разновидности ПЛМ:

1. Обе матрицы могут быть выполнены на однотипных ЛЭ, например на базовых ТТЛ элементах И-НЕ. Тогда вентили второй ступени (В7, …, В9) будут выполнять функции ИЛИ.

2.Программируемой может быть только одна матрица И (И-НЕ),а матрица ИЛИ при этом имеет фиксированную (непрограммируемую) структуру (программируемая матричная логика).

3.«Полуфабрикат» ПЛМ может состоять из одних матриц ЛЭ без линий соединения. При программировании таких матриц получают специализированный фотошаблон, который используется для нанесения металлизированных соединений.

4.ПЛМ может быть репрограммируемой, т.е. можно стирать старую информацию (систему соединений ЛЭ) и производить новое программирование (ПЛМ с плавкими перемычками – нерепрограммируемая).

Программируемые логические матрицы

Программируемая логическая матрица (ПЛМ) – это универсальная структура, позволяющая запрограммировать

Программируемые логические матрицы

Программируемая логическая матрица (ПЛМ) – это универсальная структура, позволяющая запрограммировать

Матрица М1 реализует необходимые конъюнкции, причем, если необходимо установить связь в матрице М1, на пересечении устанавливается диод, позволяющий осуществлять гальваническую связь между горизонтальной шиной, имеющей соответствующую переменную, и вертикальной шиной, имеющей необходимую конъюнкцию. Если такой связи не надо, диод прожигается и переменная не участвует в образовании конъюнкции. Сопротивления R1,R2,R3,R4,R5 обеспечивают протекание тока через диод на базис соответствующего транзистора и появление потенциалов.

Матрица М2 обладает собирательным свойством и программируется для организации необходимой ДНФ. На пересечении матрицы устанавливаются программируемые тсятранзисторы p-n типа. В цепи эмиттера этого транзистора имеется сопротивление, которое при программировании прожигается. В результате связь между горизонтальной и вертикальной шиной теряется.

При программировании X указывается наличие связей в матрице М2 ,т.е. «X » на схеме означают, что в этих местах матрицы имеются транзисторы. При срабатывании транзистора, соответственно на R6, R7 или R8 появляется лог. 1 и становится истинной соответствующие функции y1-y3.

Учитывая, что любая булевая функция может быть представлена в СДНФ, которая затем может быть минимизирована, программирование логической матрицы позволяет осуществить построение матрицы любой комбинированной схемы, которая отсутствует в памяти. Схема работает только при наличии входных сигналов и не запоминает предыдущее состояние.

R1 R2 R3 R4 R5

R6

R7

R8

Программируемые логические матрицы

Программируемые логические матрицы

ПЛМ. Пример реализации шифратора/дешифратора

ПЛМ. Пример реализации шифратора/дешифратора

ПЛМ. Пример реализации мультиплексора/демультиплексора

Схема де-

ПЛМ. Пример реализации мультиплексора/демультиплексора

Схема де-

ПЛМ. Пример реализации регистра

ПЛМ. Пример реализации регистра

Обобщенная модель ПЛИС на основе ПЛМ

Основу всех ПЛИС составляет логическая матрица.

Обобщенная модель ПЛИС на основе ПЛМ

Основу всех ПЛИС составляет логическая матрица.

«Программируемые вентильные матрицы» фирмы Xilinx (XC2018, XC2064, …, XC3090) имеют особенности: 1.Логическая матрица построена на базе КМОП-элементов, состоит из до сотни и более логических блоков (ЛБ) с динамически изменяемой конфигурацией, построенных на основе ячеек статических ЗУ с произвольной выборкой. 3.Каждый ЛБ имеет 4 – 5 логических входов, два выхода и тактовый вход (синхровход). Такой ЛБ может реализовать любую логическую функцию 4-5 логических переменных.

4.Каждый ЛБ может воспринимать на входе и формировать на выходе сигналы как положительной, так и отрицательной логики. 5.Вокруг логической матрицы расположено несколько десятков двунаправленных

БВВ тоже с изменяемой конфигурацией. 6. Каждый БВВ содержит входной регистр, схему настройки входного порогового напряжения и выходную схему с тремя состояниями (0,1, z). ЛБ и БВВ соединяются между собой. Для обеспечения дополнительных возможностей в изменении конфигурации ЛБ и БВВ используются разнообразные соединительные элементы, программируемые потребителем: а) горизонтальные и вертикальные металлизированные линии, проложенные между ЛБ и БВВ и разделённые на сегменты; б) элементы обмена на координатных переключателях, соединяющие между собой отдельные сегменты металлизированных линий;

в) программируемые соединительные точки, связывающие металлизированные линии с логическими блоками и блоками ввода-вывода.

Во вх. блоках имеются формирователи парафазных сигналов (A,~A , …) и элементы запоминания (триггеры, регистры). Вых. ячейки могут быть многофункциональными и выполнять функции от простого линейного до управляемого выхода с управлением полярностью выхода (при возможности выбора активно-низкого(отрицательная логика) или активно-высокого(положительная логика) выходного сигнала), с запоминанием сумм произведений, с разрешением (запретом) выхода, с внутренней синхронизацией и т.д. Выбор функции многофункциональных выходных ячеек (блоков) осуществляет управляющая матрица. Под действием обратной связи (ОС) выходные блоки могут быть преобразованы в двунаправленные БВВ. Синхронные узлы имеют входы синхронизации. Сигналы внешнего управления могут выполнять такие функции, как предварительная установка, сброс или загрузка регистров, разрешение (запрет) выходов и др. В составе некоторых высокоинтегрированных ПЛИС имеются макроячейки высокого уровня сложности – счётчики, мультиплексоры, дешифраторы, АЛУ и ЗУ.

Классификация ПЛИС

Классификация ПЛИС

Свойства и преимущества ПЛИС

Свойства и преимущества ПЛИС

HDL общие сведения

HDL (Hardware Description Language) - язык описания аппаратуры. VHDL

HDL общие сведения

HDL (Hardware Description Language) - язык описания аппаратуры. VHDL

VHDL (VHSIC (Very high speed integrated circuits) Hardware Description Language) — язык описания аппаратуры интегральных схем. Язык проектирования VHDL является базовым языком при разработке аппаратуры современных вычислительных систем. Разработан с целью формального описания логических схем для всех этапов разработки электронных систем, начиная модулями микросхем и заканчивая крупными вычислительными системами.

Verilog, Verilog HDL (англ. Verilog Hardware Description Language) —язык описания аппаратуры, используемый для описания и моделирования электронных систем. Verilog HDL, наиболее часто используется в проектировании, верификации и реализации (например, в виде СБИС) аналоговых, цифровых и смешанных электронных систем на различных уровнях абстракции. Синтаксис похож на C ( конструкции «if», «while»)

CPLD – сложные программируемые логические устройства

CPLD – сложные программируемые логические устройства

Блоки ввода/вывода CPLD

Блоки ввода/вывода CPLD

Программируемая матрица соединений

Передача сигналов от ПМС в ФБ

Программируемая матрица соединений

Передача сигналов от ПМС в ФБ

Функциональные блоки CPLD

Структура ФБ

Функциональные блоки CPLD

Структура ФБ

Макроячейка ФБ CPLD

Макроячейка ФБ CPLD

Программируемые пользователем вентильные матрицы FPGA

Программируемые пользователем вентильные матрицы FPGA

Блоки ввода/вывода FPGA

Блоки ввода/вывода FPGA

Межсоединения FPGA

Межсоединения FPGA

Функциональные блоки FPGA

Через верх. вх. MUX1 и нижн. вх. MUX2 ф-ции

Функциональные блоки FPGA

Через верх. вх. MUX1 и нижн. вх. MUX2 ф-ции

1.Табличный ФП типа LUT представляет собой ЗУ, хранящее значения искомых функций, считываемые по адресу-аргументу. ЗУ с организацией 2m *n имеет m адресных входов и n выходных линий, может хранить таблицу для считывания я функций от m переменных. Время вычисления результата равно времени считывания слова из памяти.

2.ФБ — программируемые MUX (фирма Actel) Вых. величина описывается некоторой так называемой порождающей функцией, соответствующей использованию всех входов схемы как информационных. При программировании на некоторые входы задаются константы 0 и 1, разные сочетания которых порождают целый.

3. Мелкозернистые ФБ, составленные из транзисторных пар, выделяемых из цепочек транзисторов с п - и р -каналами. Из таких пар собираются традиционные для КМОП - схем логические элементы.

ФБ FPGA с триггерной памятью-конфигурации на примере микросхемы семейства Spartan фирмы Хilinx. В функциональных блоках этих микросхем логические преобразования выполняются тремя LUT-блоками (функциональными преобразователями ФП) G, F и Н. Преобразователи G и F — программируемые ЗУ 16x1, способные воспроизводить любые функции 4-х переменных, значения которых могут быть переданы на выходы Y и X через MUX 4 и 6 при соответствующем их программировании (через линии верхних вх. MUX).

ПЛИС с комбинированной архитектурой

Семейство FLEX

ПЛИС с комбинированной архитектурой

Семейство FLEX

Логические элементы ПЛИС семейства FLEX

Логические элементы ПЛИС семейства FLEX

Блоки памяти ПЛИС семейства FLEX

Блоки памяти ПЛИС семейства FLEX

HDL модульность

HDL модульность

HDL модульность

HDL модульность

HDL модульность

HDL модульность

HDL модульность

HDL модульность

HDL тестирующая программа

HDL тестирующая программа

HDL программирование

HDL программирование

HDL операторы

HDL операторы

Verilog операторы

Verilog операторы

20160108_zhivichkova_e._i._schastlivyy_skazochnyy_sluchay

20160108_zhivichkova_e._i._schastlivyy_skazochnyy_sluchay Автомобилестроение в Европе на примере одного из городов Германии

Автомобилестроение в Европе на примере одного из городов Германии Второй цикл семинаров по медиаобразованию и духовно-нравственному воспитанию для преподавателей Тверского региона

Второй цикл семинаров по медиаобразованию и духовно-нравственному воспитанию для преподавателей Тверского региона Программа (концепция) развития муниципального образования Город Ижевск

Программа (концепция) развития муниципального образования Город Ижевск Психодиагностика

Психодиагностика Дорога к храму

Дорога к храму 20180115_zvuk_sh_powerpoint

20180115_zvuk_sh_powerpoint Адаптация обучающихся с расстройствами аутистического спектра (РАС) в специализированном классе общеобразовательной школы

Адаптация обучающихся с расстройствами аутистического спектра (РАС) в специализированном классе общеобразовательной школы תהליך מקוצר לרישום

תהליך מקוצר לרישום Покер Roofbuilder

Покер Roofbuilder Корневая система

Корневая система 20130320_blok1

20130320_blok1 Транспортировка углеводородного сырья с месторождения

Транспортировка углеводородного сырья с месторождения Свойства пластовых флюидов, отношения PVT

Свойства пластовых флюидов, отношения PVT Топливно – энергетический комплекс России (ТЭК)

Топливно – энергетический комплекс России (ТЭК) Влияние минорных тональностей на психофизиологическое состояние человека

Влияние минорных тональностей на психофизиологическое состояние человека Експертиза риби та рибних товарів

Експертиза риби та рибних товарів Колористические типы внешности человека. Аксессуары

Колористические типы внешности человека. Аксессуары Новые возможности видеокамер IP-P Starvis

Новые возможности видеокамер IP-P Starvis Теоретические основы реконструкции. Формы и виды реконструкции

Теоретические основы реконструкции. Формы и виды реконструкции Диакритические знаки во французском языке

Диакритические знаки во французском языке 20151117_distantsionnoe_obuchenie

20151117_distantsionnoe_obuchenie Экстрактивная и азеотропная ректификация

Экстрактивная и азеотропная ректификация Кундалини Рэйки

Кундалини Рэйки The way of making the mold: d60-48 holder-01 mold report

The way of making the mold: d60-48 holder-01 mold report LaserJet Enterprise M60x/M63x NPI Technical Training

LaserJet Enterprise M60x/M63x NPI Technical Training den-rozhdeniya_1

den-rozhdeniya_1 Морфологическая норма

Морфологическая норма