Содержание

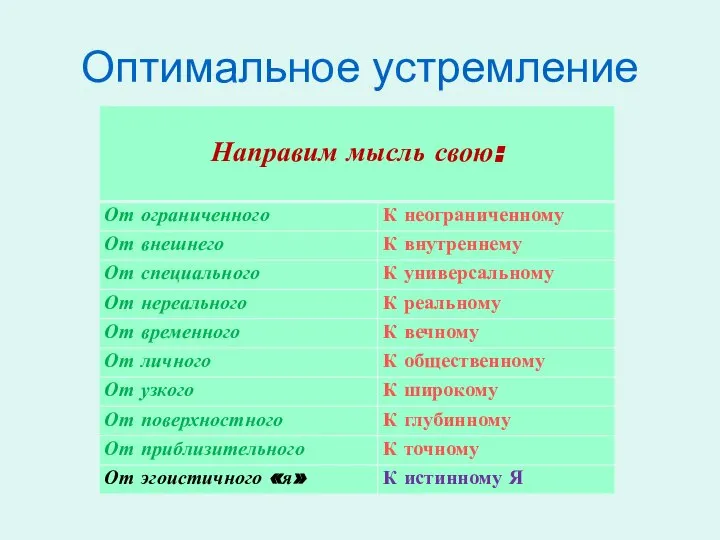

- 2. Оптимальное устремление

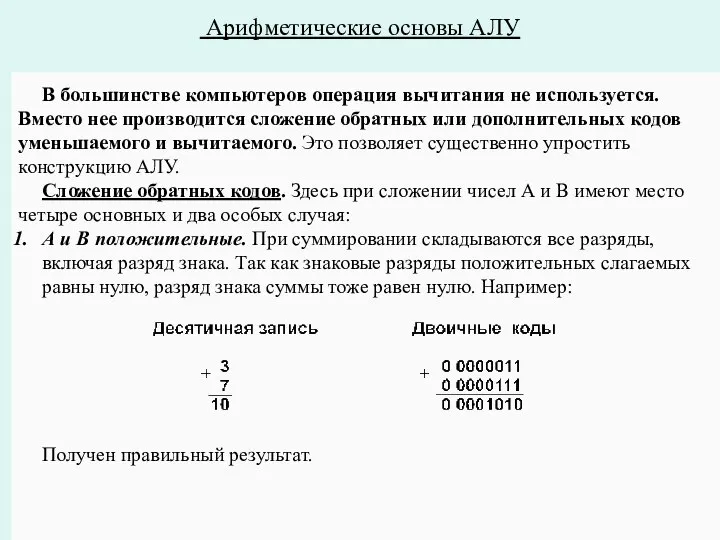

- 4. Арифметические основы АЛУ В большинстве компьютеров операция вычитания не используется. Вместо нее производится сложение обратных или

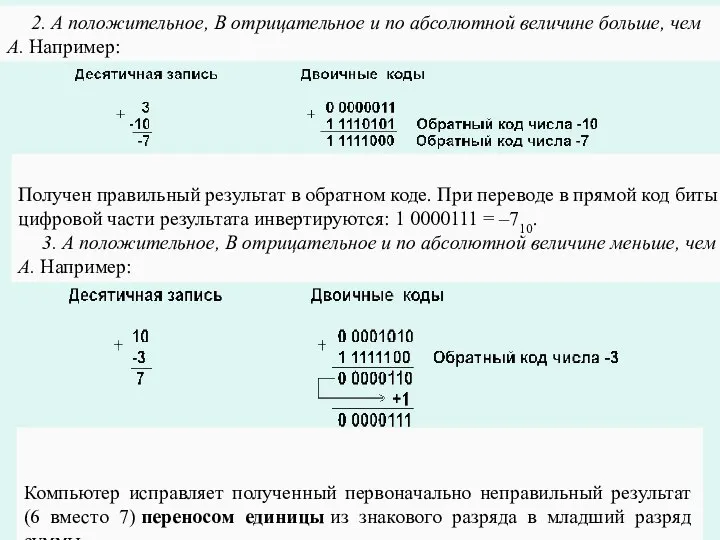

- 5. 2. А положительное, B отрицательное и по абсолютной величине больше, чем А. Например: Получен правильный результат

- 6. 4. А и В отрицательные. Например: Полученный первоначально неправильный результат (обратный код числа –1110 вместо обратного

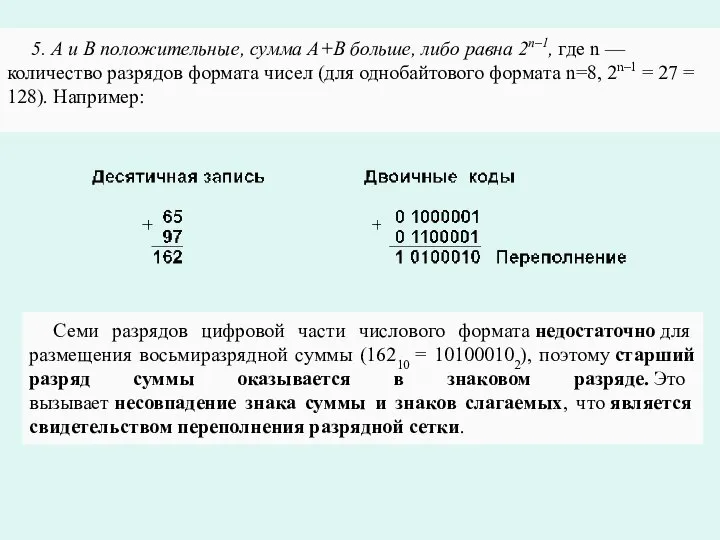

- 7. 5. А и В положительные, сумма А+В больше, либо равна 2n–1, где n — количество разрядов

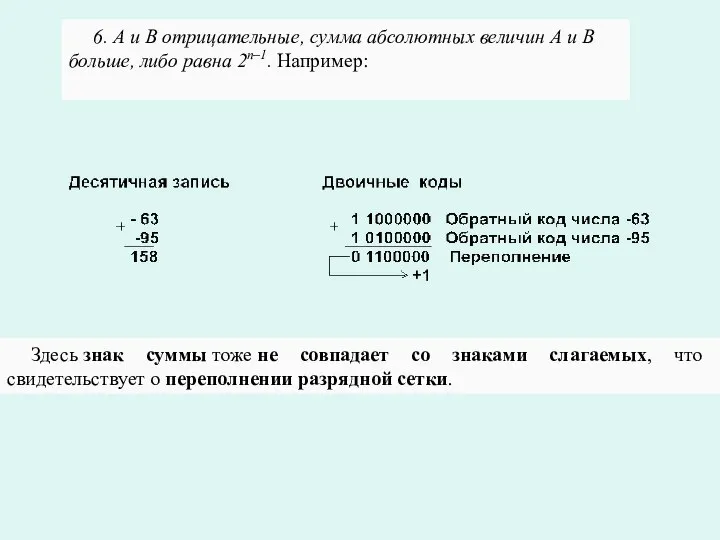

- 8. 6. А и В отрицательные, сумма абсолютных величин А и В больше, либо равна 2n–1. Например:

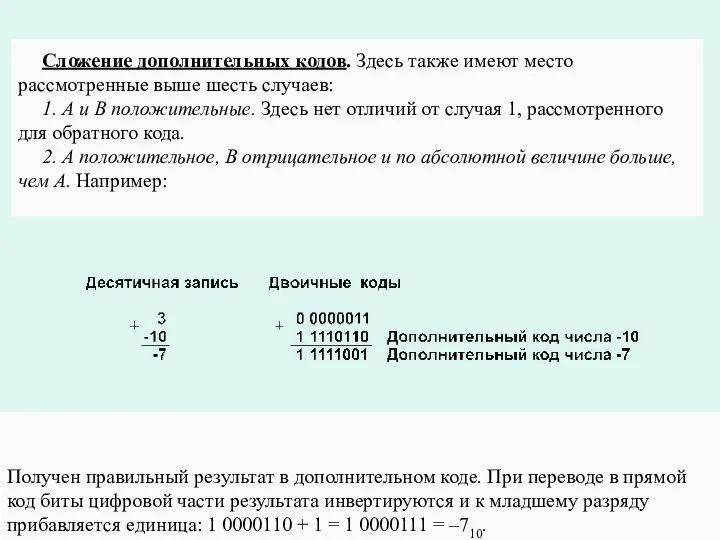

- 9. Сложение дополнительных кодов. Здесь также имеют место рассмотренные выше шесть случаев: 1. А и В положительные.

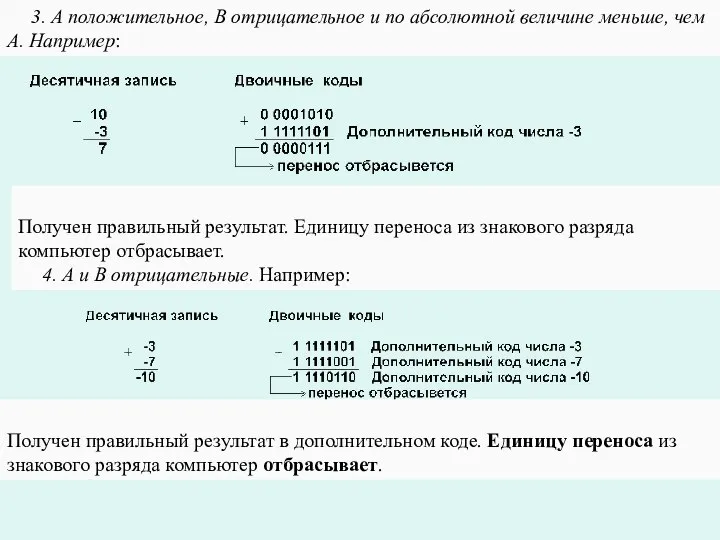

- 10. 3. А положительное, B отрицательное и по абсолютной величине меньше, чем А. Например: Получен правильный результат.

- 11. Случаи переполнения для дополнительных кодов рассматриваются по аналогии со случаями 5 и 6 для обратных кодов.

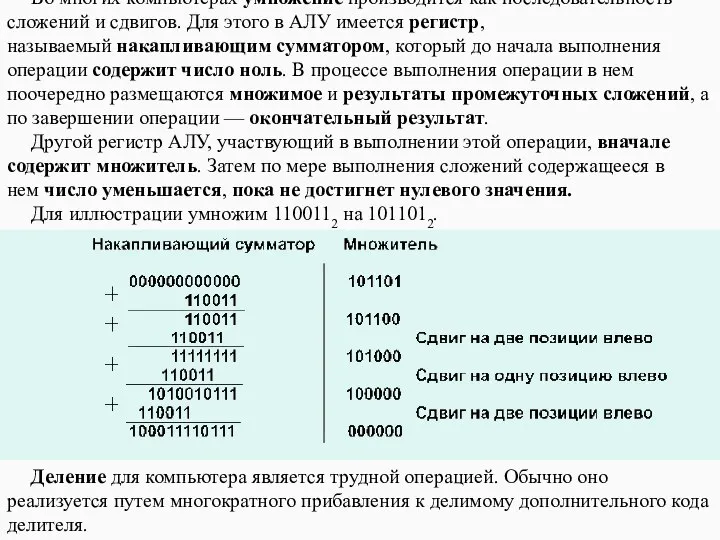

- 12. Умножение и деление Во многих компьютерах умножение производится как последовательность сложений и сдвигов. Для этого в

- 13. Классификация АЛУ По способу действия над операндами АЛУ делятся на последовательные и параллельные. По структуре АЛУ

- 14. Вариант Подробной классификации АЛУ

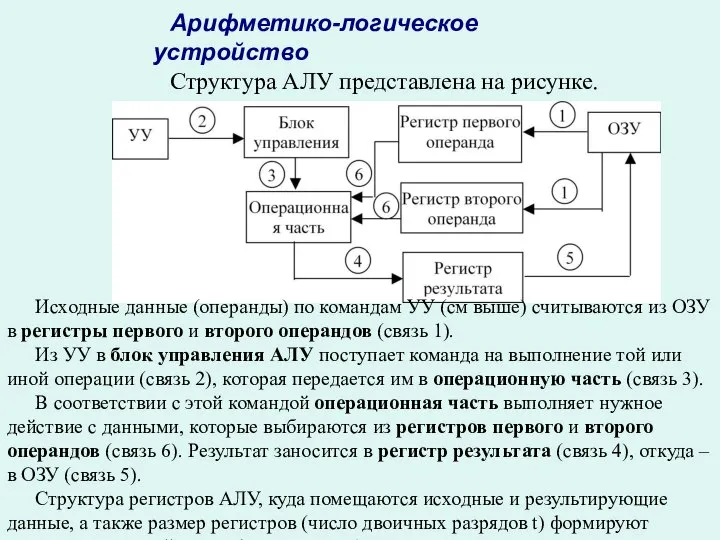

- 15. Арифметико-логическое устройство Структура АЛУ представлена на рисунке. Исходные данные (операнды) по командам УУ (см выше) считываются

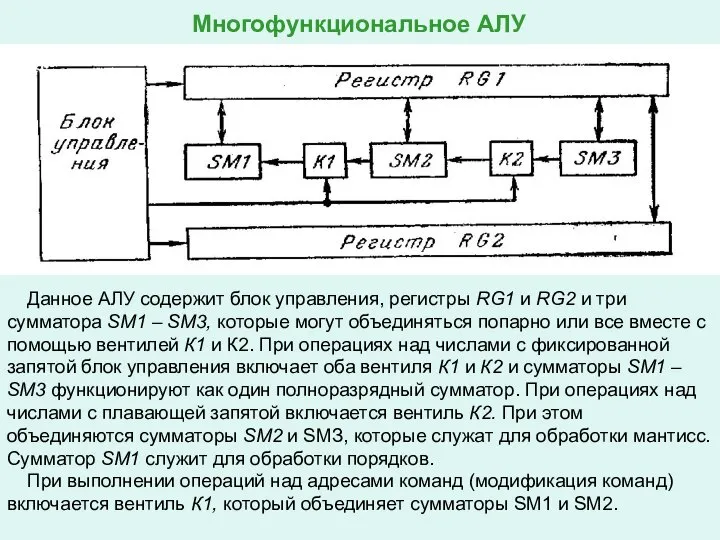

- 16. Многофункциональное АЛУ Данное АЛУ содержит блок управления, регистры RG1 и RG2 и три сумматора SM1 –

- 17. АЛУ с непосредственными связями и накапливающим сумматором Сумматор, схемы для выполнения логических операций и cдвигов, а

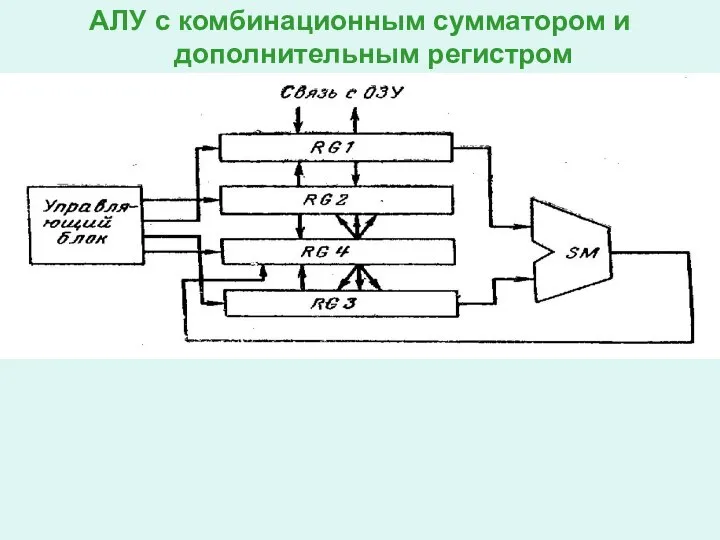

- 18. АЛУ с комбинационным сумматором и дополнительным регистром

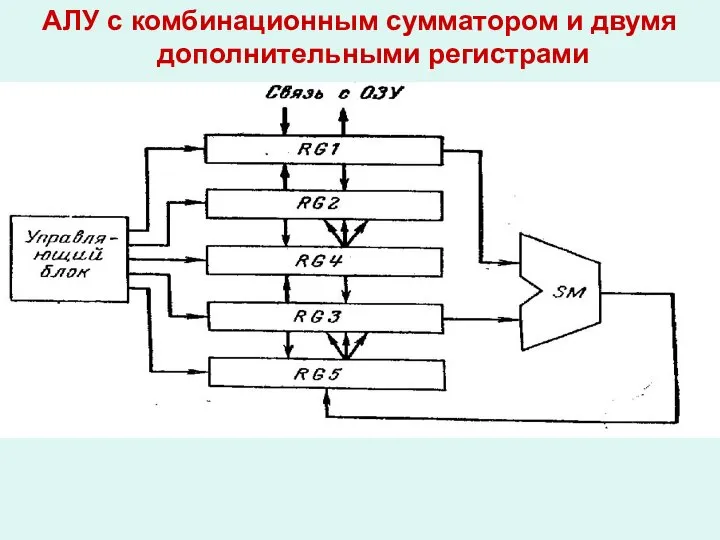

- 19. АЛУ с комбинационным сумматором и двумя дополнительными регистрами

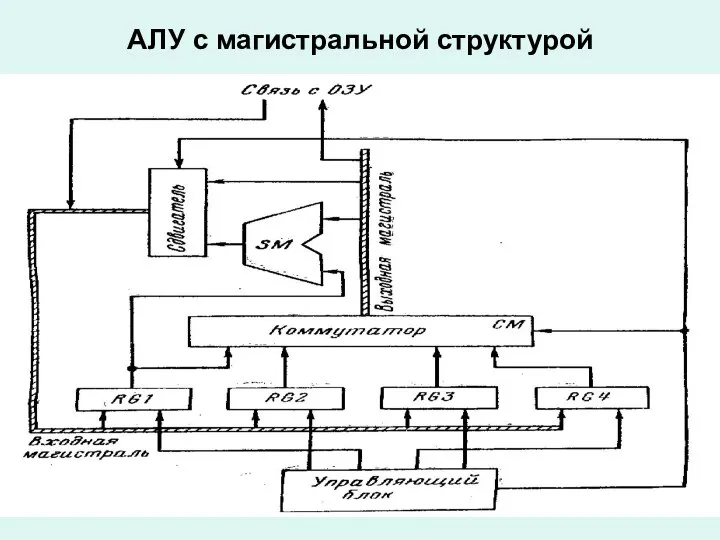

- 20. АЛУ с магистральной структурой

- 21. Алгоритмы сложения (вычитания) и умножения Структурная схема микропрограммы сложения

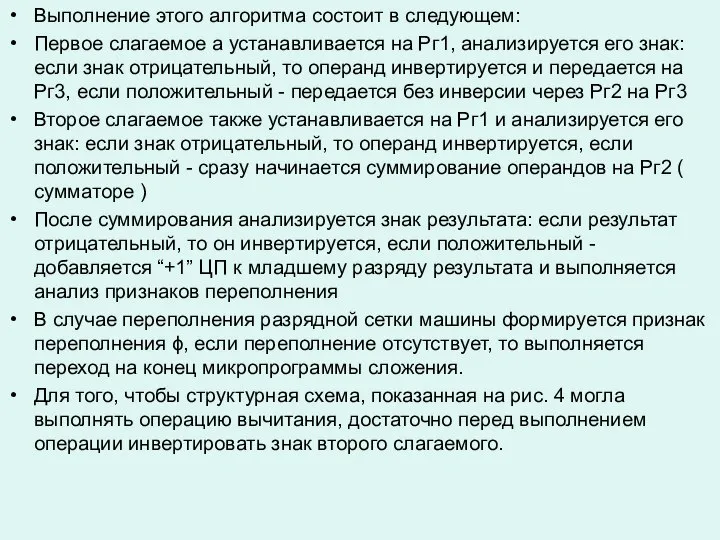

- 22. Выполнение этого алгоритма состоит в следующем: Первое слагаемое а устанавливается на Рг1, анализируется его знак: если

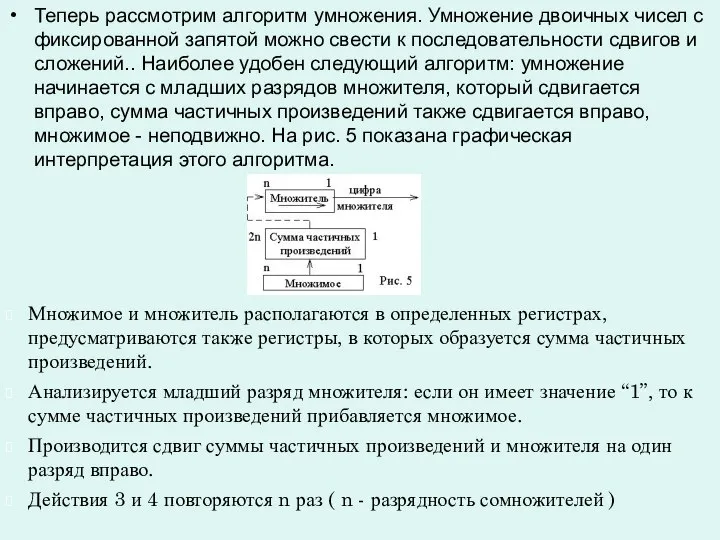

- 23. Теперь рассмотрим алгоритм умножения. Умножение двоичных чисел с фиксированной запятой можно свести к последовательности сдвигов и

- 24. Структурная схема микропрограммы умножения

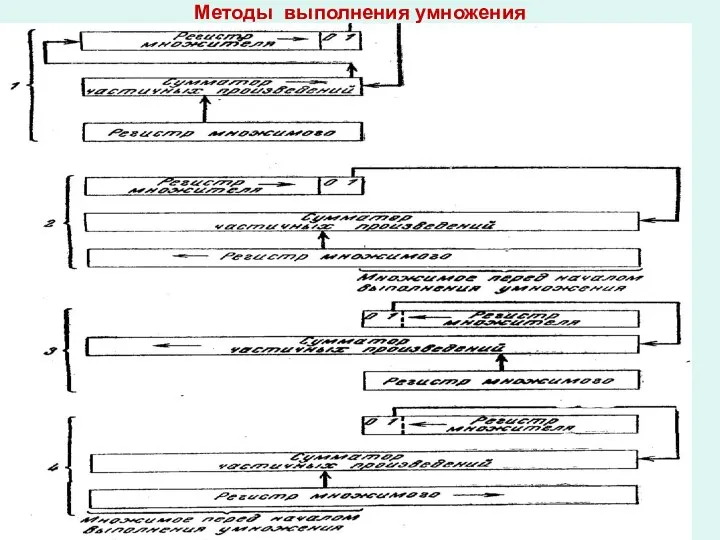

- 25. Методы выполнения умножения

- 26. Умножение в вычислительной машине обычно сводится к последовательности операций прибавления множимого к сумме уже ранее вычисленных

- 27. Схема деления с восстановлением остатка Перед началом выполнения деления делимое находится в сумматоре, а делитель –

- 28. Обобщенная структурная схема АЛУ

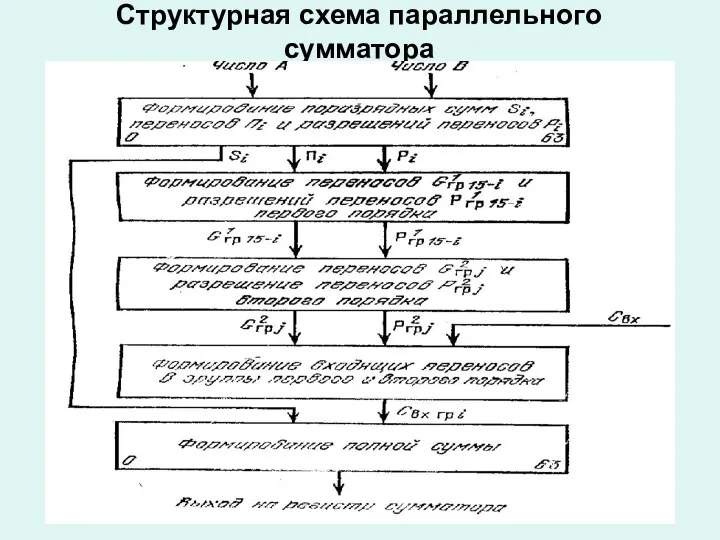

- 29. Структурная схема параллельного сумматора

- 30. Логическая схема 16-разрядного сумматора с параллельно- последовательным переносом

- 31. Функциональная схема седьмого разряда входного регистра АЛУ

- 32. Функциональные схемы работы DV-триггеров

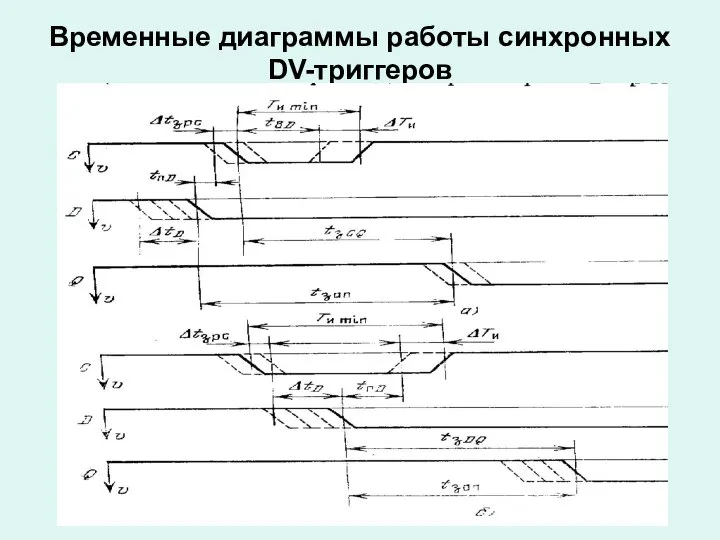

- 33. Временные диаграммы работы синхронных DV-триггеров

- 35. Арифметико-логическое устройство Общие сведения, функции и классификация Выполнили: cтуденты группы ИС-1-07 Гринкевич Я.В. Мандрыкин Д.А. Киселев

- 36. АЛУ реализует важную часть процесса обработки данных. Она заключается в выполнении набора простых операций. Операции АЛУ

- 37. Подробная классификация АЛУ

- 38. АЛУ состоит из регистров, сумматора с соответствующими логическими схемами и элемента управления выполняемым процессом. Устройство работает

- 39. В состав АЛУ входят регистры Рг1 - Рг7, в которых обрабатывается информация , поступающая из оперативной

- 40. Рг1 - сумматор (или сумматоры) - основной регистр АЛУ, в котором образуется результат вычислений; Рг2, РгЗ

- 41. Алгоритмы сложения (вычитания) и умножения Структурная схема микропрограммы сложения

- 42. Выполнение этого алгоритма состоит в следующем: Первое слагаемое а устанавливается на Рг1, анализируется его знак: если

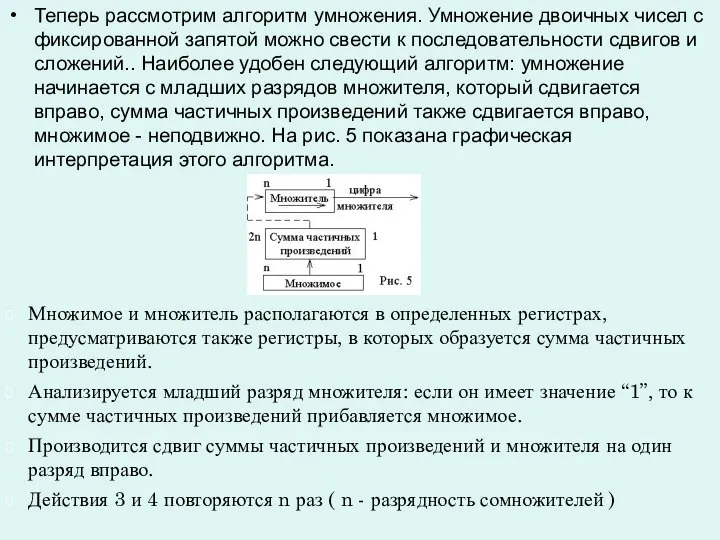

- 43. Теперь рассмотрим алгоритм умножения. Умножение двоичных чисел с фиксированной запятой можно свести к последовательности сдвигов и

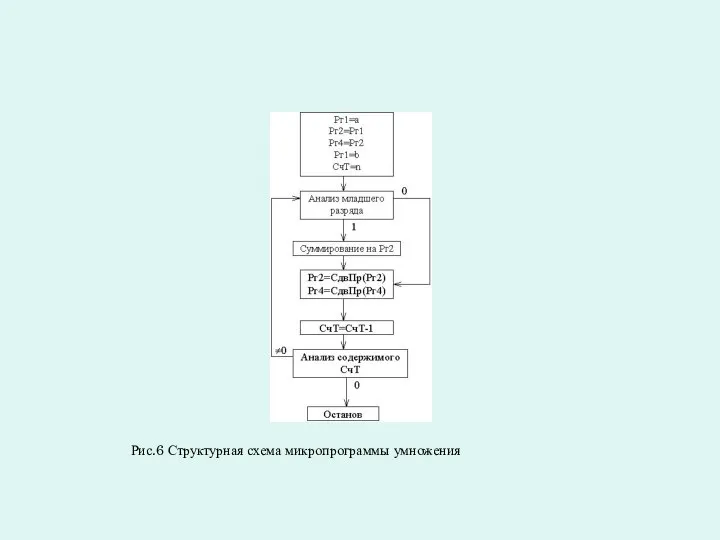

- 44. Рис.6 Структурная схема микропрограммы умножения

- 46. Скачать презентацию

Техническое обслуживание рулевого управления ВАЗ 2112, ремонт ГУР

Техническое обслуживание рулевого управления ВАЗ 2112, ремонт ГУР Понятие и механизм правотворчества

Понятие и механизм правотворчества Доходы и расходы семьи. Стоимость жизни.

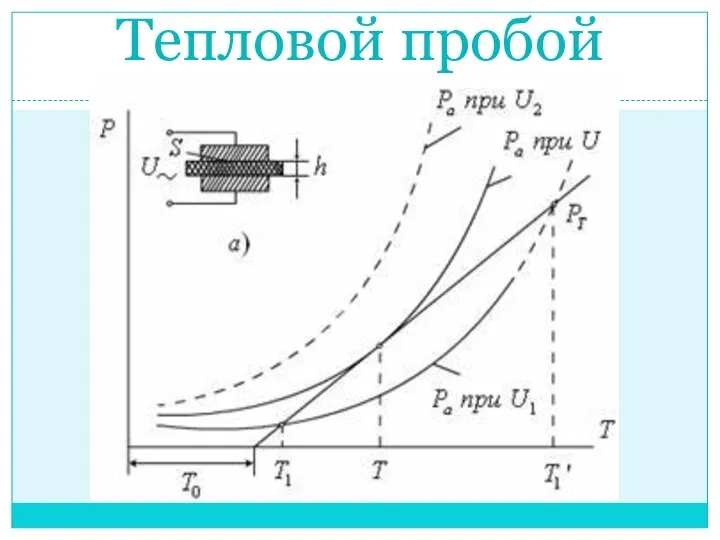

Доходы и расходы семьи. Стоимость жизни.  Пробой диэлектриков

Пробой диэлектриков  Жамбыл деген жәй атым,Халық менің шын атым

Жамбыл деген жәй атым,Халық менің шын атым  Ми-маленькі українці. Тренажер з читання - презентация для начальной школы_

Ми-маленькі українці. Тренажер з читання - презентация для начальной школы_ Структура правовой системы

Структура правовой системы Основы электричества и электротехники. Часть I

Основы электричества и электротехники. Часть I Атымский древодел

Атымский древодел «Аналитическая деятельность учителя: содержание, результаты, пути совершенствования» Декабрь 2010 года Подготовила: зам.директо

«Аналитическая деятельность учителя: содержание, результаты, пути совершенствования» Декабрь 2010 года Подготовила: зам.директо Стратегия развития муниципальной системы образования Сургута до 2020 года

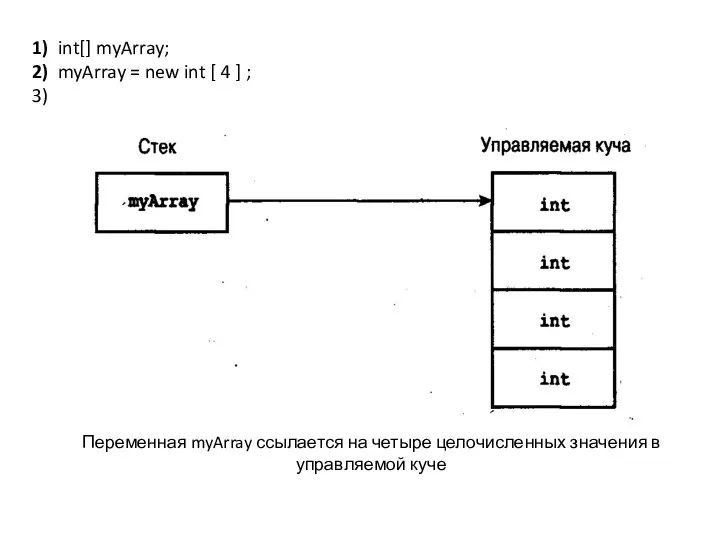

Стратегия развития муниципальной системы образования Сургута до 2020 года Массивы и кортежи

Массивы и кортежи Религиозные ценности и свобода совести

Религиозные ценности и свобода совести Сертификация квалификаций выпускников Самарской области

Сертификация квалификаций выпускников Самарской области  Презентация "Страны в мировой экономике. Часть 1" - скачать презентации по Экономике

Презентация "Страны в мировой экономике. Часть 1" - скачать презентации по Экономике Расчет радиовещательного приемника первого класса

Расчет радиовещательного приемника первого класса Ферменты-5

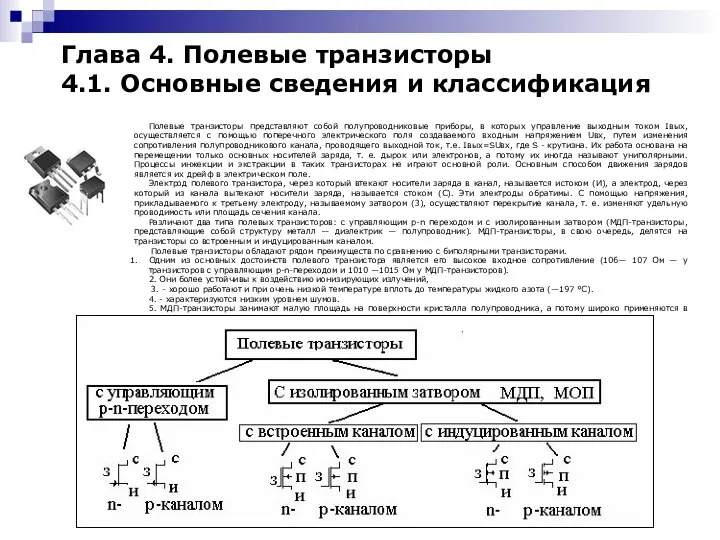

Ферменты-5 Полевые транзисторы. Основные сведения и классификация

Полевые транзисторы. Основные сведения и классификация «Защита прав участников рынка: как обезопасить себя и своих клиентов » Докладчик: Валентина Нагиева, Генеральный директор компан

«Защита прав участников рынка: как обезопасить себя и своих клиентов » Докладчик: Валентина Нагиева, Генеральный директор компан ООП. Наследование

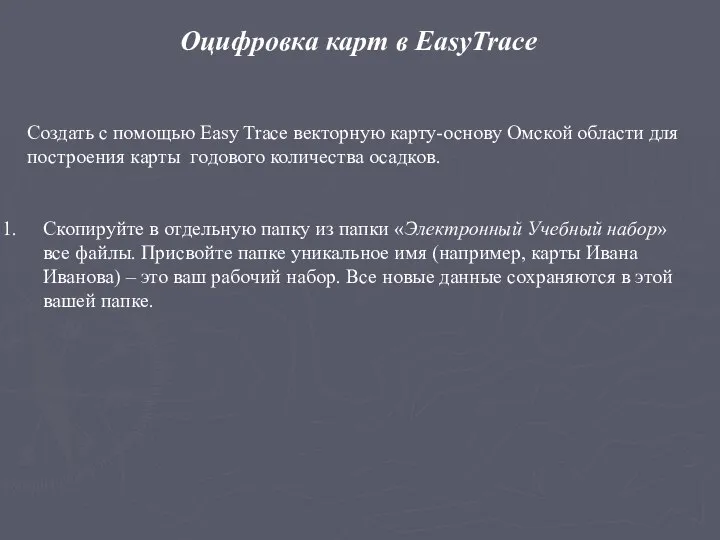

ООП. Наследование Easy Trace

Easy Trace  Определение угловой скорости маховика

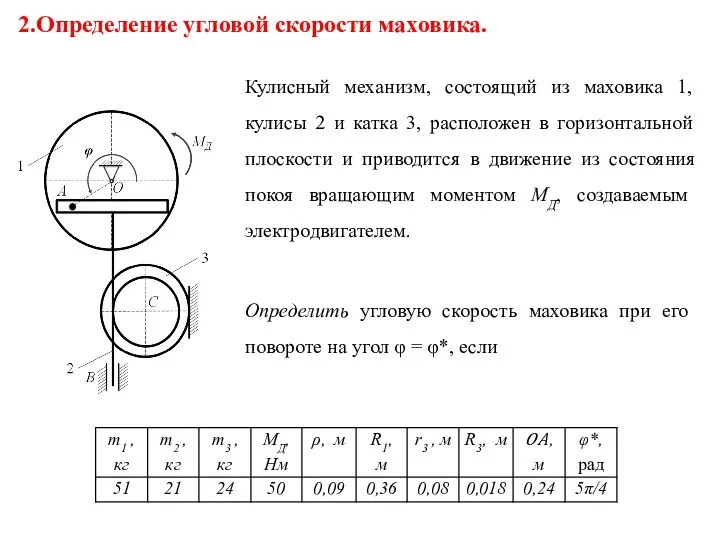

Определение угловой скорости маховика ОДНОПУТНАЯ АВТОБЛОКИРОВКА

ОДНОПУТНАЯ АВТОБЛОКИРОВКА ЛИТЕРАТУРНОЕ ЧТЕНИЕ 2 КЛАСС Обобщающий урок по разделу «Сказочные человечки»

ЛИТЕРАТУРНОЕ ЧТЕНИЕ 2 КЛАСС Обобщающий урок по разделу «Сказочные человечки» Средства для работы в Защ реж

Средства для работы в Защ реж М.М. Поташник, М.В. Левит Презентацию выполнила Н.П.Мастюгина, заместитель директора по УВР

М.М. Поташник, М.В. Левит Презентацию выполнила Н.П.Мастюгина, заместитель директора по УВР Оказание первой помощи при поражении промышленным и бытовым током. (Тема 7)

Оказание первой помощи при поражении промышленным и бытовым током. (Тема 7) Ropes или веревочное дерево

Ropes или веревочное дерево