Содержание

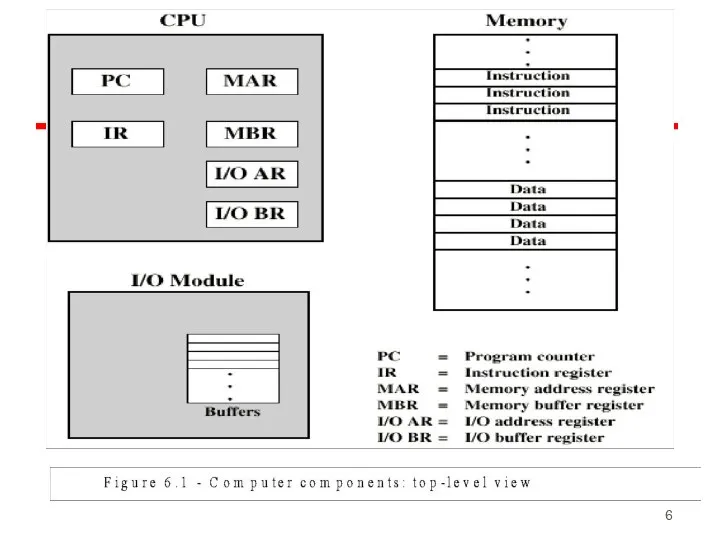

- 2. КОМПОНЕНТЫ КОМПЬЮТЕРА На верхнем уровне компьютер состоит из центрального процессора (CPU), памяти и устройств ввода -

- 3. Концепция фон Неймана Практически все современные компьютеры следуют концепции, выработанной фон Нейманом. Эта концепция включает три

- 4. Концепция фон Неймана - к отдельным элементам данных, хранящимся в памяти, можно обращаться по адресу, характеризующему

- 5. Базовые компоненты компьютера Существует небольшой набор базовых логических элементов, комбинируя которые разными способами, можно создавать средства

- 7. Центральный процессор ЦП должен обмениваться с памятью данными и извлекать из нее команды программы Для этого

- 8. Центральный процессор - БРгП буферный регистр памяти (MBR), который служит для временного хранения данных, записываемых в

- 9. Центральный процессор РгА В/В регистр адреса внешнего устройства (I/O AR) служит для хранения адреса устройства ввода-вывода

- 10. Устройство оперативной памяти Содержит множество ячеек Каждая ячейка имеет свой числовой идентификатор - адрес В каждой

- 11. Модуль ввода-вывода Передает данные от внешнего устройства в ЦП или в память и обратно В состав

- 12. Выполнение программы Выполнение последовательности элементарных шагов Каждый шаг - это выполнение арифметической, логической операции или операции

- 13. Выполнение программы Каждая команда имеет уникальный код например Add, Move и т.д. Аппаратный сегмент принимает код

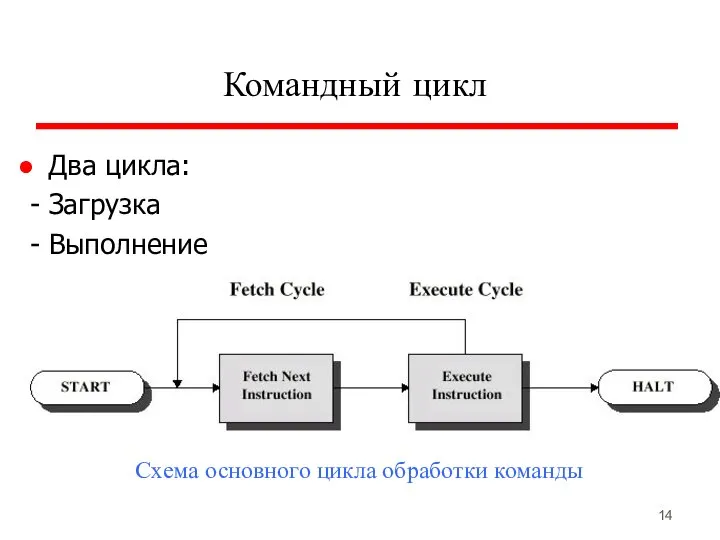

- 14. Командный цикл Два цикла: - Загрузка - Выполнение Схема основного цикла обработки команды

- 15. Цикл загрузки Программный счетчик (PC) содержит адрес следующей команды Процессор загружает команду из памяти по адресу,

- 16. Цикл выполнения Процессор распознает команду и выполняет необходимые действия Часть битов кода команды представляет собой код

- 17. Цикл выполнения Процессор - память Данные перемещаются между ЦП и памятью Процессор – модуль ввода/вывода Данные

- 18. Цикл выполнения Обработка данных Процессор выполняет заданную арифметическую или логическую операцию над данными Управление Изменение естественной

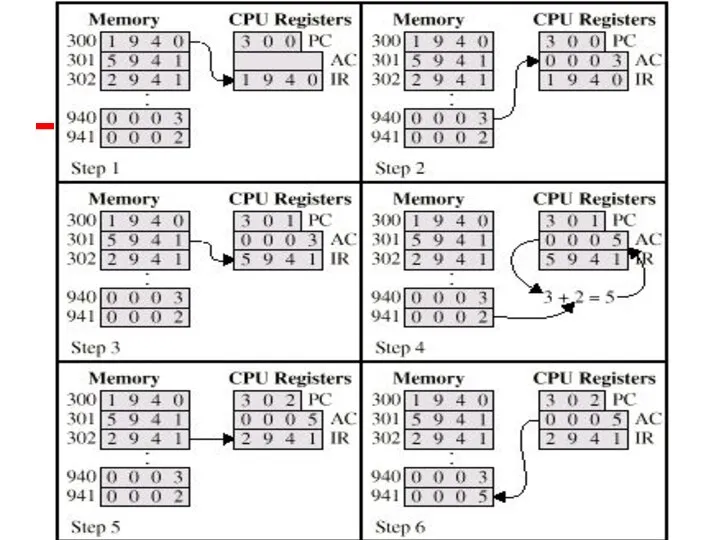

- 19. Постановка задачи Выполнить пошаговое сложение кодов двух чисел 3 и 2, расположенных в ячейках 940 и

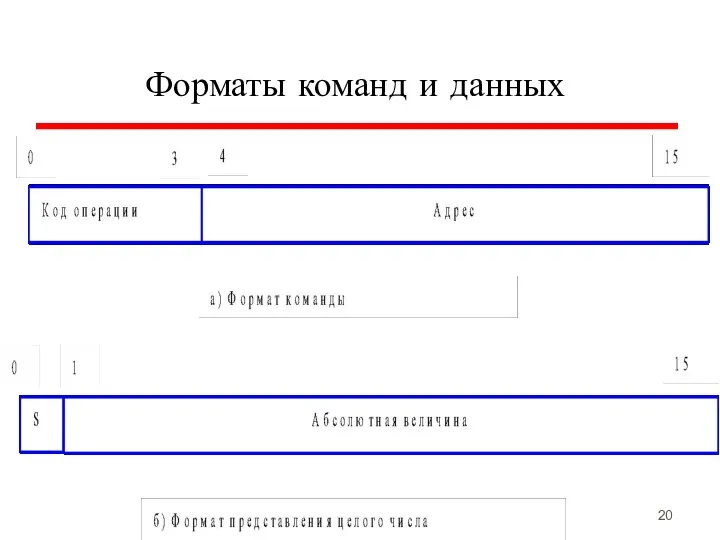

- 20. Форматы команд и данных

- 21. Форматы команд и данных Как команды, так и данные представлены 16-разрядными словами Формат команды позволяет представить

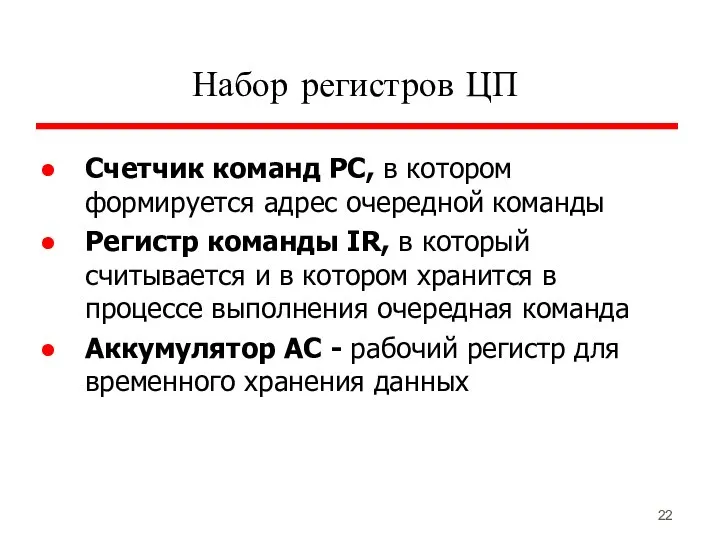

- 22. Набор регистров ЦП Счетчик команд PC, в котором формируется адрес очередной команды Регистр команды IR, в

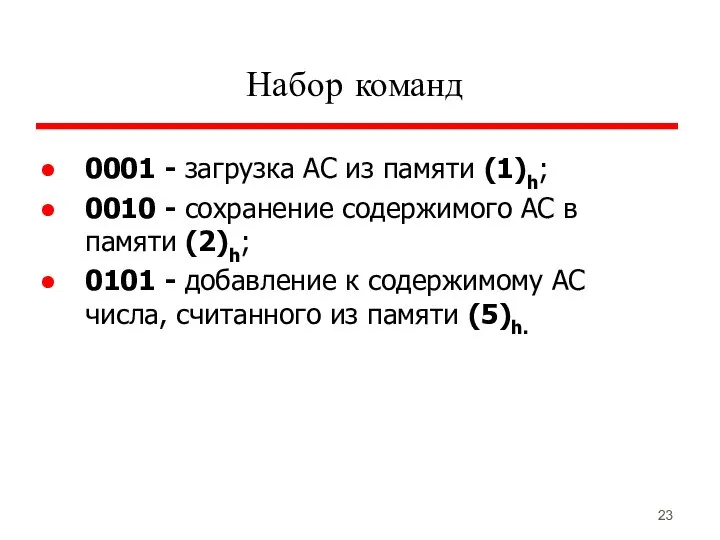

- 23. Набор команд 0001 - загрузка АС из памяти (1)h; 0010 - сохранение содержимого АС в памяти

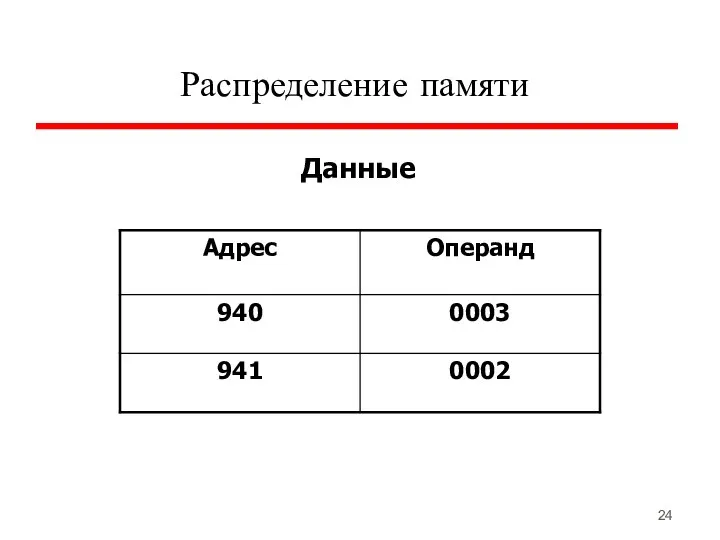

- 24. Распределение памяти Данные

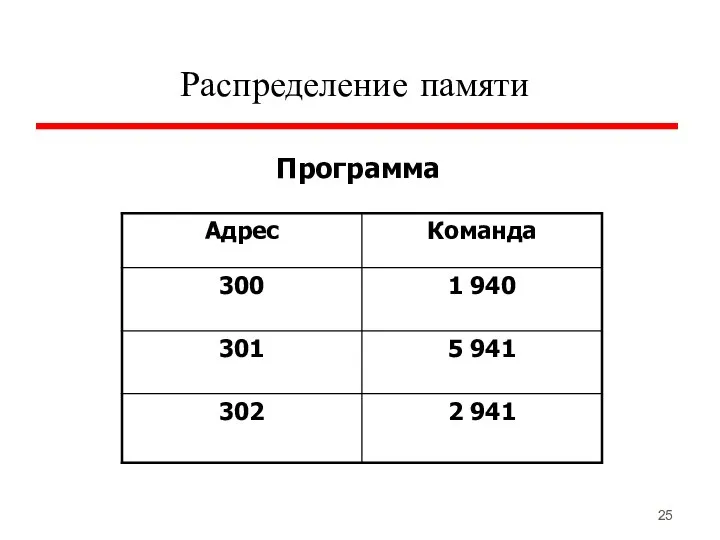

- 25. Распределение памяти Программа

- 27. Пошаговое выполнение команд 1 В счетчике команд PC содержится число 300 — адрес первой команды фрагмента

- 28. Пошаговое выполнение команд 2 Первые 4 разряда в IR — код операции — указывают ЦП, что

- 29. Пошаговое выполнение команд 4 Первые 4 разряда новой команды задают сложение содержимого АС с числом, считанным

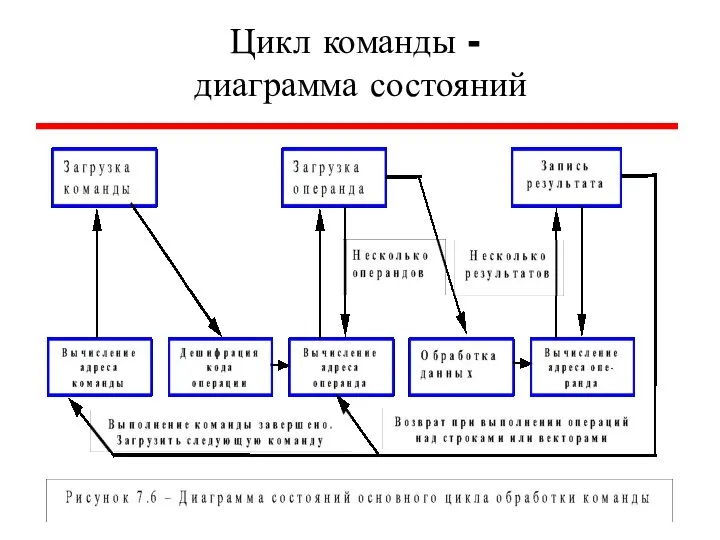

- 30. Цикл команды - диаграмма состояний

- 31. Этапы диаграммы состояний Вычисление адреса команды При естественном порядке выполнения команд программы адрес следующей команды образуется

- 32. Вычисления адреса команды Если же оперативная память организована таким образом, что адресуемой единицей данных является 8-разрядный

- 33. Этапы диаграммы состояний Загрузка команды Считывание команды из ячейки памяти по адресу, заданному в PC, в

- 34. Этапы диаграммы состояний Вычисление адреса операнда Если в операции используются операнды, хранящиеся в памяти или передаваемые

- 36. Скачать презентацию

Кодирование Информации

Кодирование Информации  Системы здравоохранения в различных странах мира Системы здравоохранения в различных странах мира Манерова Ольга Александ

Системы здравоохранения в различных странах мира Системы здравоохранения в различных странах мира Манерова Ольга Александ МЕТОДИЧЕСКАЯ ТЕМА: «АКТИВИЗАЦИЯ ПОЗНАВАТЕЛЬНОЙ ДЕЯТЕЛЬНОСТИ УЧАЩИХСЯ НА УРОКАХ ПУТЕМ ИСПОЛЬЗОВАНИЯ НОВЫХ ПЕДАГОГИЧЕСКИХ ТЕХН

МЕТОДИЧЕСКАЯ ТЕМА: «АКТИВИЗАЦИЯ ПОЗНАВАТЕЛЬНОЙ ДЕЯТЕЛЬНОСТИ УЧАЩИХСЯ НА УРОКАХ ПУТЕМ ИСПОЛЬЗОВАНИЯ НОВЫХ ПЕДАГОГИЧЕСКИХ ТЕХН Научно-технические методы стандартизации. (Лекция 8)

Научно-технические методы стандартизации. (Лекция 8) Иррациональные уравнения Урок алгебры и начал анализа 11 класс Учитель: Вязовченко Н.К.

Иррациональные уравнения Урок алгебры и начал анализа 11 класс Учитель: Вязовченко Н.К.  НАНЕСЕНИЕ РАЗМЕРОВ

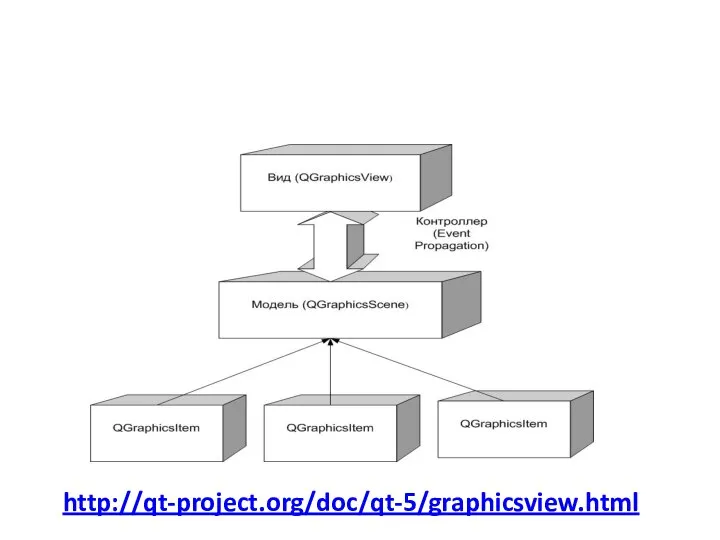

НАНЕСЕНИЕ РАЗМЕРОВ Программирование графики с помощью Graphics View Framework

Программирование графики с помощью Graphics View Framework Патология обмена белков

Патология обмена белков  Под Рождественской звездой

Под Рождественской звездой Население. Безработица. Гендерный баланс.

Население. Безработица. Гендерный баланс. Презентация Судебное разбирательство между ЗАО «ЛОНМАДИ» и Центральной акцизной таможней России

Презентация Судебное разбирательство между ЗАО «ЛОНМАДИ» и Центральной акцизной таможней России  1 октября 2011 - Project Management Camp «30 советов по управлению маркетинговыми услугами»

1 октября 2011 - Project Management Camp «30 советов по управлению маркетинговыми услугами»  формирования социального государства в россии Петрова М.А Курчина М.С.

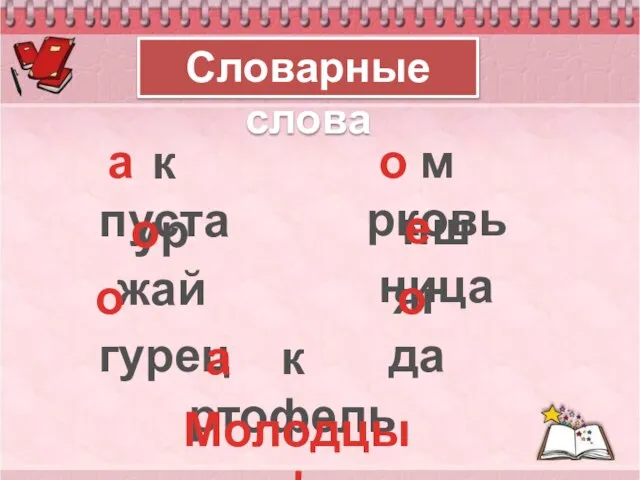

формирования социального государства в россии Петрова М.А Курчина М.С. Словарные слова, 3 класс - презентация для начальной школы

Словарные слова, 3 класс - презентация для начальной школы Развитие Тамбовской области Нечаева А. Юрлова В.

Развитие Тамбовской области Нечаева А. Юрлова В. Анатомо-физиологическая основа ВНД Строение и функции НС

Анатомо-физиологическая основа ВНД Строение и функции НС Pure Auto

Pure Auto Выпускная квалификационная работа: Оптимизация параметров технико-технологической безопасности организации

Выпускная квалификационная работа: Оптимизация параметров технико-технологической безопасности организации Теория стационарных возмущений

Теория стационарных возмущений  Локальные компьютерные сети. Адаптер. Виды адаптеров. Топология сети

Локальные компьютерные сети. Адаптер. Виды адаптеров. Топология сети Современный культурный процесс (тема 1)

Современный культурный процесс (тема 1) Презентация Государственный флаг РФ

Презентация Государственный флаг РФ Физические приборы

Физические приборы Презентация Договор ренты

Презентация Договор ренты Элементная база электронных устройств

Элементная база электронных устройств Организационное собрание Подготовка выпускной квалификационной работы

Организационное собрание Подготовка выпускной квалификационной работы Новый год в Армении

Новый год в Армении Нагрузка и восстановление в спорте. Стресс и релакс

Нагрузка и восстановление в спорте. Стресс и релакс