Содержание

- 2. To be covered today: Quick overview of the architectures of the both the Blackfin and Sharc

- 3. Sharc ADSP-21061[1]

- 4. Sharc’s Main Features[2]: 32/40-bit IEEE floating-point math 32-bit fixed-point MACs with 64-bit product and 80-bit accumulation

- 5. Sharc’s Main Features Cont.: Six nested levels of zero-overhead looping in hardware Four busses to memory

- 6. Blackfin ADSP-21535[3]

- 7. Blackfin’s Main Features[4]: Two 16-bit MACs, two 40-bit ALUs, and four 8-bit Video ALUs Support for

- 8. Blackfin’s Main Features Cont.: Possibility of the following parallel operations processed in one clock cycle Execution

- 9. Main Differences: The Blackfin is only a 16-bit integer processor, however can operate on 32-bit data

- 10. Main Differences Cont.: The Blackfin has 4 address registers (with corresponding base, length, and modify) to

- 11. Blackfin FIR Code Sample[5]: LSETUP(E_FIR_START,E_FIR_END) LC0=P1>>1; //Loop 1 to Ni/2 E_FIR_START: R1=PACK(R1.H,R0.H) || [I0++]=R0 || R2.L=W[I2++];

- 12. Benchmarks: For the Sharc[6] For the Blackfin[7]

- 13. Analysis: Blackfin is faster for the three algorithms Unsure of exact performance gain on the FFT

- 14. References ENCM515 Lecture Slides for January 11, 2002, [http://www.enel.ucalgary.ca/People/Smith/2002webs/encm515_02/02presentations/02january/02overviewSHARCarchitecture.ppt], Dr. Mike Smith Sharc Architecture Overview, [http://www.analog.com/technology/dsp/Sharc/architecture.html],

- 16. Скачать презентацию

![Sharc ADSP-21061[1]](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1475255/slide-2.jpg)

![Sharc’s Main Features[2]: 32/40-bit IEEE floating-point math 32-bit fixed-point MACs with](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1475255/slide-3.jpg)

![Blackfin ADSP-21535[3]](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1475255/slide-5.jpg)

![Blackfin’s Main Features[4]: Two 16-bit MACs, two 40-bit ALUs, and four](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1475255/slide-6.jpg)

![Blackfin FIR Code Sample[5]: LSETUP(E_FIR_START,E_FIR_END) LC0=P1>>1; //Loop 1 to Ni/2 E_FIR_START:](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1475255/slide-10.jpg)

![Benchmarks: For the Sharc[6] For the Blackfin[7]](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1475255/slide-11.jpg)

![References ENCM515 Lecture Slides for January 11, 2002, [http://www.enel.ucalgary.ca/People/Smith/2002webs/encm515_02/02presentations/02january/02overviewSHARCarchitecture.ppt], Dr. Mike](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1475255/slide-13.jpg)

Дополнительное обследование почек

Дополнительное обследование почек Презентация Факторы производства

Презентация Факторы производства  Стили поведения Левина. Стили управления Лайкерта. Управленческая сетка Блейка и Моутон Выполнила: Жукова Юлия

Стили поведения Левина. Стили управления Лайкерта. Управленческая сетка Блейка и Моутон Выполнила: Жукова Юлия Мировые политические процессы в эпоху позднего модерна

Мировые политические процессы в эпоху позднего модерна Презентация Предпосылки возникновения философии в Древней Греции

Презентация Предпосылки возникновения философии в Древней Греции Символічне значення одягу священнослужителів. Символіка кольорів

Символічне значення одягу священнослужителів. Символіка кольорів ВИТАМИНЫ

ВИТАМИНЫ План для свай

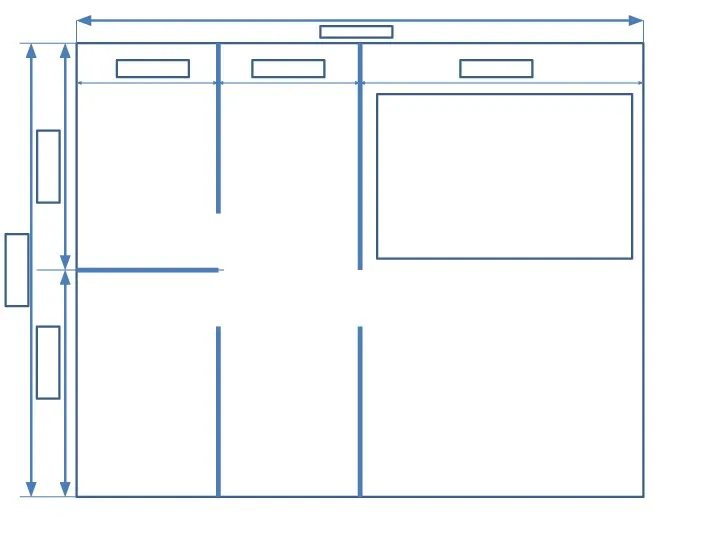

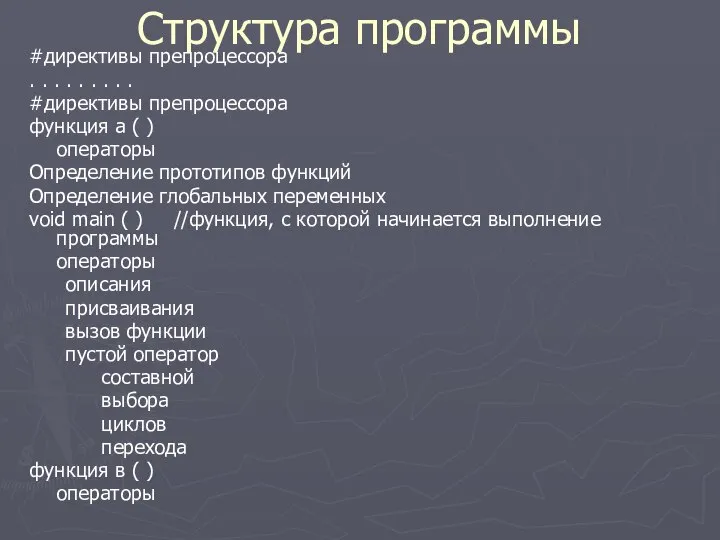

План для свай Структура программы

Структура программы Магазин 5 Элемент

Магазин 5 Элемент Итальянский стиль садов

Итальянский стиль садов Осциллографы. Методы и средства измерения параметров электрических цепей

Осциллографы. Методы и средства измерения параметров электрических цепей . экономика и политика

. экономика и политика Методы экспертных оценок в стратегическом государственном управлении

Методы экспертных оценок в стратегическом государственном управлении Базові засоби розробки і оформлення програм на мові Pascal

Базові засоби розробки і оформлення програм на мові Pascal Человек в зеркале искусства: жанр портрета

Человек в зеркале искусства: жанр портрета Выбор расположения клиентской точки Wi Fi для лучшего покрытия сети

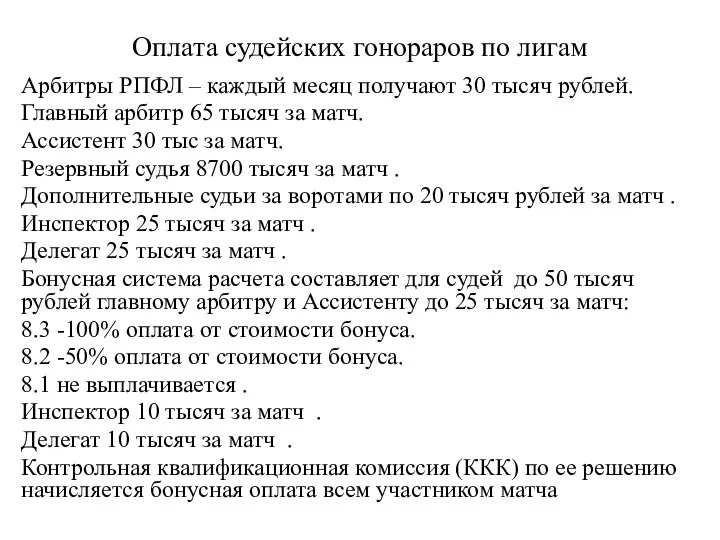

Выбор расположения клиентской точки Wi Fi для лучшего покрытия сети Оплата судейских гонораров по лигам. Арбитры по мини-футболу

Оплата судейских гонораров по лигам. Арбитры по мини-футболу Система «производство кабеля

Система «производство кабеля Графический материал к отчету по учебной практике

Графический материал к отчету по учебной практике TStringGrid

TStringGrid Страховка. Виды страховки

Страховка. Виды страховки Жүсіпбек Аймауытов «Ақбілек». Романы

Жүсіпбек Аймауытов «Ақбілек». Романы Самым дорогим посвящается…

Самым дорогим посвящается… Схемы. Виды схем. (Лекция 8)

Схемы. Виды схем. (Лекция 8) Пасха. День 6. Для малышей. Возраст 2-5 лет

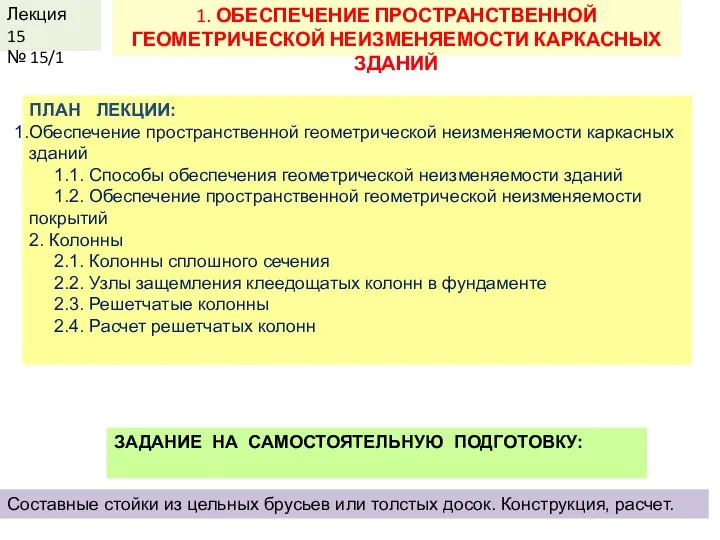

Пасха. День 6. Для малышей. Возраст 2-5 лет Обеспечение пространственной геометрической неизменяемости каркасных зданий

Обеспечение пространственной геометрической неизменяемости каркасных зданий Анализ и оценка финансовых показателей деят-ти сбер банка Выполнили студентки 2-го курса Экономического факультета Петрова М

Анализ и оценка финансовых показателей деят-ти сбер банка Выполнили студентки 2-го курса Экономического факультета Петрова М