Содержание

- 2. IDEA. Начало IDEA - (англ. International Data Encryption Algorithm, международный алгоритм шифрования данных) — симметричный блочный

- 3. IDEA. Введение Будут приведены дизайны в двух архитектурах bit-parallel(параллельно-двоичная) и bit-serial(последовательно-двоичная) их отличие заключается в способе

- 4. IDEA. Проблемс? Хоть алгоритм и включает в себя только 16ти битные операции, его программные реализации до

- 5. IDEA. Решение Проблемы со скоростью решаются аппаратной реализацией алгоритма и использования распараллеливания между операторами. В совокупности

- 6. IDEA. Решение Леонг, 500 Мб/сек. с последовательной реализацией алгоритма IDEA на Xilinx Virtex XCV300-6 FPGA, который

- 7. IDEA. Идея Блок шифрования содержит нисходящую структуру из 8 идентичных блоков, называемых раундами, сопровождающимися полураундом или

- 8. IDEA. Идея IDEA позиционируется, как крипоустойчивый алгоритм потому что: В нём заложены примитивные операции трёх отдельных

- 9. IDEA. Алгоритм. Обзор алгоритма Процесс шифрования: 64 битный текст делится на 4 подблока( X1, …, X4

- 10. IDEA. Алгоритм. Получение ключей. Шифрование Процесс вычисления ключей(подключей) для шифрования (key-schedule): Упорядочим 52 подключа таким образом:

- 11. IDEA. Алгоритм. Получение ключей. Расшифрование Процесс вычисления ключей(подключей) для расшифрования иллюстрирует следующая таблица: Zi(r)-1 * Zi(r)

- 12. IDEA. Алгоритм. Шифрование Процесс превращения текста в криптограммы. Один раунд: Y1(1) = X1, …, Y4(1) =

- 13. IDEA. Алгоритм. Шифрование Процесс превращения текста в криптограммы. Последний(9ый) раунд: Y1(9) = Y1(9) * Z1(9) Y2(9)

- 14. Bit-parallel. Параллельно-двоичная архитектура Умножение по модулю 216 + 1 — это камень преткновения этого алгоритма. В

- 15. Bit-parallel. Параллельно-двоичная архитектура. Оператор умножение по модулю 216 + 1 В этом алгоритме передаются два аргумента

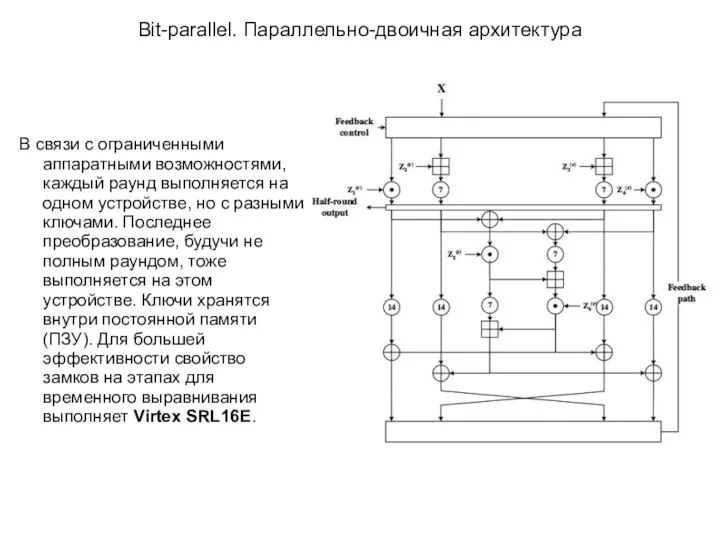

- 16. Bit-parallel. Параллельно-двоичная архитектура В связи с ограниченными аппаратными возможностями, каждый раунд выполняется на одном устройстве, но

- 17. Bit-parallel. Параллельно-двоичная архитектура В одном раунде используется 3 умножения по модулю с задержкой в 7 циклов,

- 18. Bit-serial. Последовательно-двоичная архитектура Представленная здесь модель, это слегонца улучшенная реализация классической модели путём перемещения и копирования

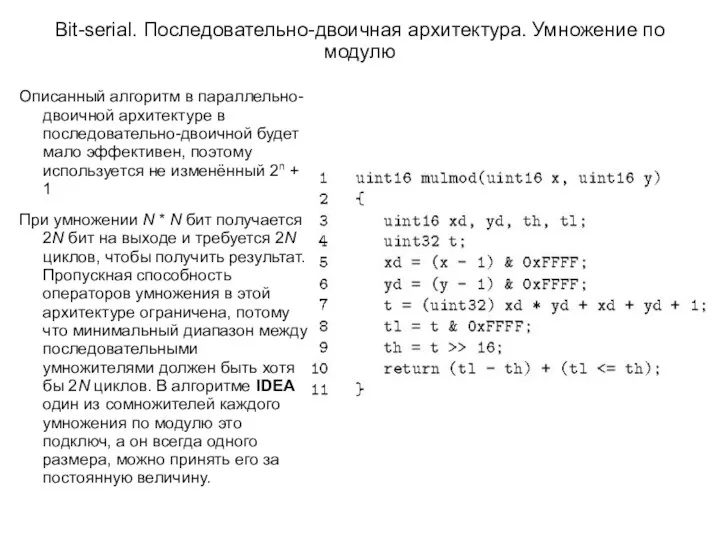

- 19. Bit-serial. Последовательно-двоичная архитектура. Умножение по модулю Описанный алгоритм в параллельно-двоичной архитектуре в последовательно-двоичной будет мало эффективен,

- 20. Bit-serial. Последовательно-двоичная архитектура. Умножение по модулю Представим, что промежуточное значение t в умножении разделено на 2

- 21. Bit-serial. Последовательно-двоичная архитектура. Умножение по модулю Была разработана изменённая схема последовательного умножителя Лиона которая решила эту

- 22. Bit-serial. Последовательно-двоичная архитектура. Умножение по модулю Так как вектор был перенаправлен на одну из дорожек, логический

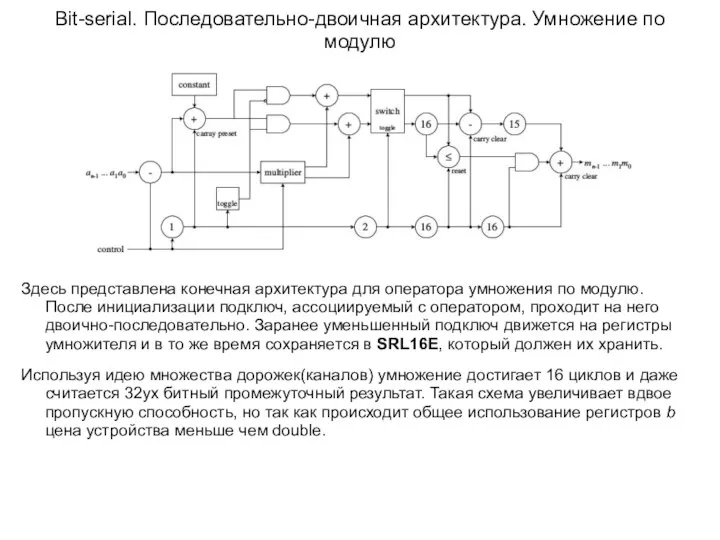

- 23. Bit-serial. Последовательно-двоичная архитектура. Умножение по модулю Здесь представлена конечная архитектура для оператора умножения по модулю. После

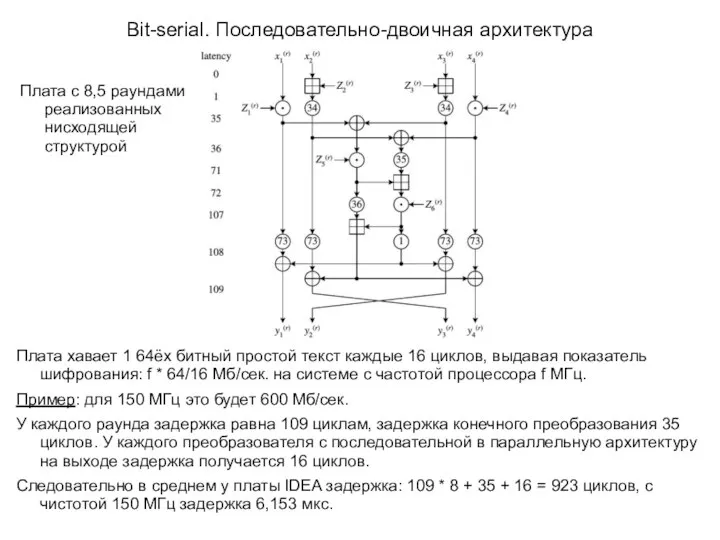

- 24. Bit-serial. Последовательно-двоичная архитектура Плата хавает 1 64ёх битный простой текст каждые 16 циклов, выдавая показатель шифрования:

- 25. Слабые ключи Существуют большие классы слабых ключей. Слабые они в том смысле, что существуют процедуры, позволяющие

- 26. Преимущества

- 27. Недостатки

- 28. hh Один из наиболее известных в мире криптологов Брюс Шнайер в своей книге «Прикладная криптография», 1996

- 29. Источники * https://google.ru

- 30. Источники * http://www.quadibloc.com/crypto/co040302.htm * http://htrd.su/wiki/_media/zhurnal/2012/03/23/todo_prikladnaja_kriptografija/cryptoshn.pdf * https://en.wikipedia.org/wiki/International_Data_Encryption_Algorithm * https://ru.wikipedia.org/wiki/IDEA * http://www.ti.com/lit/an/slyt264/slyt264.pdf * https://books.google.ru/books?id=UmUd3aIuk3IC&pg=SA2-PA17&lpg=SA2-PA17&dq=latency+n+cycles&source=bl&ots=TXbar0nRWX&sig=yAVhb1jN1nT1UnvHpwlRQVEdhhY&hl=ru&sa=X&ved=0ahUKEwjiuIaC6aPQAhVIhywKHXKmDT4Q6AEINDAD#v=onepage&q=latency%20n%20cycles&f=false

- 32. Скачать презентацию

Система энергообеспечения клетки

Система энергообеспечения клетки  Компьютер – исполнитель алгоритмов

Компьютер – исполнитель алгоритмов Эпигенетические процессы восстановительного глеевого ряда

Эпигенетические процессы восстановительного глеевого ряда Терапия острой и хронической печеночной недостаточности С.Б.Ляпустин 20.10.11.

Терапия острой и хронической печеночной недостаточности С.Б.Ляпустин 20.10.11.  Проект модернизации поста текущего ремонта, агрегатов для СТО

Проект модернизации поста текущего ремонта, агрегатов для СТО Καισάρεια Καππαδοκίας. τα Θεμέλια της Τριαδικότητας του Θεού

Καισάρεια Καππαδοκίας. τα Θεμέλια της Τριαδικότητας του Θεού Поляризация волн

Поляризация волн Динамика развития лоббистских технологий в России

Динамика развития лоббистских технологий в России Оборудование транспорта АТУ системой мониторинга транспорта

Оборудование транспорта АТУ системой мониторинга транспорта Обмен веществ и энергии

Обмен веществ и энергии отчет Лолита

отчет Лолита Центрально-растянутые элементы

Центрально-растянутые элементы Аналитическая машина

Аналитическая машина Презентация Северо-Западное таможенное управление

Презентация Северо-Западное таможенное управление Применение граната в абразивно-струйной очистке поверхности

Применение граната в абразивно-струйной очистке поверхности «Переменка». Разработка программного продукта в среде Delphi 7

«Переменка». Разработка программного продукта в среде Delphi 7 Диспансеризация и реабилитация терапевтических больных

Диспансеризация и реабилитация терапевтических больных РАСЧЁТ ТРЁХШАРНИРНЫХ СИСТЕМ

РАСЧЁТ ТРЁХШАРНИРНЫХ СИСТЕМ Проектирование систем автоматизации. Проектная компоновка УВК. (Модуль 5)

Проектирование систем автоматизации. Проектная компоновка УВК. (Модуль 5) ПЕЧАТНЫЕ КРАСКИ

ПЕЧАТНЫЕ КРАСКИ Вирусные гепатиты

Вирусные гепатиты  Иероглифы

Иероглифы Пунктограми при відокремлених другорядних членах речення

Пунктограми при відокремлених другорядних членах речення priroda_v_opasnosti1

priroda_v_opasnosti1 Строительные конструкции. Расчет прочности сжатых элементов. (Лекция 3)

Строительные конструкции. Расчет прочности сжатых элементов. (Лекция 3) Shisha bar

Shisha bar Презентация на тему "Связь универсальных учебных действий с учебными предметами" - скачать презентации по Педагогике

Презентация на тему "Связь универсальных учебных действий с учебными предметами" - скачать презентации по Педагогике Анализ программы и учебников Е.В.Чудиновой

Анализ программы и учебников Е.В.Чудиновой