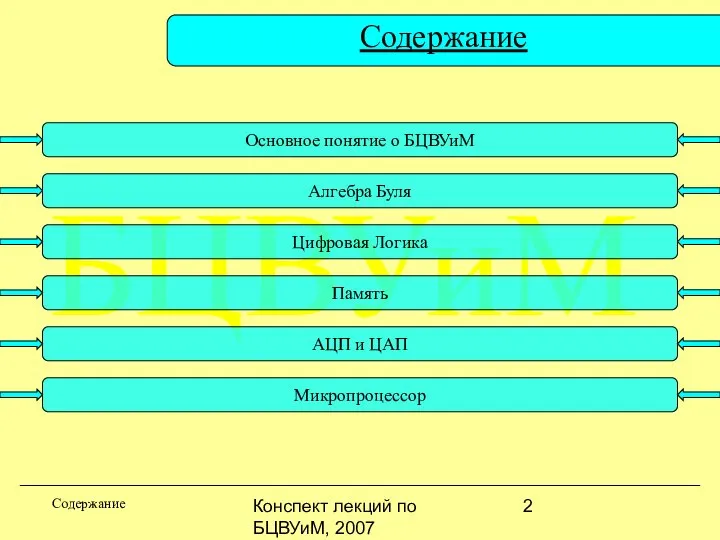

Содержание

- 2. Конспект лекций по БЦВУиМ, 2007 БЦВУиМ Содержание Содержание Основное понятие о БЦВУиМ Алгебра Буля Цифровая Логика

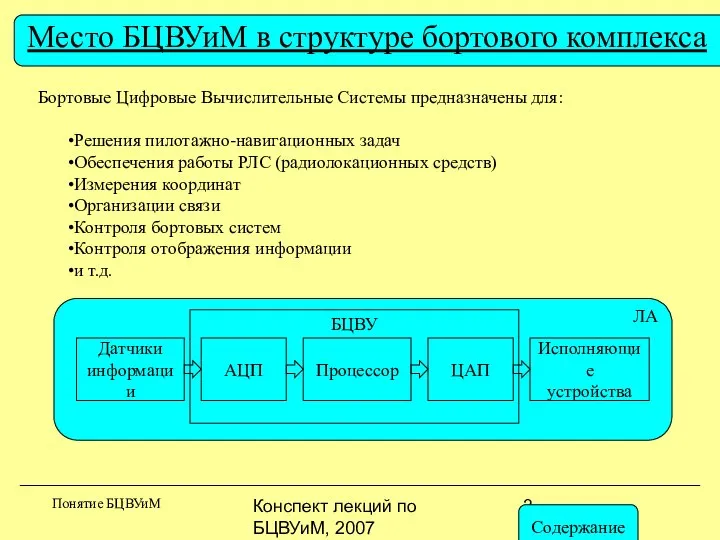

- 3. Конспект лекций по БЦВУиМ, 2007 Место БЦВУиМ в структуре бортового комплекса Понятие БЦВУиМ ЛА Бортовые Цифровые

- 4. Конспект лекций по БЦВУиМ, 2007 Особенности работы БЦВУиМ Понятие БЦВУиМ 3. Работа в реальном масштабе времени

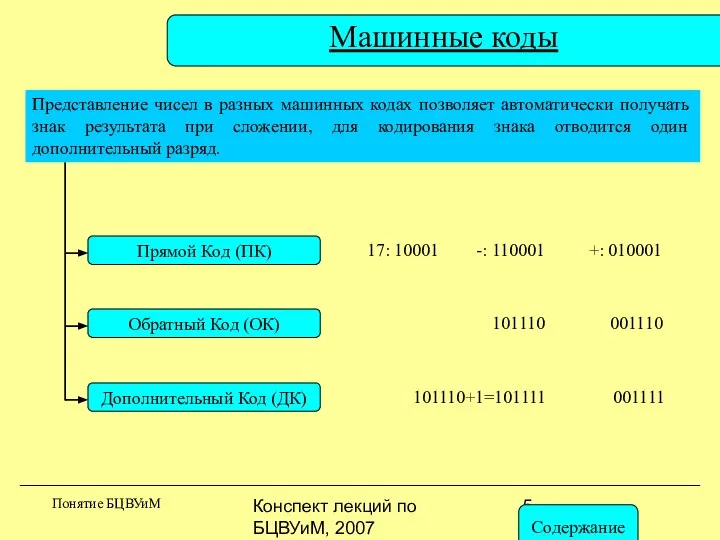

- 5. Конспект лекций по БЦВУиМ, 2007 Машинные коды Понятие БЦВУиМ Прямой Код (ПК) Обратный Код (ОК) Дополнительный

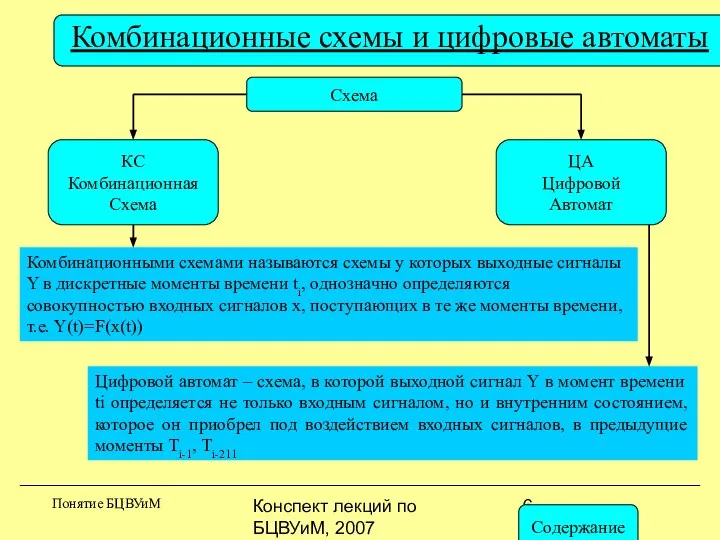

- 6. Конспект лекций по БЦВУиМ, 2007 Комбинационные схемы и цифровые автоматы Понятие БЦВУиМ Схема КС Комбинационная Схема

- 7. Конспект лекций по БЦВУиМ, 2007 БЦВУиМ Содержание: Алгебра Буля Алгебра Буля Аксиомы Законы Схема «И» Схема

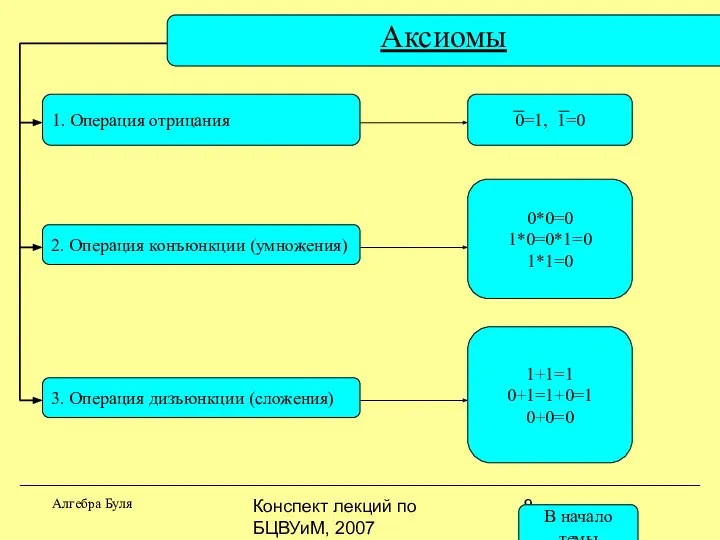

- 8. Конспект лекций по БЦВУиМ, 2007 Аксиомы Алгебра Буля 1. Операция отрицания 2. Операция конъюнкции (умножения) 3.

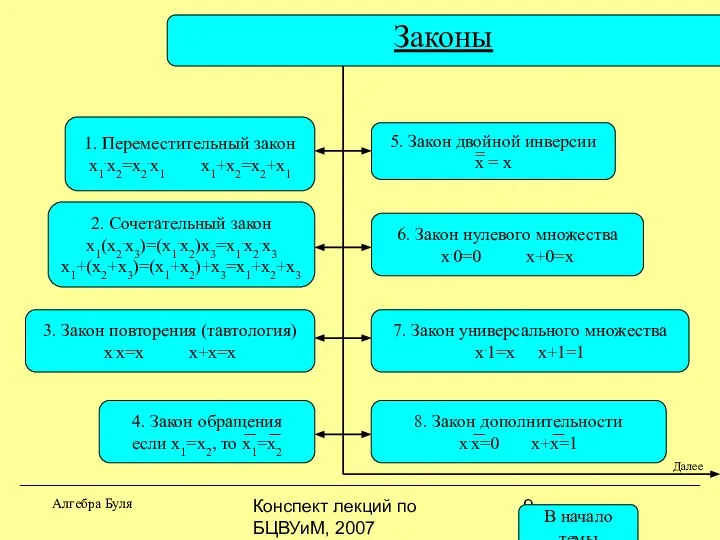

- 9. Конспект лекций по БЦВУиМ, 2007 Законы Алгебра Буля 1. Переместительный закон х1.х2=х2.х1 х1+х2=х2+х1 2. Сочетательный закон

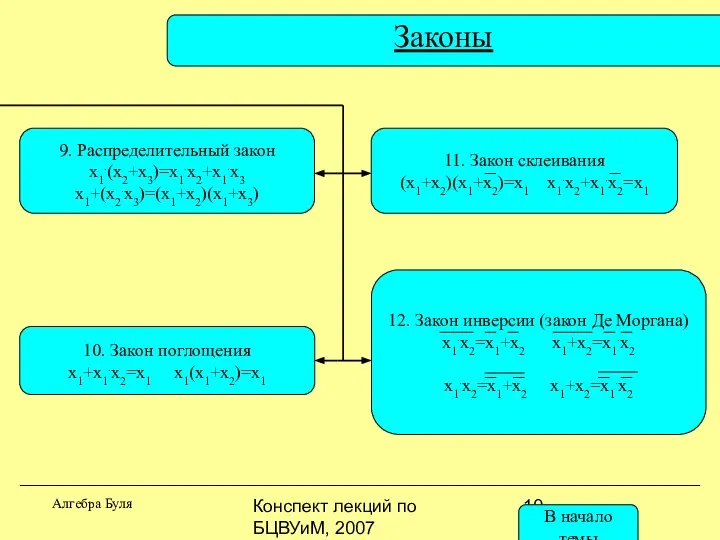

- 10. Конспект лекций по БЦВУиМ, 2007 Законы Алгебра Буля 9. Распределительный закон х1.(х2+х3)=х1.х2+х1.х3 х1+(х2.х3)=(х1+х2)(х1+х3) 10. Закон поглощения

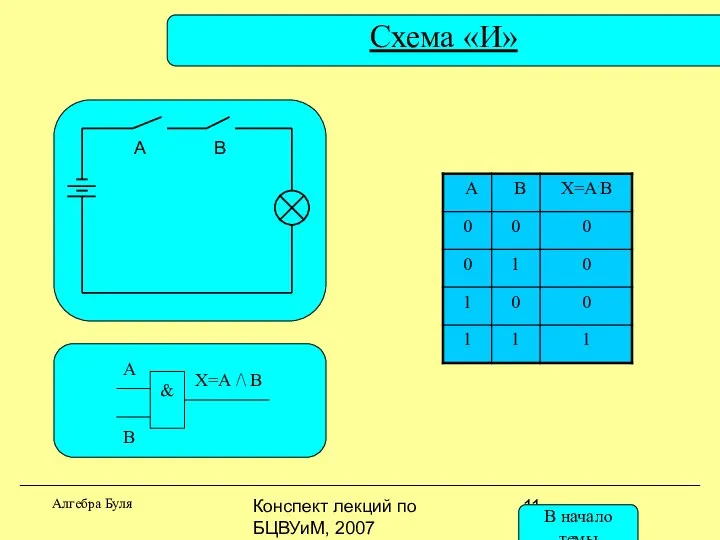

- 11. Конспект лекций по БЦВУиМ, 2007 Схема «И» Алгебра Буля А В & А В Х=А /\

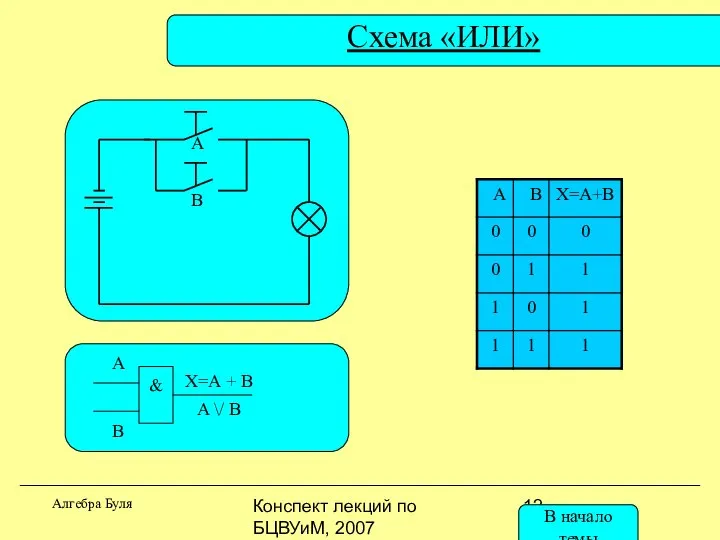

- 12. Конспект лекций по БЦВУиМ, 2007 Схема «ИЛИ» Алгебра Буля А В & А В Х=А +

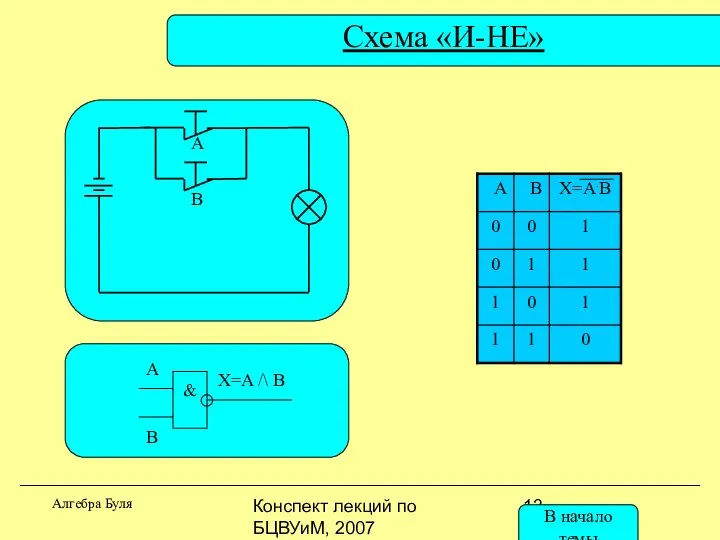

- 13. Конспект лекций по БЦВУиМ, 2007 Схема «И-НЕ» Алгебра Буля & А В Х=А /\ В А

- 14. Конспект лекций по БЦВУиМ, 2007 Схема «ИЛИ-НЕ» Алгебра Буля А В 1 А В Х=А /\

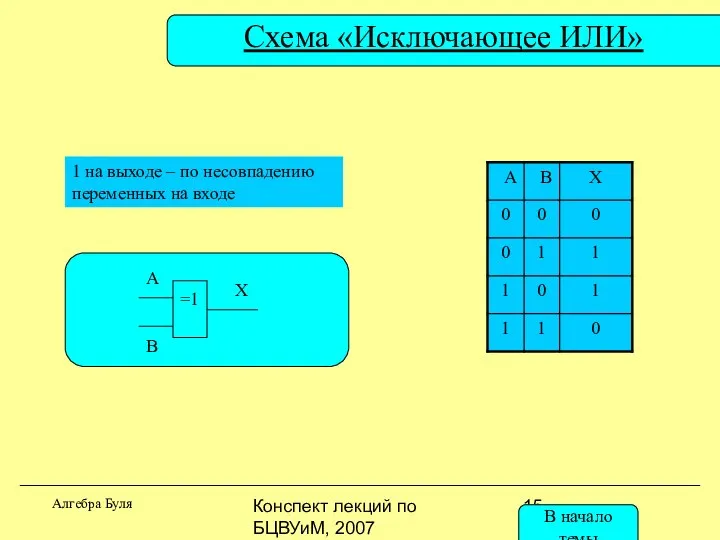

- 15. Конспект лекций по БЦВУиМ, 2007 Схема «Исключающее ИЛИ» Алгебра Буля =1 А В Х 1 на

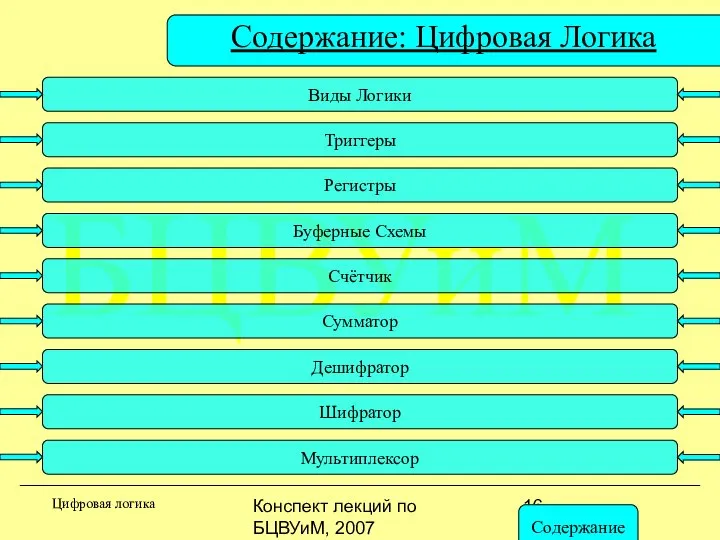

- 16. Конспект лекций по БЦВУиМ, 2007 БЦВУиМ Содержание: Цифровая Логика Цифровая логика Триггеры Регистры Буферные Схемы Счётчик

- 17. Конспект лекций по БЦВУиМ, 2007 Виды цифровой логики Цифровая логика ТТЛ – Транзисторно-Транзисторная Логика ДТЛ –

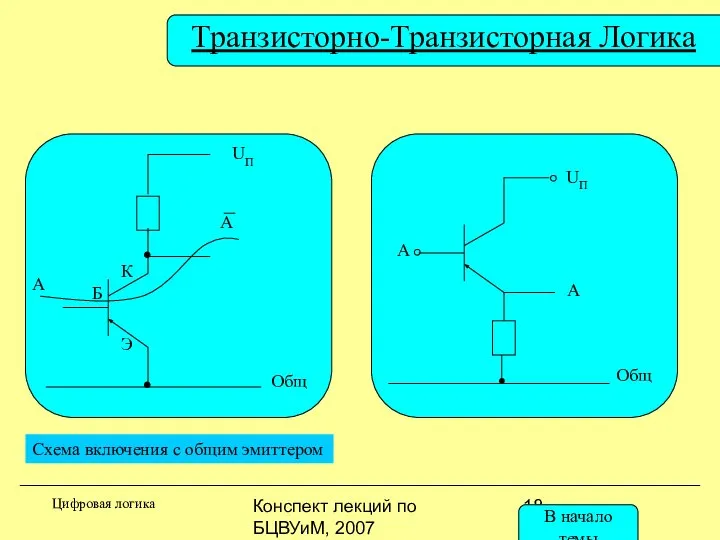

- 18. Конспект лекций по БЦВУиМ, 2007 Транзисторно-Транзисторная Логика Цифровая логика Общ UП А К Э Б А

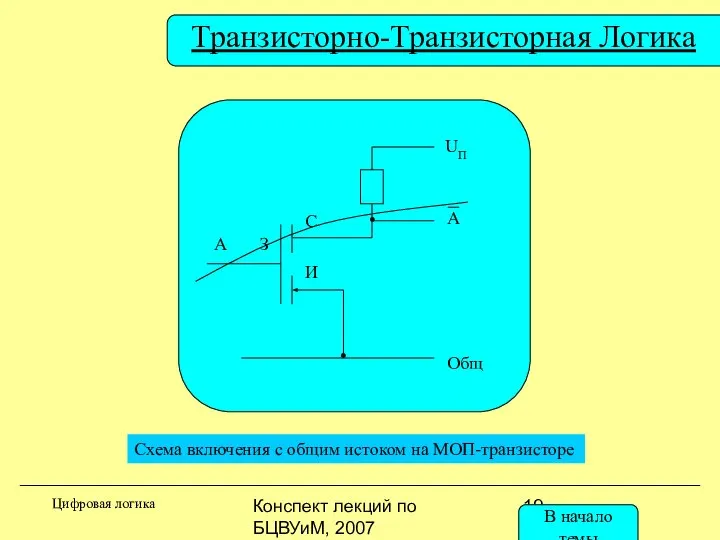

- 19. Конспект лекций по БЦВУиМ, 2007 Транзисторно-Транзисторная Логика Цифровая логика С UП А А З Общ И

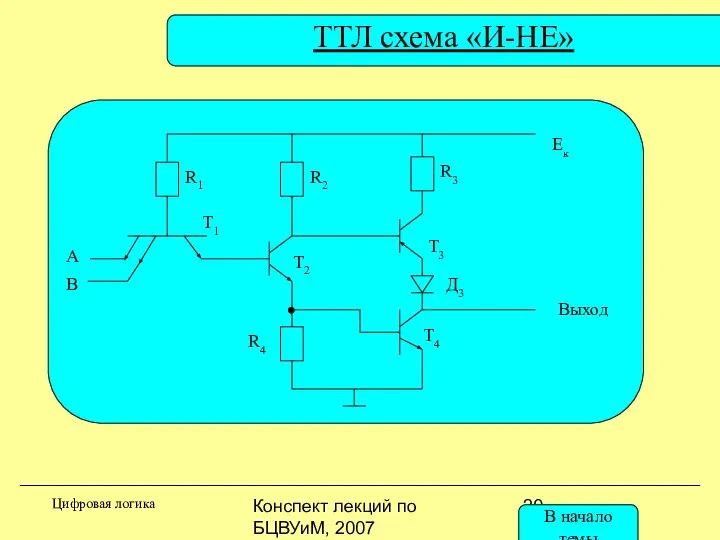

- 20. Конспект лекций по БЦВУиМ, 2007 ТТЛ схема «И-НЕ» Цифровая логика Выход Ек А В Т1 R1

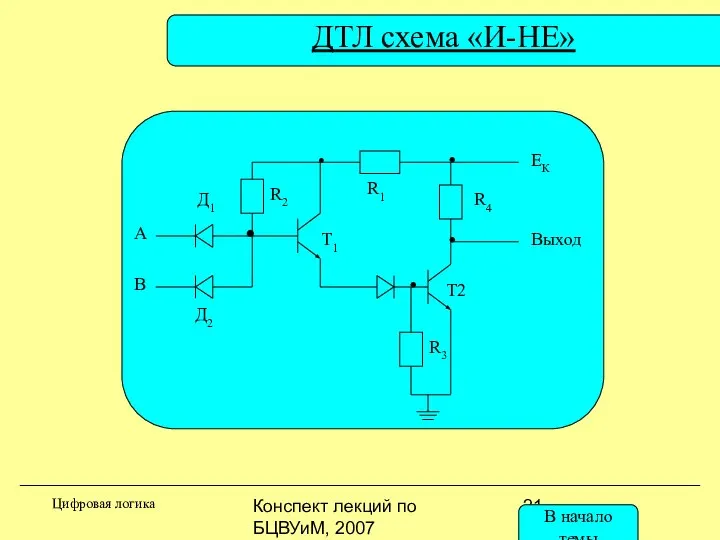

- 21. Конспект лекций по БЦВУиМ, 2007 ДТЛ схема «И-НЕ» Цифровая логика Д1 Д2 А В R2 R1

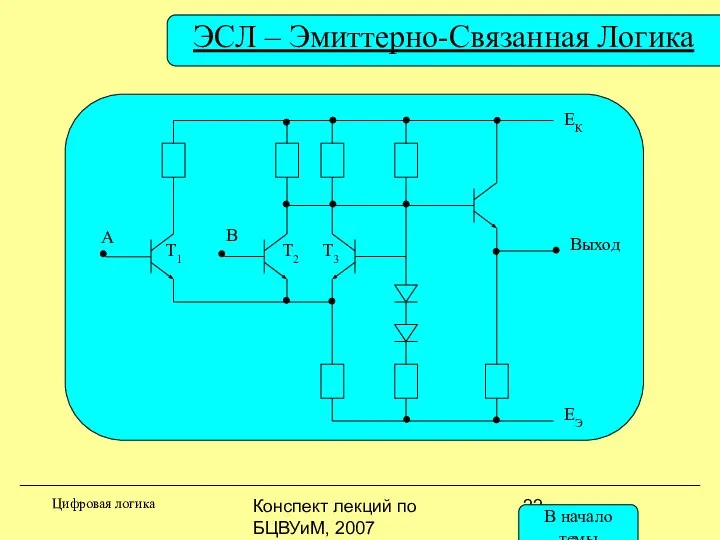

- 22. Конспект лекций по БЦВУиМ, 2007 ЭСЛ – Эмиттерно-Связанная Логика Цифровая логика Выход ЕК ЕЭ А В

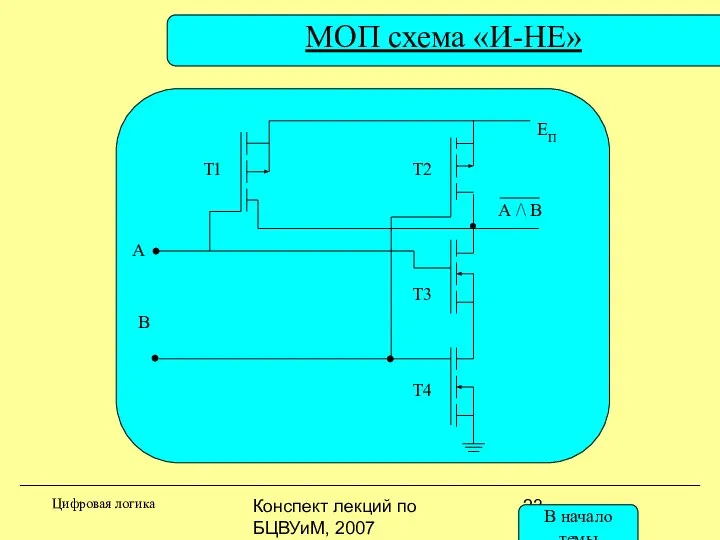

- 23. Конспект лекций по БЦВУиМ, 2007 МОП схема «И-НЕ» Цифровая логика А В Т1 Т2 Т3 Т4

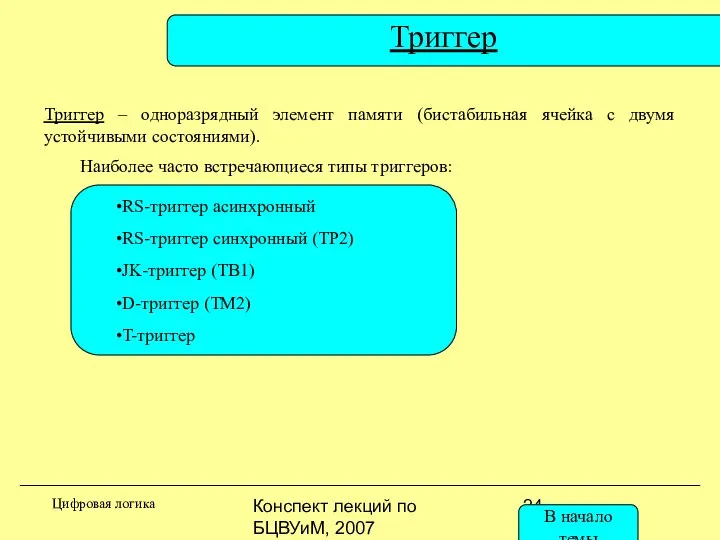

- 24. Конспект лекций по БЦВУиМ, 2007 RS-триггер асинхронный RS-триггер синхронный (ТР2) JK-триггер (ТВ1) D-триггер (ТМ2) T-триггер Цифровая

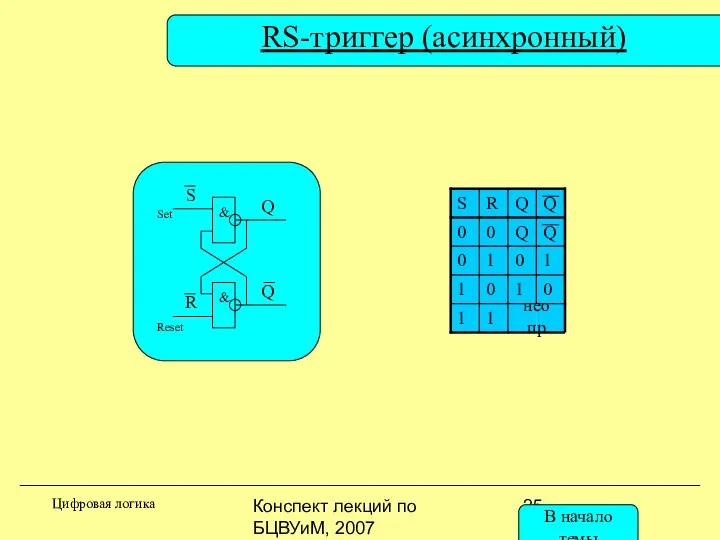

- 25. Конспект лекций по БЦВУиМ, 2007 S & & Q Q R Set Reset неопр RS-триггер (асинхронный)

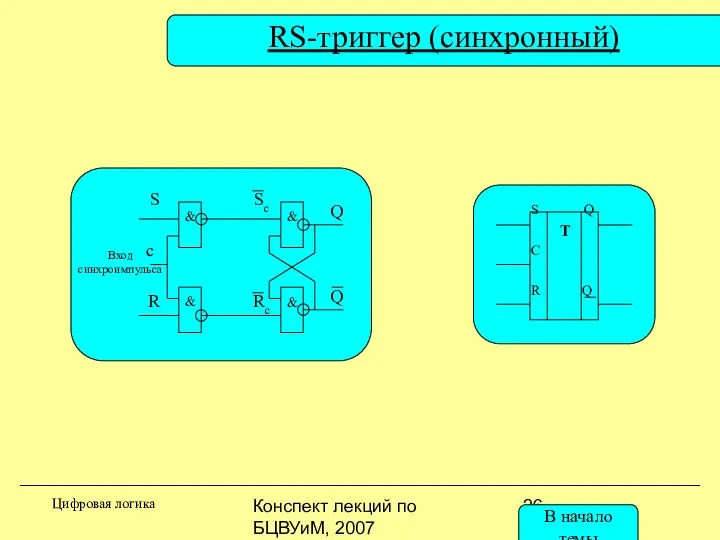

- 26. Конспект лекций по БЦВУиМ, 2007 S Q C R Q Вход синхроимпульса T Sc & &

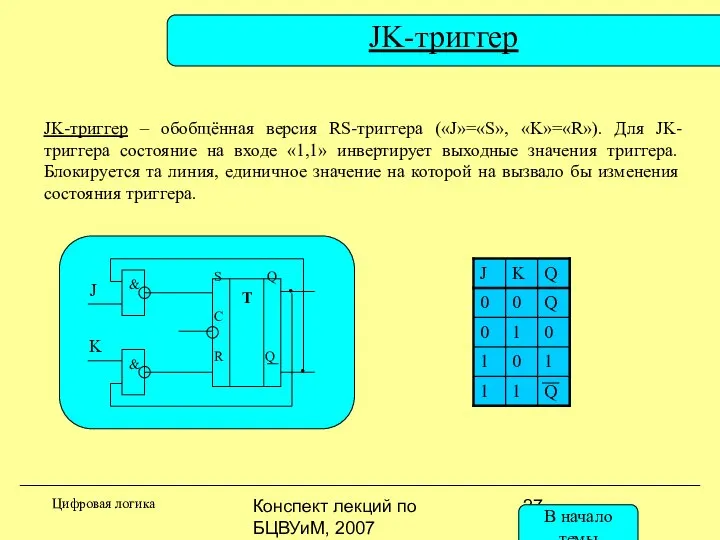

- 27. Конспект лекций по БЦВУиМ, 2007 JK-триггер – обобщённая версия RS-триггера («J»=«S», «K»=«R»). Для JK-триггера состояние на

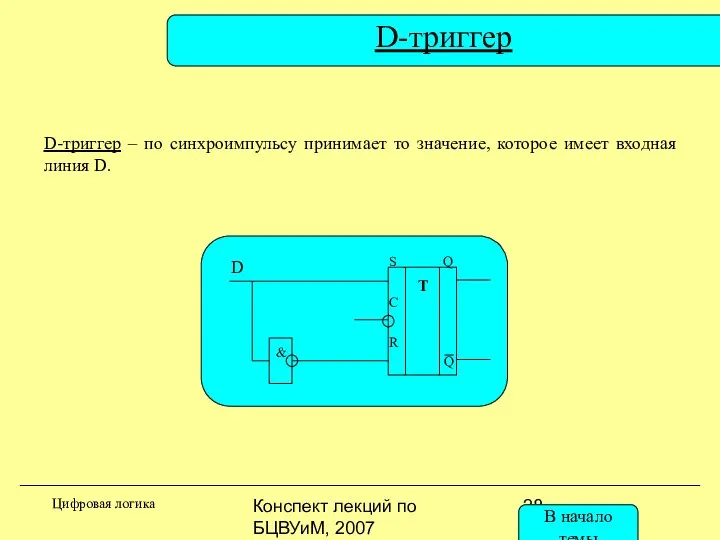

- 28. Конспект лекций по БЦВУиМ, 2007 D-триггер – по синхроимпульсу принимает то значение, которое имеет входная линия

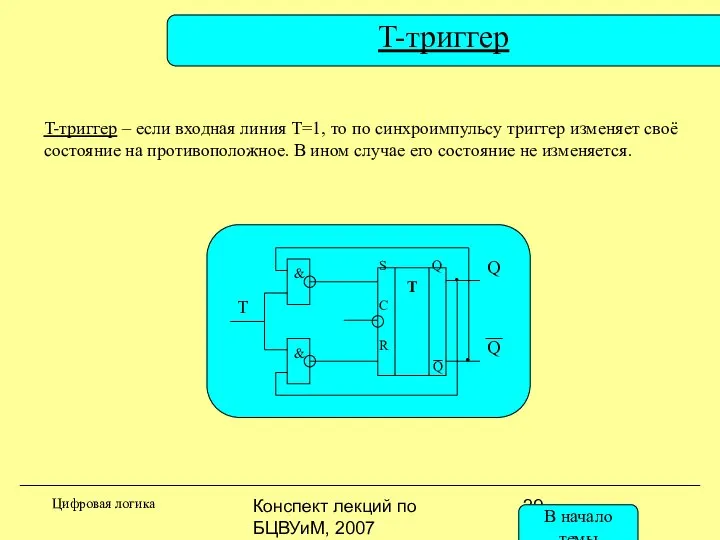

- 29. Конспект лекций по БЦВУиМ, 2007 T-триггер T-триггер – если входная линия T=1, то по синхроимпульсу триггер

- 30. Конспект лекций по БЦВУиМ, 2007 Регистр Для обработки и хранения информации используются сдвиговые регистры, состоящие из

- 31. Конспект лекций по БЦВУиМ, 2007 S Q D C R Последовательный вход Регистр с последовательным входом

- 32. Конспект лекций по БЦВУиМ, 2007 Диаграмма работы регистра Временная диаграмма работы 4х разрядного сдвигового регистра t

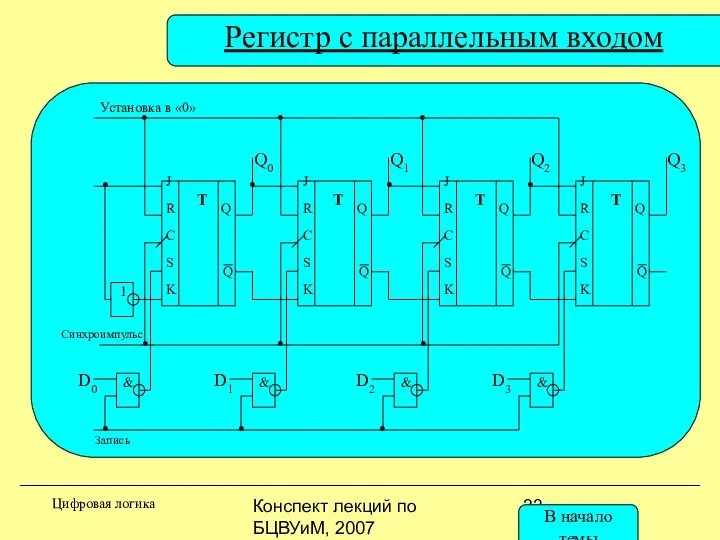

- 33. Конспект лекций по БЦВУиМ, 2007 J R Q C S K Регистр с параллельным входом T

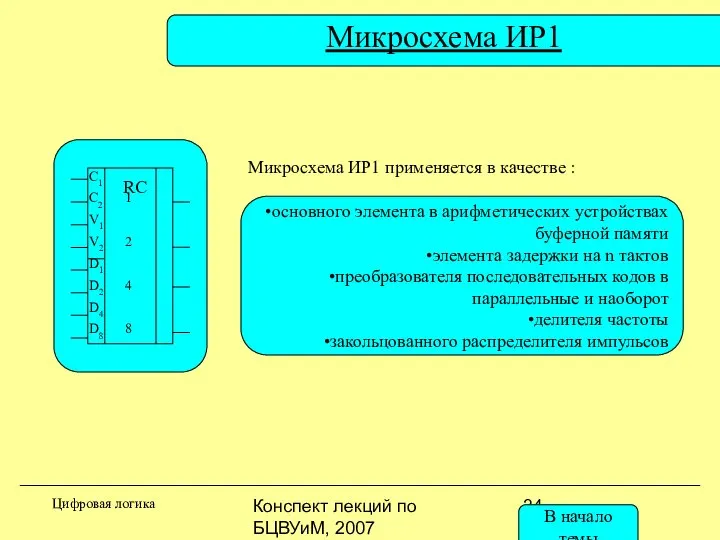

- 34. Конспект лекций по БЦВУиМ, 2007 основного элемента в арифметических устройствах буферной памяти элемента задержки на n

- 35. Конспект лекций по БЦВУиМ, 2007 Буферные схемы Схемы с открытым коллектором Схемы с тремя состояниями Цифровая

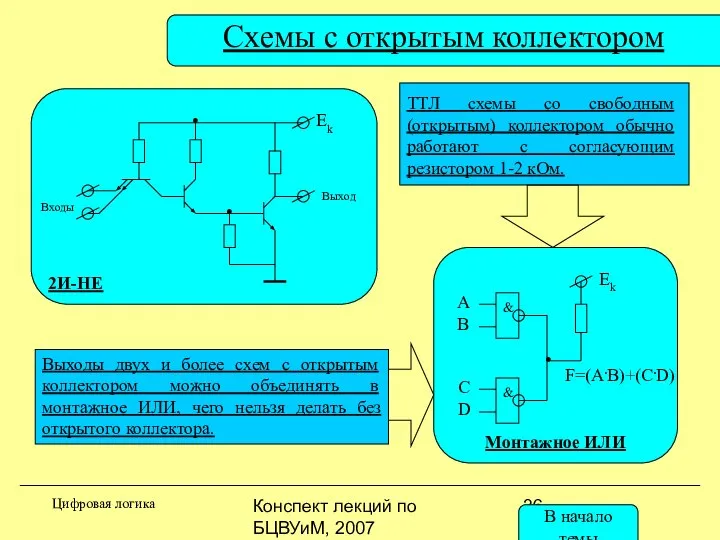

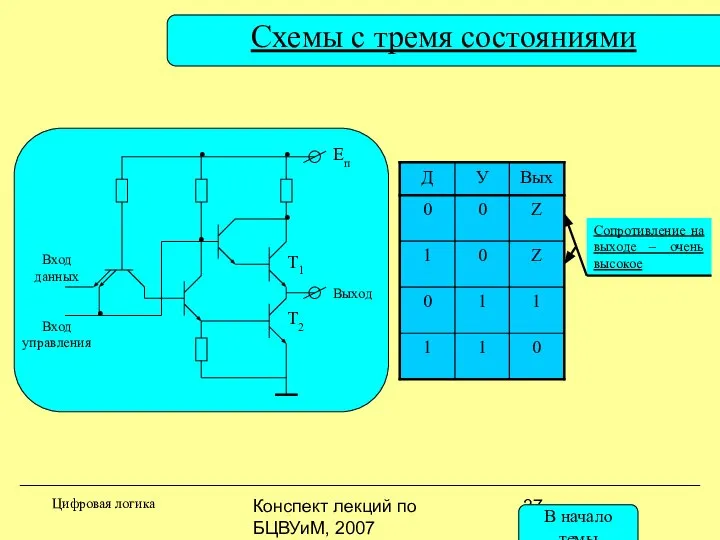

- 36. Конспект лекций по БЦВУиМ, 2007 Монтажное ИЛИ 2И-НЕ Схемы с открытым коллектором Ek Выход Входы &

- 37. Конспект лекций по БЦВУиМ, 2007 Схемы с тремя состояниями T1 T2 Выход Eп . . .

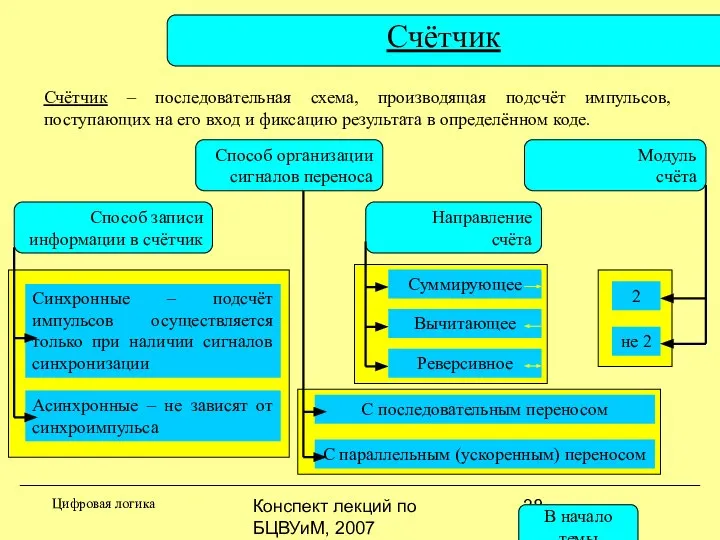

- 38. Конспект лекций по БЦВУиМ, 2007 Счётчик Счётчик – последовательная схема, производящая подсчёт импульсов, поступающих на его

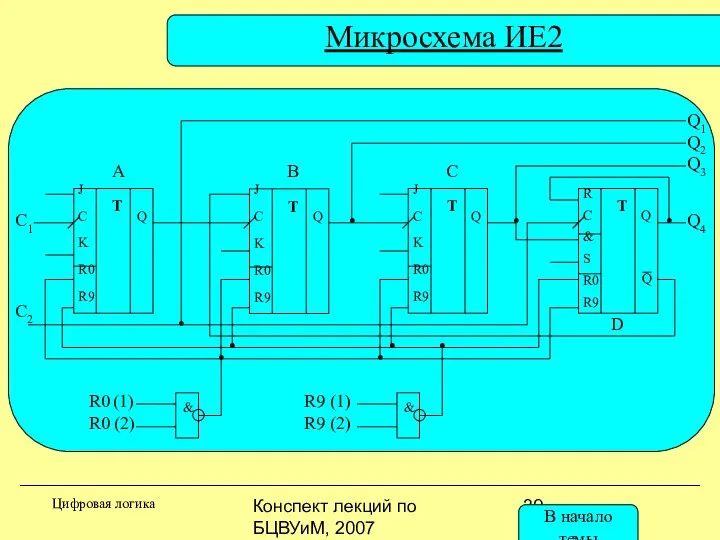

- 39. Конспект лекций по БЦВУиМ, 2007 Микросхема ИЕ2 J C Q K R0 R9 T J C

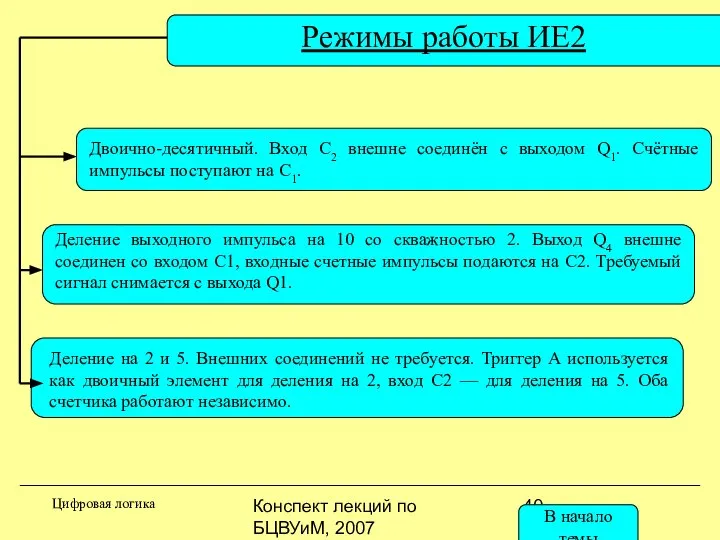

- 40. Конспект лекций по БЦВУиМ, 2007 Режимы работы ИЕ2 Двоично-десятичный. Вход C2 внешне соединён с выходом Q1.

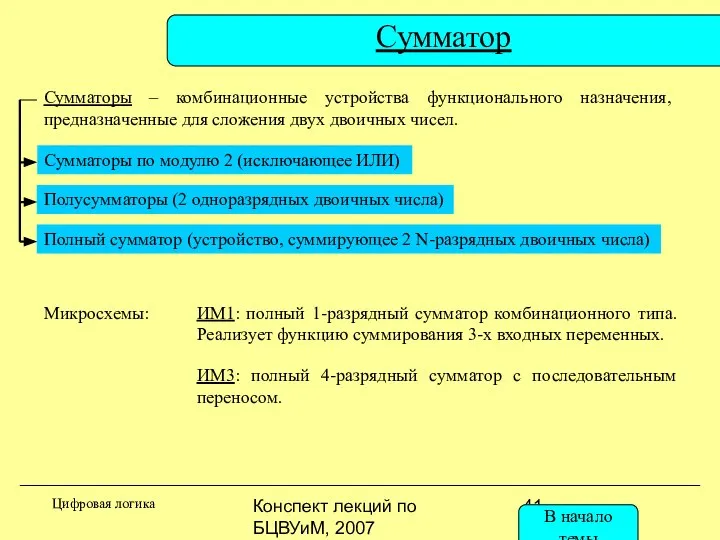

- 41. Конспект лекций по БЦВУиМ, 2007 Сумматор Сумматоры – комбинационные устройства функционального назначения, предназначенные для сложения двух

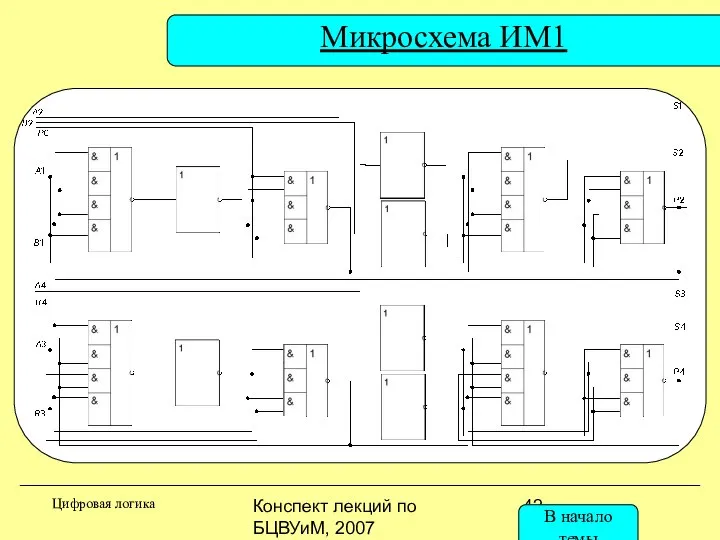

- 42. Конспект лекций по БЦВУиМ, 2007 Микросхема ИМ1 Цифровая логика В начало темы

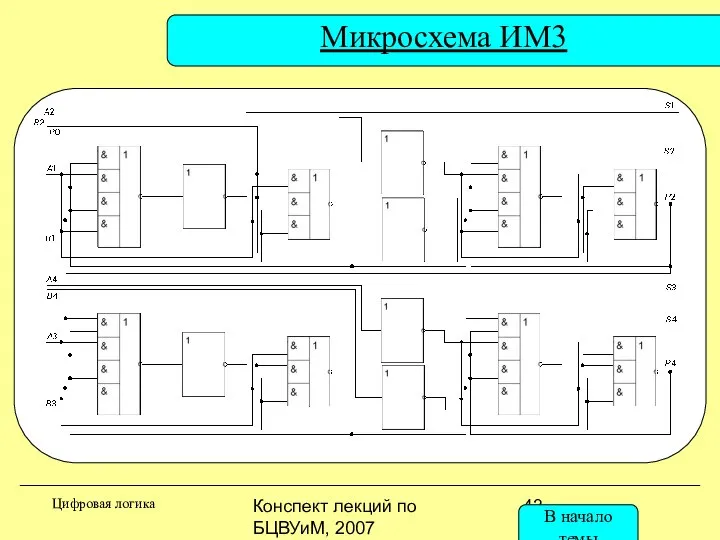

- 43. Конспект лекций по БЦВУиМ, 2007 Микросхема ИМ3 Цифровая логика В начало темы

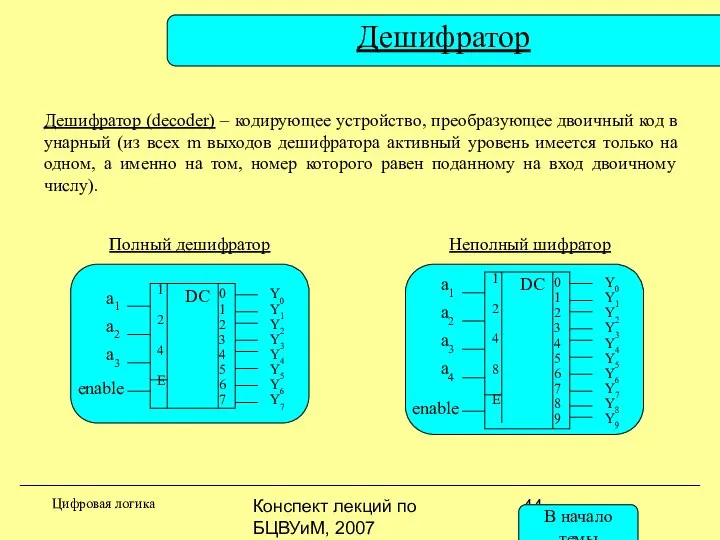

- 44. Конспект лекций по БЦВУиМ, 2007 Дешифратор Дешифратор (decoder) – кодирующее устройство, преобразующее двоичный код в унарный

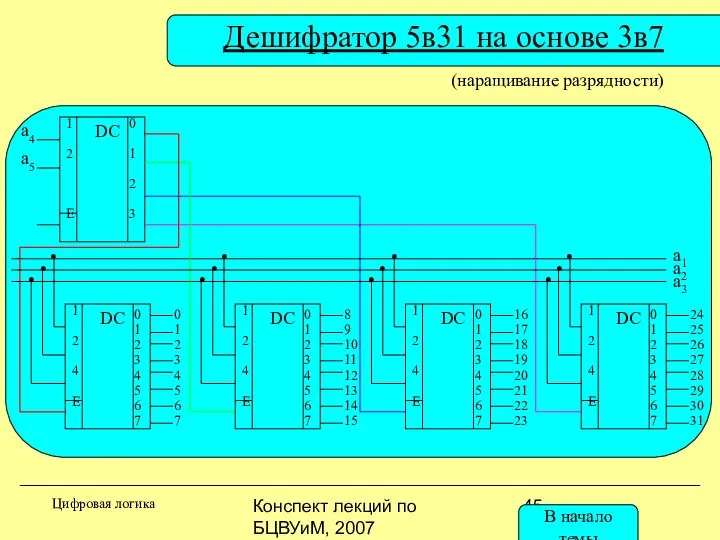

- 45. Конспект лекций по БЦВУиМ, 2007 Дешифратор 5в31 на основе 3в7 1 2 4 E 0 1

- 46. Конспект лекций по БЦВУиМ, 2007 Серии микросхем дешифраторов Дешифраторы, выпускаемые в виде отдельных микросхемах, имеют буквенное

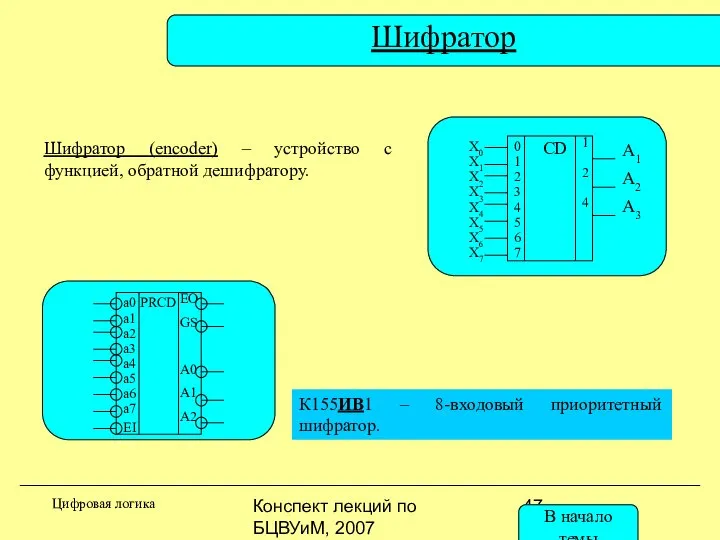

- 47. Конспект лекций по БЦВУиМ, 2007 Шифратор Шифратор (encoder) – устройство с функцией, обратной дешифратору. 1 2

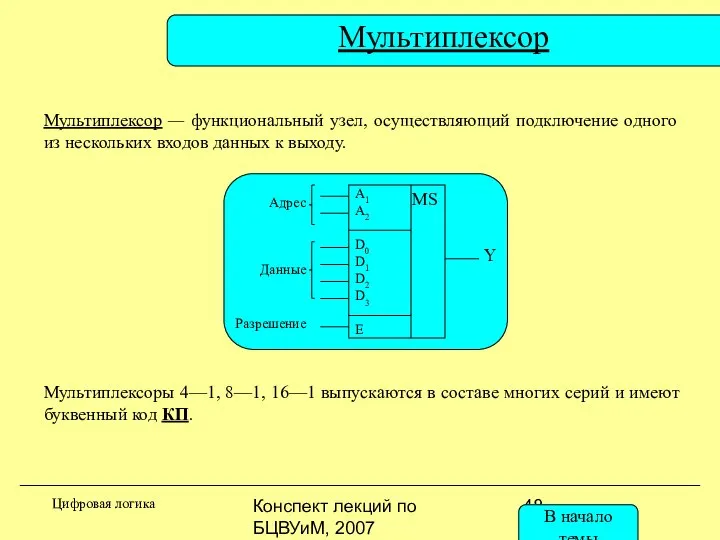

- 48. Конспект лекций по БЦВУиМ, 2007 Мультиплексор Мультиплексор — функциональный узел, осуществляющий подключение одного из нескольких входов

- 49. Конспект лекций по БЦВУиМ, 2007 БЦВУиМ Содержание: Память Память Запоминающие устройства Адресация по принципу линейной выборки

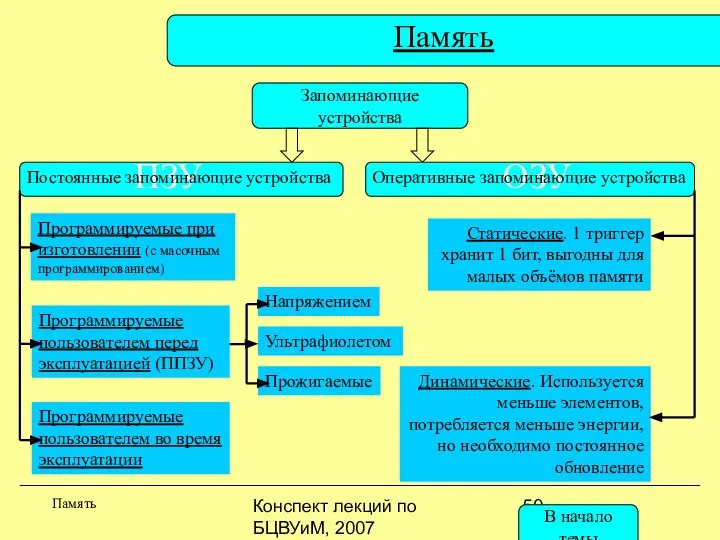

- 50. Конспект лекций по БЦВУиМ, 2007 Память Память Запоминающие устройства ПЗУ Постоянные запоминающие устройства ОЗУ Оперативные запоминающие

- 51. Конспект лекций по БЦВУиМ, 2007 Постоянное запоминающее устройство Память Дешифратор адреса памяти Матрица памяти MxN Выходной

- 52. Конспект лекций по БЦВУиМ, 2007 Полупроводниковые ПЗУ Память Полупроводниковые ПЗУ Статические Динамические Требуют цикла регенерации информации

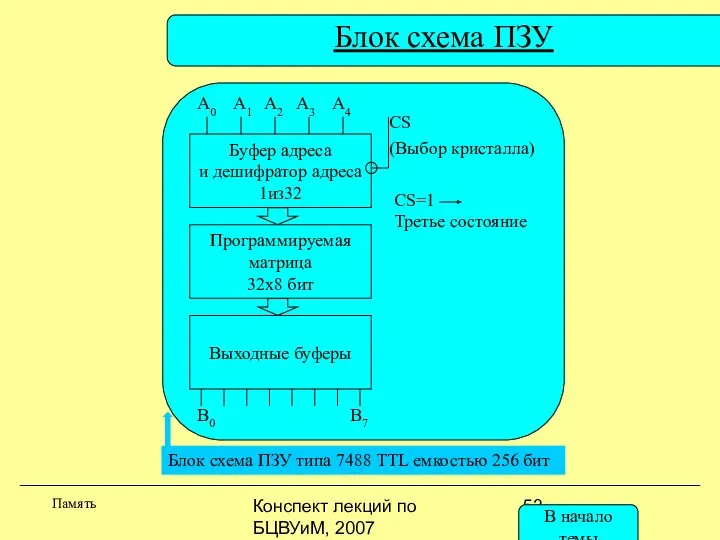

- 53. Конспект лекций по БЦВУиМ, 2007 Блок схема ПЗУ Память Буфер адреса и дешифратор адреса 1из32 A0

- 54. Конспект лекций по БЦВУиМ, 2007 Принцип адресации: Линейная выборка Память В начало темы

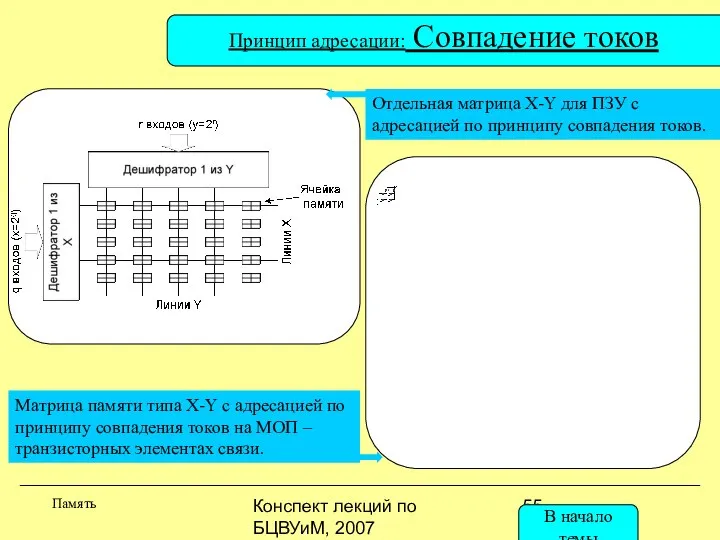

- 55. Конспект лекций по БЦВУиМ, 2007 Принцип адресации: Совпадение токов Память Матрица памяти типа X-Y с адресацией

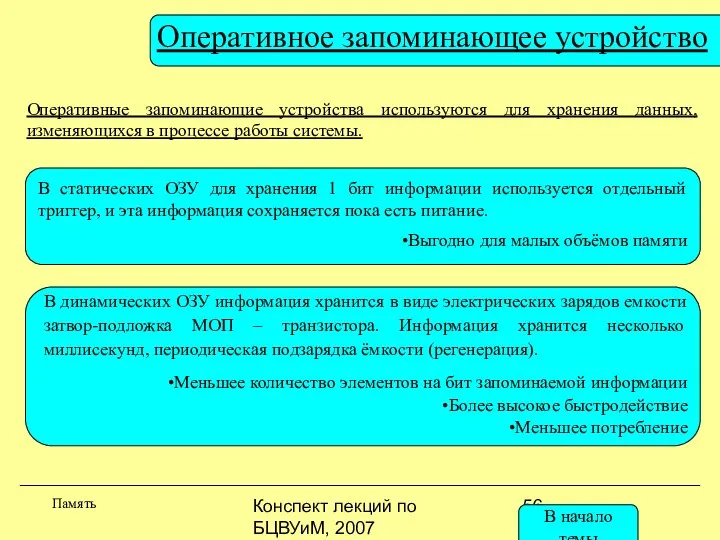

- 56. Конспект лекций по БЦВУиМ, 2007 Оперативное запоминающее устройство Память Оперативные запоминающие устройства используются для хранения данных,

- 57. Конспект лекций по БЦВУиМ, 2007 Статическое ОЗУ Память Статическое ОЗУ Nx1 бит Адресные линии Линия чтения/записи

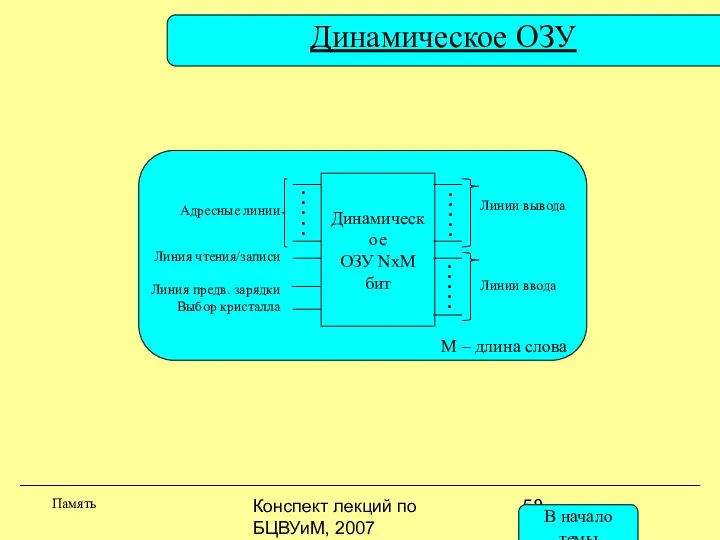

- 58. Конспект лекций по БЦВУиМ, 2007 Динамическое ОЗУ Память Динамическое ОЗУ NxM бит . . . .

- 59. Конспект лекций по БЦВУиМ, 2007 Динамическая ячейка памяти Память В начало темы

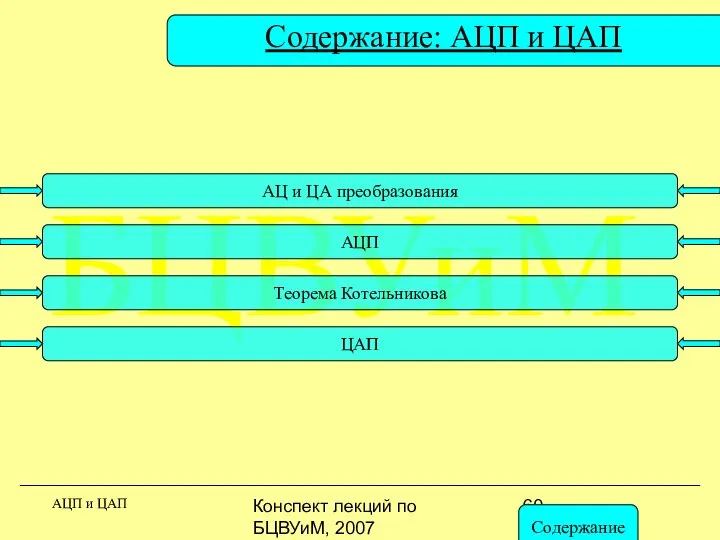

- 60. Конспект лекций по БЦВУиМ, 2007 БЦВУиМ Содержание: АЦП и ЦАП АЦП и ЦАП АЦ и ЦА

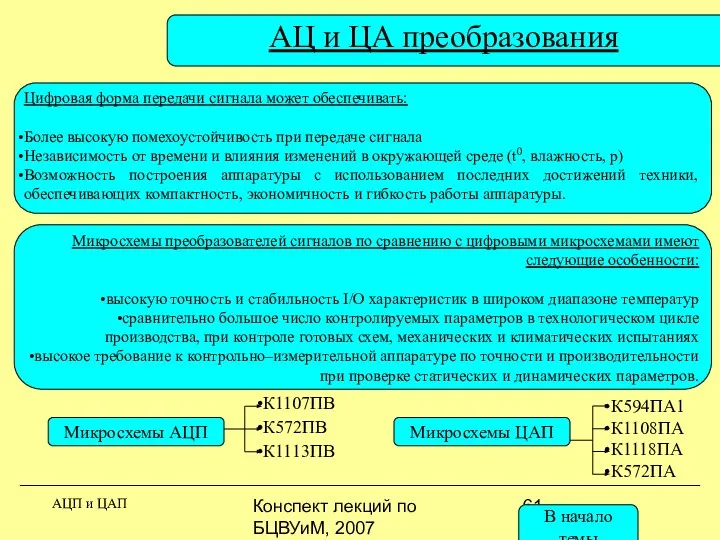

- 61. Конспект лекций по БЦВУиМ, 2007 АЦ и ЦА преобразования АЦП и ЦАП Микросхемы преобразователей сигналов по

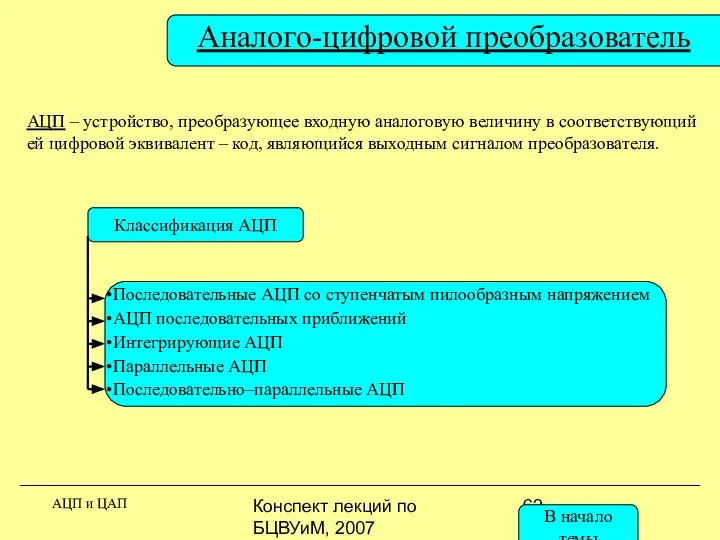

- 62. Конспект лекций по БЦВУиМ, 2007 Аналого-цифровой преобразователь АЦП и ЦАП АЦП – устройство, преобразующее входную аналоговую

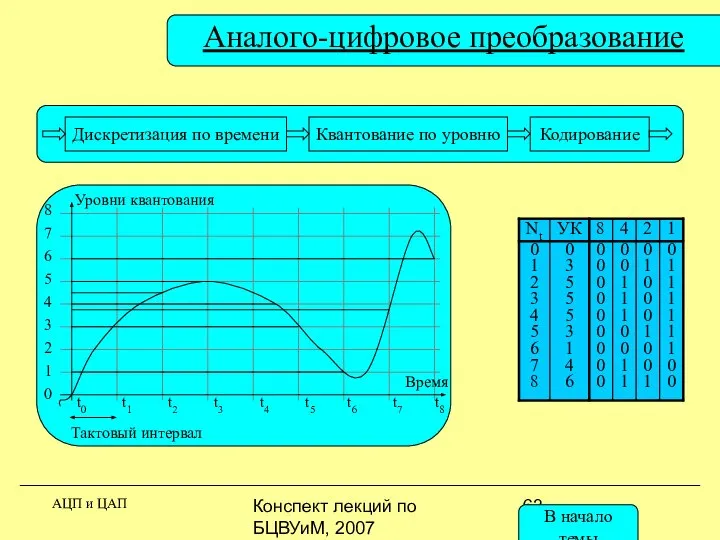

- 63. Конспект лекций по БЦВУиМ, 2007 Аналого-цифровое преобразование АЦП и ЦАП 8 7 6 5 4 3

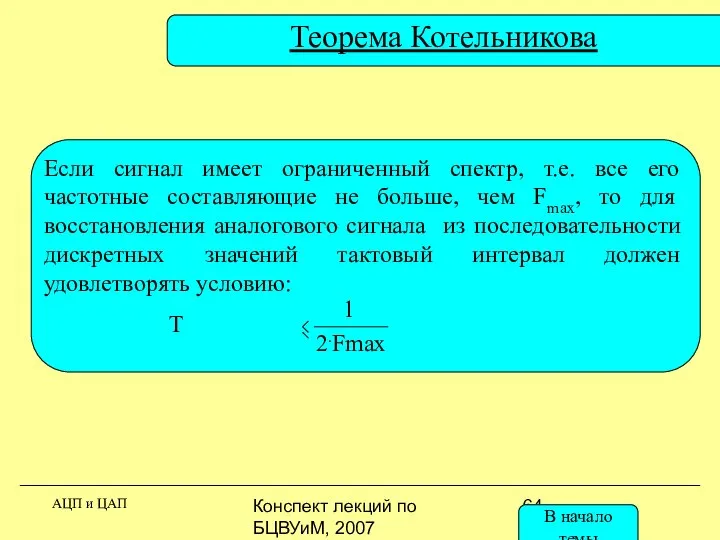

- 64. Конспект лекций по БЦВУиМ, 2007 Теорема Котельникова АЦП и ЦАП Если сигнал имеет ограниченный спектр, т.е.

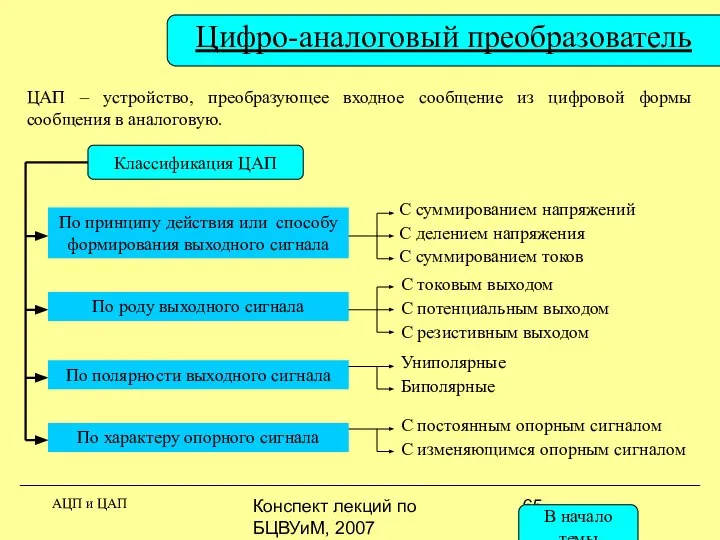

- 65. Конспект лекций по БЦВУиМ, 2007 Цифро-аналоговый преобразователь АЦП и ЦАП ЦАП – устройство, преобразующее входное сообщение

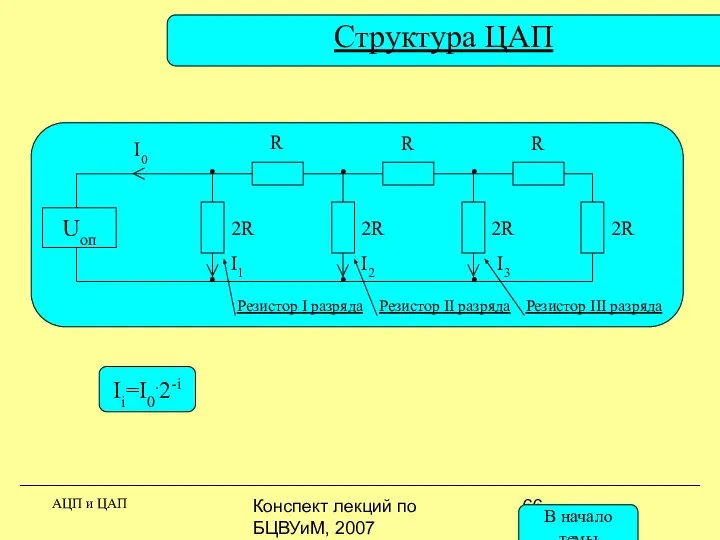

- 66. Конспект лекций по БЦВУиМ, 2007 Ii=I0.2-i Структура ЦАП АЦП и ЦАП Uоп R R R 2R

- 67. Конспект лекций по БЦВУиМ, 2007 Содержание: МП – В общих чертах Микропроцессор Содержание БЦВУиМ Управление процессами

- 68. Конспект лекций по БЦВУиМ, 2007 ЛА Структурная организация БЦВУ Микропроцессор Бортовые Цифровые Вычислительные Системы предназначены для:

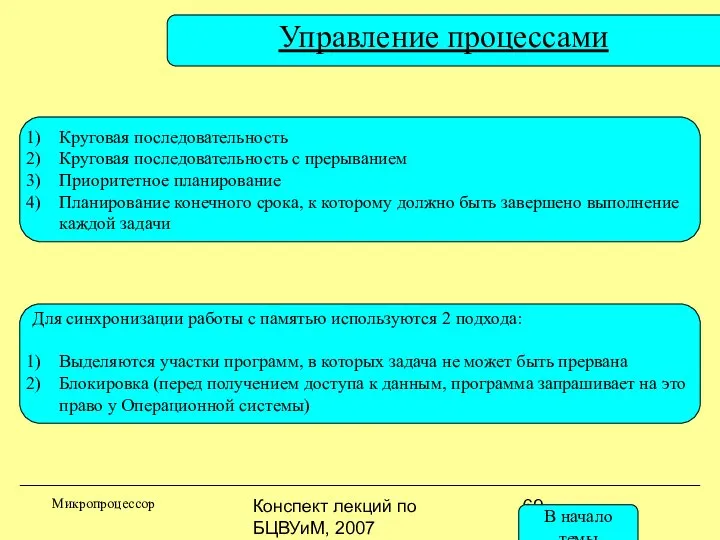

- 69. Конспект лекций по БЦВУиМ, 2007 Управление процессами Микропроцессор Круговая последовательность Круговая последовательность с прерыванием Приоритетное планирование

- 70. Конспект лекций по БЦВУиМ, 2007 БЦВУ Структурная схема БЦВМ Микропроцессор АЛУ УУ РОН Процессор ОЗУ ПЗУ

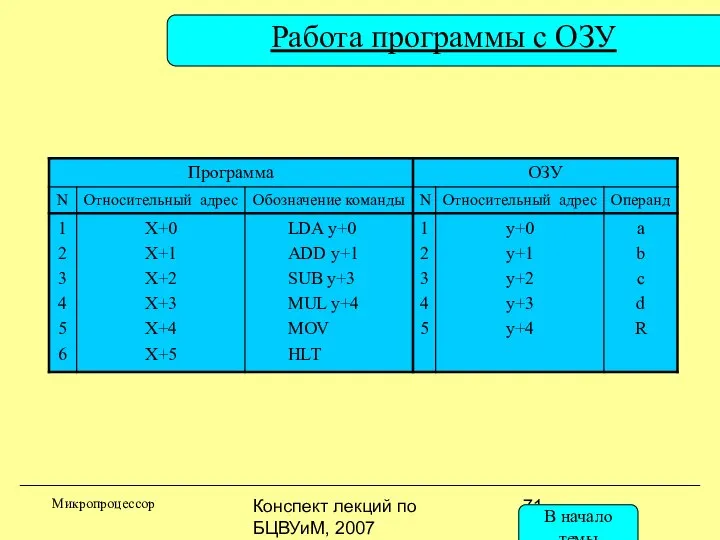

- 71. Конспект лекций по БЦВУиМ, 2007 Работа программы с ОЗУ Микропроцессор В начало темы

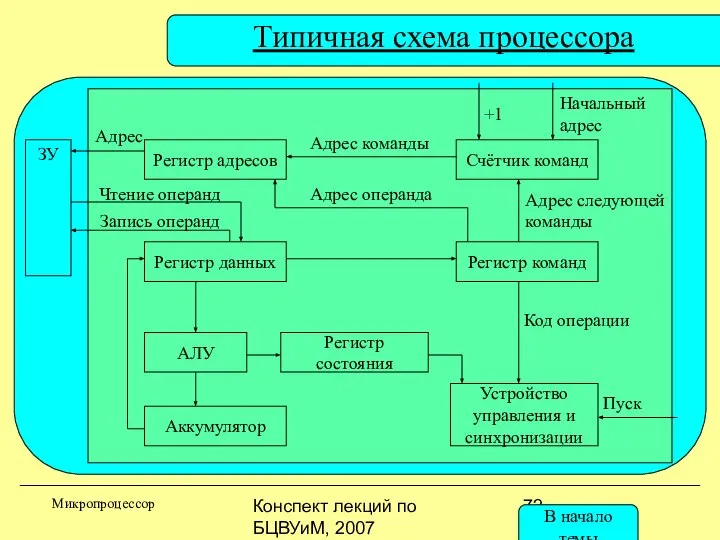

- 72. Конспект лекций по БЦВУиМ, 2007 Типичная схема процессора Микропроцессор Регистр адресов Регистр данных АЛУ Аккумулятор Регистр

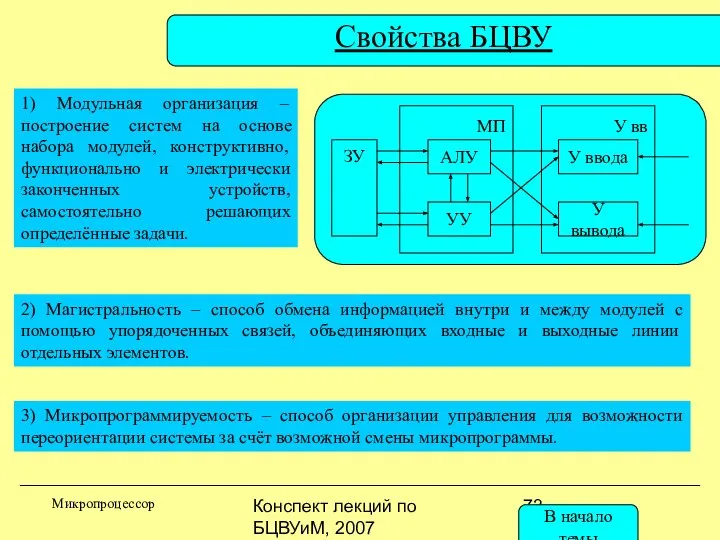

- 73. Конспект лекций по БЦВУиМ, 2007 Свойства БЦВУ Микропроцессор ЗУ АЛУ УУ У ввода У вывода У

- 74. Конспект лекций по БЦВУиМ, 2007 Классификация основных МП средств Микропроцессор Микро ЭВМ – конструктивно завершённая МПС,

- 75. Конспект лекций по БЦВУиМ, 2007 БЦВУиМ Содержание: МП – Архитектура и Интерфейс Микропроцессор Регистры микропроцессорных систем

- 76. Конспект лекций по БЦВУиМ, 2007 Микропроцессор КР580ВМ80А Микропроцессор КР580ВМ80А 8-разрядный МП Центральный процессорный элемент параллельной обработки

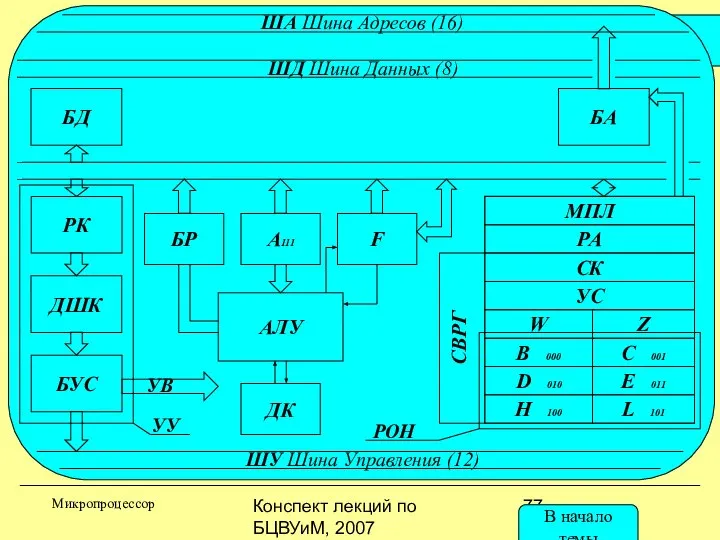

- 77. Конспект лекций по БЦВУиМ, 2007 Структурная схема КР580ВМ80А Микропроцессор В начало темы

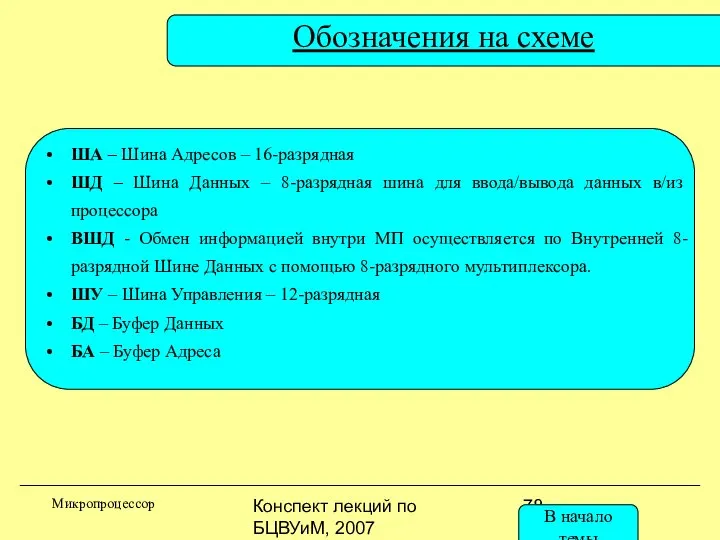

- 78. Конспект лекций по БЦВУиМ, 2007 Обозначения на схеме Микропроцессор ША – Шина Адресов – 16-разрядная ШД

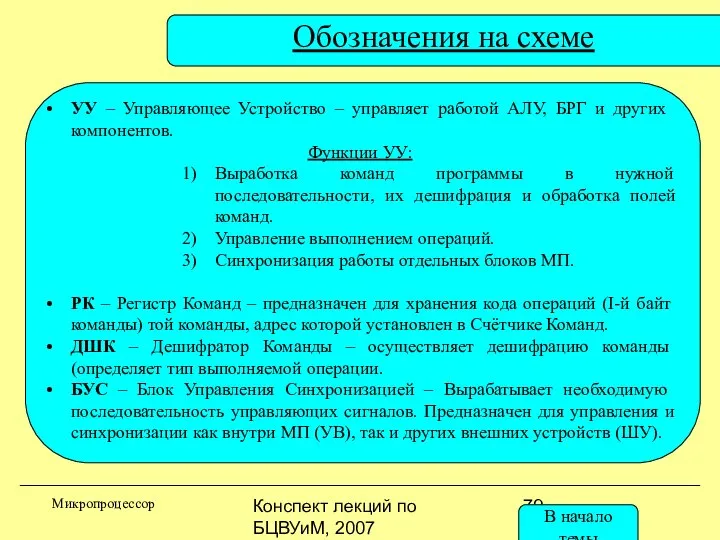

- 79. Конспект лекций по БЦВУиМ, 2007 Обозначения на схеме Микропроцессор УУ – Управляющее Устройство – управляет работой

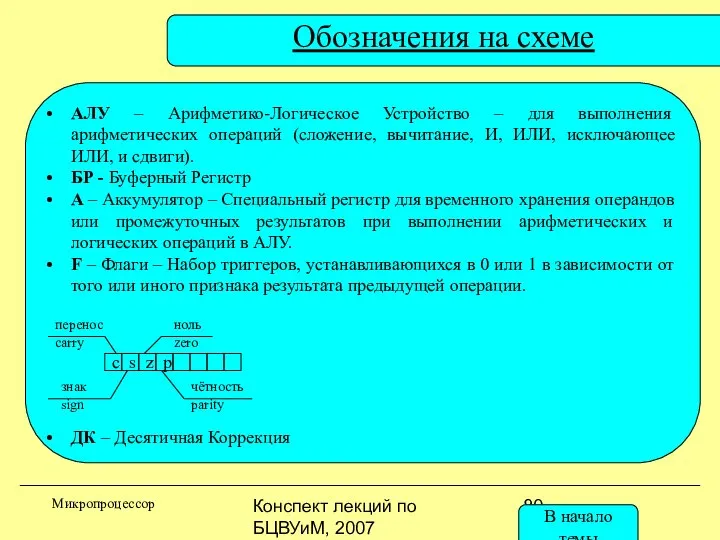

- 80. Конспект лекций по БЦВУиМ, 2007 Обозначения на схеме Микропроцессор АЛУ – Арифметико-Логическое Устройство – для выполнения

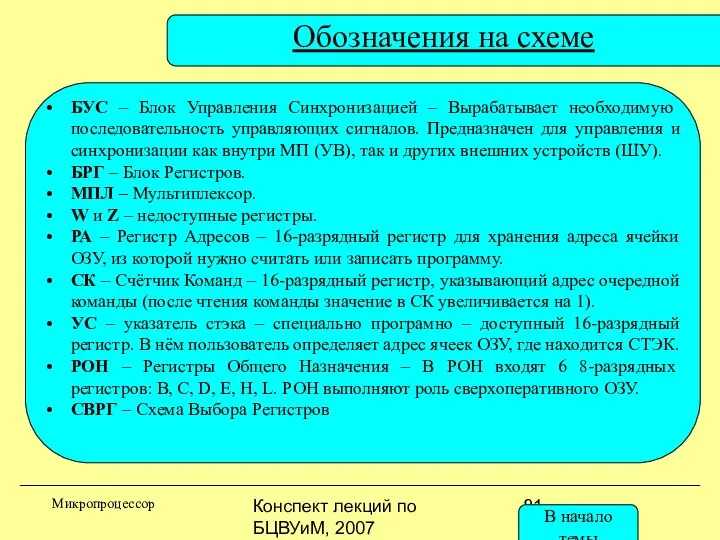

- 81. Конспект лекций по БЦВУиМ, 2007 Обозначения на схеме Микропроцессор БУС – Блок Управления Синхронизацией – Вырабатывает

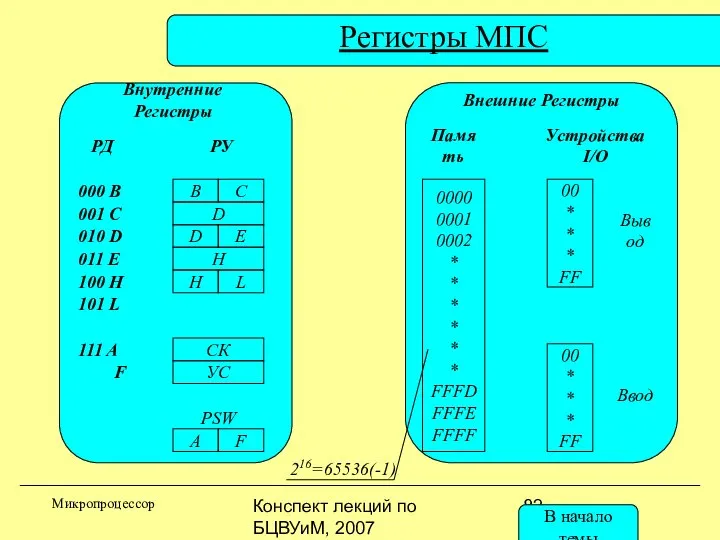

- 82. Конспект лекций по БЦВУиМ, 2007 Регистры МПС Микропроцессор B C D D E H H L

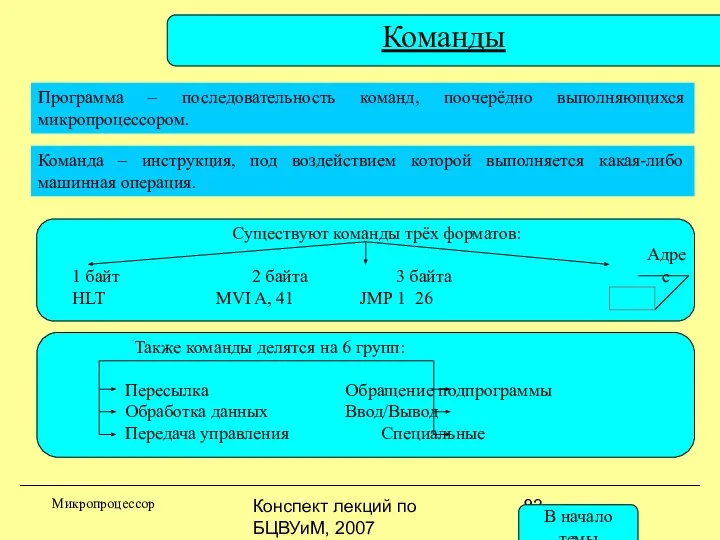

- 83. Конспект лекций по БЦВУиМ, 2007 Команды Микропроцессор Существуют команды трёх форматов: 1 байт 2 байта 3

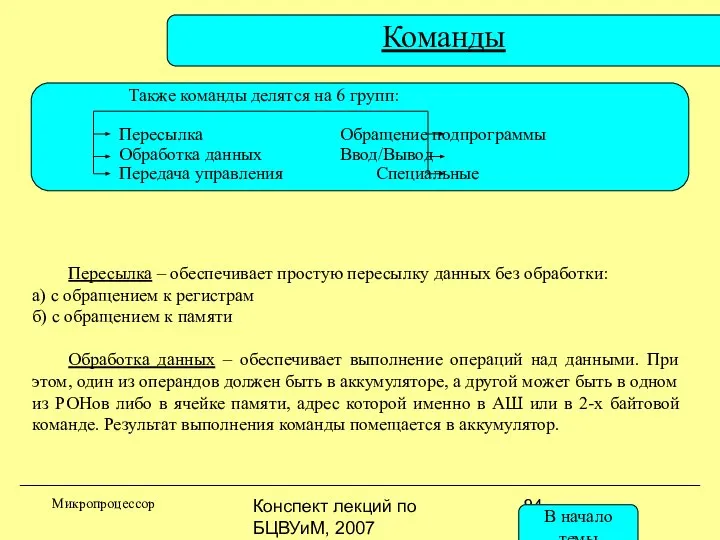

- 84. Конспект лекций по БЦВУиМ, 2007 Команды Микропроцессор Пересылка – обеспечивает простую пересылку данных без обработки: а)

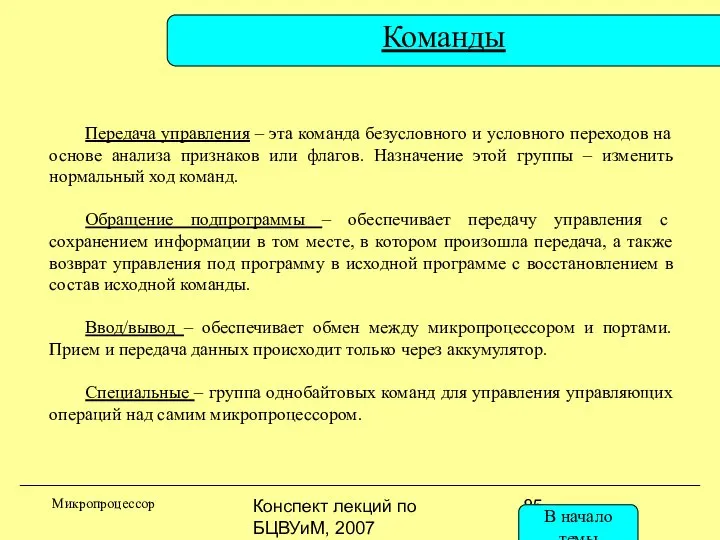

- 85. Конспект лекций по БЦВУиМ, 2007 Команды Микропроцессор Передача управления – эта команда безусловного и условного переходов

- 86. Конспект лекций по БЦВУиМ, 2007 Интерфейс Микропроцессор Интерфейс – комплекс средств унифицированного сопряжения компонентов МПС, включающей

- 87. Конспект лекций по БЦВУиМ, 2007 Порты ввода/вывода Микропроцессор МПС А Д У ПВВ1 ПВВ2 ПВВN ВУ1

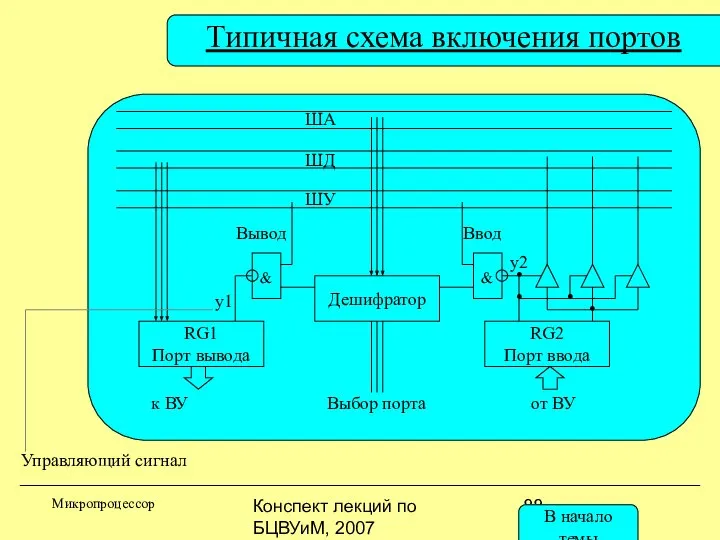

- 88. Конспект лекций по БЦВУиМ, 2007 Типичная схема включения портов Микропроцессор RG1 Порт вывода RG2 Порт ввода

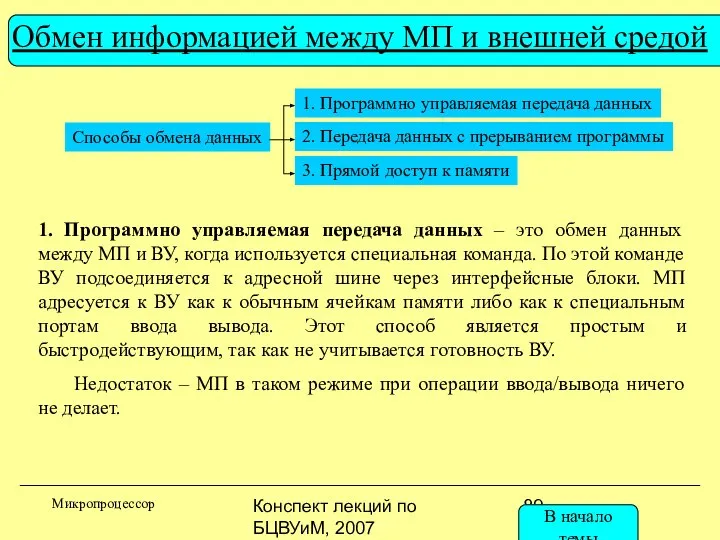

- 89. Конспект лекций по БЦВУиМ, 2007 Обмен информацией между МП и внешней средой Микропроцессор Способы обмена данных

- 90. Конспект лекций по БЦВУиМ, 2007 Обмен информацией между МП и внешней средой Микропроцессор 2. Передача данных

- 91. Конспект лекций по БЦВУиМ, 2007 Обмен информацией между МП и внешней средой Микропроцессор Существует два способа

- 92. Конспект лекций по БЦВУиМ, 2007 Обмен информацией между МП и внешней средой Микропроцессор 3. Прямой доступ

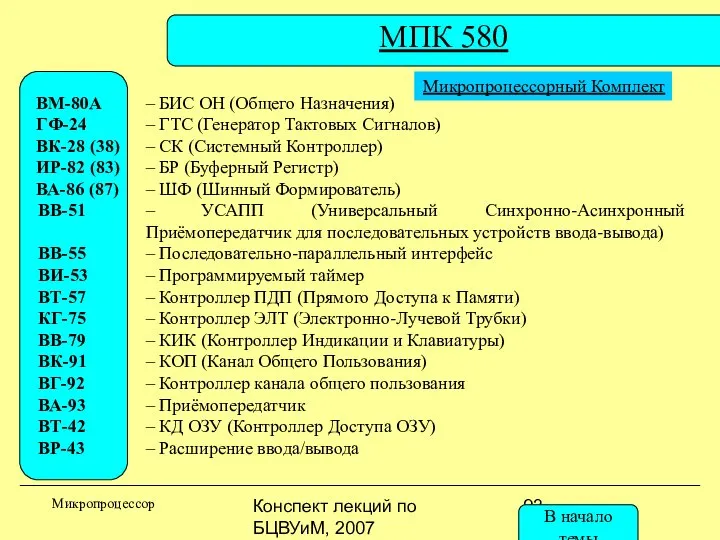

- 93. Конспект лекций по БЦВУиМ, 2007 МПК 580 Микропроцессор Микропроцессорный Комплект ВМ-80А ГФ-24 ВК-28 (38) ИР-82 (83)

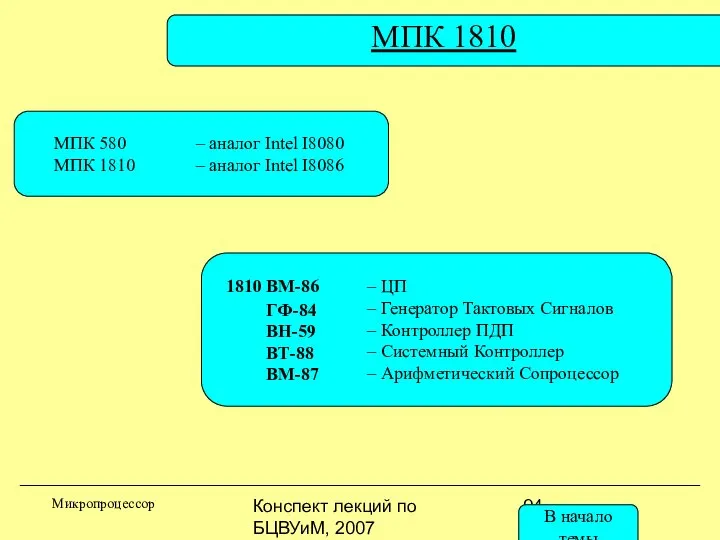

- 94. Конспект лекций по БЦВУиМ, 2007 МПК 1810 Микропроцессор МПК 580 МПК 1810 1810 ВМ-86 – ЦП

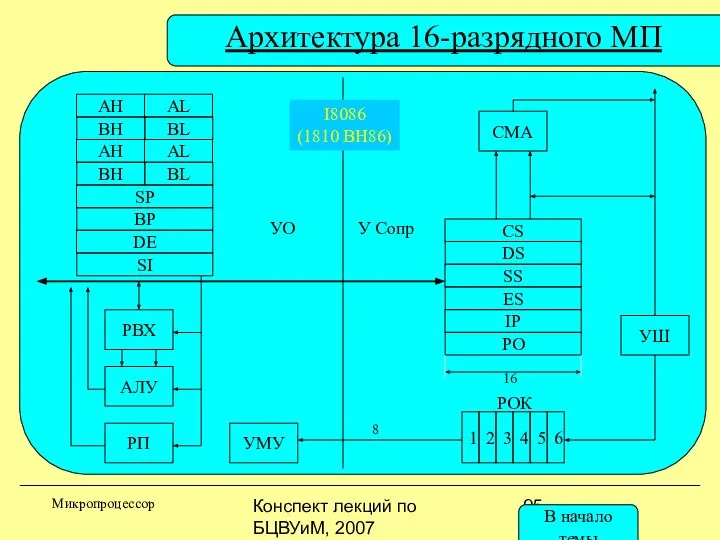

- 95. Конспект лекций по БЦВУиМ, 2007 Архитектура 16-разрядного МП Микропроцессор AH AL BH BL AH AL BH

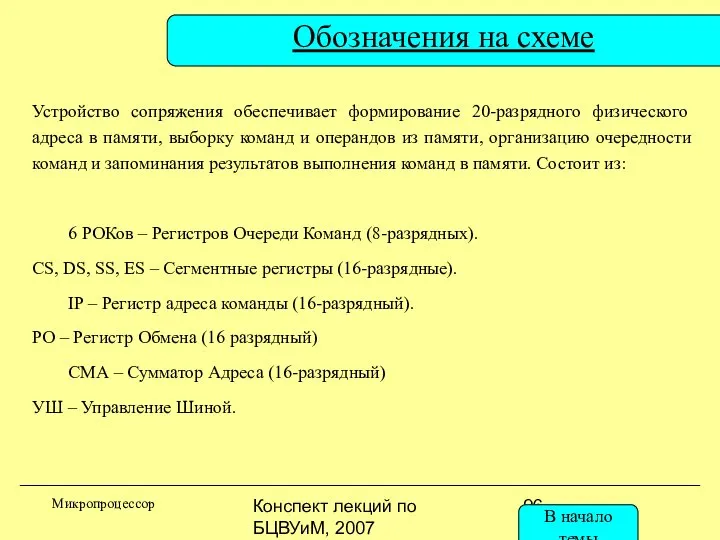

- 96. Конспект лекций по БЦВУиМ, 2007 Обозначения на схеме Микропроцессор Устройство сопряжения обеспечивает формирование 20-разрядного физического адреса

- 97. Конспект лекций по БЦВУиМ, 2007 Обозначения на схеме Микропроцессор Устройство Обработки предназначено для выполнения операций по

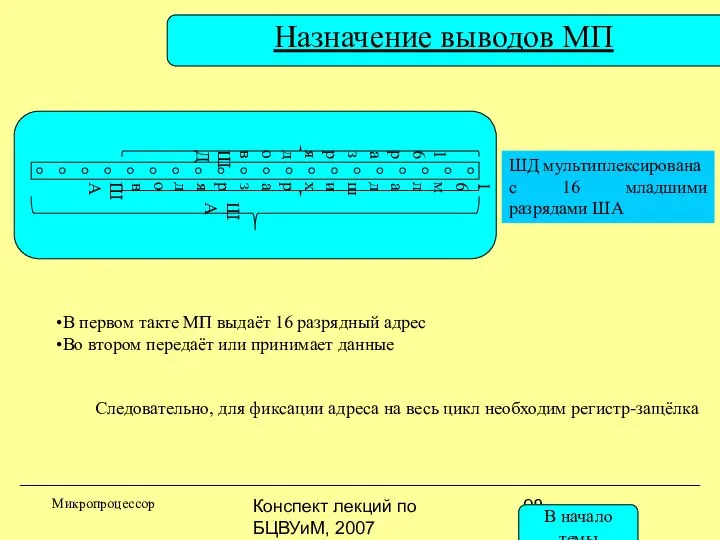

- 98. Конспект лекций по БЦВУиМ, 2007 Назначение выводов МП Микропроцессор 16 разрядов ШД 16 младших разрядов ША

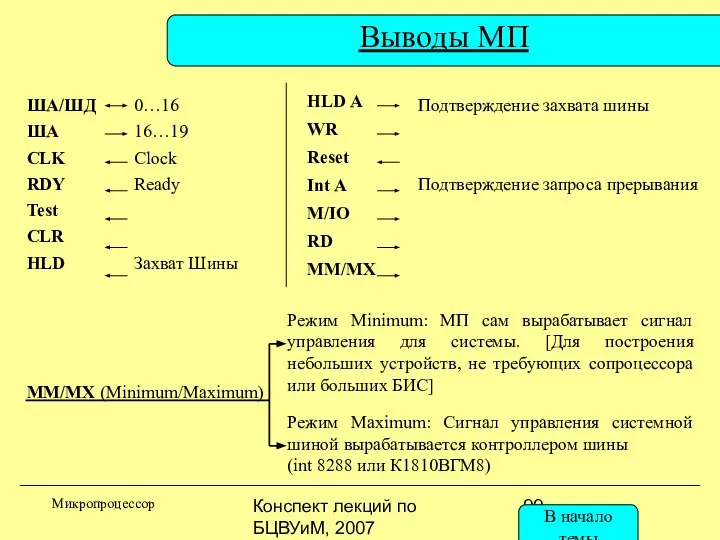

- 99. Конспект лекций по БЦВУиМ, 2007 Выводы МП Микропроцессор ША/ШД ША CLK RDY Test CLR HLD HLD

- 101. Скачать презентацию

Модель диагностики изменений Надлера и Ташмена Подготовили: студентки группы ДС04, Шунайлова Жанна и Епифанова Евгения

Модель диагностики изменений Надлера и Ташмена Подготовили: студентки группы ДС04, Шунайлова Жанна и Епифанова Евгения Этнический лоббизм

Этнический лоббизм Взвод в обороні

Взвод в обороні Plagiarism in Kazakhstan

Plagiarism in Kazakhstan Матч Украина-Латвия. Механизмы игры в футбол

Матч Украина-Латвия. Механизмы игры в футбол Презентация "Маэстро Гергиев - артист мира" - скачать презентации по МХК

Презентация "Маэстро Гергиев - артист мира" - скачать презентации по МХК Уголок психологической разгрузки «Маленькая страна» в подготовительной к школе группе № 12 Воспитатели: Алексеева Ольга Вла

Уголок психологической разгрузки «Маленькая страна» в подготовительной к школе группе № 12 Воспитатели: Алексеева Ольга Вла Казақстан ремпубликасынын конституциясы

Казақстан ремпубликасынын конституциясы Презентация "Питер Пауль Рубенс" - скачать презентации по МХК

Презентация "Питер Пауль Рубенс" - скачать презентации по МХК Надёжность оснований и строительных конструкций

Надёжность оснований и строительных конструкций Дисциплинированность - важнейшее качество личности военнослужащего внутренних войск МВД республики Беларусь

Дисциплинированность - важнейшее качество личности военнослужащего внутренних войск МВД республики Беларусь 4998f61117d196c76158f16d93ed1237

4998f61117d196c76158f16d93ed1237 Політичні конфлікти

Політичні конфлікти Презентация Понятие и значение института реабилитации в уголовном судопроизводстве. Основания и условия реабилитации.

Презентация Понятие и значение института реабилитации в уголовном судопроизводстве. Основания и условия реабилитации. ПАТОЛОГИЯ ЭНДОКРИННОЙ СИСТЕМЫ

ПАТОЛОГИЯ ЭНДОКРИННОЙ СИСТЕМЫ Лучевая диагностика заболеваний органов дыхания Основные заболевания Часть 1 Автор к.м.н. А.В.Шумаков

Лучевая диагностика заболеваний органов дыхания Основные заболевания Часть 1 Автор к.м.н. А.В.Шумаков  Профориентация в русле ФГОС нового поколения. Качурина Елена Юрьевна, педагог-психолог ГОУ СОШ № 328

Профориентация в русле ФГОС нового поколения. Качурина Елена Юрьевна, педагог-психолог ГОУ СОШ № 328 Цифровое меню для ресторанов Subway. Специальное предложение

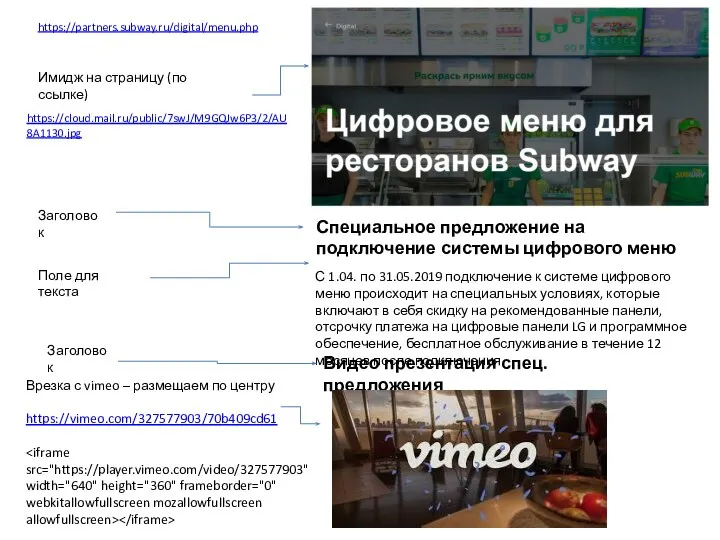

Цифровое меню для ресторанов Subway. Специальное предложение Механические характеристики электродвигателей постоянного тока

Механические характеристики электродвигателей постоянного тока Автомат Уилкса. Микропрограммное устройство

Автомат Уилкса. Микропрограммное устройство  Презентация Источники экологического права. Нормы экологического права

Презентация Источники экологического права. Нормы экологического права  Принцип действия радиотелефонной связи Радиовещание и телевидение .ppt

Принцип действия радиотелефонной связи Радиовещание и телевидение .ppt Судебно-медицинская экспертиза при повреждениях от воздействия тупых орудий

Судебно-медицинская экспертиза при повреждениях от воздействия тупых орудий Быстрый путь от стартапа до бизнеса 29 февраля 2012 Уральская Интернет Неделя

Быстрый путь от стартапа до бизнеса 29 февраля 2012 Уральская Интернет Неделя История Мезоамерика

История Мезоамерика  Государственное бюджетное дошкольное образовательное учреждение детский сад №27 Пушкинского района г.Санкт-Петербурга Реализа

Государственное бюджетное дошкольное образовательное учреждение детский сад №27 Пушкинского района г.Санкт-Петербурга Реализа Измерение аберраций оптических систем

Измерение аберраций оптических систем Кадровое делопроизводство

Кадровое делопроизводство