Содержание

- 2. Программные блоки VHDL Внутренняя архитектура (architecture) Внешнее представление (entity): Порт (входной) Порт (двунаправленный) Порт (выходной)

- 3. Блок Entity mode – направление портов: in - входной (данные поступают в блок из вне) out

- 4. Блок Architecture Architecture – архитектура модуля. Описывает внутреннюю реализацию. Возможно несколько реализаций одного и того же

- 5. Подключение внешних библиотек и пакетов Подключение библиотеки: LIBRARY library_name; library_name – имя подключаемой библиотеки Подключение пакетов

- 6. Элементы языка VHDL Комментарии . Начинаются с -- Идентификаторы. my_signal, My_Signal – одно и тоже. Нету

- 7. Использование signal в Architecture ARCHITECTURE OF IS SIGNAL clk: bit; BEGIN Concurrent Statements END ARCHITECTURE; Структура

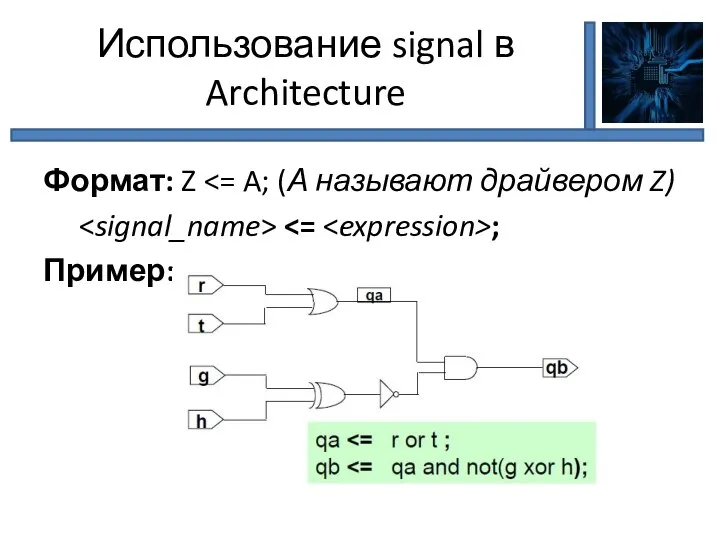

- 8. Использование signal в Architecture Формат: Z ; Пример:

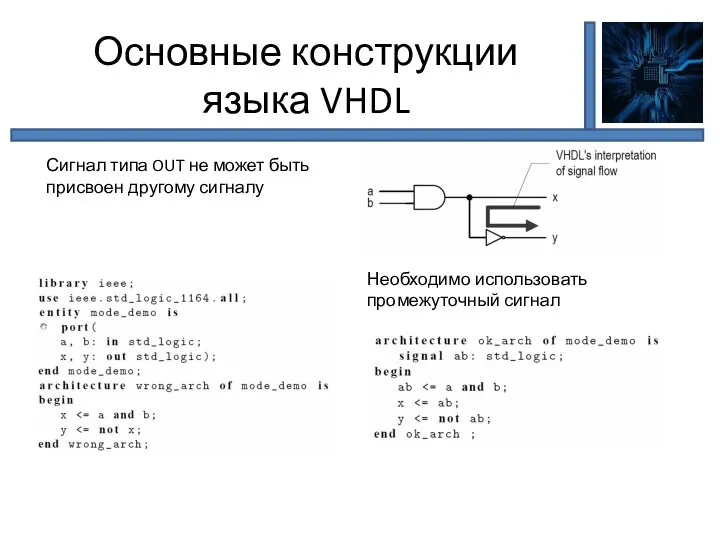

- 9. Основные конструкции языка VHDL Сигнал типа OUT не может быть присвоен другому сигналу Необходимо использовать промежуточный

- 10. Пример задания архитектуры

- 11. Использование сигналов

- 12. Типы данных VHDL Integer: от (-231-1) до (231-1). Представляется как 32-х битный массив Bollean : (true,

- 13. Задание диапазона RANGE–задает диапазон изменения индексов в массиве Диапазон может быть задан: –ввозрастающей последовательности (ascending) RANGE

- 14. Одинаково или нет?

- 15. Операторы VHDL

- 16. Операторы VHDL

- 17. Приоритеты операторов Пример: a + b > c or a Скобки: a + b + c

- 18. Арифметический сдвиг sla, sra sla - сдвиг влево. sra - сдвиг вправо. Размножается младший разряд Размножается

- 19. Присвоение значения массиву signal a: std_logic_vector (7 downto 0); a Позиционная привязка: a Привязка по имени:

- 20. Преобразование типов Пакет std_logic_1164 to_bitvector – преобразование из std_logic_vector в bit_vector to_stdlogicvector – преобразование из bit_vector

- 21. Схема определения четности

- 22. Схема определения четности

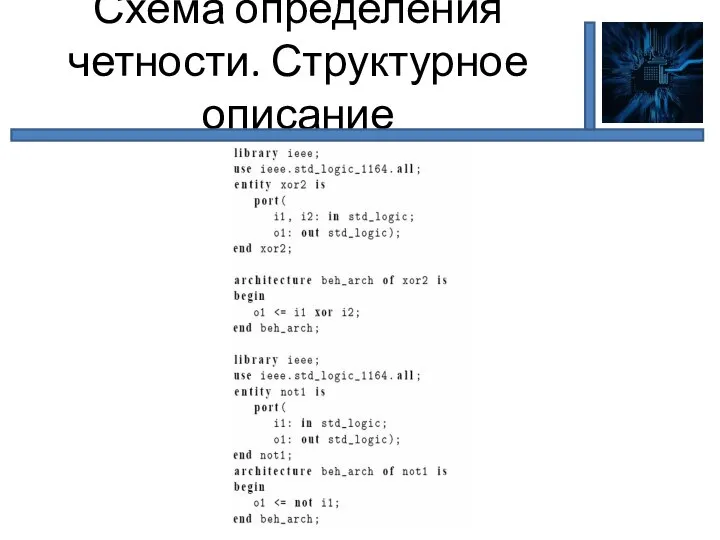

- 23. Схема определения четности. Структурное описание

- 24. Схема определения четности. Структурное описание

- 25. Схема определения четности. Структурное описание

- 26. Практика Полусумматор: Элемент сумматора:

- 27. Сумматор Задание: написать сумматор, изображённый на схеме. В итоге должно быть три файла: half_adder.vhd (полусумматор), full_adder_1.vhd

- 28. Моделирование. Добавление элемента -- Instantiate the Unit Under Test (UUT) uut: comb_02_adder PORT MAP ( switch_in

- 29. Моделирование процесс задания сигналов switch_in -- Stimulus process stim_proc: process begin A B wait for 100

- 30. Моделирование Задание: написать testbench (adder_1_tb.vhd) для 8-ми битного сумматора

- 31. Реализация сумматора на плате Atlys Создайте проект для реализации сумматора: входы к переключателям, а выходы –

- 32. Входы # onBoard switch NET "switch_in " LOC = "A10"; NET "switch_in " LOC = "D14";

- 33. Выходы # onBoard leds_outs NET "leds_out " LOC = "U18"; NET "leds_out " LOC = "M14";

- 35. Скачать презентацию

Система энергообеспечения клетки

Система энергообеспечения клетки  Компьютер – исполнитель алгоритмов

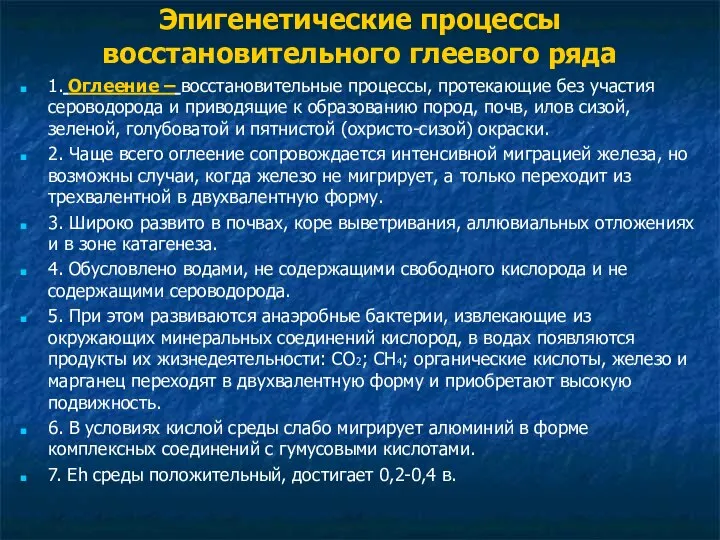

Компьютер – исполнитель алгоритмов Эпигенетические процессы восстановительного глеевого ряда

Эпигенетические процессы восстановительного глеевого ряда Терапия острой и хронической печеночной недостаточности С.Б.Ляпустин 20.10.11.

Терапия острой и хронической печеночной недостаточности С.Б.Ляпустин 20.10.11.  Проект модернизации поста текущего ремонта, агрегатов для СТО

Проект модернизации поста текущего ремонта, агрегатов для СТО Καισάρεια Καππαδοκίας. τα Θεμέλια της Τριαδικότητας του Θεού

Καισάρεια Καππαδοκίας. τα Θεμέλια της Τριαδικότητας του Θεού Поляризация волн

Поляризация волн Динамика развития лоббистских технологий в России

Динамика развития лоббистских технологий в России Оборудование транспорта АТУ системой мониторинга транспорта

Оборудование транспорта АТУ системой мониторинга транспорта Обмен веществ и энергии

Обмен веществ и энергии отчет Лолита

отчет Лолита Центрально-растянутые элементы

Центрально-растянутые элементы Аналитическая машина

Аналитическая машина Презентация Северо-Западное таможенное управление

Презентация Северо-Западное таможенное управление Применение граната в абразивно-струйной очистке поверхности

Применение граната в абразивно-струйной очистке поверхности «Переменка». Разработка программного продукта в среде Delphi 7

«Переменка». Разработка программного продукта в среде Delphi 7 Диспансеризация и реабилитация терапевтических больных

Диспансеризация и реабилитация терапевтических больных РАСЧЁТ ТРЁХШАРНИРНЫХ СИСТЕМ

РАСЧЁТ ТРЁХШАРНИРНЫХ СИСТЕМ Проектирование систем автоматизации. Проектная компоновка УВК. (Модуль 5)

Проектирование систем автоматизации. Проектная компоновка УВК. (Модуль 5) ПЕЧАТНЫЕ КРАСКИ

ПЕЧАТНЫЕ КРАСКИ Вирусные гепатиты

Вирусные гепатиты  Иероглифы

Иероглифы Пунктограми при відокремлених другорядних членах речення

Пунктограми при відокремлених другорядних членах речення priroda_v_opasnosti1

priroda_v_opasnosti1 Строительные конструкции. Расчет прочности сжатых элементов. (Лекция 3)

Строительные конструкции. Расчет прочности сжатых элементов. (Лекция 3) Shisha bar

Shisha bar Презентация на тему "Связь универсальных учебных действий с учебными предметами" - скачать презентации по Педагогике

Презентация на тему "Связь универсальных учебных действий с учебными предметами" - скачать презентации по Педагогике Анализ программы и учебников Е.В.Чудиновой

Анализ программы и учебников Е.В.Чудиновой