Содержание

- 2. Литература для изучения материала Таненбаум «Архитектура компьютера» Поворознюк «Архитектура компьютеров» в2-х частях Цилькер, Орлов «Организация ЭВМ

- 3. Принцип работы устройства управления

- 4. Способы адресации информации Способом адресации называется механизм получения исполнительного адреса из исходного. Применение различных способов адресации

- 5. Способы адресации информации Непосредственная адресация – способ адресации, при котором в адресном поле команды размещается сам

- 6. Классификация устройств управления Функциональная ориентация – универсальные УУ, специализированные УУ; Принцип организации цикла выполнения команды –

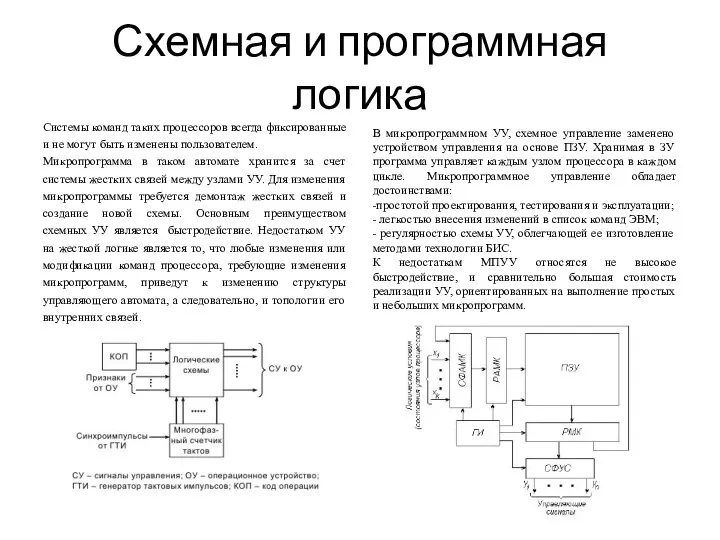

- 7. Схемная и программная логика Системы команд таких процессоров всегда фиксированные и не могут быть изменены пользователем.

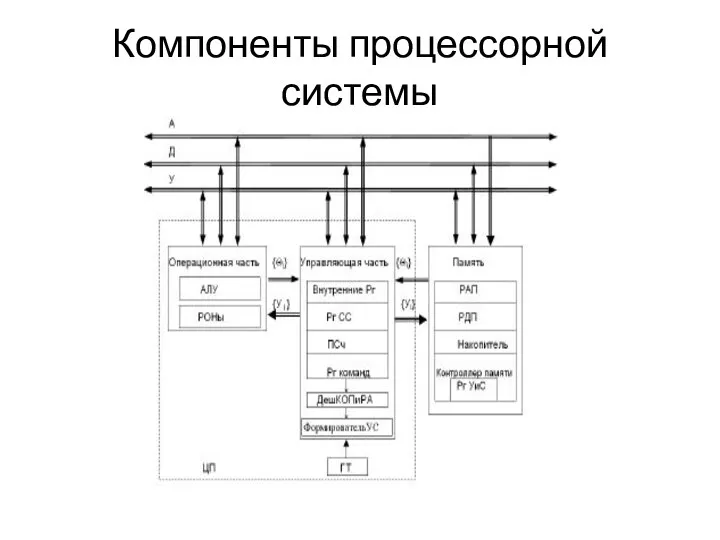

- 8. Компоненты процессорной системы

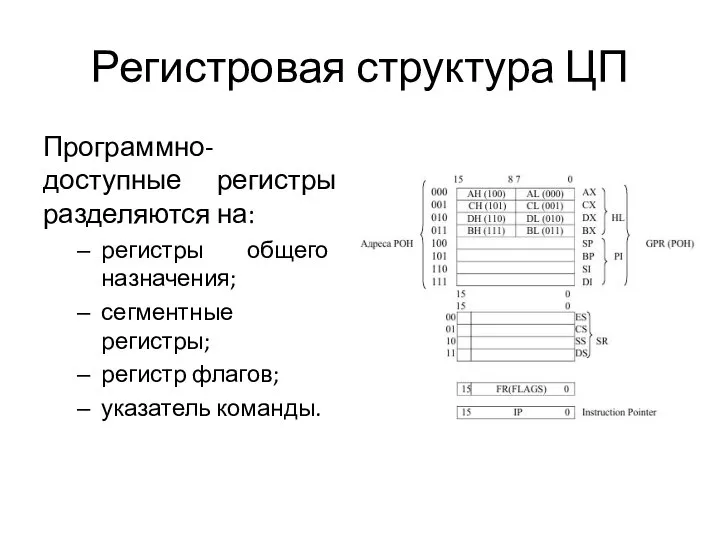

- 9. Регистровая структура ЦП Программно-доступные регистры разделяются на: регистры общего назначения; сегментные регистры; регистр флагов; указатель команды.

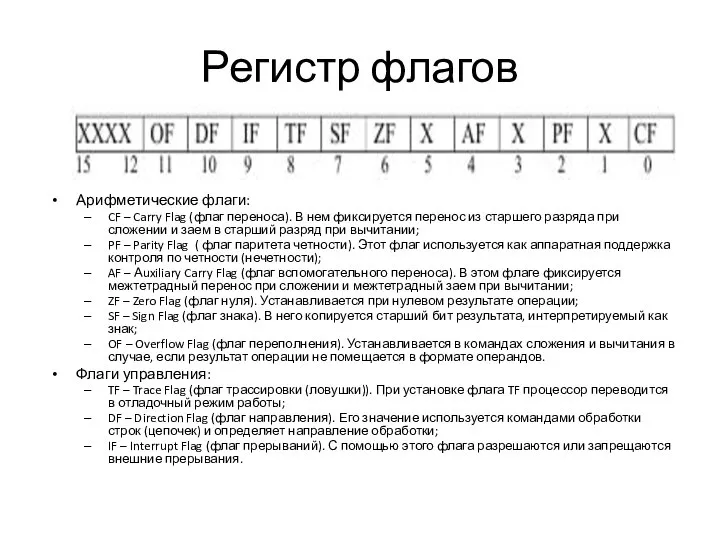

- 10. Регистр флагов Арифметические флаги: CF – Carry Flag (флаг переноса). В нем фиксируется перенос из старшего

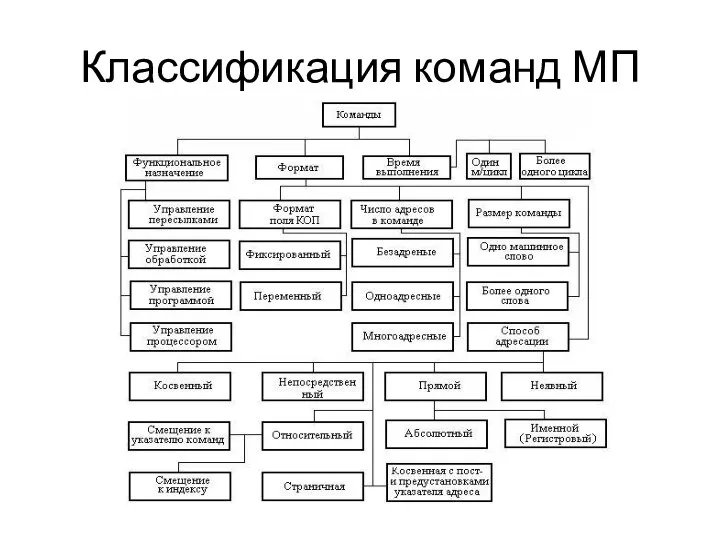

- 11. Классификация команд МП

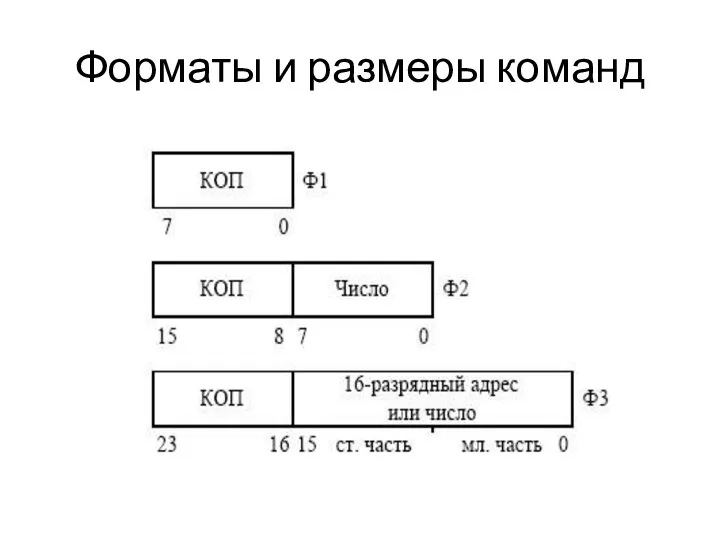

- 12. Форматы и размеры команд

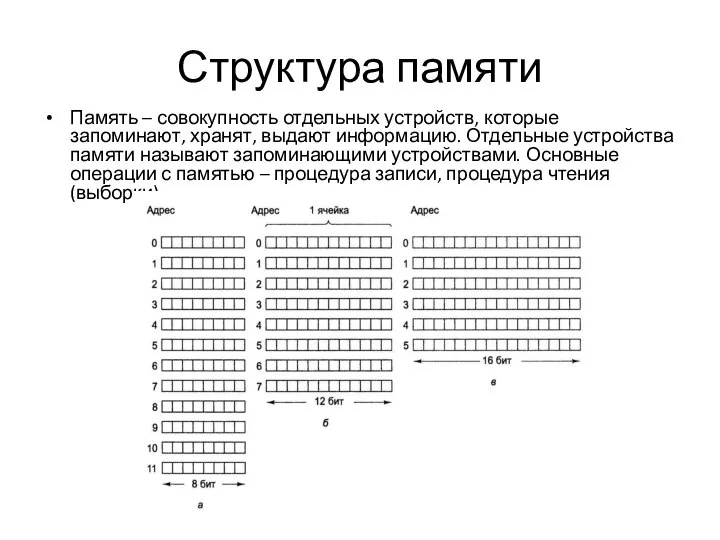

- 13. Структура памяти Память – совокупность отдельных устройств, которые запоминают, хранят, выдают информацию. Отдельные устройства памяти называют

- 14. Структура памяти Под физической ОП понимают конкретное физическое устройство памяти, адресация в котором осуществляется в соответствии

- 15. Методы доступа к памяти Последовательный доступ - информация хранится в виде последовательности блоков данных, называемых записями.

- 16. Иерархическая структура памяти

- 17. Иерархическая структура памяти Имеется несколько иерархических уровней хранения организованной в блоки информации. Иерархические уровни памяти отличаются

- 18. Основные параметры памяти Быстродействие памяти определяется временем выполнения операций записи и считывания данных. Для количественной оценки

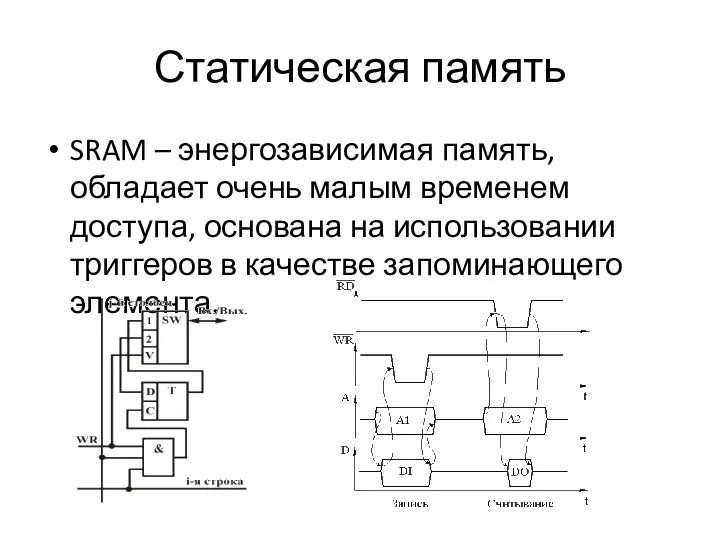

- 19. Статическая память SRAM – энергозависимая память, обладает очень малым временем доступа, основана на использовании триггеров в

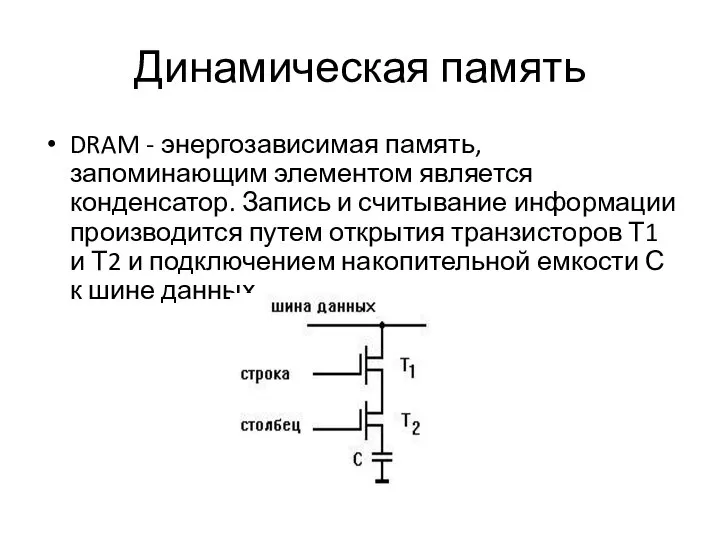

- 20. Динамическая память DRAM - энергозависимая память, запоминающим элементом является конденсатор. Запись и считывание информации производится путем

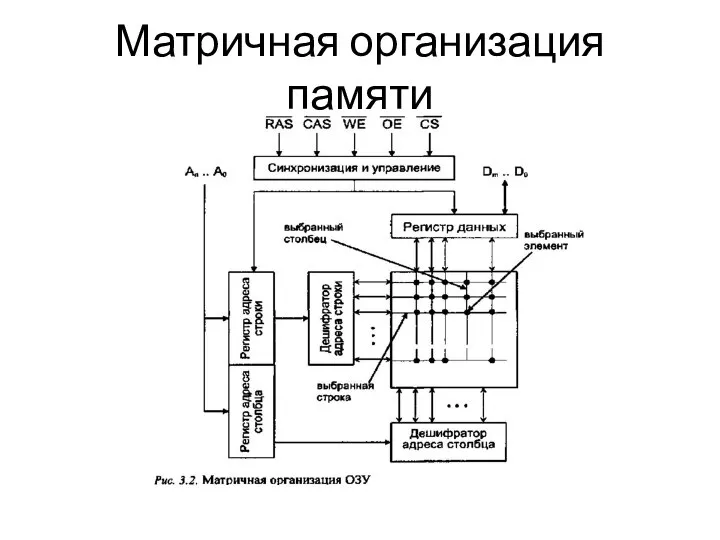

- 21. Матричная организация памяти

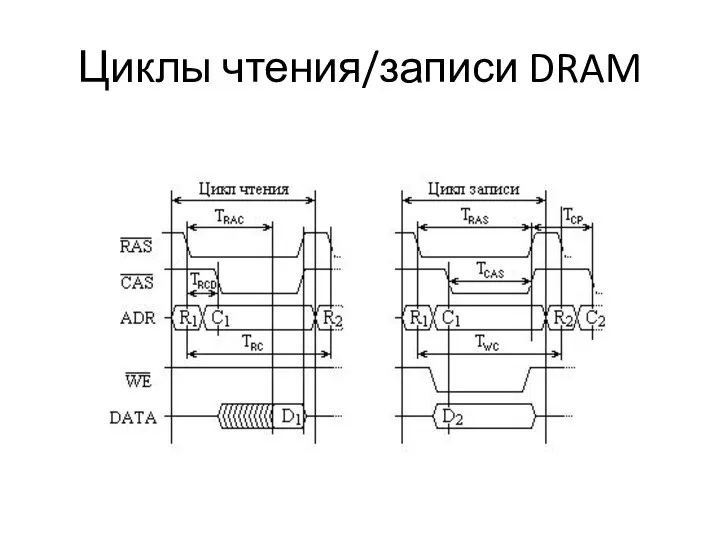

- 22. Циклы чтения/записи DRAM

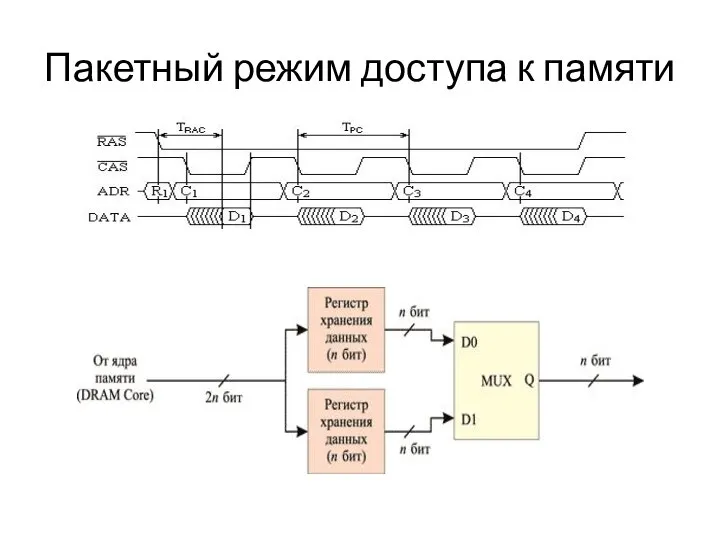

- 23. Пакетный режим доступа к памяти

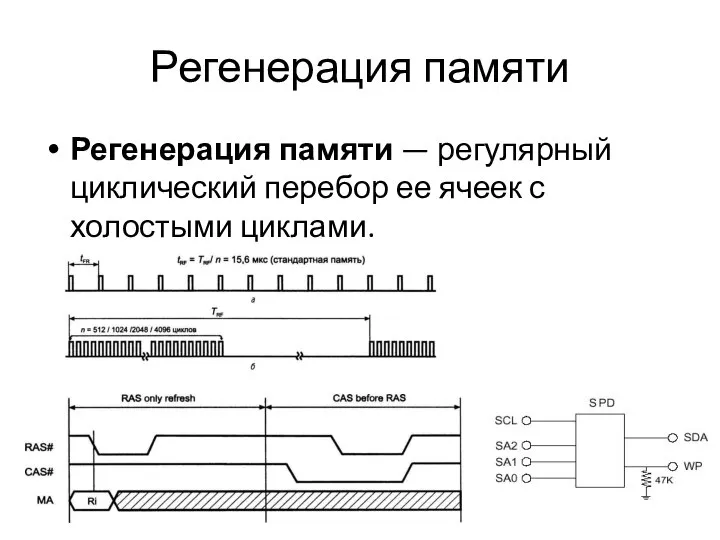

- 24. Регенерация памяти Регенерация памяти — регулярный циклический перебор ее ячеек с холостыми циклами.

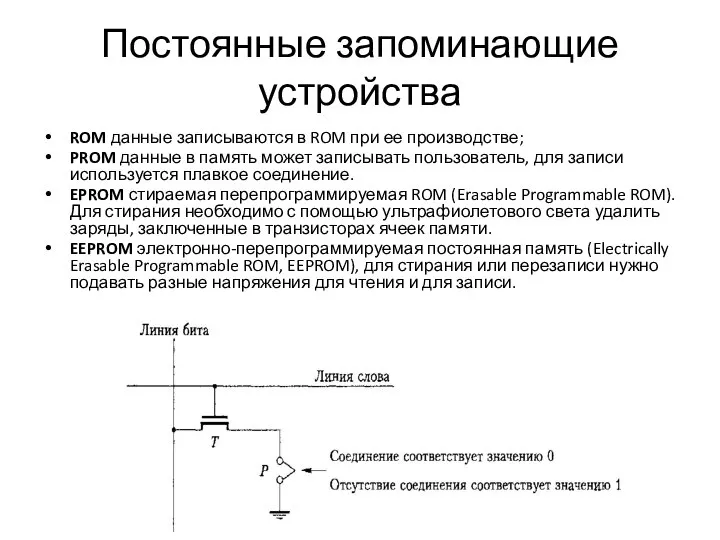

- 25. Постоянные запоминающие устройства ROM данные записываются в ROM при ее производстве; PROM данные в память может

- 26. Стековая память При занесении в стек очередного слова происходит следующее: УС:= УС -1; ОП[(УС)]:=ШД. При извлечении

- 27. Ассоциативная память

- 28. Кэш-память Параметры кэш-памяти: размер строки; способ отображения основной памяти на кэш-память; алгоритм замещения информации в заполненной

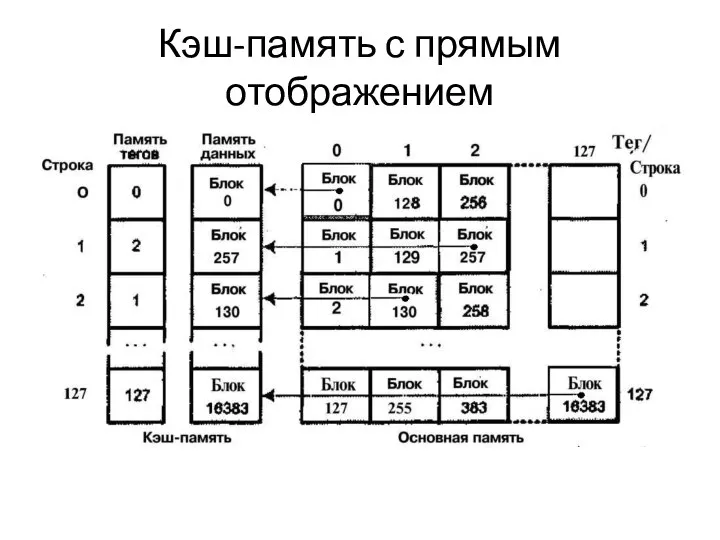

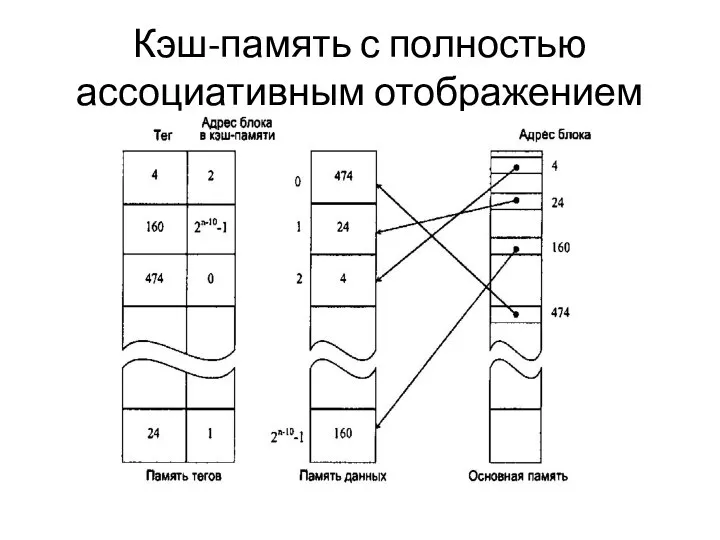

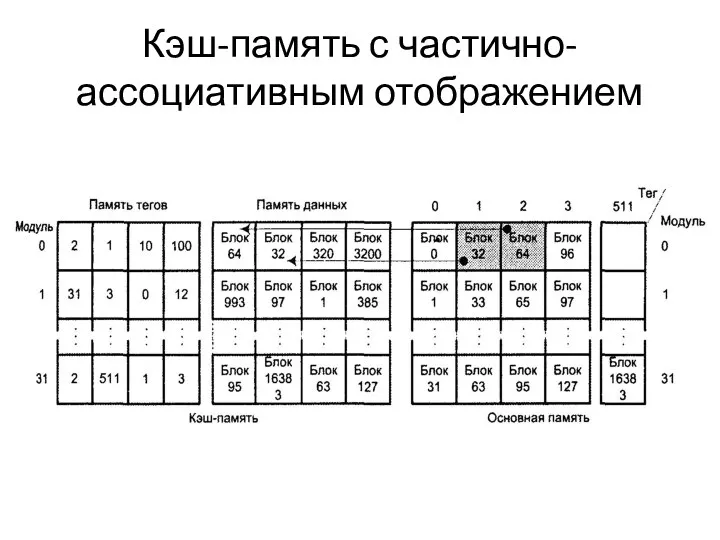

- 29. Кэш-память с прямым отображением

- 30. Кэш-память с полностью ассоциативным отображением

- 31. Кэш-память с частично-ассоциативным отображением

- 32. Алгоритмы замещения кэш-памяти Алгоритм наиболее давнего использования (LRU); Алгоритм работающий по принципу «первый вошел, первый вышел»

- 34. Скачать презентацию

Роль показателей в реализации статистических методов изучения правонарушений

Роль показателей в реализации статистических методов изучения правонарушений Разработка гастрономического тура выходного дня в Таджикистане

Разработка гастрономического тура выходного дня в Таджикистане Vorbereitung für die kontrollarbeit (2)

Vorbereitung für die kontrollarbeit (2) Экономические показатели предприятия

Экономические показатели предприятия  Артикуляционный отдел

Артикуляционный отдел  Современная деревянная архитектура и традиции

Современная деревянная архитектура и традиции Микрофлора организма человека

Микрофлора организма человека «Практика применения вывозных таможенных пошлин (на примере нефти сырой и нефтепродуктов» Выполнили студенты 3 курса Гр.

«Практика применения вывозных таможенных пошлин (на примере нефти сырой и нефтепродуктов» Выполнили студенты 3 курса Гр.  Культура Месопотамии

Культура Месопотамии Место и роль динамической метеорологии

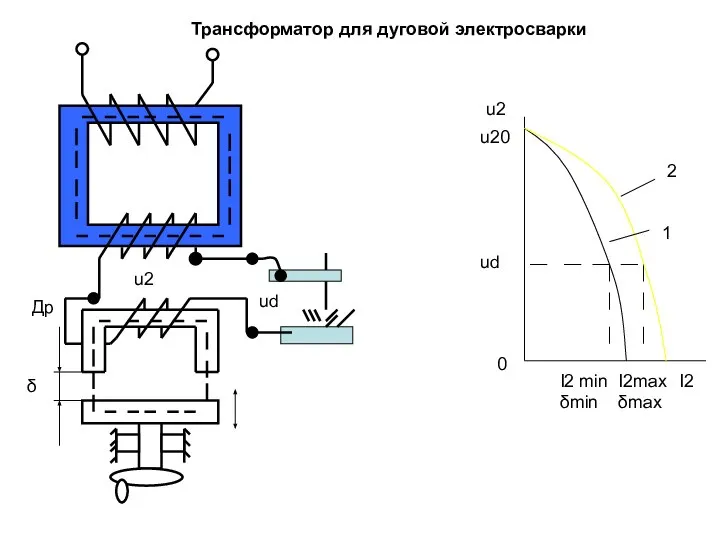

Место и роль динамической метеорологии  Трансформатор для дуговой электросварки

Трансформатор для дуговой электросварки  Спеціалізований туризм. Екстремальний туризм

Спеціалізований туризм. Екстремальний туризм ПОДГОТОВКА К ПЕДАГОГИЧЕСКОЙ ДЕЯТЕЛЬНОСТИ ПРЕПОДАВАТЕЛЕЙ В ММА им. И.М. Сеченова

ПОДГОТОВКА К ПЕДАГОГИЧЕСКОЙ ДЕЯТЕЛЬНОСТИ ПРЕПОДАВАТЕЛЕЙ В ММА им. И.М. Сеченова  Школьный кошелек. Оплата питания в школе без проблем

Школьный кошелек. Оплата питания в школе без проблем История футбола

История футбола Презентация Соление рыбы. Мороженная рыба.

Презентация Соление рыбы. Мороженная рыба. выполнил: студентка 13 гр. филологич.фак-та Савинова Татьяна проверил: Шереметьева О. А.

выполнил: студентка 13 гр. филологич.фак-та Савинова Татьяна проверил: Шереметьева О. А. Всемирное наследие в России

Всемирное наследие в России Файлы

Файлы Наноэлектроника. Физические основы. Методы формирования наноразмерных структур. Перенос носителей заряда

Наноэлектроника. Физические основы. Методы формирования наноразмерных структур. Перенос носителей заряда Пословицы и поговорки как выражение народной мудрости

Пословицы и поговорки как выражение народной мудрости НАДЕЛЕНИЕ ОРГАНОВ МЕСТНОГО САМОУПРАВЛЕНИЯ ОТДЕЛЬНЫМИ ГОСУДАРСТВЕННЫМИ ПОЛНОМОЧИЯМИ

НАДЕЛЕНИЕ ОРГАНОВ МЕСТНОГО САМОУПРАВЛЕНИЯ ОТДЕЛЬНЫМИ ГОСУДАРСТВЕННЫМИ ПОЛНОМОЧИЯМИ Мышечная ткань

Мышечная ткань Тренер в Зеленограде. Самбо. Дзюдо. Джиу-джитсу. ММА. Бокс. Художественная гимнастика. Самооборона. Йога

Тренер в Зеленограде. Самбо. Дзюдо. Джиу-джитсу. ММА. Бокс. Художественная гимнастика. Самооборона. Йога Любовь

Любовь Об особенностях финансовой поддержки экспорта услуг Подготовил Ивантей М. группа Т-093

Об особенностях финансовой поддержки экспорта услуг Подготовил Ивантей М. группа Т-093  Презентация "Оборудование предприятий" - скачать презентации по Экономике

Презентация "Оборудование предприятий" - скачать презентации по Экономике Жизнь средневекового человека

Жизнь средневекового человека