Стенд для моделирования объектов и обучения представителей заказчика. НПП «Преобразователь-комплекс»

Содержание

- 2. «НПП «Преобразователь-комплекс» Назначение: моделирование объекта регулирования (ДПТ, СД, ШБМ-СГ) для исследования свойств и поведения СУ при

- 3. «НПП «Преобразователь-комплекс» Структура стенда: Модель объекта в «железе» Настольный ПК СУ (на базе СМ3) Пульт с

- 4. «НПП «Преобразователь-комплекс» Состав стенда: модель объекта в «железе» представляет собой блок с DSP-контроллером или ПЛИС; ПК

- 5. «НПП «Преобразователь-комплекс» Функции блока с быстродействующей системой-«моделью»: реализация математической модели: а) ДПТ с имитацией нагрузки; б)

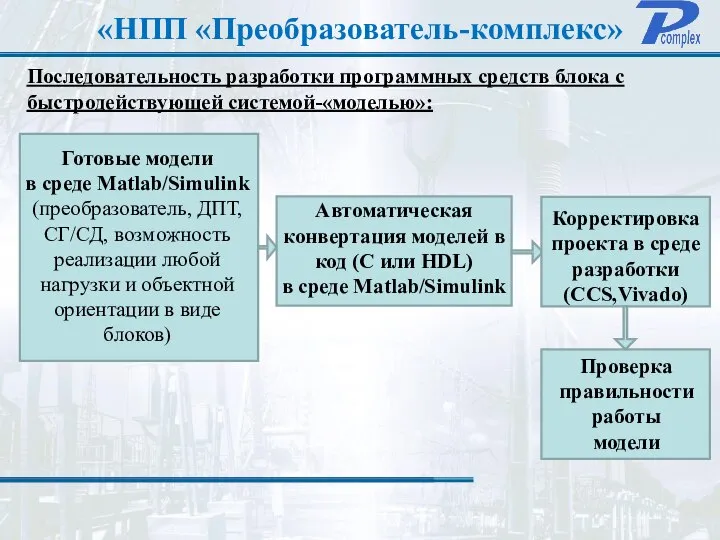

- 6. «НПП «Преобразователь-комплекс» Последовательность разработки программных средств блока с быстродействующей системой-«моделью»: Готовые модели в среде Matlab/Simulink (преобразователь,

- 7. «НПП «Преобразователь-комплекс» Аппаратная реализация блока с быстродействующей системой- «моделью»: На базе DSP-контроллера TMS320F2812 (Texas Instruments). На

- 8. «НПП «Преобразователь-комплекс» ДА TMS320F2812 ПЛИС Xilinx Возможная аппаратная реализация НЕТ JTAG-отладчик Существующий отладочный комплект Наличие СУ

- 9. «НПП «Преобразователь-комплекс» Начальные этапы разработки блока на базе ПЛИС: Изучение правил создания модели в среде Matlab

- 11. Скачать презентацию

Экономичность проектных решений жилых зданий

Экономичность проектных решений жилых зданий Family and relations 1

Family and relations 1 Halloween. Ogtober, 31

Halloween. Ogtober, 31 СИСТЕМЫ АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ.

СИСТЕМЫ АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ. Ливарні шедеври

Ливарні шедеври Мастер-класс. Создание онлайн курсов с помощью STEPIK.ORG

Мастер-класс. Создание онлайн курсов с помощью STEPIK.ORG Системы уравнений Методы решений

Системы уравнений Методы решений Общие представления о языке Java. Интегрированная среда разработки NetBeans

Общие представления о языке Java. Интегрированная среда разработки NetBeans Современные особенности подходов к управлению

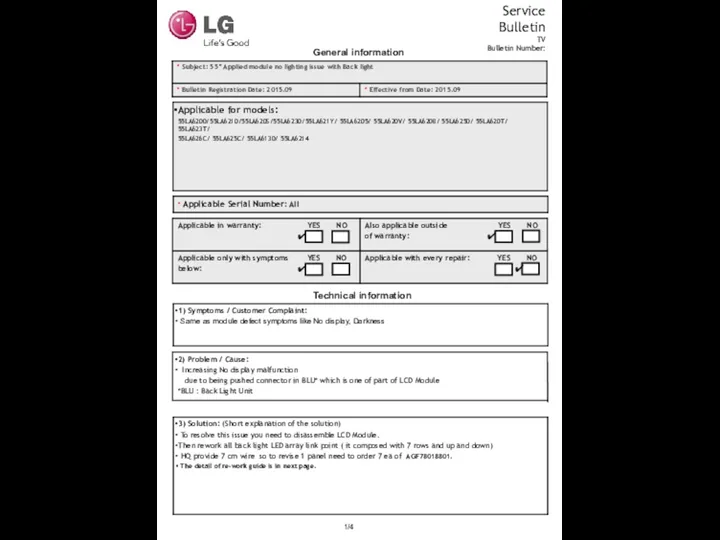

Современные особенности подходов к управлению Service Bulletin. General information TV

Service Bulletin. General information TV Быть спортивным – модно!

Быть спортивным – модно! Назначение, подходы и этапы проектирования БД. Модели многоуровневой архитектуры систем баз данных.

Назначение, подходы и этапы проектирования БД. Модели многоуровневой архитектуры систем баз данных.  Налоговое право Абдрашитова Ю.В., учитель истории и обществознания МОУ СОШ № 17 г. Твери

Налоговое право Абдрашитова Ю.В., учитель истории и обществознания МОУ СОШ № 17 г. Твери Методика курса Психология и Педагогика

Методика курса Психология и Педагогика Логопедический массаж в комплексной системе преодоления речевых расстройств. Практикум «Мастер-Класс» по логопедиче

Логопедический массаж в комплексной системе преодоления речевых расстройств. Практикум «Мастер-Класс» по логопедиче Осетия. Обычаи осетинского народа

Осетия. Обычаи осетинского народа Основные виды политических идеологий

Основные виды политических идеологий Гражданские правоотношения

Гражданские правоотношения Патофизиология печени

Патофизиология печени  Системный анализ как методология решения проблем

Системный анализ как методология решения проблем сувенир своими руками МАСТЕР-КЛАСС ПО ИЗГОТОВЛЕНИЮ ПЕНДИБУЛЯ

сувенир своими руками МАСТЕР-КЛАСС ПО ИЗГОТОВЛЕНИЮ ПЕНДИБУЛЯ Ремонт деталей пластическим деформированием

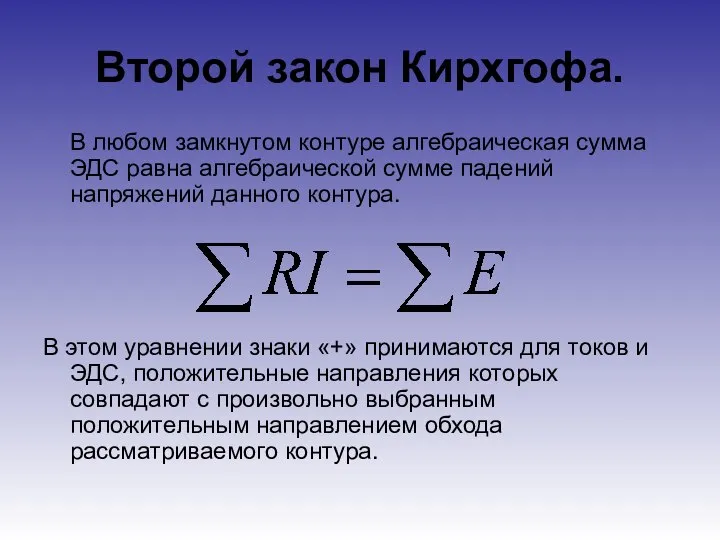

Ремонт деталей пластическим деформированием Второй закон Кирхгофа

Второй закон Кирхгофа Управление моделями в UML

Управление моделями в UML Види і категорії легкоатлетичних змагань

Види і категорії легкоатлетичних змагань Оцинкованный профнастил (профилированный лист)

Оцинкованный профнастил (профилированный лист) Формы и виды социальной ответственности современного бизнеса

Формы и виды социальной ответственности современного бизнеса Тени. Общие положения. Чертежи пространственных фигур. (Лекция 12)

Тени. Общие положения. Чертежи пространственных фигур. (Лекция 12)