Содержание

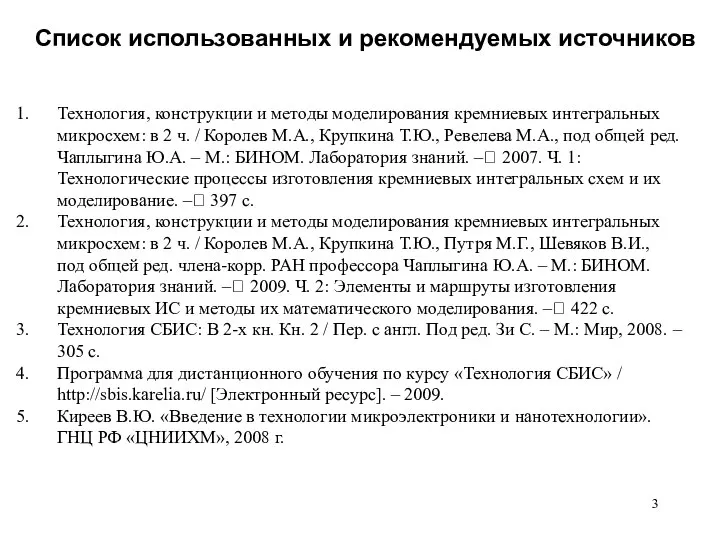

- 3. Список использованных и рекомендуемых источников Технология, конструкции и методы моделирования кремниевых интегральных микросхем: в 2 ч.

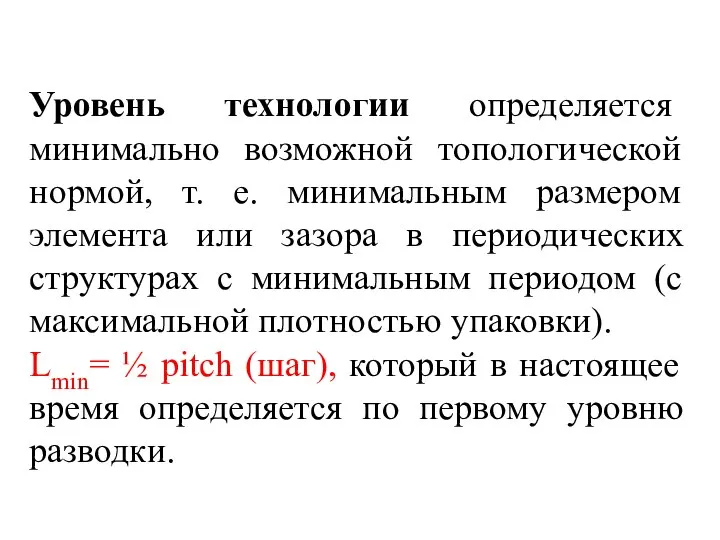

- 4. Уровень технологии определяется минимально возможной топологической нормой, т. е. минимальным размером элемента или зазора в периодических

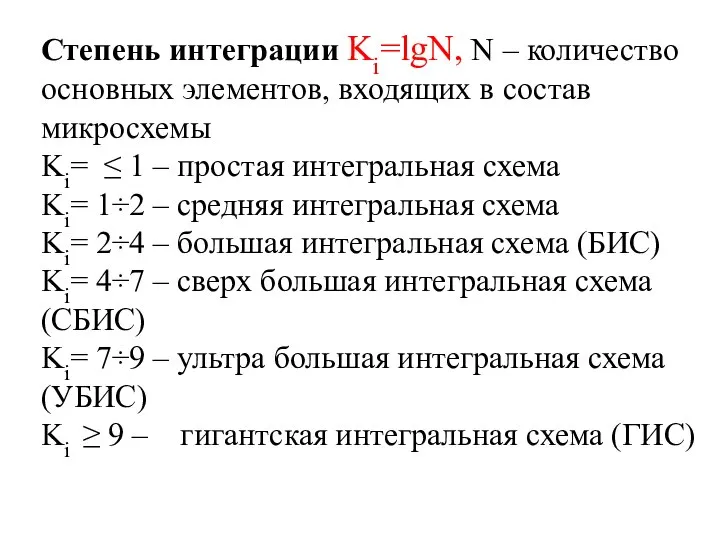

- 5. Степень интеграции Ki=lgN, N – количество основных элементов, входящих в состав микросхемы Ki= ≤ 1 –

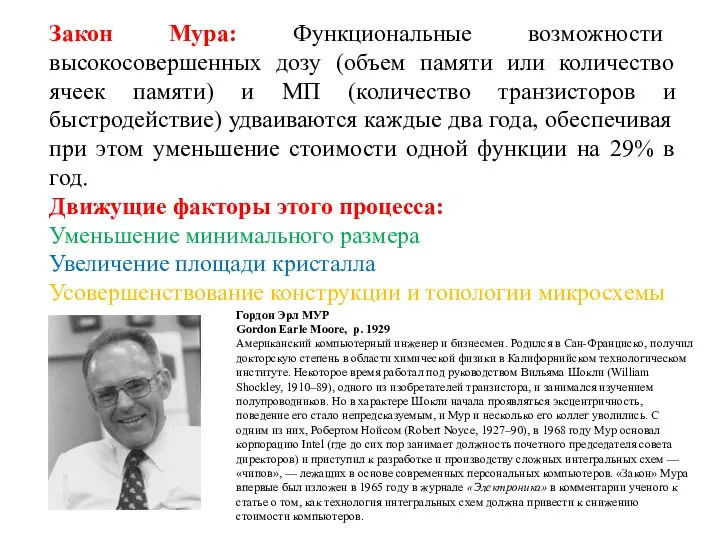

- 6. Закон Мура: Функциональные возможности высокосовершенных дозу (объем памяти или количество ячеек памяти) и МП (количество транзисторов

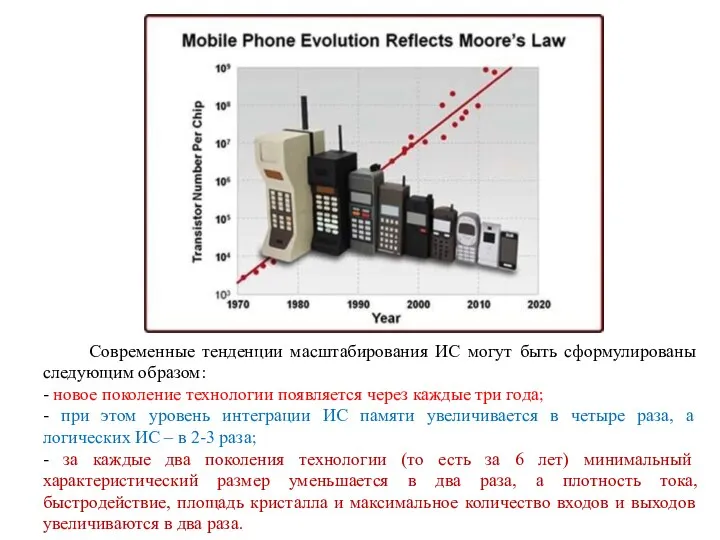

- 7. Современные тенденции масштабирования ИС могут быть сформулированы следующим образом: - новое поколение технологии появляется через каждые

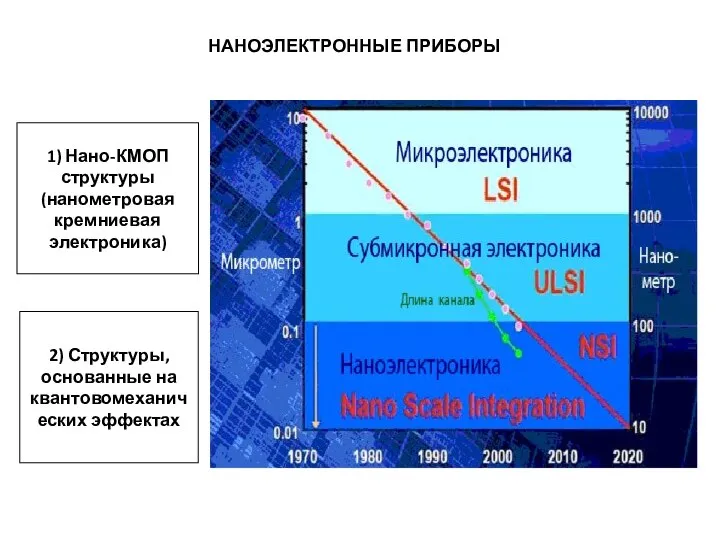

- 8. НАНОЭЛЕКТРОННЫЕ ПРИБОРЫ 2) Структуры, основанные на квантовомеханических эффектах 1) Нано-КМОП структуры (нанометровая кремниевая электроника)

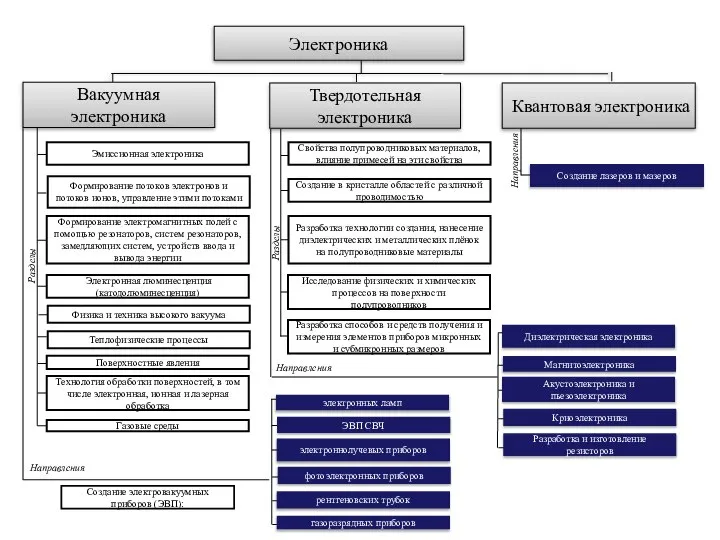

- 9. Электроника Вакуумная электроника Твердотельная электроника Квантовая электроника НАНО * 10-9

- 10. Электроника Квантовая электроника Создание электровакуумных приборов (ЭВП): Акустоэлектроника и пьезоэлектроника Разработка и изготовление резисторов Криоэлектроника Магнитоэлектроника

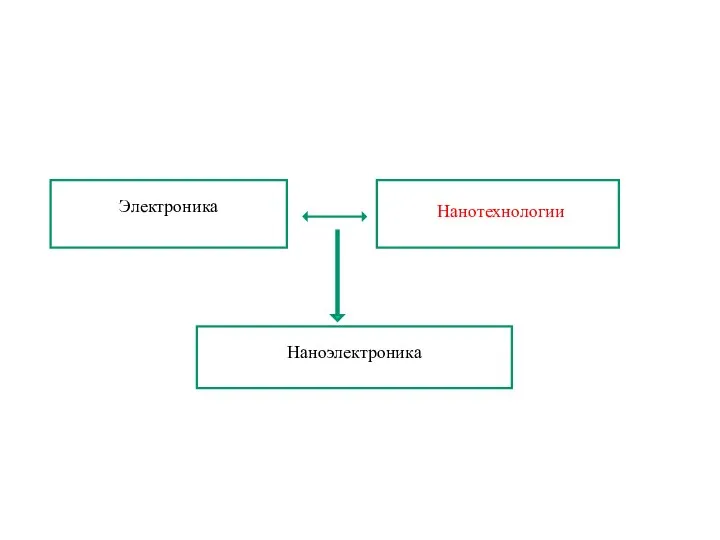

- 11. Электроника Нанотехнологии Наноэлектроника

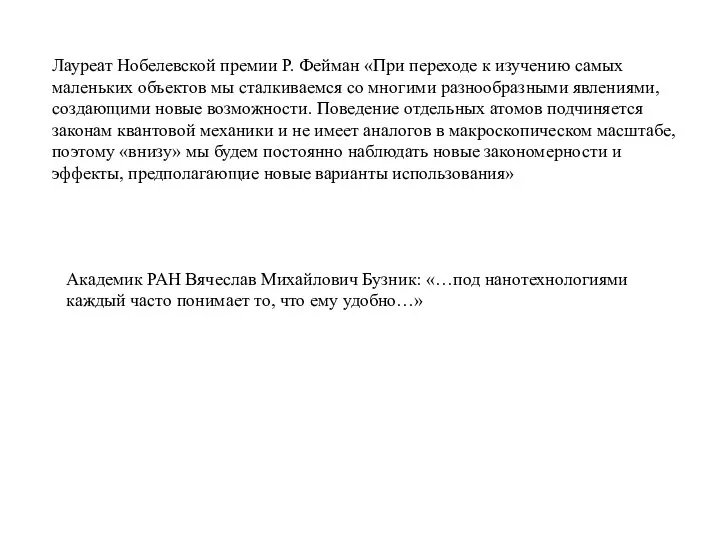

- 12. Лауреат Нобелевской премии Р. Фейман «При переходе к изучению самых маленьких объектов мы сталкиваемся со многими

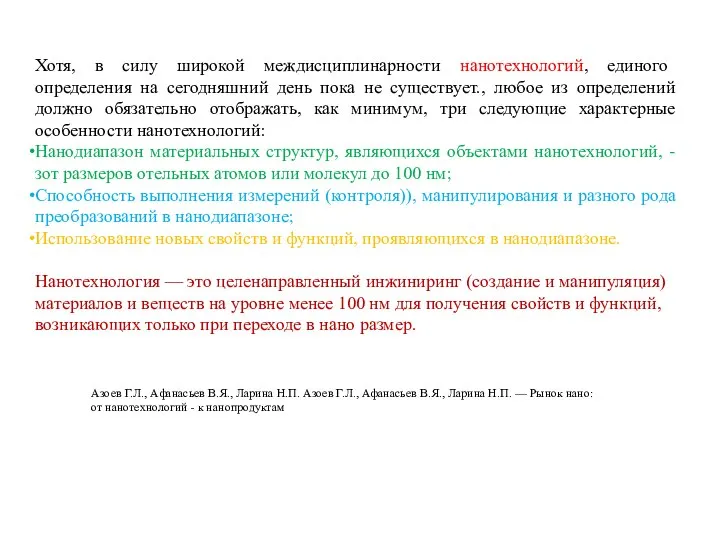

- 13. Хотя, в силу широкой междисциплинарности нанотехнологий, единого определения на сегодняшний день пока не существует., любое из

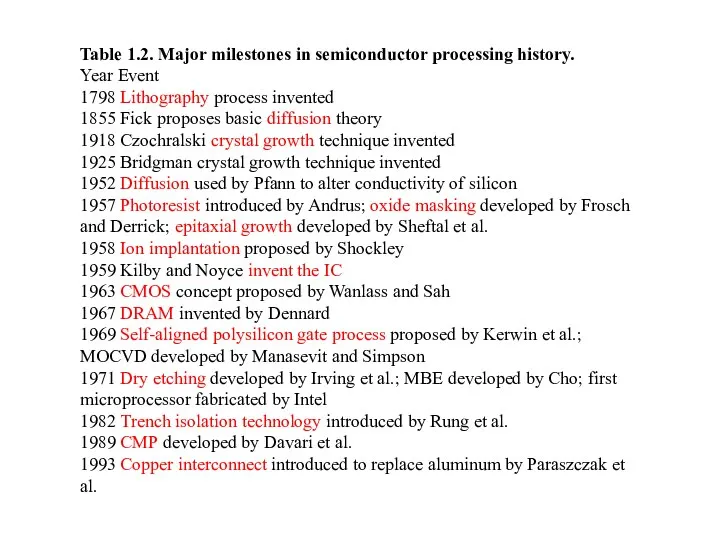

- 14. Table 1.2. Major milestones in semiconductor processing history. Year Event 1798 Lithography process invented 1855 Fick

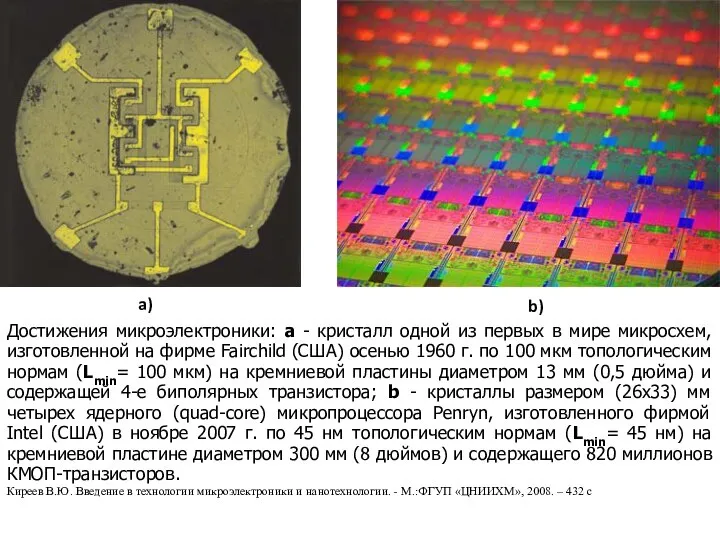

- 15. Достижения микроэлектроники: a - кристалл одной из первых в мире микросхем, изготовленной на фирме Fairchild (США)

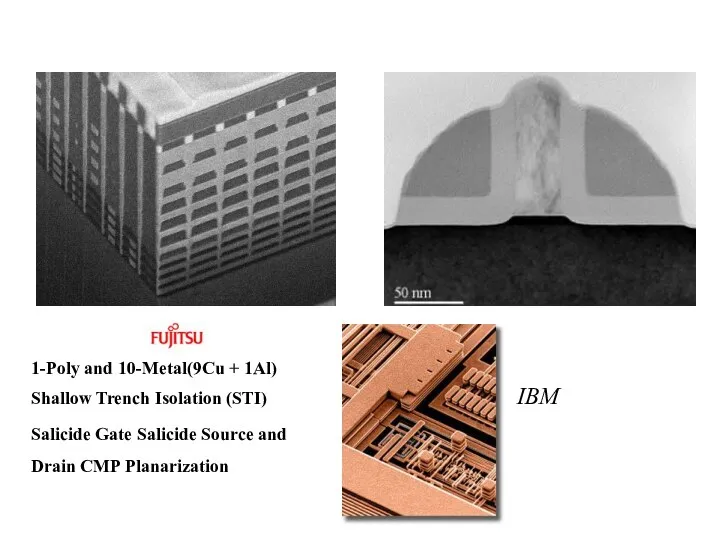

- 16. 1-Poly and 10-Metal(9Cu + 1Al) Shallow Trench Isolation (STI) Salicide Gate Salicide Source and Drain CMP

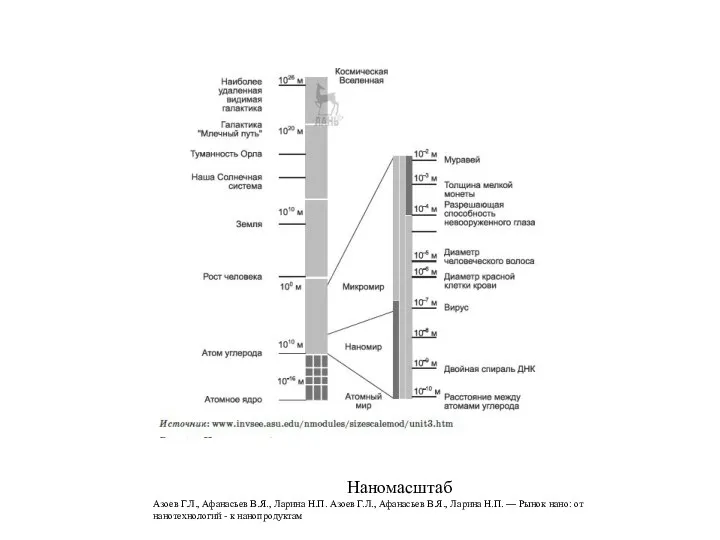

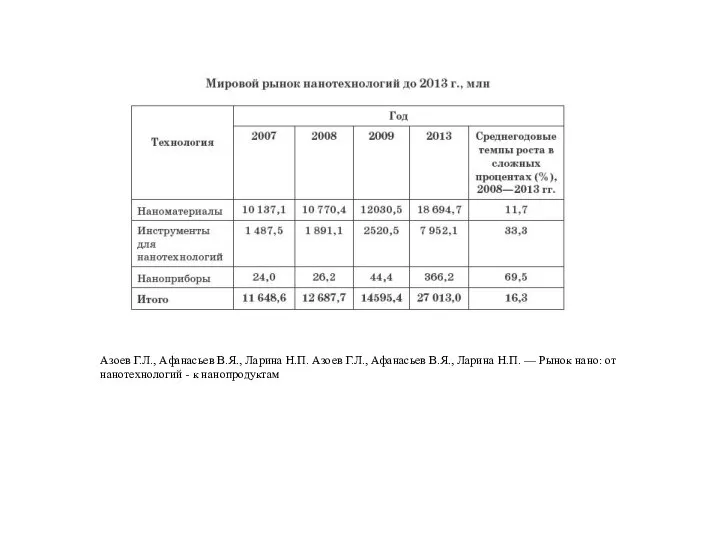

- 18. Наномасштаб Азоев Г.Л., Афанасьев В.Я., Ларина Н.П. Азоев Г.Л., Афанасьев В.Я., Ларина Н.П. — Рынок нано:

- 19. Что производит наноэлектроника

- 20. Вся продукция микро-, нано- электронной отрасли традиционно сегментируется на следующие основные четыре группы компонентов: оптоэлектроника; датчики;

- 21. Оптоэлектронные компоненты: • ПЗС и КМОП датчики изображения; • лазерные передатчики и звукосниматели; • светоизлучающие диоды

- 22. Датчики: температурные датчики; датчики давления; датчики поворота и ускорения; датчики магнитного поля; управляющие датчики. микрогироскопы

- 23. Дискретные компоненты: • cиловые транзисторы и модули; • малосигнальные транзисторы; • переключающие транзисторы; • диоды, выпрямители

- 24. Интегральные схемы: микропроцессоры (Microprocessing Units - MPU); микроконтроллеры (Microcontrolling Units - MCU); цифровые сигнальные процессоры (Digital

- 25. Азоев Г.Л., Афанасьев В.Я., Ларина Н.П. Азоев Г.Л., Афанасьев В.Я., Ларина Н.П. — Рынок нано: от

- 26. Развитие рынка наноэлектронной продукции Азоев Г.Л., Афанасьев В.Я., Ларина Н.П. Азоев Г.Л., Афанасьев В.Я., Ларина Н.П.

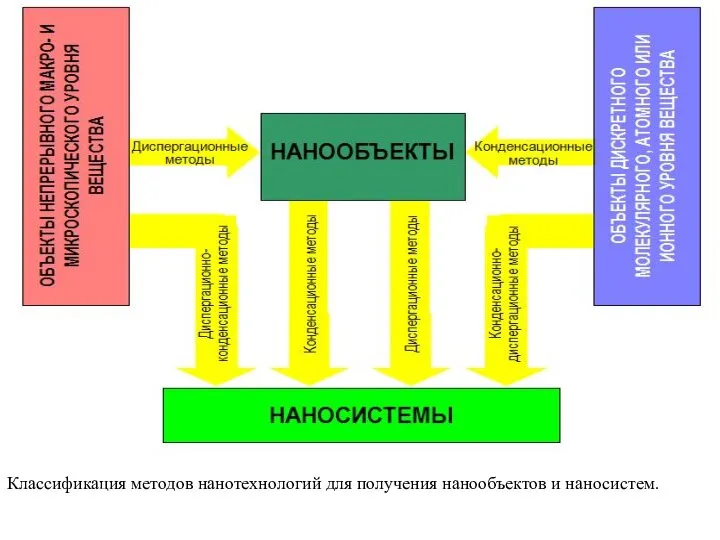

- 27. Классификация методов нанотехнологий для получения нанообъектов и наносистем.

- 28. Некоторые особенности работы наноэлектронных устройств

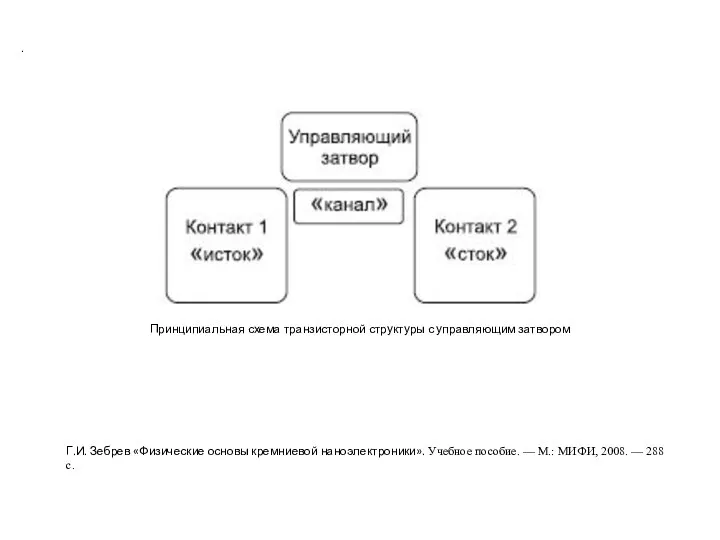

- 29. . Принципиальная схема транзисторной структуры с управляющим затвором Г.И. Зебрев «Физические основы кремниевой наноэлектроники». Учебное пособие.

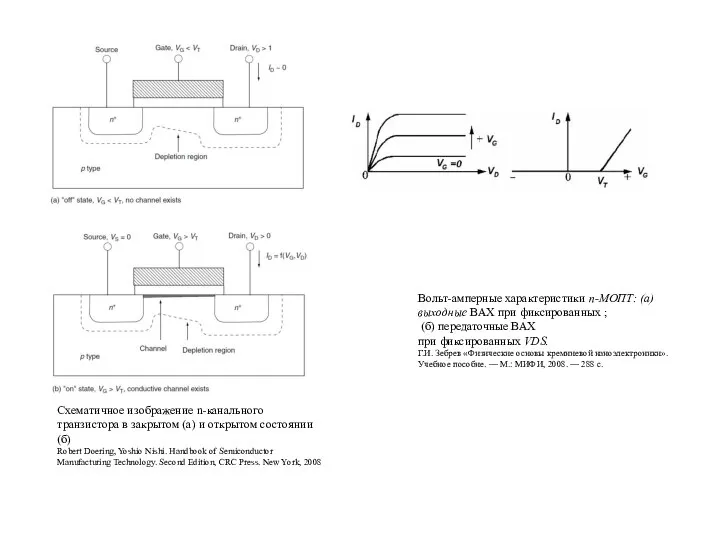

- 30. Схематичное изображение n-канального транзистора в закрытом (а) и открытом состоянии (б) Robert Doering, Yoshio Nishi. Handbook

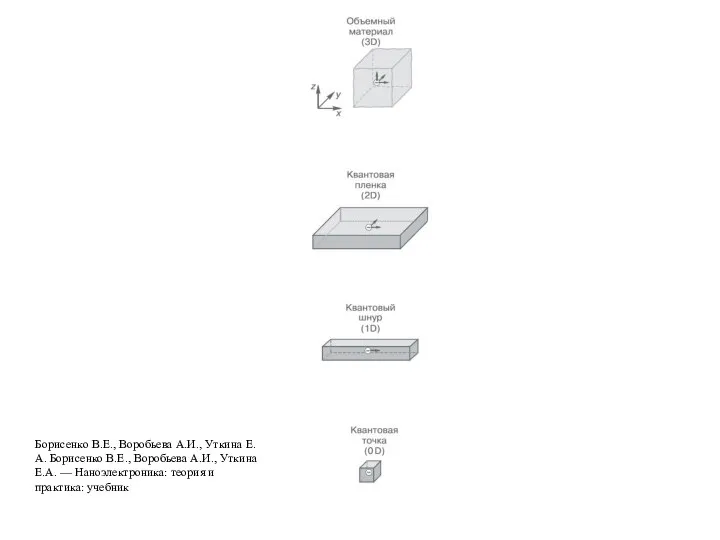

- 31. Борисенко В.Е., Воробьева А.И., Уткина Е.А. Борисенко В.Е., Воробьева А.И., Уткина Е.А. — Наноэлектроника: теория и

- 32. Борисенко В.Е., Воробьева А.И., Уткина Е.А. Борисенко В.Е., Воробьева А.И., Уткина Е.А. — Наноэлектроника: теория и

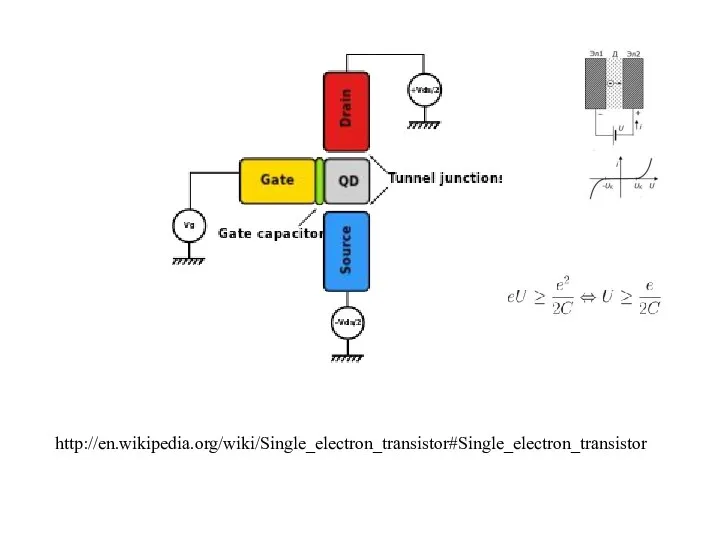

- 33. http://en.wikipedia.org/wiki/Single_electron_transistor#Single_electron_transistor

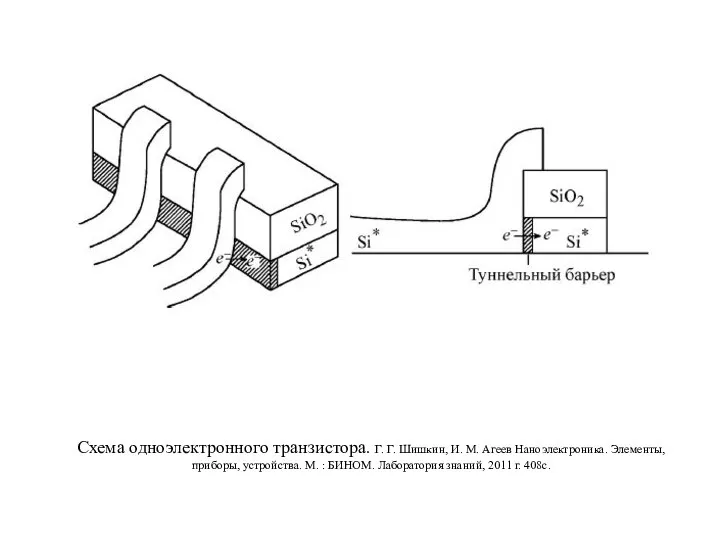

- 34. Схема одноэлектронного транзистора. Г. Г. Шишкин, И. М. Агеев Наноэлектроника. Элементы, приборы, устройства. М. : БИНОМ.

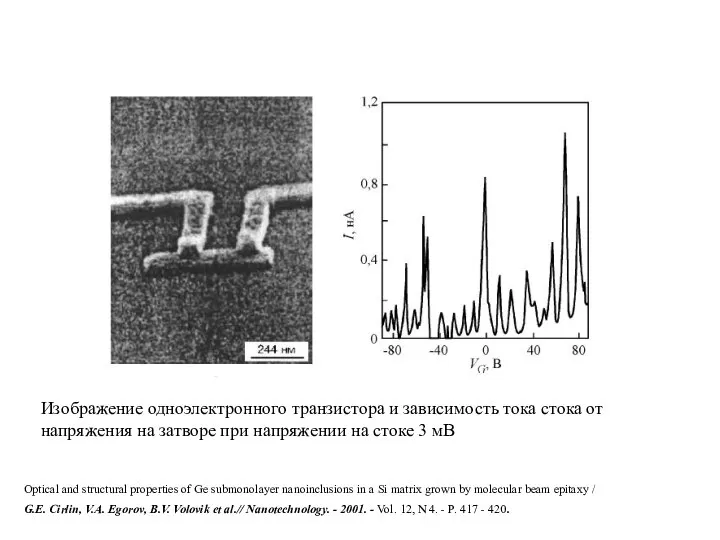

- 35. Изображение одноэлектронного транзистора и зависимость тока стока от напряжения на затворе при напряжении на стоке 3

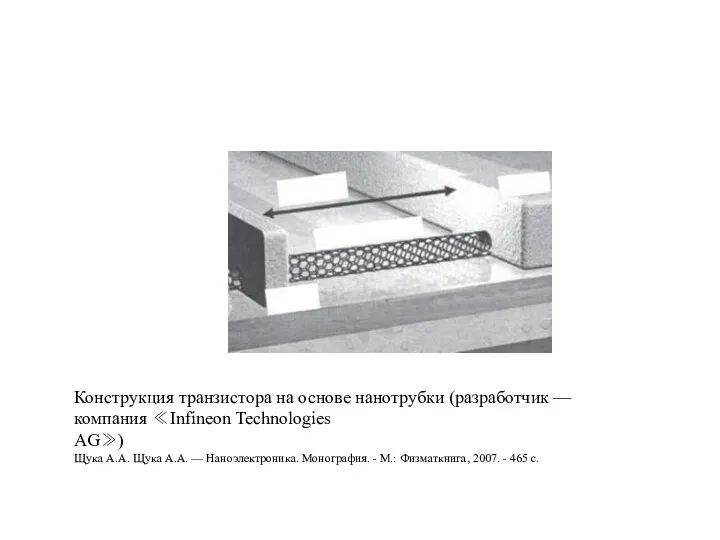

- 36. Конструкция транзистора на основе нанотрубки (разработчик — компания ≪Infineon Technologies AG≫) Щука А.А. Щука А.А. —

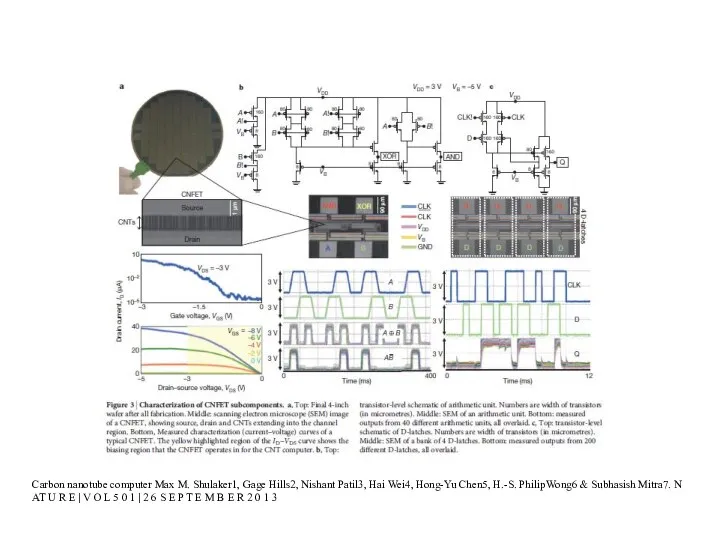

- 37. Carbon nanotube computer Max M. Shulaker1, Gage Hills2, Nishant Patil3, Hai Wei4, Hong-Yu Chen5, H.-S. PhilipWong6

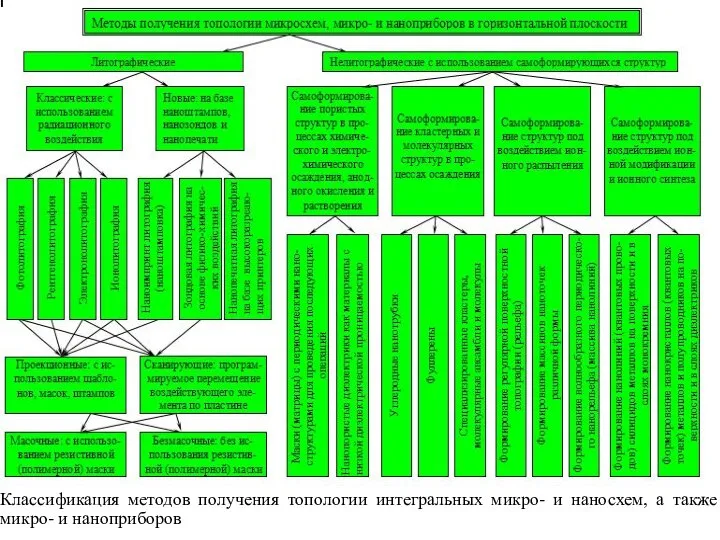

- 38. Классификация методов получения топологии интегральных микро- и наносхем, а также микро- и наноприборов

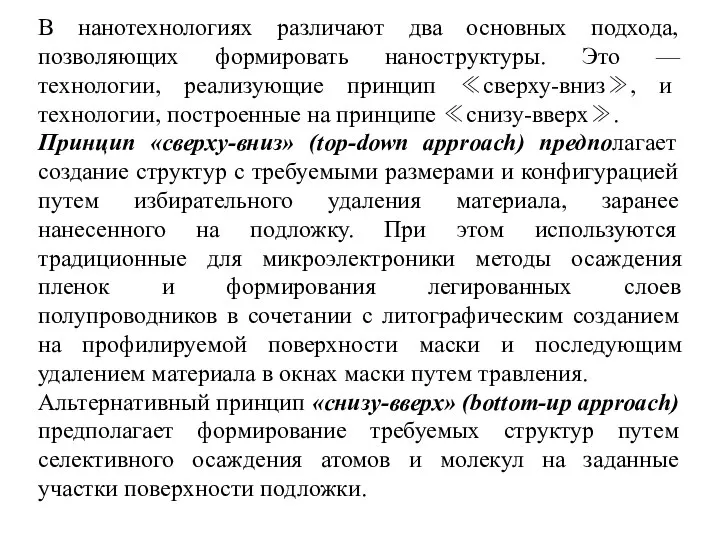

- 39. В нанотехнологиях различают два основных подхода, позволяющих формировать наноструктуры. Это — технологии, реализующие принцип ≪сверху-вниз≫, и

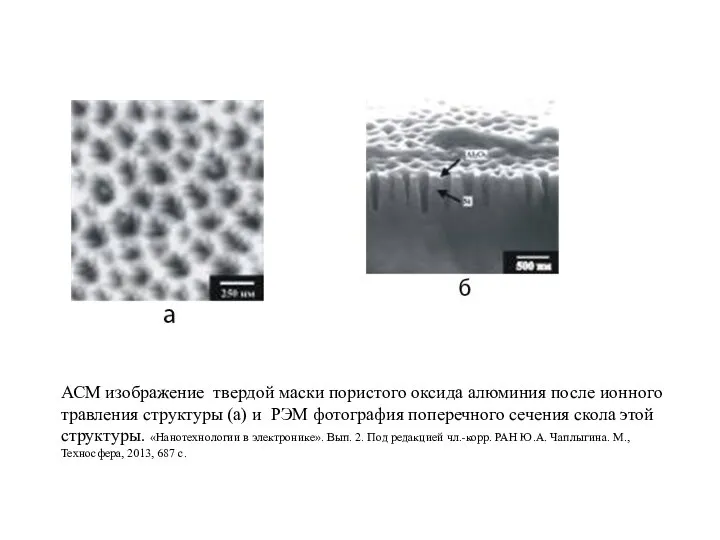

- 40. АСМ изображение твердой маски пористого оксида алюминия после ионного травления структуры (а) и РЭМ фотография поперечного

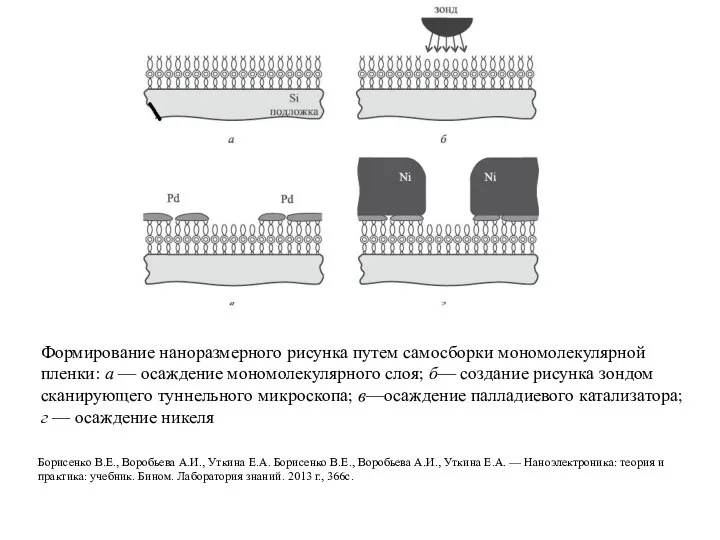

- 41. Формирование наноразмерного рисунка путем самосборки мономолекулярной пленки: а — осаждение мономолекулярного слоя; б— создание рисунка зондом

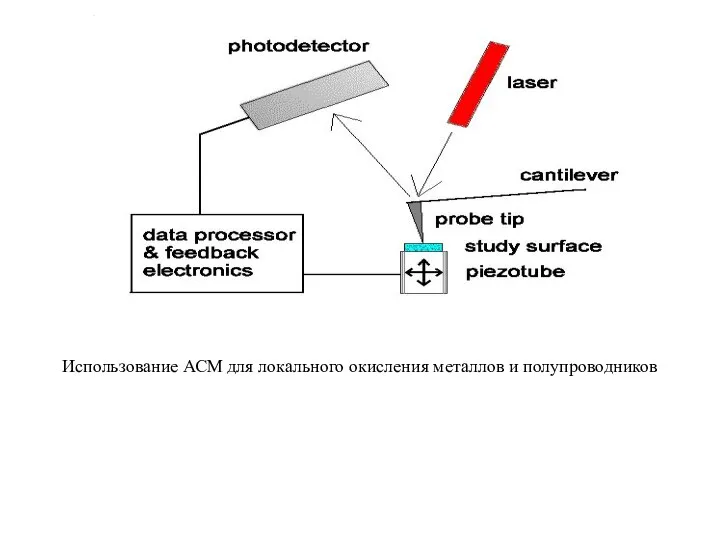

- 42. Использование АСМ для локального окисления металлов и полупроводников

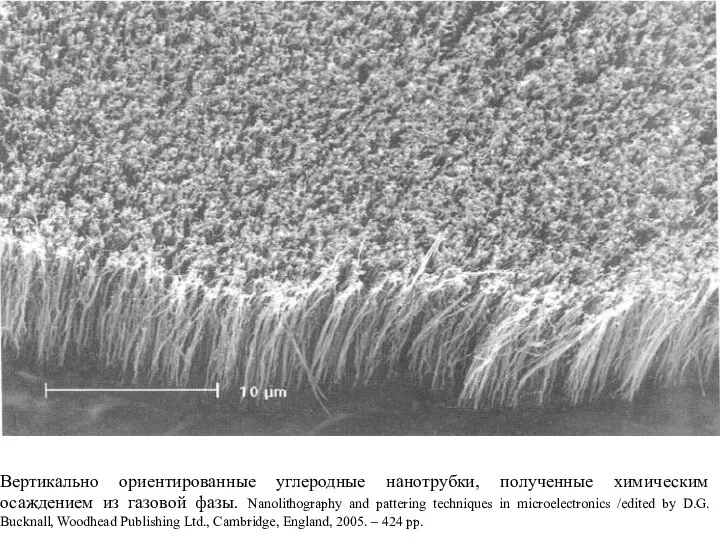

- 43. Вертикально ориентированные углеродные нанотрубки, полученные химическим осаждением из газовой фазы. Nanolithography and pattering techniques in microelectronics

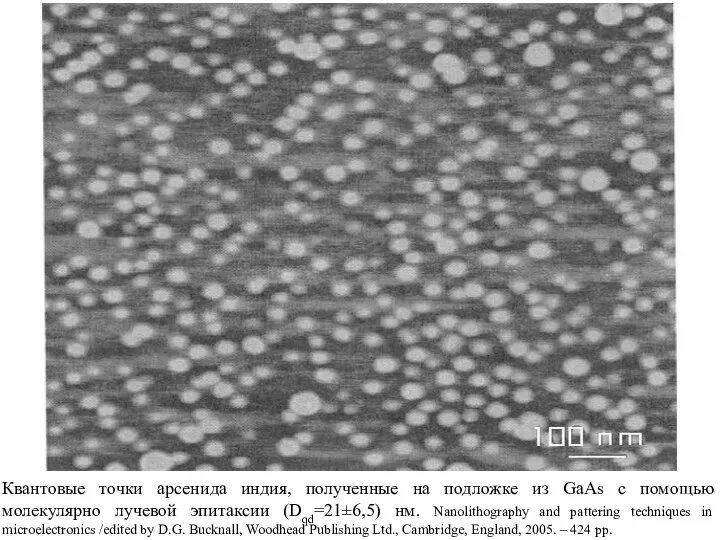

- 44. Квантовые точки арсенида индия, полученные на подложке из GaAs с помощью молекулярно лучевой эпитаксии (Dqd=21±6,5) нм.

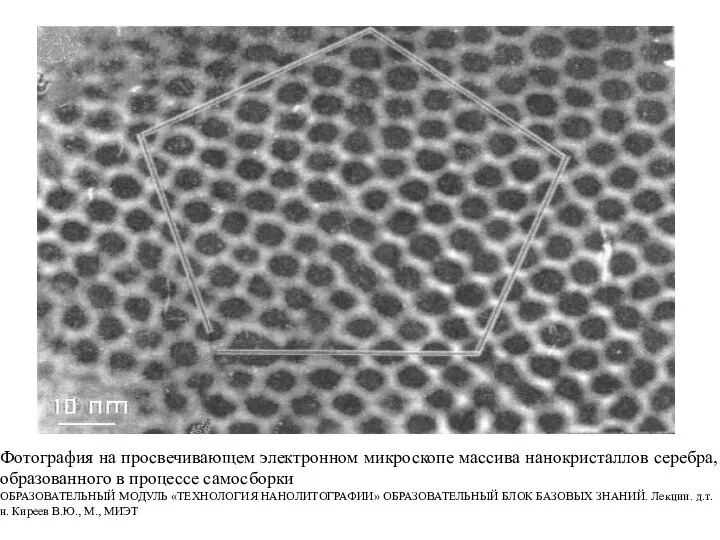

- 45. Фотография на просвечивающем электронном микроскопе массива нанокристаллов серебра, образованного в процессе самосборки ОБРАЗОВАТЕЛЬНЫЙ МОДУЛЬ «ТЕХНОЛОГИЯ НАНОЛИТОГРАФИИ»

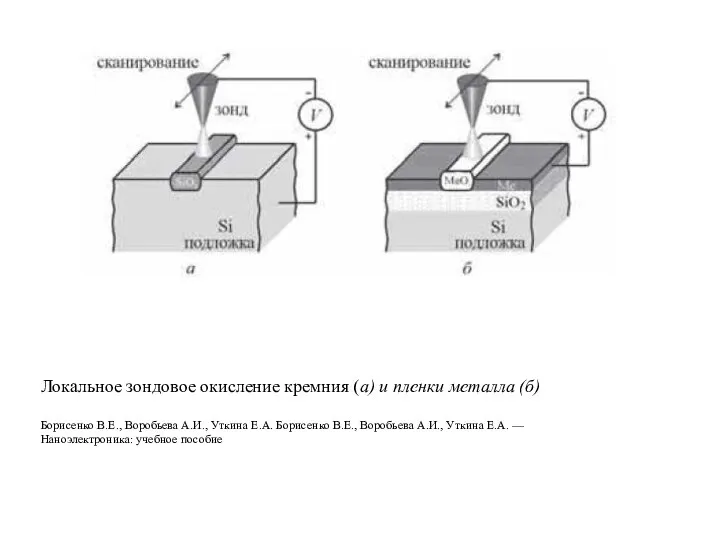

- 46. Локальное зондовое окисление кремния (а) и пленки металла (б) Борисенко В.Е., Воробьева А.И., Уткина Е.А. Борисенко

- 47. Принцип проекционной литографии

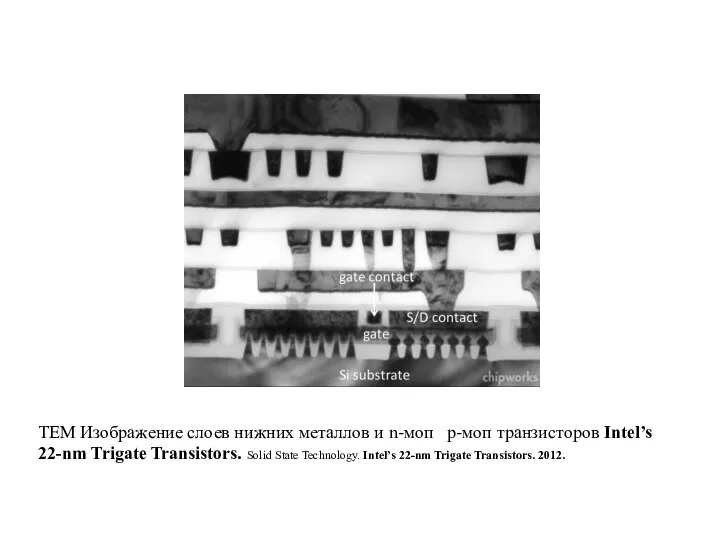

- 48. TEM Изображение слоев нижних металлов и n-моп p-моп транзисторов Intel’s 22-nm Trigate Transistors. Solid State Technology.

- 49. Вопросы промежуточного контроля: Дайте определение наноэлектроники. Сформулируйте Мура. Назовите основные сегменты электронной отрасли. Какой из сегментов

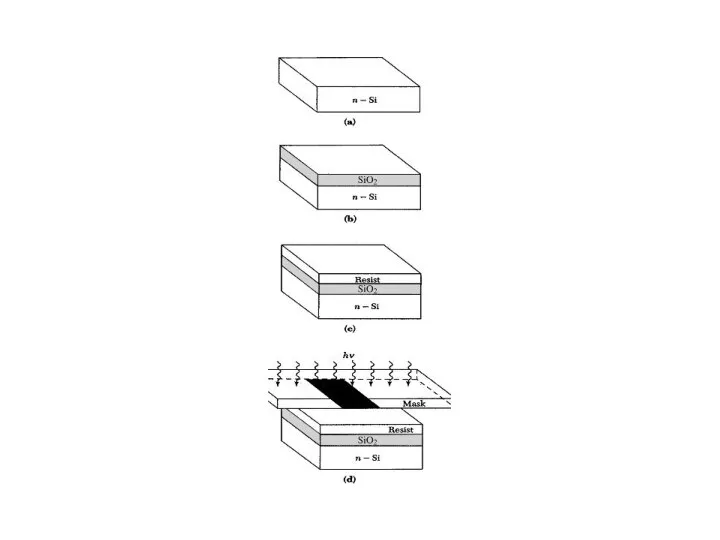

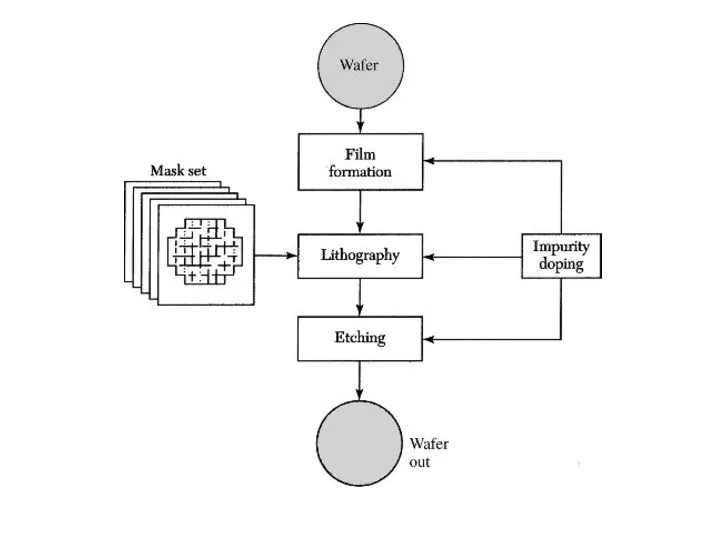

- 50. Планарная технология Основным технологическим методом создания современных интегральных микросхем остается разработанная в конце 50-х годов двадцатого

- 51. Планарная технология (от англ. planar, от лат. planus – плоский, ровный), – форма организации технологического процесса

- 52. Планарная технология позволяет реализовать групповой процесс изготовления элементов интегральных схем на полупроводниковой подложке одновременно и на

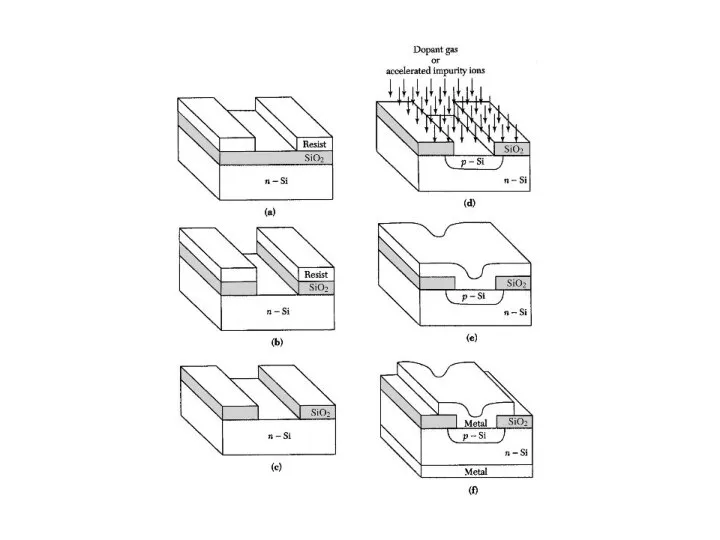

- 53. Основные операции планарной технологии легирование полупроводника (диффузия примесей в полупроводник и ионная имплантация) окисление кремния травление

- 54. Легирование атомами примеси Сущность процессов легирования полупроводника заключается в создании на поверхности полупроводника источника примеси и

- 55. Окисление кремния В результате процесса окисления происходит взаимодействие поверхностного слоя кремния с кислородом и создание на

- 56. Травление Травление – это технологическая операция удаления обрабатываемого материала в процессе химического взаимодействия и растворения в

- 57. Локальное травление и фотолитография Метод фотолитографии, использует в качестве защитного слоя стойкое к действию травителей вещество,

- 58. Технологический маршрут Изготовление каждого полупроводникового прибора (соответственно, интегральной микросхемы) идет по строго определенной последовательности. Такая последовательность

- 59. Сопроводительный лист На предприятиях микроэлектроники данная последовательность отражена в маршрутной карте (сопроводительном листе) соответствующей партии пластин,

- 60. Принципы планарной технологии взаимосвязь конструкции интегральных микросхем и технологии их изготовления совместимость элементов (на одном кристалле)

- 61. Взаимосвязь конструкции интегральных микросхем и технологии их изготовления Проектирование конструкции интегральной микросхемы связано с технологией ее

- 62. Конструктивно-технологические ограничения при разработке и изготовлении интегральных микросхем Наряду с конструктивными, эксплутационными и электрическими параметрами для

- 63. Совместимость элементов интегральных микросхем Единый групповой метод изготовления. Основной элемент – самый сложный элемент ИС -

- 64. Локальность технологических обработок Во время технологических операций обрабатывается не вся поверхность пластины. Методы локальных технологий: масочная

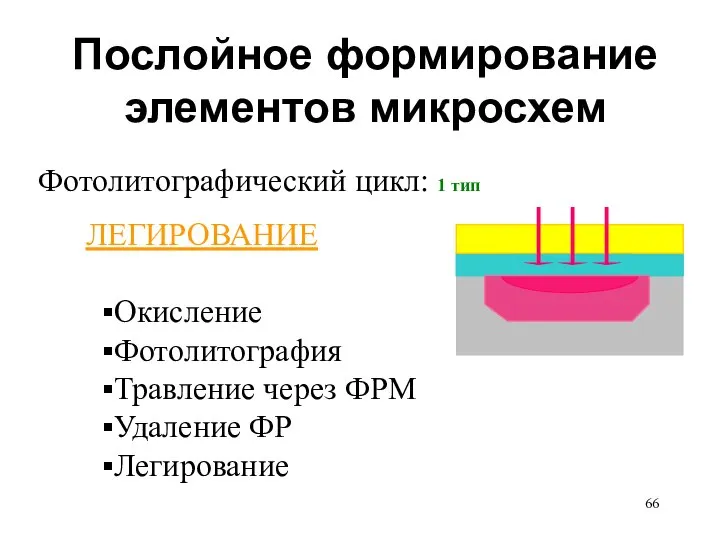

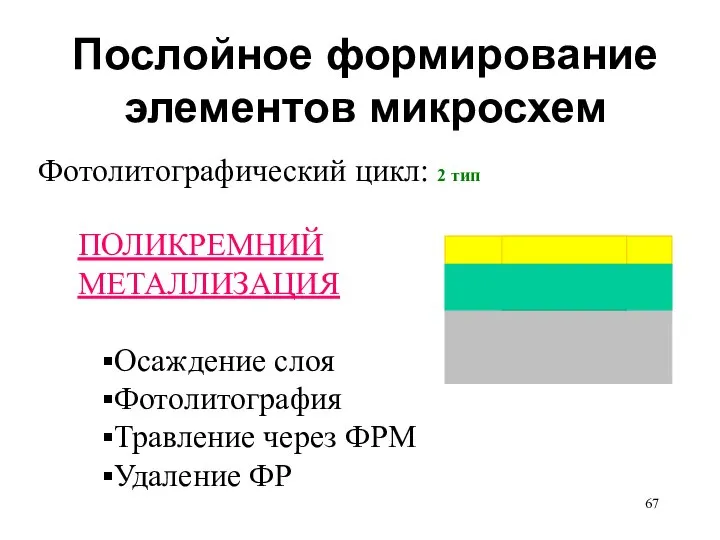

- 65. Послойное формирование элементов микросхем Локальные обработки различных участков пластины выполняют многократно. Фотолитографический цикл: 2 типа

- 66. Послойное формирование элементов микросхем Фотолитографический цикл: 1 тип ЛЕГИРОВАНИЕ Окисление Фотолитография Травление через ФРМ Удаление ФР

- 67. Послойное формирование элементов микросхем Фотолитографический цикл: 2 тип ПОЛИКРЕМНИЙ МЕТАЛЛИЗАЦИЯ Осаждение слоя Фотолитография Травление через ФРМ

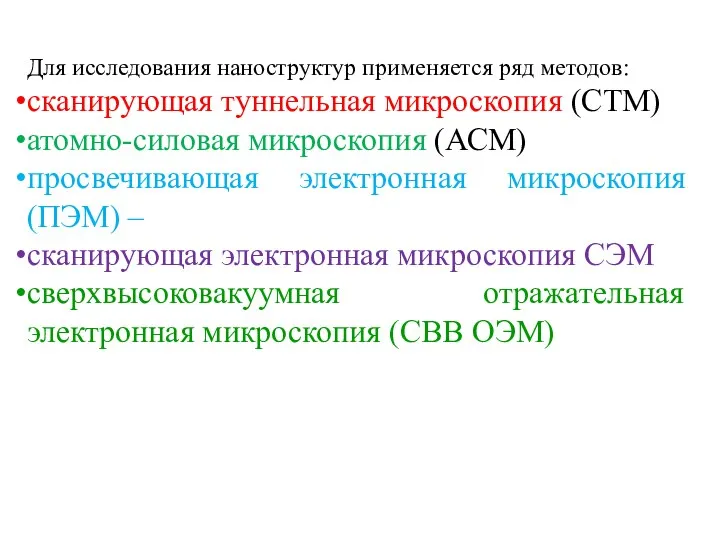

- 71. Методы контроля наноструктур

- 72. Для исследования наноструктур применяется ряд методов: сканирующая туннельная микроскопия (СТМ) атомно-силовая микроскопия (АСМ) просвечивающая электронная микроскопия

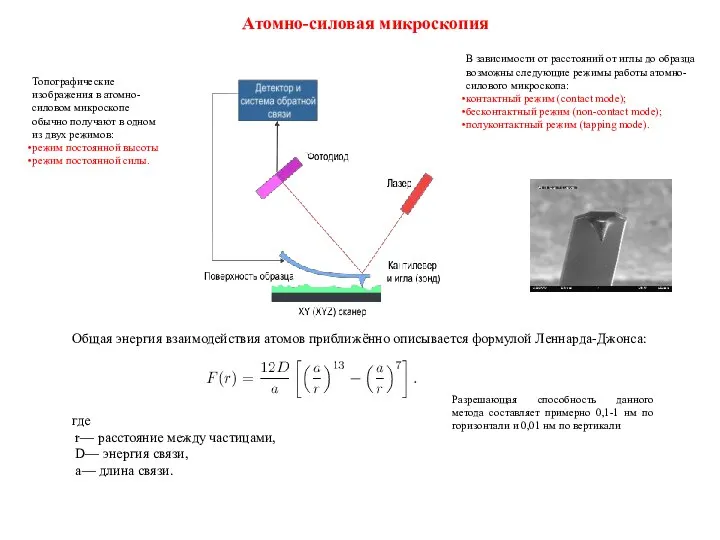

- 73. Сканирование обычно проводят в двух режимах: постоянного тока или постоянного уровня кантилевера (сенсорное устройство, закрепленно на

- 74. Общая энергия взаимодействия атомов приближённо описывается формулой Леннарда-Джонса: где r— расстояние между частицами, D— энергия связи,

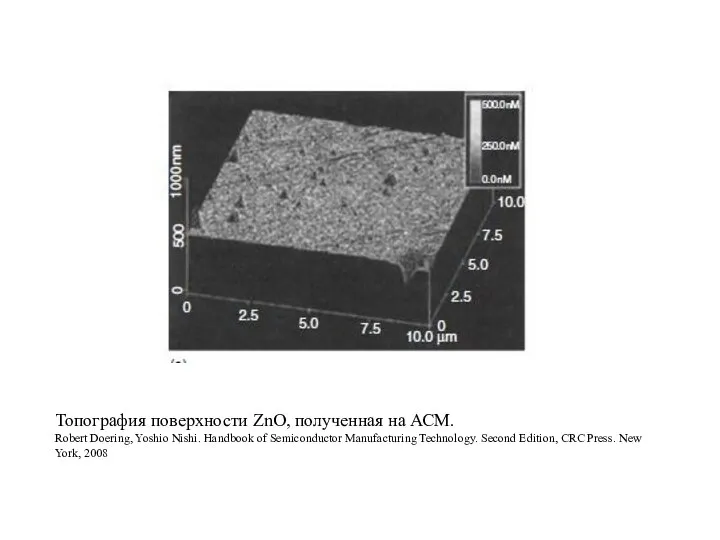

- 75. Топография поверхности ZnO, полученная на АСМ. Robert Doering, Yoshio Nishi. Handbook of Semiconductor Manufacturing Technology. Second

- 76. Просвечивающий электронный микроскоп Метод просвечивающей электронной микроскопии позволяет изучать внутреннюю структуру исследуемых материалов: определять тип и

- 77. При проведении исследований на СЭМ (часто также встречается название «растровый электроный микроскоп» или сокращенно РЭМ) Тонкий

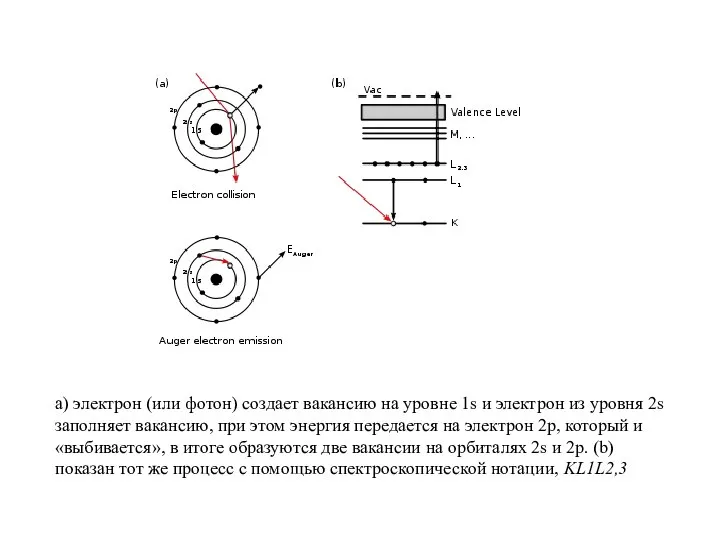

- 78. a) электрон (или фотон) создает вакансию на уровне 1s и электрон из уровня 2s заполняет вакансию,

- 80. Скачать презентацию

Мудрая сова 1 тур «Мы знаем всё и обо всём». Щкола-интернат № 22 VIII вида, Зав. библиотекой Вызинская Л.М.

Мудрая сова 1 тур «Мы знаем всё и обо всём». Щкола-интернат № 22 VIII вида, Зав. библиотекой Вызинская Л.М. Лекция №6 Требования, предъявляемые к тестовым заданиям. Психолого-педагогические аспекты тестирования. План лекции: Требован

Лекция №6 Требования, предъявляемые к тестовым заданиям. Психолого-педагогические аспекты тестирования. План лекции: Требован Презентация по алгебре Определение степени с натуральным показателем 7 класс

Презентация по алгебре Определение степени с натуральным показателем 7 класс  Управление потоком

Управление потоком Презентация "Памятка дольщику" - скачать презентации по Экономике

Презентация "Памятка дольщику" - скачать презентации по Экономике ТИПОЛОГИЯ ПОЛИТИЧЕСКИХ РЕЖИМОВ Выполнили: Белоусова Александра Маслова Юлия

ТИПОЛОГИЯ ПОЛИТИЧЕСКИХ РЕЖИМОВ Выполнили: Белоусова Александра Маслова Юлия Система программирования PascalABC.NET и электронный задачник Programming Taskbook

Система программирования PascalABC.NET и электронный задачник Programming Taskbook Една година след старта на кризата Или по-точно година и половина Светлозар Петров, JobTiger XII HR Weekend Януари 2010, Луковит. - презентация

Една година след старта на кризата Или по-точно година и половина Светлозар Петров, JobTiger XII HR Weekend Януари 2010, Луковит. - презентация Общие сведения о железобетонных конструкциях

Общие сведения о железобетонных конструкциях Матлаб (Создание графических приложений)

Матлаб (Создание графических приложений) Хоккеисты России

Хоккеисты России Трансляция языков программирования

Трансляция языков программирования Художественная культура России

Художественная культура России Строительная теплотехника. Воздухопроницаемость. Разность давлений

Строительная теплотехника. Воздухопроницаемость. Разность давлений Профессия следователь

Профессия следователь  Кәсіпкерлікті мемлекеттік қолдау және оның инфрақұрылымы. (Тақырып 13)

Кәсіпкерлікті мемлекеттік қолдау және оның инфрақұрылымы. (Тақырып 13) Сервитутное право

Сервитутное право  Презентация Содержание договора

Презентация Содержание договора Основные компетенции и направления профессионального образования

Основные компетенции и направления профессионального образования Физиологическая классификация и характеристика спортивных упражнений

Физиологическая классификация и характеристика спортивных упражнений Тема 5. Маркетинговая информационная система Дисциплина «Основы маркетинга»

Тема 5. Маркетинговая информационная система Дисциплина «Основы маркетинга»  Разработка устройства разделения смесей по аэродинамическим свойствам компонентов

Разработка устройства разделения смесей по аэродинамическим свойствам компонентов Учитель ГОУ школы № 341 г. Санкт-Петербурга Паничева Марина Владимировна

Учитель ГОУ школы № 341 г. Санкт-Петербурга Паничева Марина Владимировна проект «Разработка модели современного урока»

проект «Разработка модели современного урока» Презентация на тему "Как правильно выбрать эффективный биологически активный препарат" - скачать презентации по Медицине

Презентация на тему "Как правильно выбрать эффективный биологически активный препарат" - скачать презентации по Медицине Перемещение товаров трубопроводным транспортом и по линиям электропередачи. Выполнили: студенты ЮФ Стародубцева Т.В. Мищук Я.

Перемещение товаров трубопроводным транспортом и по линиям электропередачи. Выполнили: студенты ЮФ Стародубцева Т.В. Мищук Я. Основы кристаллооптики

Основы кристаллооптики  Урок окружающего мира - презентация для начальной школы

Урок окружающего мира - презентация для начальной школы