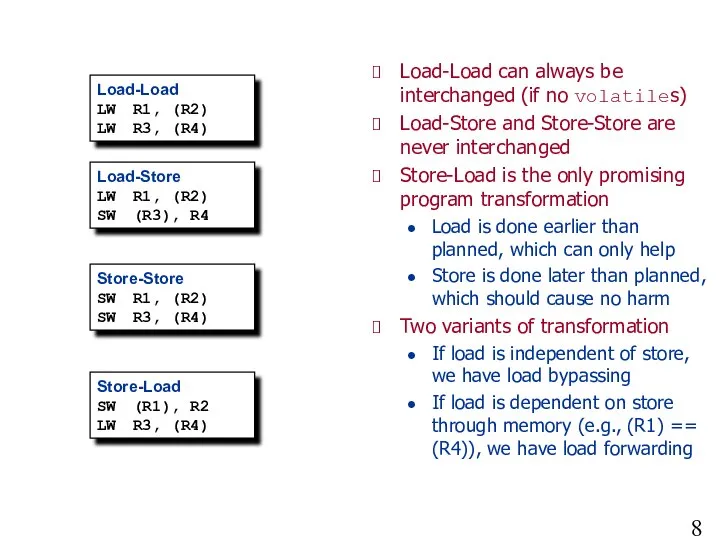

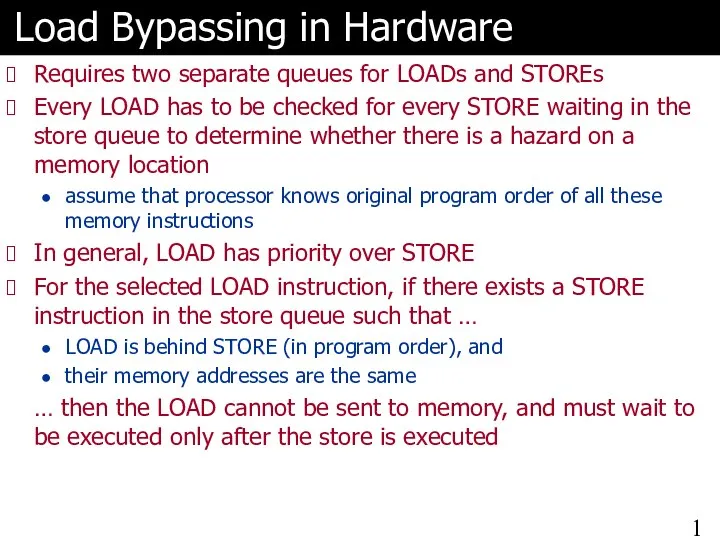

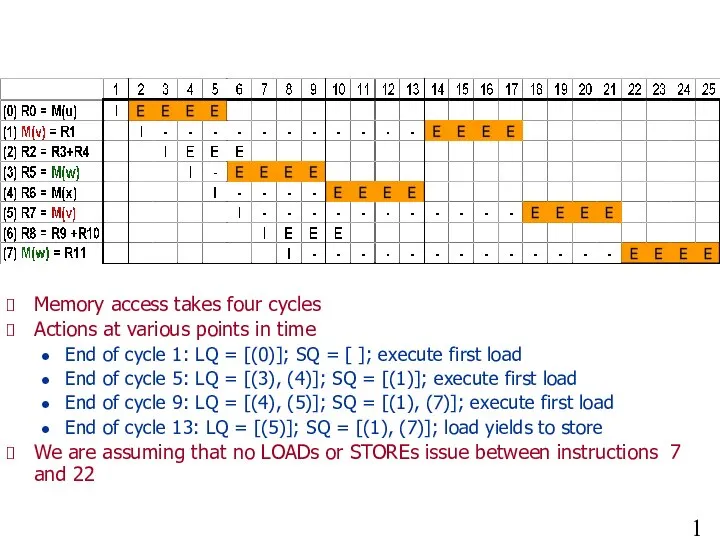

Four Possibilities for Load/Store Motion

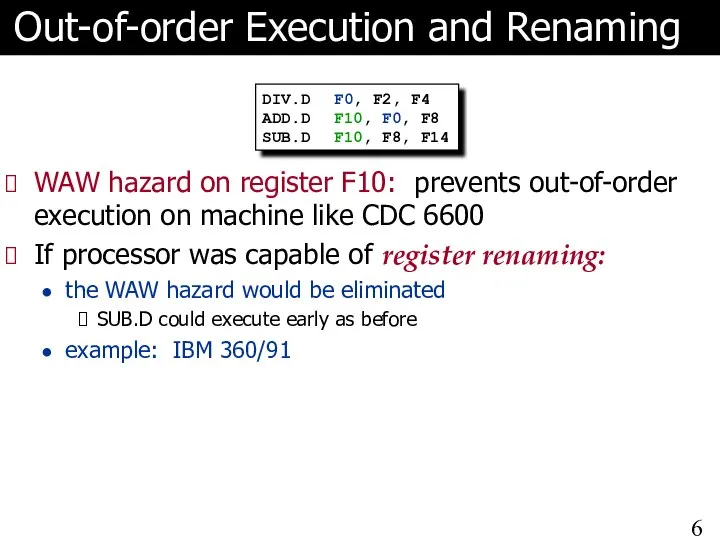

Load-Load

LW R1, (R2)

LW R3, (R4)

Load-Load can always be interchanged

(if no volatiles)

Load-Store and Store-Store are never interchanged

Store-Load is the only promising program transformation

Load is done earlier than planned, which can only help

Store is done later than planned, which should cause no harm

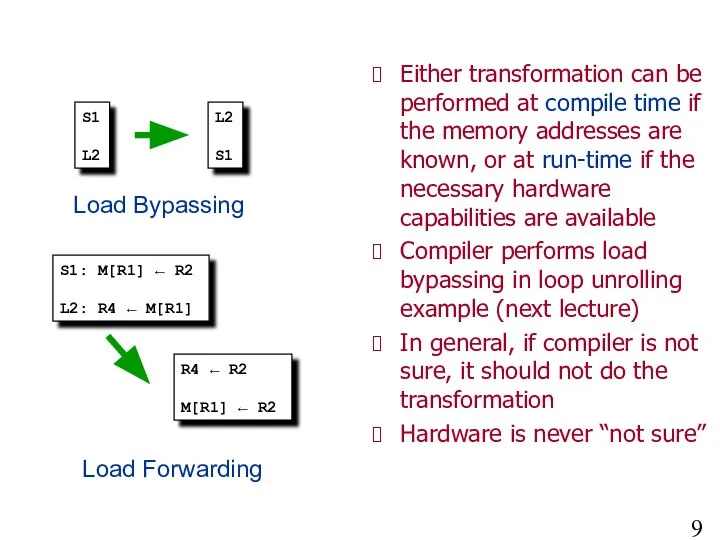

Two variants of transformation

If load is independent of store, we have load bypassing

If load is dependent on store through memory (e.g., (R1) == (R4)), we have load forwarding

Load-Store

LW R1, (R2)

SW (R3), R4

Store-Store

SW R1, (R2)

SW R3, (R4)

Store-Load

SW (R1), R2

LW R3, (R4)

История отношений России и Британии

История отношений России и Британии Улуттук кийимдер жана жасалгалар

Улуттук кийимдер жана жасалгалар Морально-этические принципы работы юриста уголовно-правовой специализации

Морально-этические принципы работы юриста уголовно-правовой специализации ТЕМА 1.2. ИСТОЧНИКИ ГРАЖДАНСКОГО ПРАВА _

ТЕМА 1.2. ИСТОЧНИКИ ГРАЖДАНСКОГО ПРАВА _ Дифракция световых волн 2

Дифракция световых волн 2 Инструкция по ремонту рукояти

Инструкция по ремонту рукояти Технологический процесс технического обслуживания и ремонта системы питания автомобиля ГАЗ- 3307

Технологический процесс технического обслуживания и ремонта системы питания автомобиля ГАЗ- 3307 Тема: «Кружевные узоры» Украшения и фантазия Составила: Газизова З.А., учитель Нововасюга

Тема: «Кружевные узоры» Украшения и фантазия Составила: Газизова З.А., учитель Нововасюга ФИЗИОЛОГИЯ СИНАПСОВ. ФИЗИОЛОГИЯ НЕЙРОНА. ФИЗИОЛОГИЯ ЖЕЛЕЗ

ФИЗИОЛОГИЯ СИНАПСОВ. ФИЗИОЛОГИЯ НЕЙРОНА. ФИЗИОЛОГИЯ ЖЕЛЕЗ Рекурсия и сложность

Рекурсия и сложность  Лечение бронхиальной астмы

Лечение бронхиальной астмы Теорія електричних та електронних кіл

Теорія електричних та електронних кіл Допиши предложения - презентация для начальной школы

Допиши предложения - презентация для начальной школы Благоустройство общественного пространства по адресу: Ростовская область, станица Егорлыкская. «Город на земле»

Благоустройство общественного пространства по адресу: Ростовская область, станица Егорлыкская. «Город на земле» Есть ли разум во Вселенной

Есть ли разум во Вселенной Горные экосистемы

Горные экосистемы  Современные методы управления

Современные методы управления Дресс-код в компании

Дресс-код в компании Аттестационная работа. Образовательная программа внеурочной деятельности спортивно-оздоровительного кружка «Туризм»

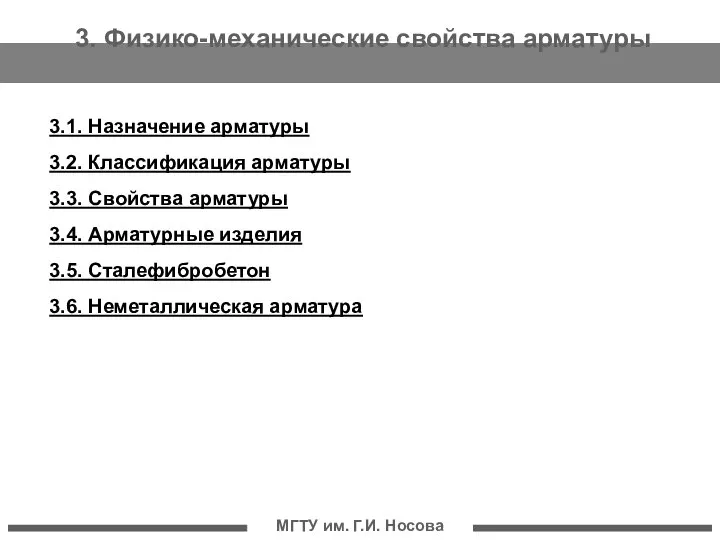

Аттестационная работа. Образовательная программа внеурочной деятельности спортивно-оздоровительного кружка «Туризм» Физико-механические свойства арматуры

Физико-механические свойства арматуры Самовсасывающие устройства применяемые на технических средствах службы горючего

Самовсасывающие устройства применяемые на технических средствах службы горючего Презентация к уроку МХК в 6 классе по теме «Рождение христианской художественной образности. Библия как основная книга христианс

Презентация к уроку МХК в 6 классе по теме «Рождение христианской художественной образности. Библия как основная книга христианс Сущность и виды предпринимательской деятельности

Сущность и виды предпринимательской деятельности Решение дробных рациональных уравнений Алгебра 8 класс

Решение дробных рациональных уравнений Алгебра 8 класс Умный ночник

Умный ночник Международный конкурс социальных проектов с применением цифровых технологий «Social Idea». МТС

Международный конкурс социальных проектов с применением цифровых технологий «Social Idea». МТС Молоко и молочные товары

Молоко и молочные товары Dziesięć Bożych przykazań

Dziesięć Bożych przykazań