Содержание

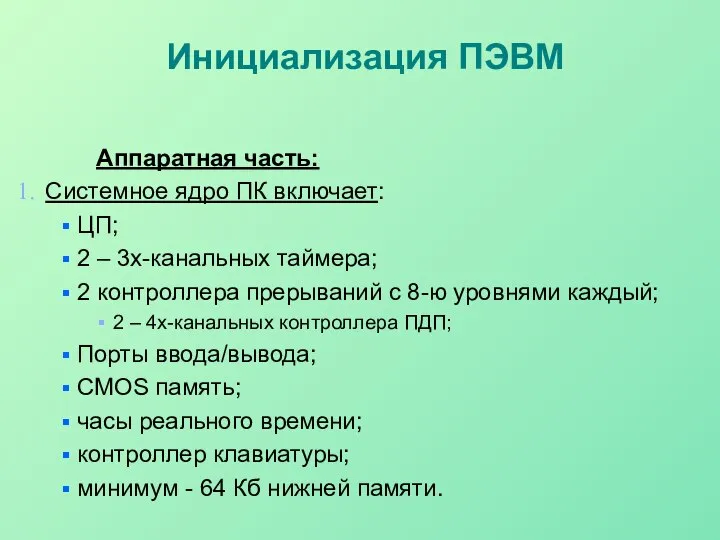

- 2. Инициализация ПЭВМ Аппаратная часть: Системное ядро ПК включает: ЦП; 2 – 3х-канальных таймера; 2 контроллера прерываний

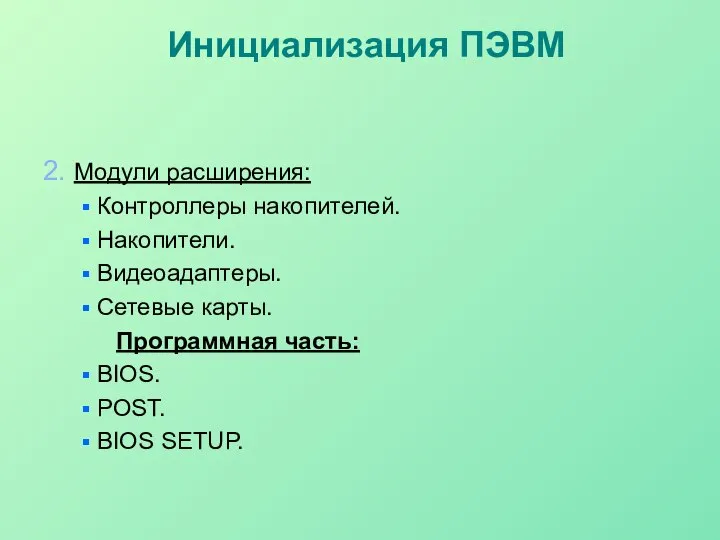

- 3. Инициализация ПЭВМ 2. Модули расширения: Контроллеры накопителей. Накопители. Видеоадаптеры. Сетевые карты. Программная часть: BIOS. POST. BIOS

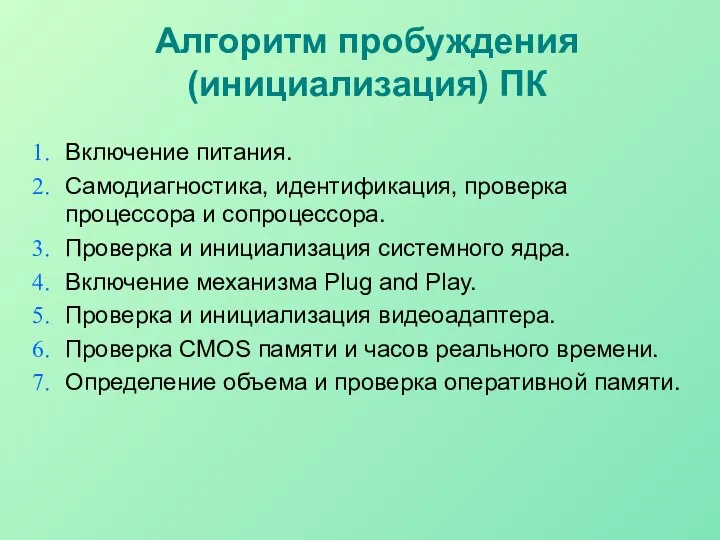

- 4. Алгоритм пробуждения (инициализация) ПК Включение питания. Самодиагностика, идентификация, проверка процессора и сопроцессора. Проверка и инициализация системного

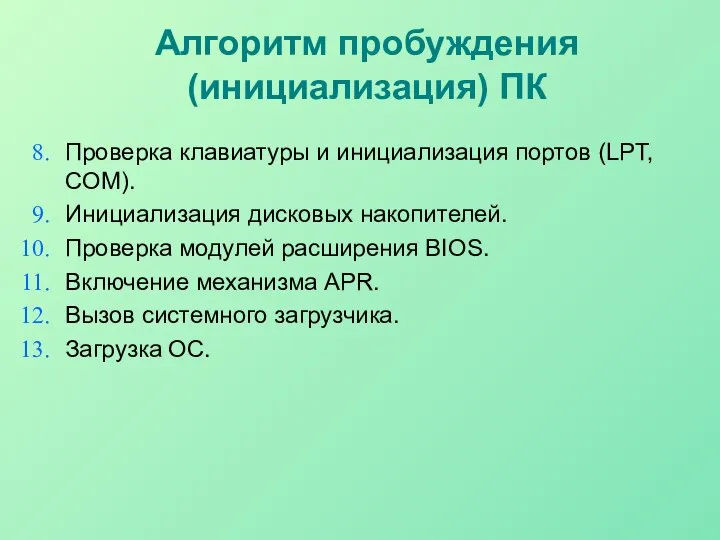

- 5. Алгоритм пробуждения (инициализация) ПК Проверка клавиатуры и инициализация портов (LPT, COM). Инициализация дисковых накопителей. Проверка модулей

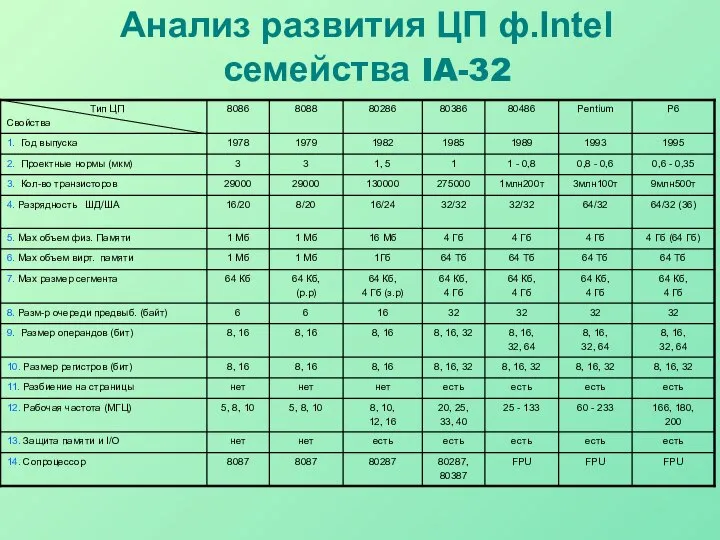

- 6. Анализ развития ЦП ф.Intel семейства IA-32

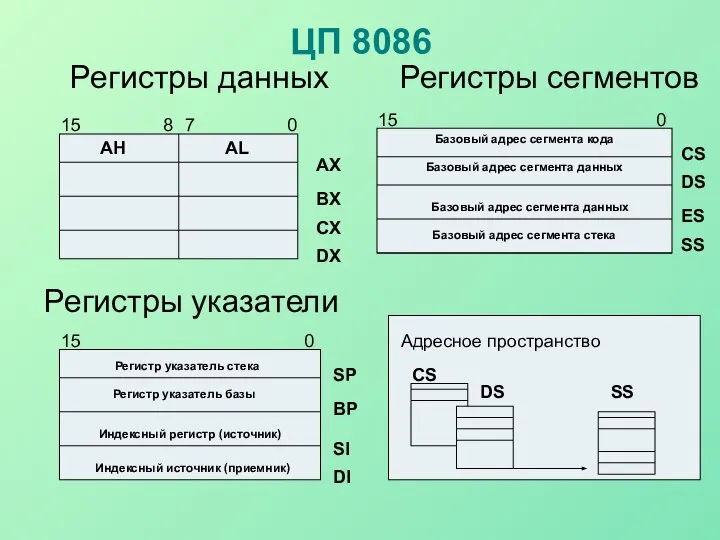

- 7. ЦП 8086 Регистры данных Регистры сегментов Регистры указатели АН AL 15 8 7 0 AX BX

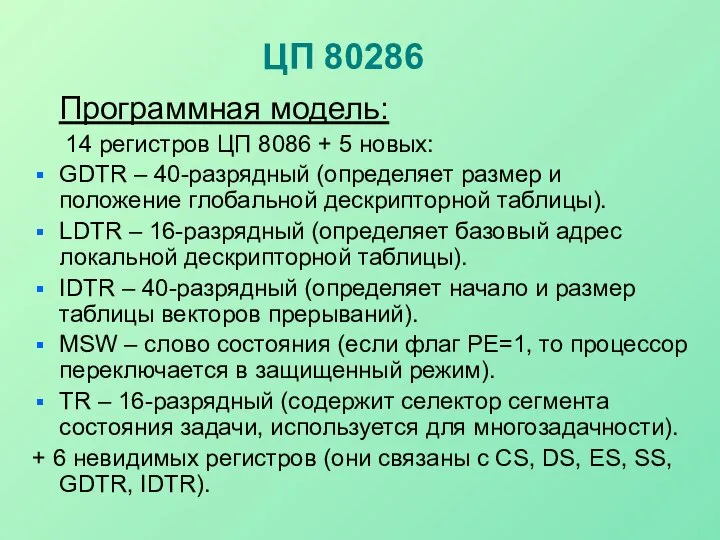

- 8. ЦП 80286 Программная модель: 14 регистров ЦП 8086 + 5 новых: GDTR – 40-разрядный (определяет размер

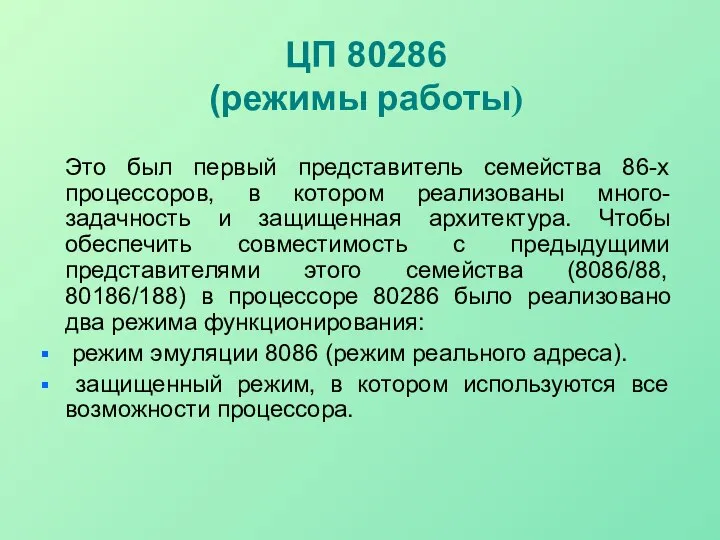

- 9. ЦП 80286 (режимы работы) Это был первый представитель семейства 86-х процессоров, в котором реализованы много-задачность и

- 10. Формирование линейного адреса без участия селекторов Способ формирования физического адреса зависит от режима работы процессора. В

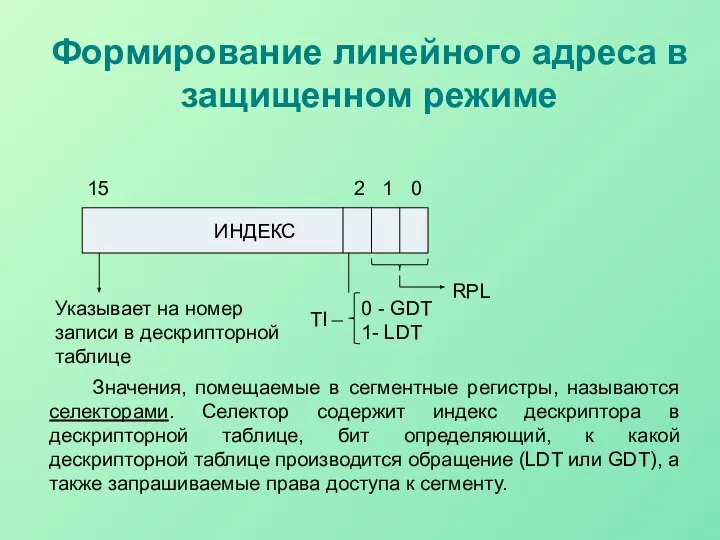

- 11. Формирование линейного адреса в защищенном режиме ИНДЕКС 0 1 2 15 RPL TI 0 - GDT

- 12. Формирование линейного адреса в защищенном режиме По указанному в селекторе номеру записи в соответствующей (бит TI

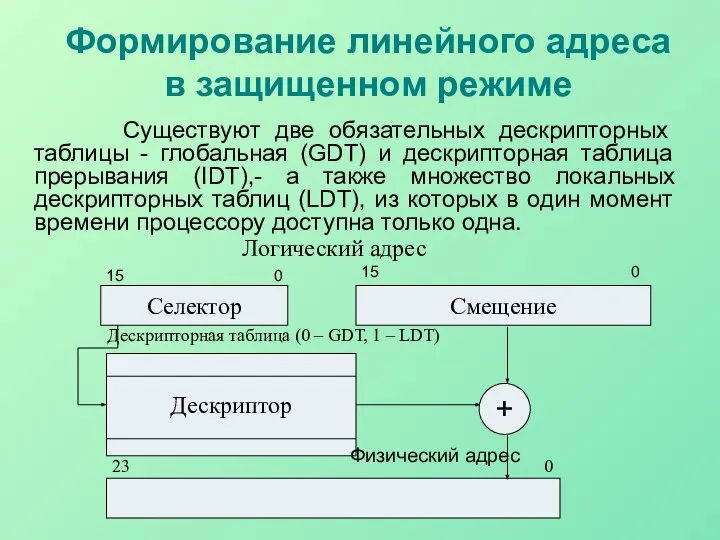

- 13. Формирование линейного адреса в защищенном режиме Существуют две обязательных дескрипторных таблицы - глобальная (GDT) и дескрипторная

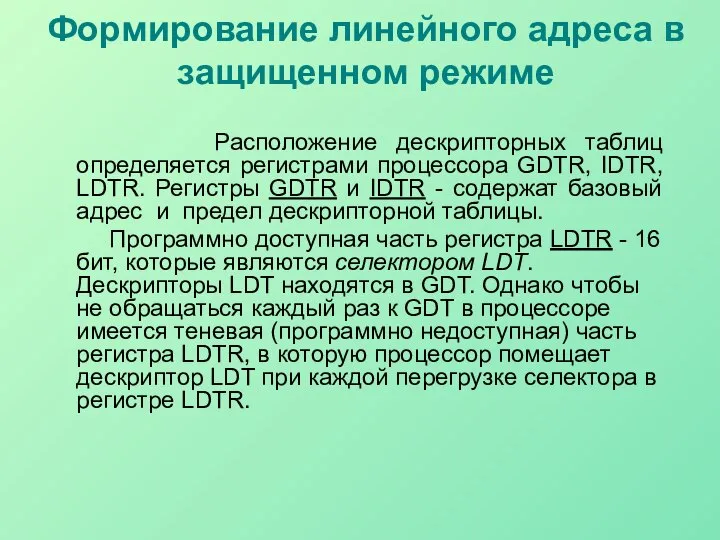

- 14. Формирование линейного адреса в защищенном режиме Расположение дескрипторных таблиц определяется регистрами процессора GDTR, IDTR, LDTR. Регистры

- 15. Шинная архитектура ЦП 80286 Синхро- генератор 82284 ЦП 80286 CLK RESET READK Шинный контроллер 82288 S0

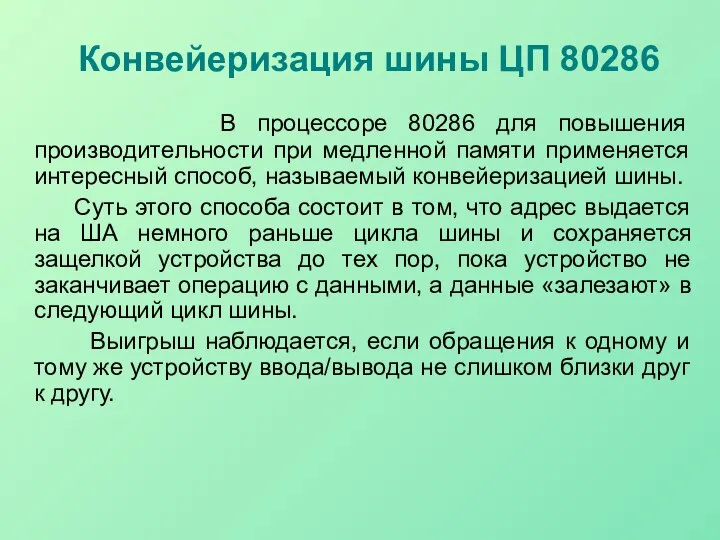

- 16. Конвейеризация шины ЦП 80286 В процессоре 80286 для повышения производительности при медленной памяти применяется интересный способ,

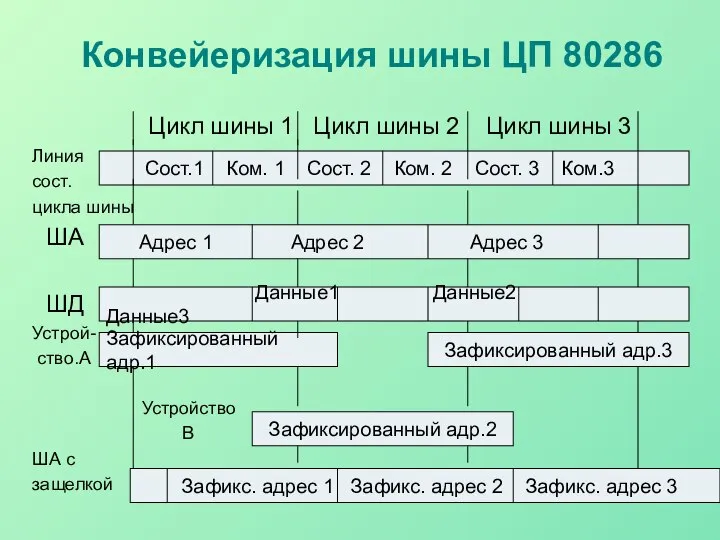

- 17. Конвейеризация шины ЦП 80286 Цикл шины 1 Цикл шины 2 Цикл шины 3 Линия сост. цикла

- 18. Вопросы для самоконтроля Какие устройства составляют системное ядро ПК? При инициализации ПК информация о проверке каких

- 20. Скачать презентацию

Критерии правильного построения публичного выступления. Выбор темы спора и оппонента

Критерии правильного построения публичного выступления. Выбор темы спора и оппонента  Лингвистические традиции

Лингвистические традиции Методы исследования механической активности сердца

Методы исследования механической активности сердца Идентификация кожаной обуви _

Идентификация кожаной обуви _ 1vektoryikordinatyivektoraprosteyshiezadachivkoordinataxzadachinachertejax9klass

1vektoryikordinatyivektoraprosteyshiezadachivkoordinataxzadachinachertejax9klass Организация медицинской помощи сельскому населению

Организация медицинской помощи сельскому населению Физика 8г теплопроводность...

Физика 8г теплопроводность... Смартфон в житті. Застосування в життєвих ситуаціях

Смартфон в житті. Застосування в життєвих ситуаціях Кафедра «Финансы и налоги» Преподаватель: Просалова Вероника Сергеевна, к.э.н., доцент «БЮДЖЕТНОЕ ПЛАНИРОВАНИЕ И ПРОГНОЗИРОВА

Кафедра «Финансы и налоги» Преподаватель: Просалова Вероника Сергеевна, к.э.н., доцент «БЮДЖЕТНОЕ ПЛАНИРОВАНИЕ И ПРОГНОЗИРОВА Функціональні матеріали для високоенергетичної електроніки

Функціональні матеріали для високоенергетичної електроніки Богослужение и его участники

Богослужение и его участники Тема 10. Ценовая политика Дисциплина «Маркетинг»

Тема 10. Ценовая политика Дисциплина «Маркетинг»  Презентация Соборное уложение 1649 года

Презентация Соборное уложение 1649 года Патология красной крови

Патология красной крови Влияние программ начальной школы на развитие орфографической зоркости учащихся II и III ступени

Влияние программ начальной школы на развитие орфографической зоркости учащихся II и III ступени Презентация на тему "Комы при интоксикациях" - скачать презентации по Медицине

Презентация на тему "Комы при интоксикациях" - скачать презентации по Медицине Конструктивное и декоративное начало в изобразительном искусстве

Конструктивное и декоративное начало в изобразительном искусстве Дидактические игры на занятиях по иностранному языку

Дидактические игры на занятиях по иностранному языку Классификация рисков

Классификация рисков Принцип работы сканирующего туннельного микроскопа (СТМ). Получение изображения поверхности в режиме постоянного туннельного то

Принцип работы сканирующего туннельного микроскопа (СТМ). Получение изображения поверхности в режиме постоянного туннельного то Политика как социальный феномен и объект исследования Подготовили: студенты группы Ю092 Юридического факультета Виноградская Ек

Политика как социальный феномен и объект исследования Подготовили: студенты группы Ю092 Юридического факультета Виноградская Ек Типы высшей нервной деятельности

Типы высшей нервной деятельности Регистрация ИП

Регистрация ИП Физико-химические основы регулирования свойств буровых растворов

Физико-химические основы регулирования свойств буровых растворов  Соблюдение дидактических и методических требований к уроку с учетом психологических особенностей ребенка Докладчик Педагог-пси

Соблюдение дидактических и методических требований к уроку с учетом психологических особенностей ребенка Докладчик Педагог-пси Моторное масло

Моторное масло Массивы. Массив vs vector/string

Массивы. Массив vs vector/string Презентация по алгебре Сумма n членов арифметической прогрессии

Презентация по алгебре Сумма n членов арифметической прогрессии