Содержание

- 2. SPARC – SUN MIPS – Silicon Graphics Исторически x86 доминировала в ПК, остальные – в серверах

- 3. 2. Эволюция Intel x86 8086 16 разрядов для команд и данных, 20 – для адреса !

- 4. 286 появился защищ. режим поддержка многозадачности 386 32 разряда поддержка страничной адресации памяти мобильный вариант!

- 5. 486 в 2 раза меньше тактов на выполнение команды встроены: L1-кэш, FPU частота ядра: 40*3 МГц

- 6. 586 – Pentium два конвейера отдельные кэши L1 для команд и данных предсказание переходов 64 бит

- 7. MMX-расширение – 57 спец. команд для мультимедийных задач Н-р, операции над векторами, свёртки, преобразование Фурье 60%

- 8. Pentium Pro Исполнение по предположению Внеочередное исполнение DIB – Dual Independent Bus (see BSB, FSB) Встроен

- 9. P-II = PentiumPro + MMX Дешевле, чем PPro, за счёт вынесения L2-кэша на другой кристалл ECC

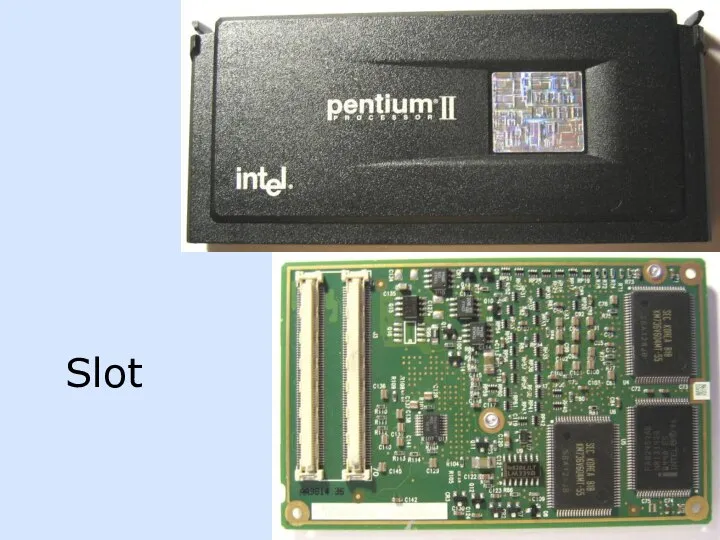

- 10. Slot

- 12. P-III Streaming SIMD Extensions обработка 4 двойных слов в FPU одновременно

- 13. Новые регистры – для обработки арифметических исключений Более надёжные расчёты Самоконтроль сбоев в микрокоде и кэше

- 14. P-IV Гиперконвейер: >20 шагов Speed Daemon

- 15. “quad pumped” bus Эффективная частота СШ до 1066 МГц SSE2 L3 до 2 МБ (Extreme Edition)

- 16. Hyper-Threading (HT) – «многопоточная» обработка Удвоение числа некоторых регистров Два потока команд Более полная загрузка ОУ

- 17. Itanium 2 VLIW 64 бит ALU, 80 – FPU, 128 – шина данных встроен L3-кэш до

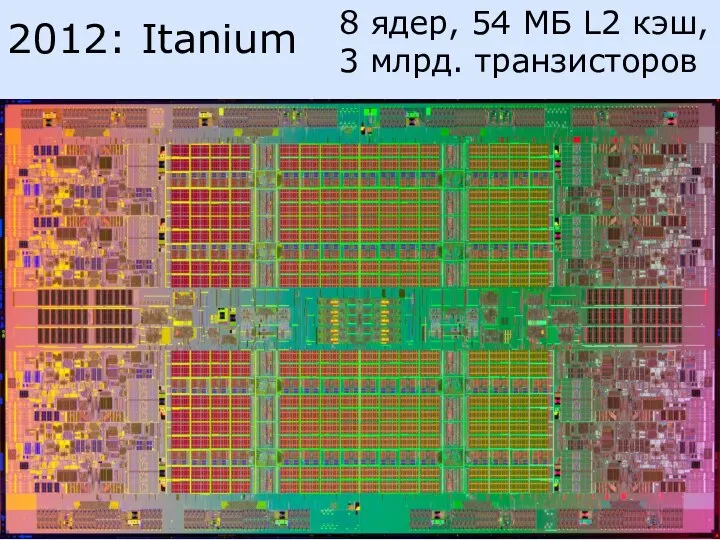

- 18. 2012: Itanium 8 ядер, 54 МБ L2 кэш, 3 млрд. транзисторов

- 19. Atom – самый маленький УЦП Intel: 25 мм2, до 2.5 Вт Ядро 1.8 ГГц, FSB 533

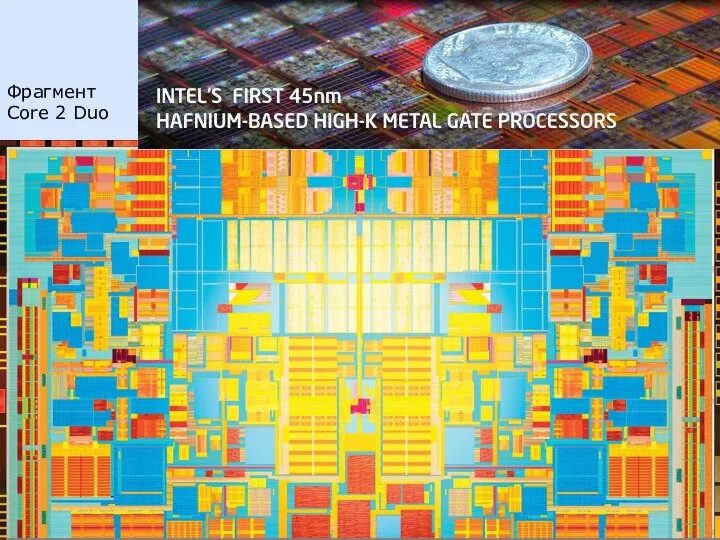

- 20. Фрагмент Core 2 Duo

- 21. 2008 C трёхканальным контроллером DDR3

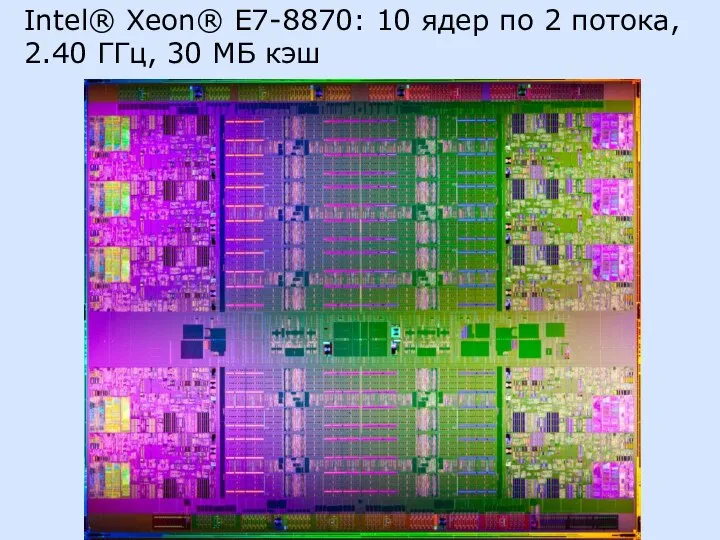

- 22. Intel® Xeon® E7-8870: 10 ядер по 2 потока, 2.40 ГГц, 30 МБ кэш

- 23. 3. Современные AMD x86 Фирма AMD основана в 1969 г. Sunnyvale, California До 1990 г. отставала

- 24. K6-II (Athlon) – герой AMD 1999 г. 3DNow! – команды для 2 real операндов мощный блок

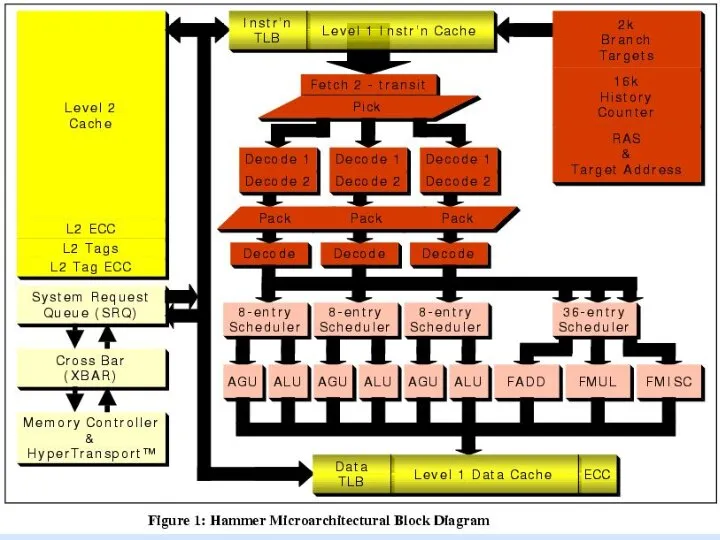

- 25. 8 поколение AMD Архитектура x86-64 (Hammer): полная совместимость с x86 64 разрядные регистры общего назначения -

- 26. Opteron – серверный ЦП: встроен 2-канальный контроллер DDR DRAM (по 4 DIMM на канал) HyperTransport линки

- 29. Athlon 64 – урезанный Opteron: одноканальный контроллер пямяти Cool‘n'Quiet Система бесшумна, если мало загружена

- 30. Sempron – урезанная (32-бит, 256 КБ L2 и 333 МГц FSB) версия Athlon 64

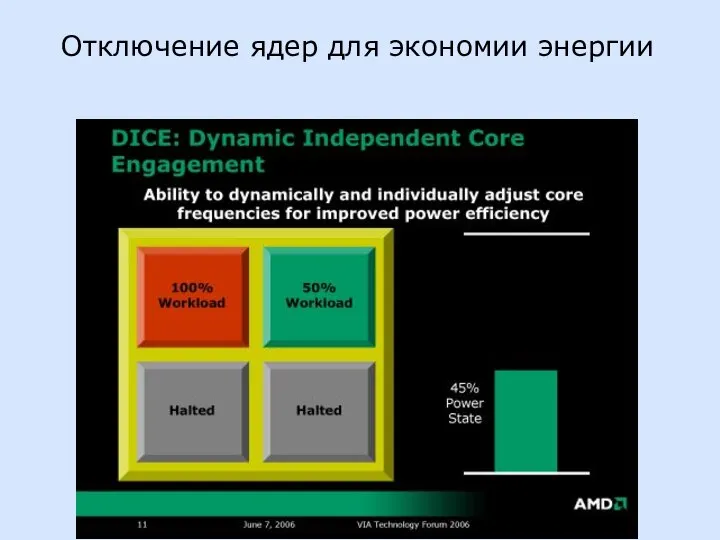

- 31. Отключение ядер для экономии энергии

- 32. Модное направление – использование GPU для научных вычислений: > 1Топ/c

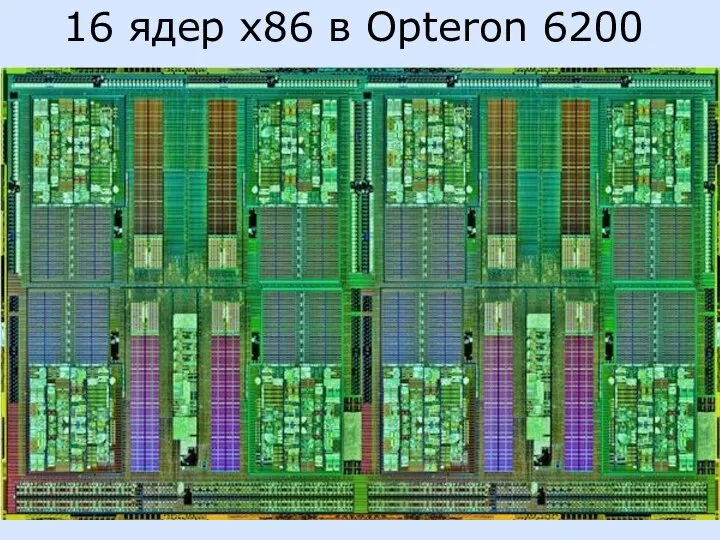

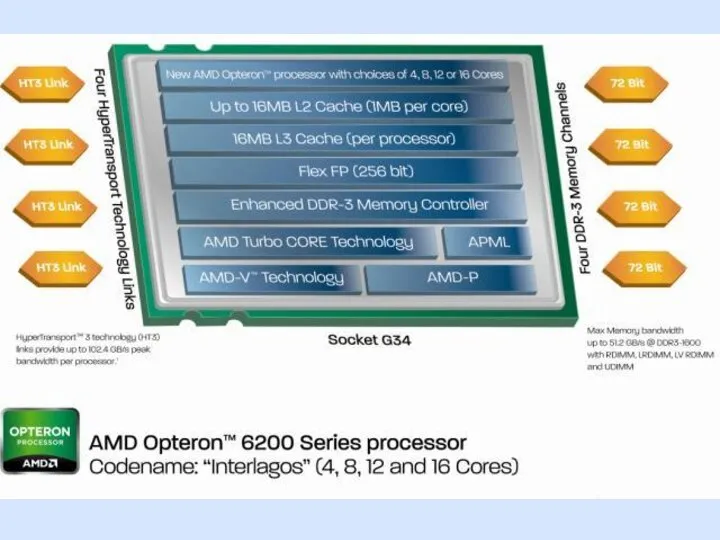

- 33. 16 ядер x86 в Opteron 6200

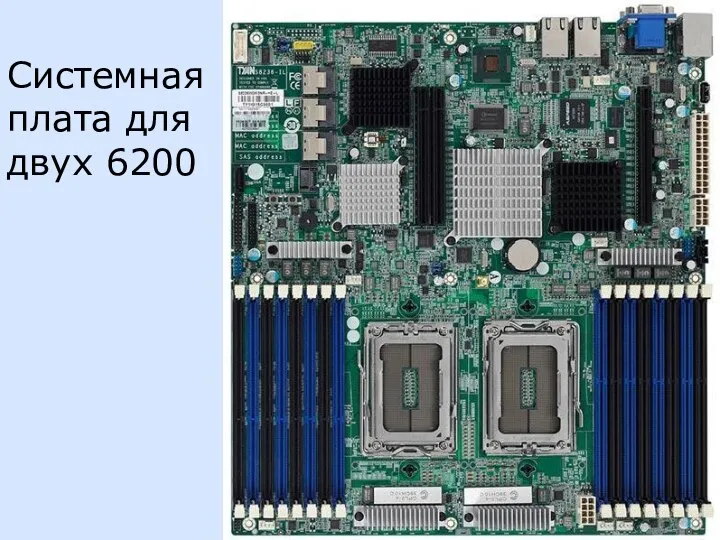

- 35. Системная плата для двух 6200

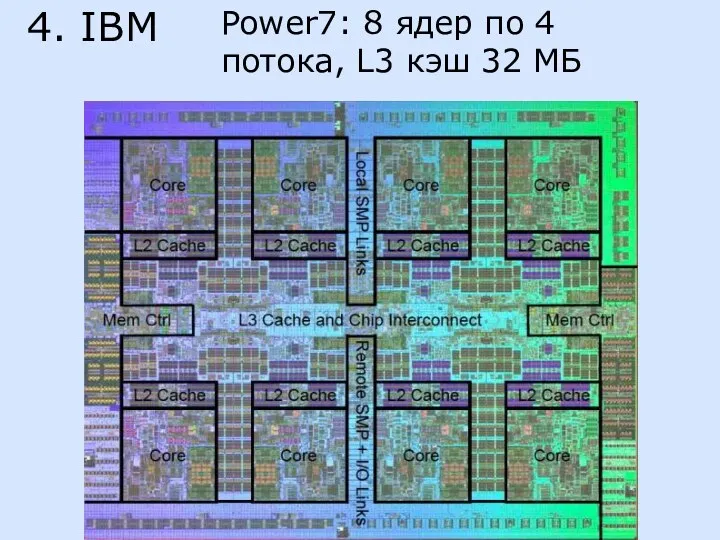

- 36. Power7: 8 ядер по 4 потока, L3 кэш 32 МБ 4. IBM

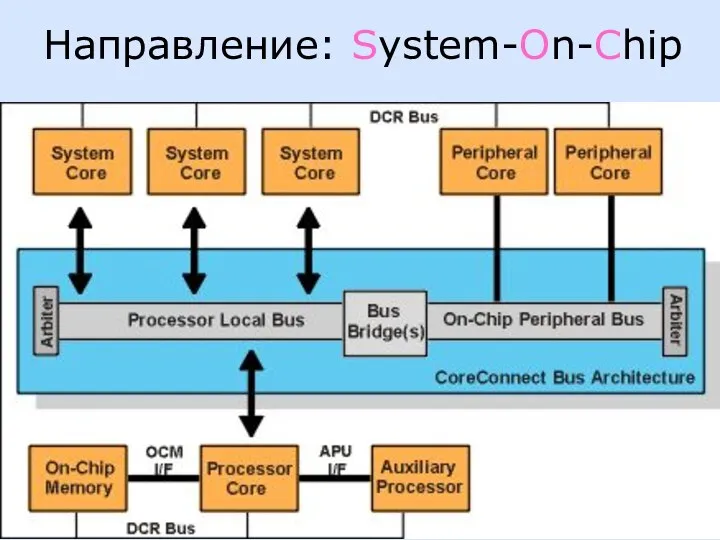

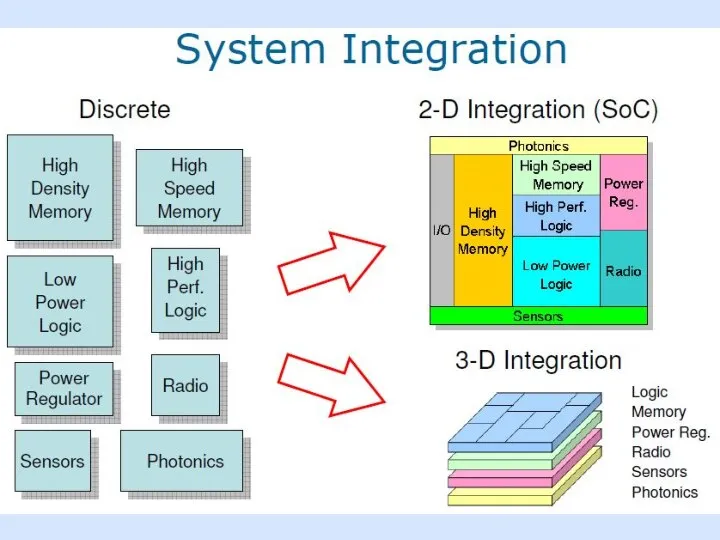

- 37. Направление: System-On-Chip

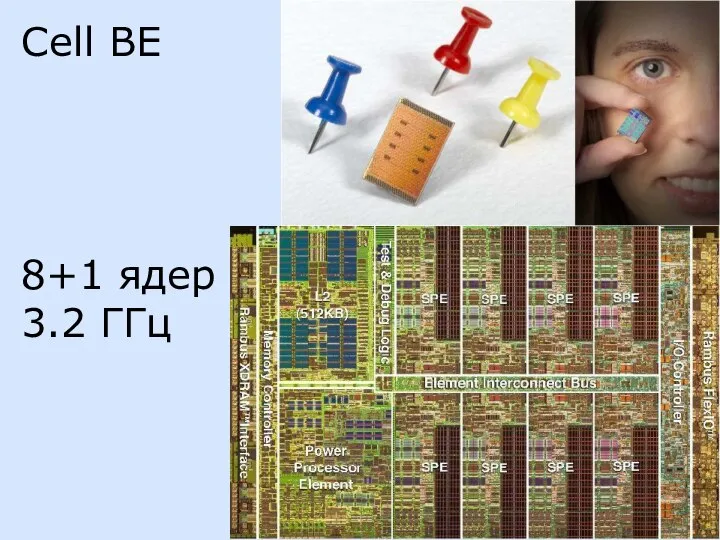

- 38. Cell BE 8+1 ядер 3.2 ГГц

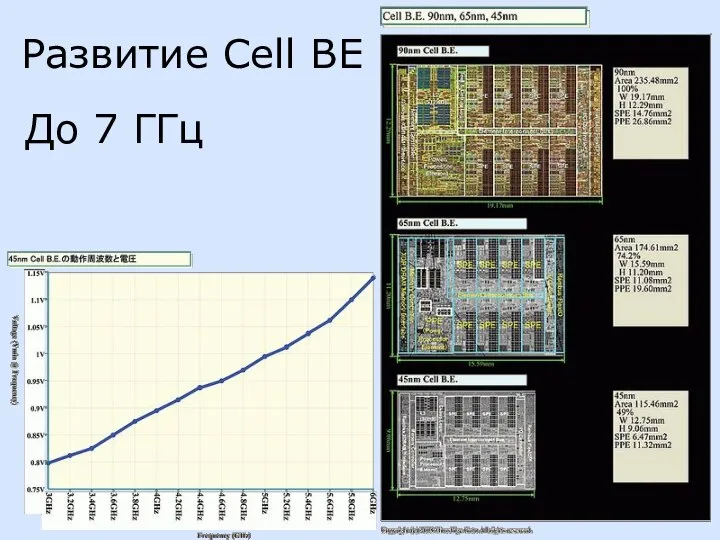

- 39. Развитие Cell BE До 7 ГГц

- 40. 5. SUN “Stanford University Network” since 1982 1987 – разработка своего CPU: SPARC – Scalable Processor

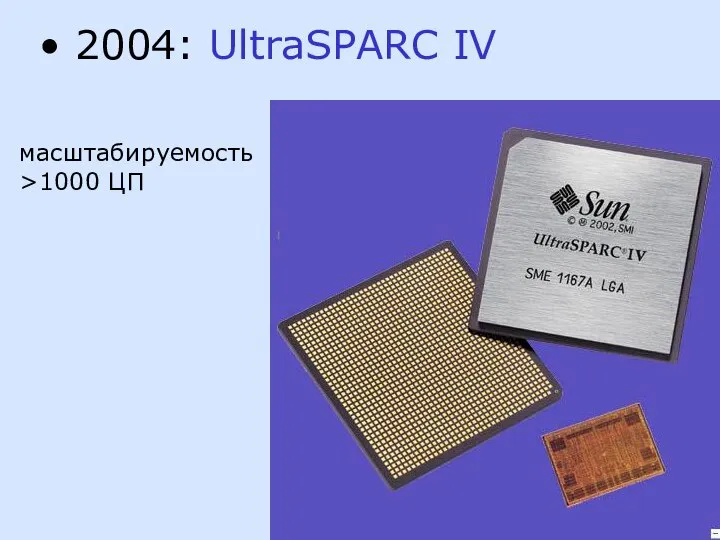

- 41. 2004: UltraSPARC IV масштабируемость >1000 ЦП

- 42. 8 ядер по 4 потока = 32 потока 1.2 ГГц 80 Вт 2005: UltraSPARC T1

- 43. 2007: UltraSPARC T2 8 ядер по 8 потоков контроллеры памяти, 10 Гб Ethernet, PCIe криптографы 1.4

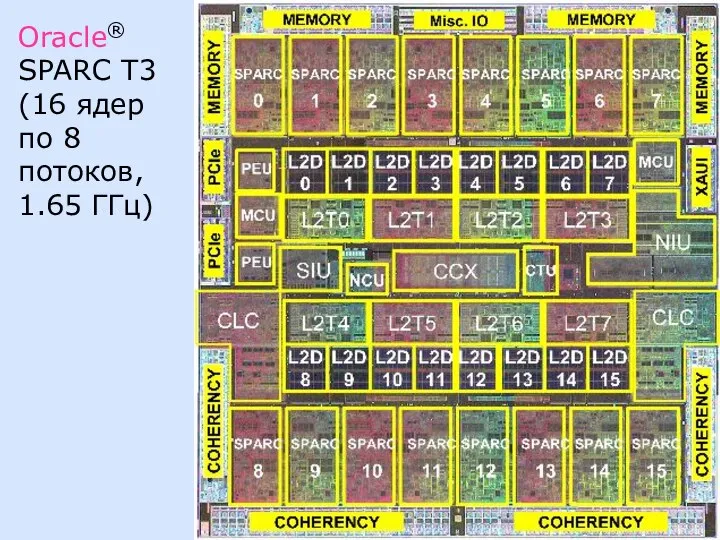

- 44. Oracle® SPARC T3 (16 ядер по 8 потоков, 1.65 ГГц)

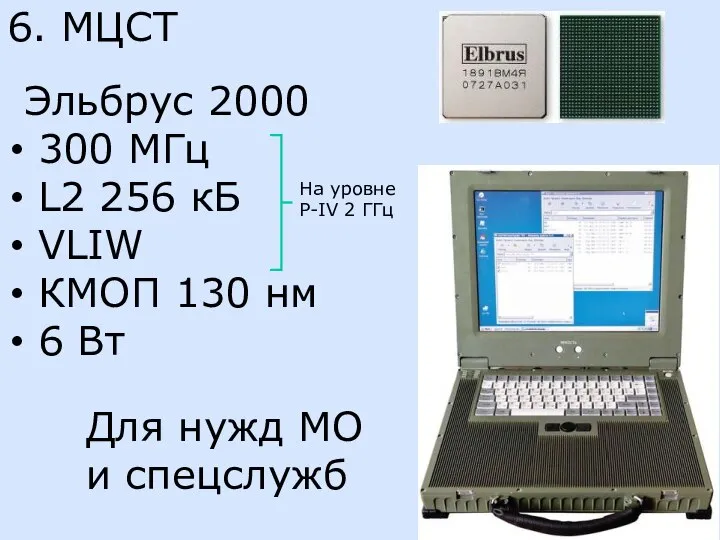

- 45. 6. МЦСТ Эльбрус 2000 300 МГц L2 256 кБ VLIW КМОП 130 нм 6 Вт На

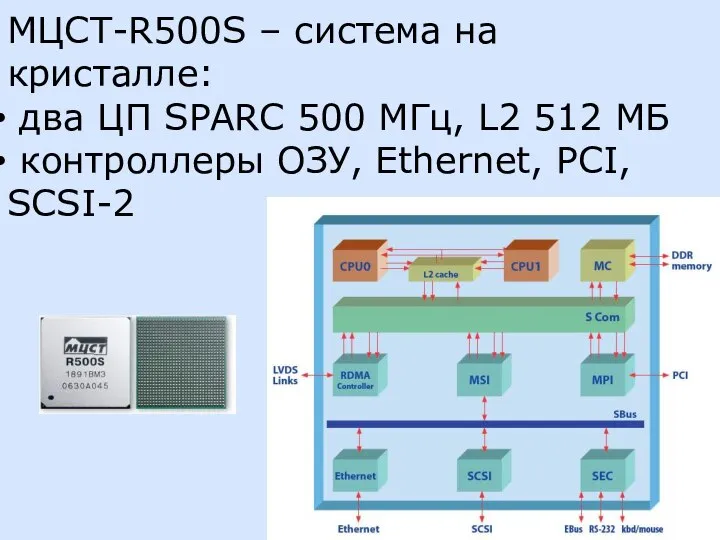

- 46. МЦСТ-R500S – система на кристалле: два ЦП SPARC 500 МГц, L2 512 МБ контроллеры ОЗУ, Ethernet,

- 47. Восьмипроцессорная одноплатная универсальная ЭВМ на базе МЦСТ-R500S Вычислительный комплекс «Эльбрус-3М1» в серверном исполнении

- 48. 7. Тенденции развития УМП Рост числа ядер числа параллельных конвейеров объёма кэшей

- 49. Brainiac-методы Уменьшение энергопотребления и размеров Интеграция с чипсетом (SOC)

- 52. Скачать презентацию

Лидерство и управление мотивацией команды Татьяна Коробенко, «Мастер-класс», г.С- Петербург

Лидерство и управление мотивацией команды Татьяна Коробенко, «Мастер-класс», г.С- Петербург  Этикет: «искусство жить по правилам»

Этикет: «искусство жить по правилам» Хэллоуин

Хэллоуин Культурология. Типология культурной деятельности людей

Культурология. Типология культурной деятельности людей Презентация "Чудеса страны восходящего Солнца" - скачать презентации по МХК

Презентация "Чудеса страны восходящего Солнца" - скачать презентации по МХК Аттестационная работа. Программа внеурочной деятельности школьников в рамках взаимодействия школа - ВУЗ - церковь

Аттестационная работа. Программа внеурочной деятельности школьников в рамках взаимодействия школа - ВУЗ - церковь Уровни стратегического планирования

Уровни стратегического планирования МЕЖДУНАРОДНЫЕ ЭКОНОМИЧЕСКИЕ ОТНОШЕНИЯ ЯРОСЛАВСКОЙ ОБЛАСТИ Студент ПКФК Группа 44-БД Бызов И.О.

МЕЖДУНАРОДНЫЕ ЭКОНОМИЧЕСКИЕ ОТНОШЕНИЯ ЯРОСЛАВСКОЙ ОБЛАСТИ Студент ПКФК Группа 44-БД Бызов И.О. Виниловые обои

Виниловые обои Методика государственной кадастровой оценки земель промышленности и иного специального назначения

Методика государственной кадастровой оценки земель промышленности и иного специального назначения Подбор людей для формирования работоспособной команды с учетом основных черт и качеств личности

Подбор людей для формирования работоспособной команды с учетом основных черт и качеств личности Компания «ГЕОметрия»

Компания «ГЕОметрия» Программирование гипертекстовых переходов

Программирование гипертекстовых переходов Easy access to embedded at SIM800(R)

Easy access to embedded at SIM800(R) London

London Инструктор-методист по альпинизму Михаил Еремкин

Инструктор-методист по альпинизму Михаил Еремкин События и делегаты

События и делегаты Неопределенность окружения проекта как фактор риска

Неопределенность окружения проекта как фактор риска Настройка веб-сервера (07)

Настройка веб-сервера (07) Демократія. Принципи демократії

Демократія. Принципи демократії О внесении изменений в Земельный кодекс Российской Федерации и отдельные законодательные акты Российской Федерации

О внесении изменений в Земельный кодекс Российской Федерации и отдельные законодательные акты Российской Федерации Лекція 1/10. Організація хеш-пошуку як узагальнення вибірки за прямою адресою, вибір хеш-функцій та розв’язання колізій

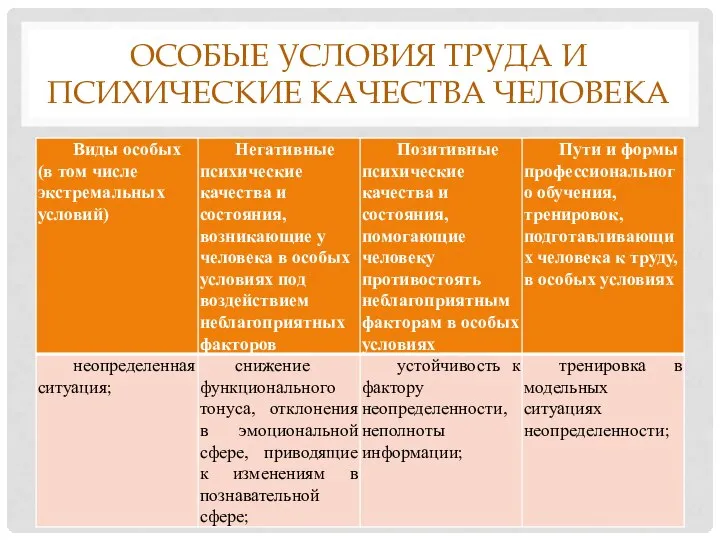

Лекція 1/10. Організація хеш-пошуку як узагальнення вибірки за прямою адресою, вибір хеш-функцій та розв’язання колізій Особые условия труда и психические качества человека

Особые условия труда и психические качества человека  ЦЕЛОЧИСЛЕННОЕ ЛИНЕЙНОЕ ПРОГРАММИРОВАНИЕ

ЦЕЛОЧИСЛЕННОЕ ЛИНЕЙНОЕ ПРОГРАММИРОВАНИЕ Против неограниченной свободы

Против неограниченной свободы Общая характеристика системы физического воспитания

Общая характеристика системы физического воспитания Характеристика общения в спорте

Характеристика общения в спорте Глобализация

Глобализация