Содержание

- 2. Шина LPC LPC (Low Pin Count) – специализированная системная периферийная шина, предназначенная для подключения Legacy-устройств. Была

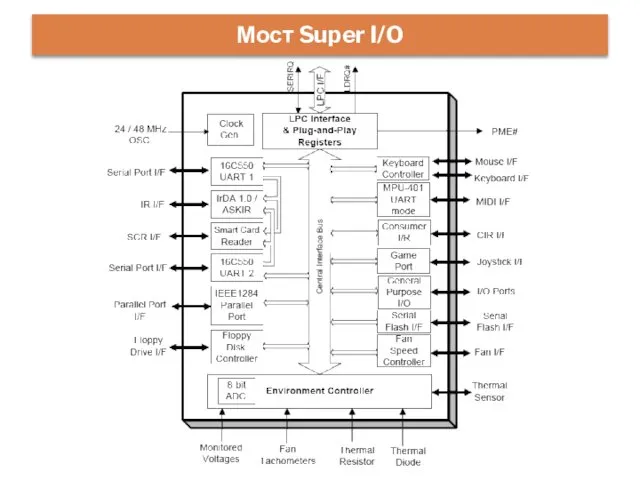

- 4. Мост Super I/O

- 5. Состав моста Super I/O Обязательные компоненты моста Super I/O: Два приемопередатчика (UART), реализующие работу асинхронного последовательного

- 6. Состав моста Super I/O Часто мост Super I/O содержит: Дополнительные контакты для подключения внешних устройств (актуально

- 7. Характеристики LPC Предназначена для подключения чипов на материнской плате. Синхронная, частота синхронизации 33 МГц, уровни напряжения

- 8. Сигналы шины LPC Обязательные сигналы: LAD[3:0] – мультиплексированная шина команд, адреса и данных LFRAME# - сигнал

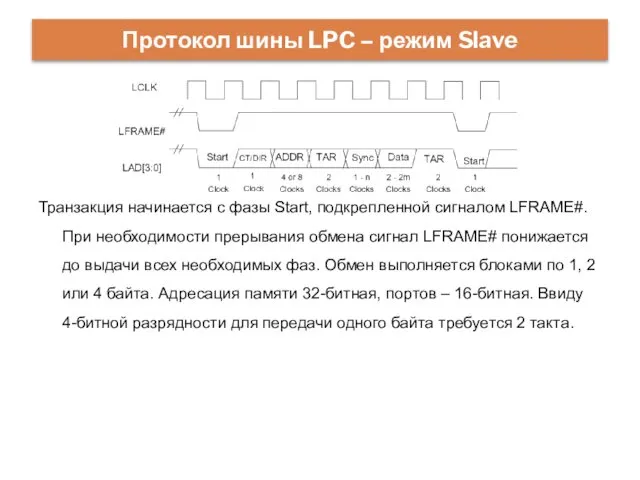

- 9. Протокол шины LPC – режим Slave Транзакция начинается с фазы Start, подкрепленной сигналом LFRAME#. При необходимости

- 10. Фазы транзакции LPC Start – начало транзакции: 0000 – начало slave-обмена, запрос от хоста 0010 –

- 11. (продолжение) ADDR – адрес, не используется в операциях DMA: Занимает 4 такта для портов и 8

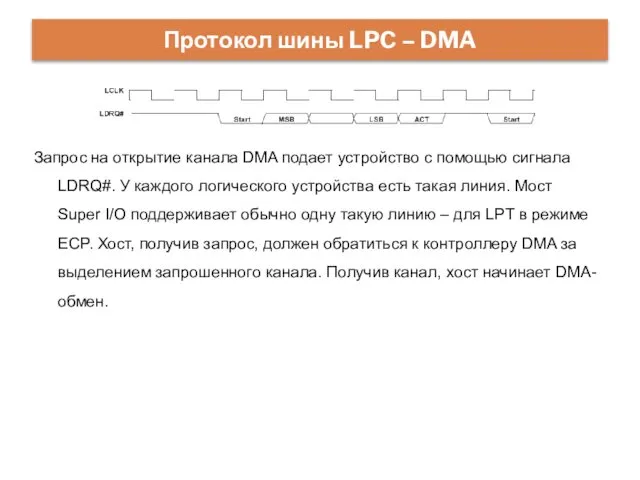

- 12. Протокол шины LPC – DMA Запрос на открытие канала DMA подает устройство с помощью сигнала LDRQ#.

- 13. (продолжение) Формат транзакции DMA изменен. Вместо фазы ADDR подается фаза Size: 00 – 8 bit 01

- 15. Скачать презентацию

![Сигналы шины LPC Обязательные сигналы: LAD[3:0] – мультиплексированная шина команд, адреса](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/469340/slide-7.jpg)

Сильноветвящиеся Б-деревья

Сильноветвящиеся Б-деревья Мастер - класс по созданию памятного поста ветерана

Мастер - класс по созданию памятного поста ветерана Добавление видеофрагментов и их воспроизведение в ходе презентации PowerPoint 2007 Жакулина Ирина Валентиновна, учитель начальных к

Добавление видеофрагментов и их воспроизведение в ходе презентации PowerPoint 2007 Жакулина Ирина Валентиновна, учитель начальных к Создание программного комплекса автоматического функционального тестирования СОДС МАРШ!-3.0

Создание программного комплекса автоматического функционального тестирования СОДС МАРШ!-3.0 Автоматизированная система управления

Автоматизированная система управления Ёжик. Картинки

Ёжик. Картинки Команды mmx/xmm

Команды mmx/xmm Способы передачи электронных документов

Способы передачи электронных документов Битрикс24: повышаем эффективность работы компании

Битрикс24: повышаем эффективность работы компании Электронная информационно-образовательная среда

Электронная информационно-образовательная среда Презентация "Уроки с использованием компьютерных технологий в учебном процессе" - скачать презентации по Информатике

Презентация "Уроки с использованием компьютерных технологий в учебном процессе" - скачать презентации по Информатике Основные понятия ООП

Основные понятия ООП АЛГОРИТМИКА И ОЛИМПИАДЫ ПО ИНФОРМАТИКЕ ДЛЯ 5-6 КЛАССОВ ЦВЕТКОВА М.С.

АЛГОРИТМИКА И ОЛИМПИАДЫ ПО ИНФОРМАТИКЕ ДЛЯ 5-6 КЛАССОВ ЦВЕТКОВА М.С.  Как GC освобождает память

Как GC освобождает память Системы контроля версий: виды, принципы организации работы

Системы контроля версий: виды, принципы организации работы Безопасный интернет. Игра для 7 - 9-х классов

Безопасный интернет. Игра для 7 - 9-х классов Normal formalar

Normal formalar Профессиональная переподготовка. «Библиотечно-информационная деятельность». Библиотековедение

Профессиональная переподготовка. «Библиотечно-информационная деятельность». Библиотековедение Компьютерная модель чайного сервиза

Компьютерная модель чайного сервиза Алгоритм Евклида

Алгоритм Евклида Технология клиент-сервер

Технология клиент-сервер Мультимедийные технологии Борисов В.А. Красноармейский филиал ГОУ ВПО «Академия народного хозяйства при Правительстве РФ» Кр

Мультимедийные технологии Борисов В.А. Красноармейский филиал ГОУ ВПО «Академия народного хозяйства при Правительстве РФ» Кр Помехоустойчивое кодирование

Помехоустойчивое кодирование Электронная почта

Электронная почта Информационные модели

Информационные модели Политика сетевой безопасности

Политика сетевой безопасности Вкладені алгоритмічні структури повторення з лічильником. Вкладені цикли з лічильником

Вкладені алгоритмічні структури повторення з лічильником. Вкладені цикли з лічильником Результаты поиска литературы в электронных каталогах

Результаты поиска литературы в электронных каталогах