Содержание

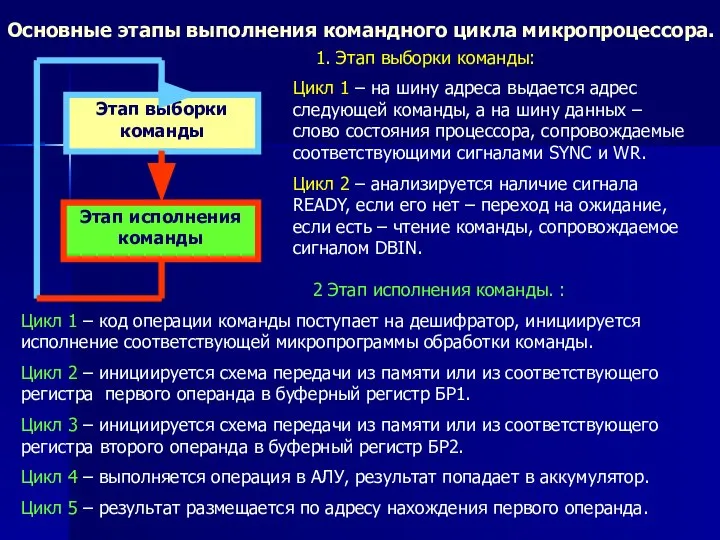

- 2. Основные этапы выполнения командного цикла микропроцессора. Этап выборки команды Этап исполнения команды 1. Этап выборки команды:

- 3. Система машинных команд микропроцессора. Разнообразие типов данных, форм их представления и действий, которые необходимы для обработки

- 4. Форматы машинных команд. Под форматом команды понимается ее длина, количество, размер, положение, назначение и способ кодирования

- 5. Способы адресации операндов в команде. Способ адресации определяет, каким образом следует использовать информацию, размещенную в поле

- 6. Классификация машинных команд по системам операций. Все операции, выполняемые микропроцессором по кодам операций машинных команд принято

- 7. 9. Базовая схема центрального процессора ПЭВМ Intel 8080 КР 580ВМ80А

- 8. Условные обозначения: А - регистр аккумулятор, БР1, БР2 – буферные регистры, РП - регистр признаков (флагов)

- 9. Эволюция архитектуры процессоров ПЭВМ семейства х86. Аналогичные процессора, совместимые по архитектуре с х86, в разное время

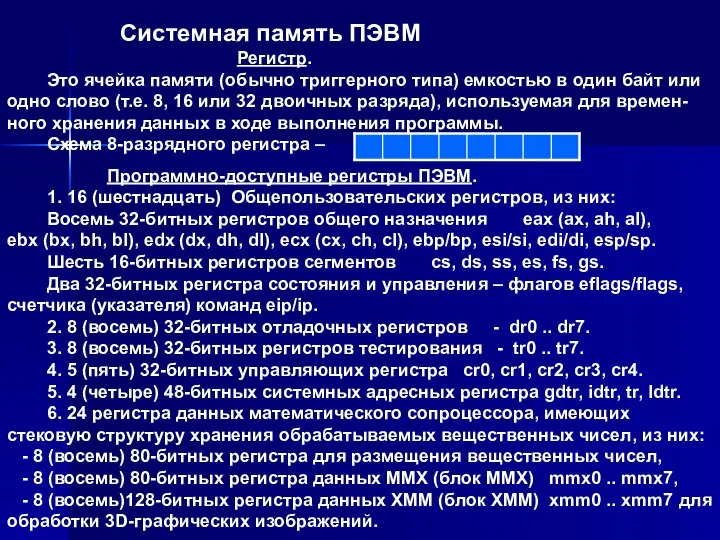

- 10. Системная память ПЭВМ Регистр. Это ячейка памяти (обычно триггерного типа) емкостью в один байт или одно

- 11. Программно-регистровая модель ПЭВМ. 31 23 15 7 0 AX DX CX BX EAX EDX ECX EBXEBP

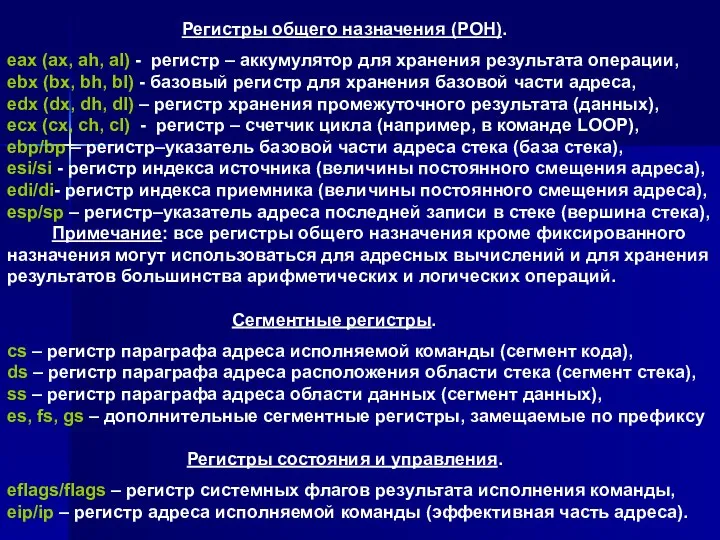

- 12. Регистры общего назначения (РОН). eax (ax, ah, al) - регистр – аккумулятор для хранения результата операции,

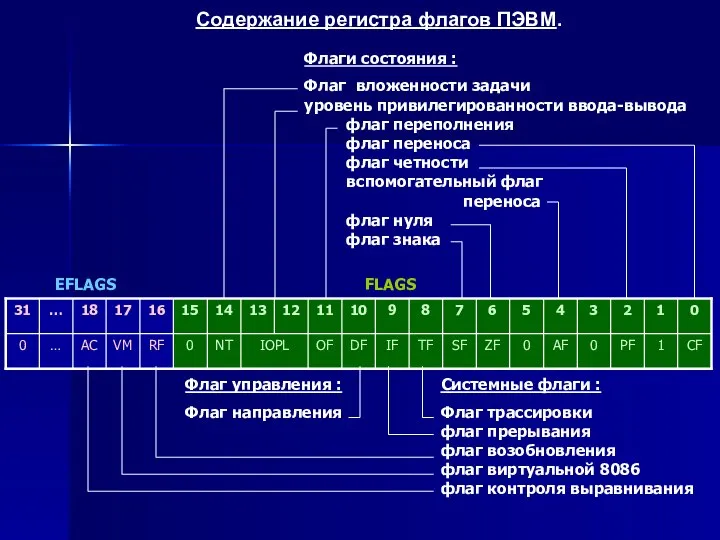

- 13. Содержание регистра флагов ПЭВМ. Системные флаги : Флаг трассировки флаг прерывания флаг возобновления флаг виртуальной 8086

- 14. 10. Схема построения машинных кодов команд центрального процессора. длина команды в байтах ( Lmax= 15 байт

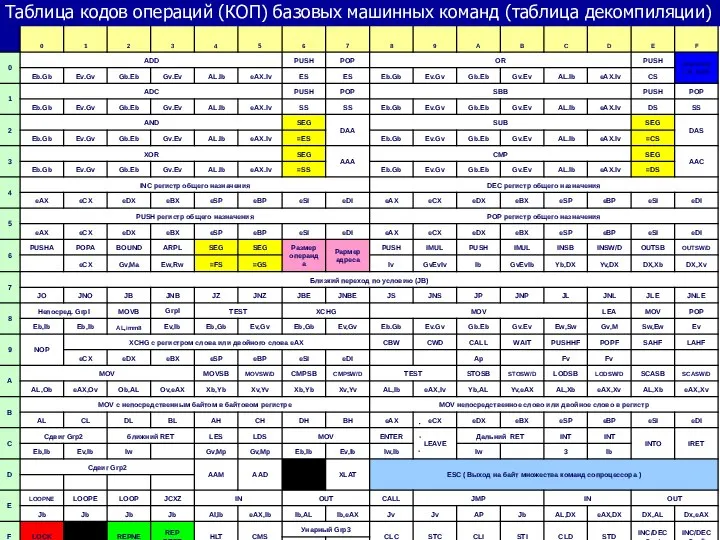

- 15. Таблица кодов операций (КОП) базовых машинных команд (таблица декомпиляции)

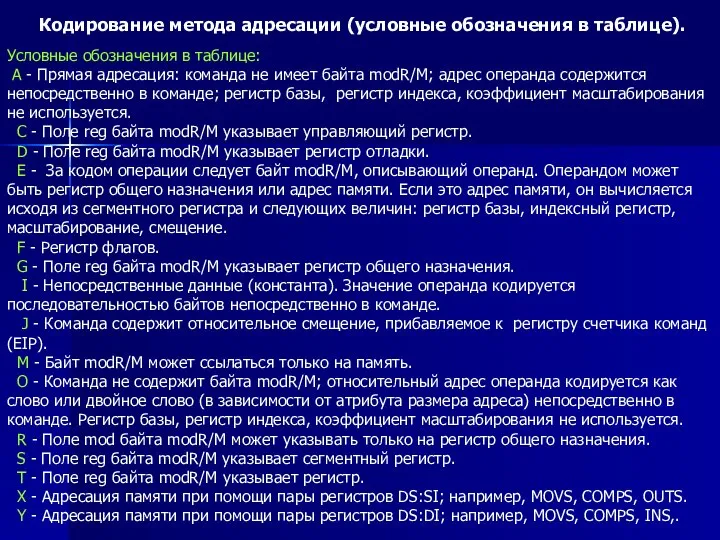

- 16. Кодирование метода адресации (условные обозначения в таблице). Условные обозначения в таблице: A - Прямая адресация: команда

- 17. Кодирование типов операндов (условные обозначения в таблице). Условные обозначения в таблице: а - Два операнда длиной

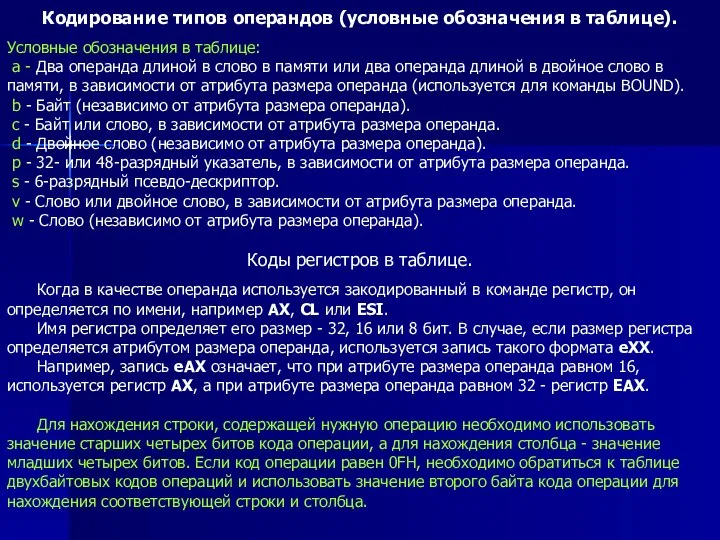

- 18. Дополнительные таблицы кодов операций машинных команд. Существует ряд дополнительных таблиц расширения кодов операций машинных команд, доступных

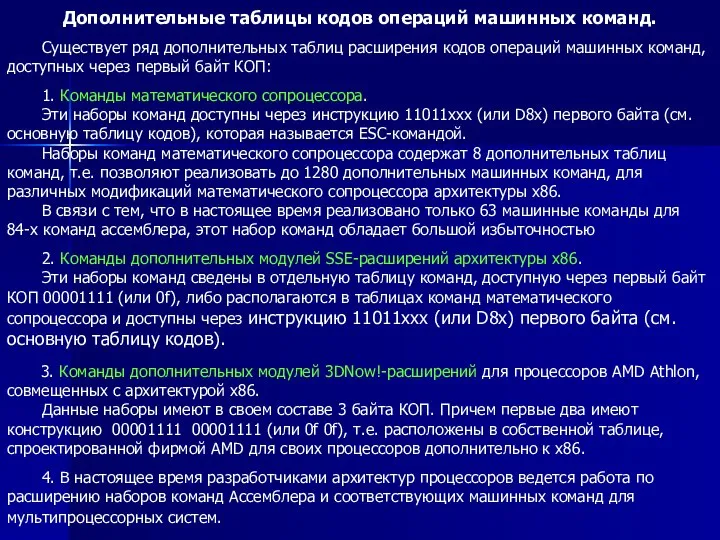

- 19. Примеры формирования кода машинной команды Команда MOV пересылки данных: Из регистра 1 в регистр 2 88

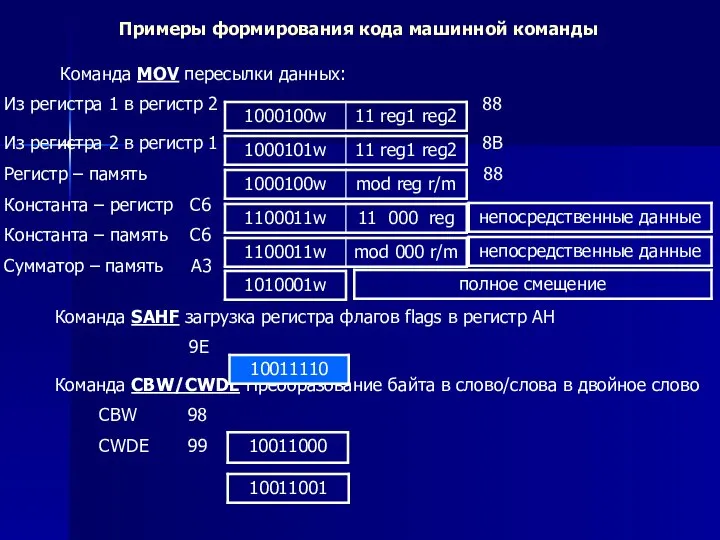

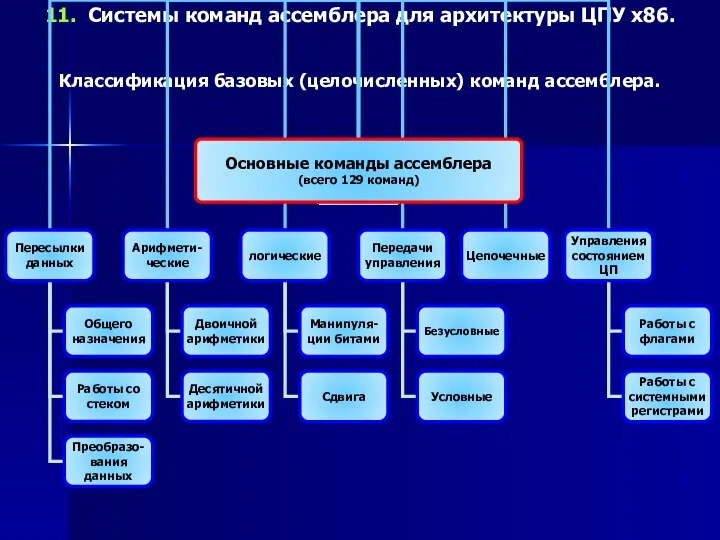

- 20. 11. Системы команд ассемблера для архитектуры ЦПУ х86. Классификация базовых (целочисленных) команд ассемблера.

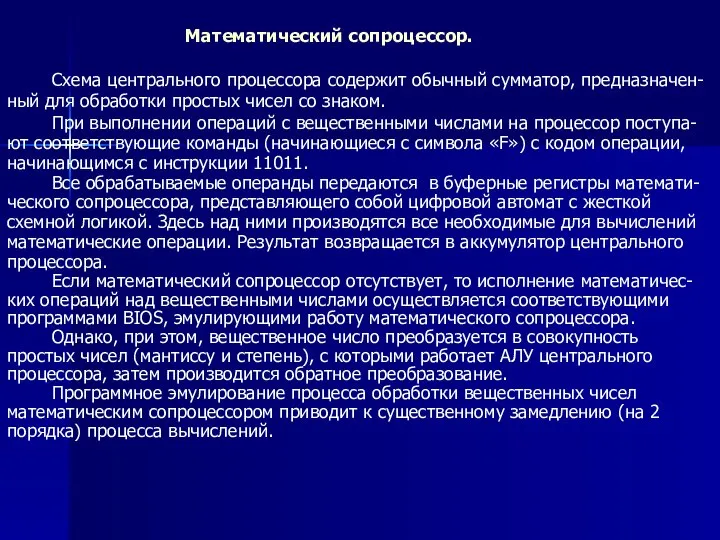

- 21. Математический сопроцессор. Схема центрального процессора содержит обычный сумматор, предназначен-ный для обработки простых чисел со знаком. При

- 22. Принципиальная схема математического сопроцессора. 80-разрядный стековый регистр st(0) Регистр 1 Регистр 2 Регистр данных Внутренняя шина

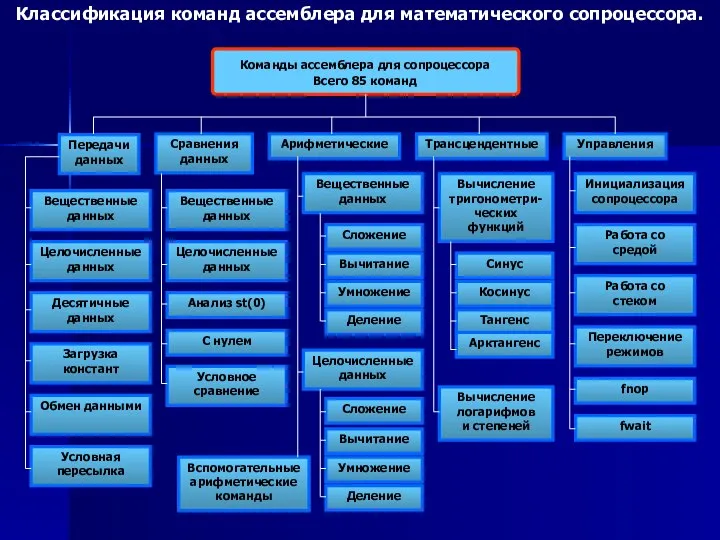

- 23. Классификация команд ассемблера для математического сопроцессора. Команды ассемблера для сопроцессора Всего 85 команд Передачи данных Сравнения

- 24. Классификация команд ассемблера для ММХ-расширения процессора. Команды ассемблера для ММХ-расширения Всего 41 команда Пересылки данных Сравнения

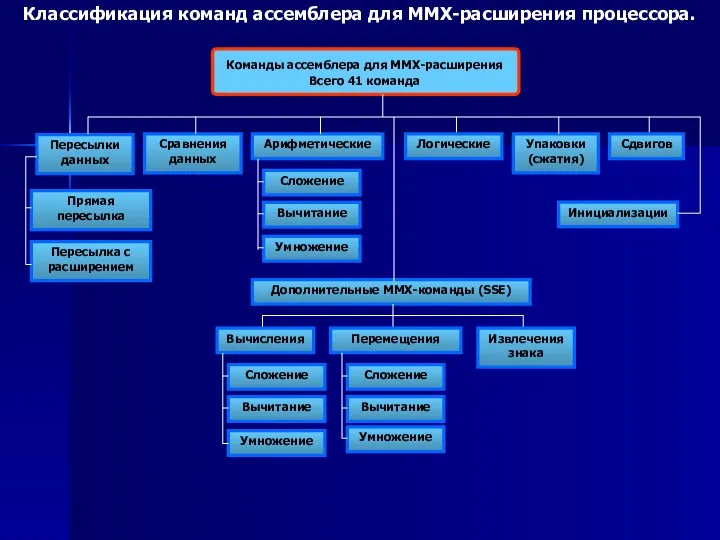

- 25. Классификация команд ассемблера для ХММ-расширения SSE-2. Команды ассемблера для ХММ-расширения Всего 149 команд Пересылки данных Сравнения

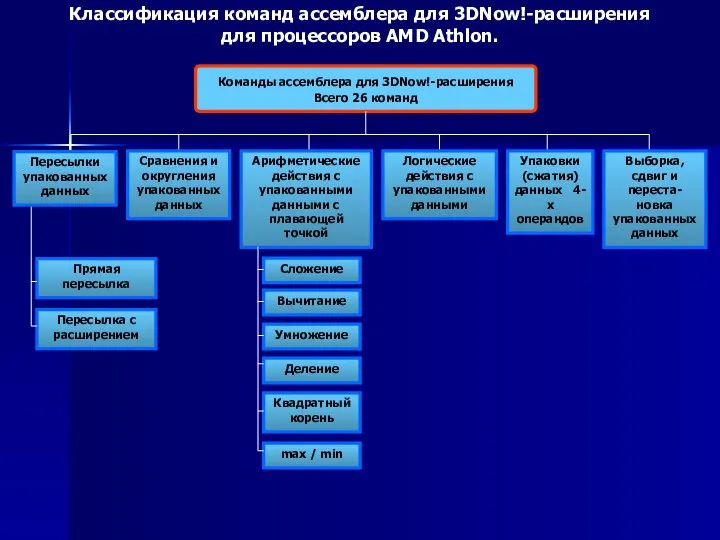

- 26. Классификация команд ассемблера для 3DNow!-расширения для процессоров AMD Athlon. Команды ассемблера для 3DNow!-расширения Всего 26 команд

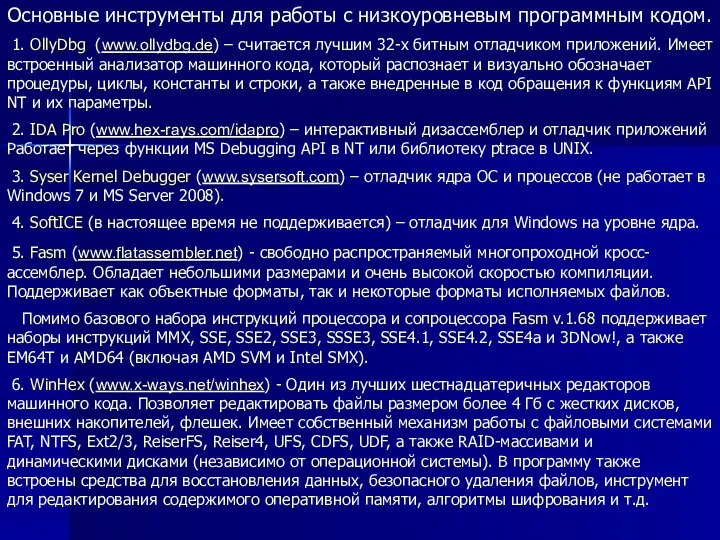

- 27. Основные инструменты для работы с низкоуровневым программным кодом. 1. OllyDbg (www.ollydbg.de) – считается лучшим 32-х битным

- 29. Скачать презентацию

Основные этапы выполнения командного цикла микропроцессора.

Этап выборки команды

Этап исполнения команды

Основные этапы выполнения командного цикла микропроцессора.

Этап выборки команды

Этап исполнения команды

Цикл 1 – на шину адреса выдается адрес следующей команды, а на шину данных – слово состояния процессора, сопровождаемые соответствующими сигналами SYNC и WR.

Цикл 2 – анализируется наличие сигнала READY, если его нет – переход на ожидание, если есть – чтение команды, сопровождаемое сигналом DBIN.

2 Этап исполнения команды. :

Цикл 1 – код операции команды поступает на дешифратор, инициируется исполнение соответствующей микропрограммы обработки команды.

Цикл 2 – инициируется схема передачи из памяти или из соответствующего регистра первого операнда в буферный регистр БР1.

Цикл 3 – инициируется схема передачи из памяти или из соответствующего регистра второго операнда в буферный регистр БР2.

Цикл 4 – выполняется операция в АЛУ, результат попадает в аккумулятор.

Цикл 5 – результат размещается по адресу нахождения первого операнда.

Система машинных команд микропроцессора.

Разнообразие типов данных, форм их представления

Система машинных команд микропроцессора.

Разнообразие типов данных, форм их представления

Система команд должна обладать двумя свойствами – функциональной полнотой и эффективностью.

Функциональная полнота – достаточность системы команд для описания любого алгоритма обработки информации. Известно, что свойством функциональной полноты обладает система, состоящая всего из трех команд (присвоение 0, проверка на 0, присвоение 1), однако построение программ на ее основе неэффективно.

Эффективность системы команд – степень соответствия системы команд назначению ПЭВМ, т.е. классу алгоритмов, для выполнения которых предназначена ПЭВМ. Необходимо отметить, что реализация развитой системы команд требует расширения операционной части процессора, увеличению числа и разрядности дополнительных групп регистров, что приводит к увеличению стоимости и энергоемкости процессоров.

Система команд процессора характеризуется форматами команд, способами адресации и системой операций.

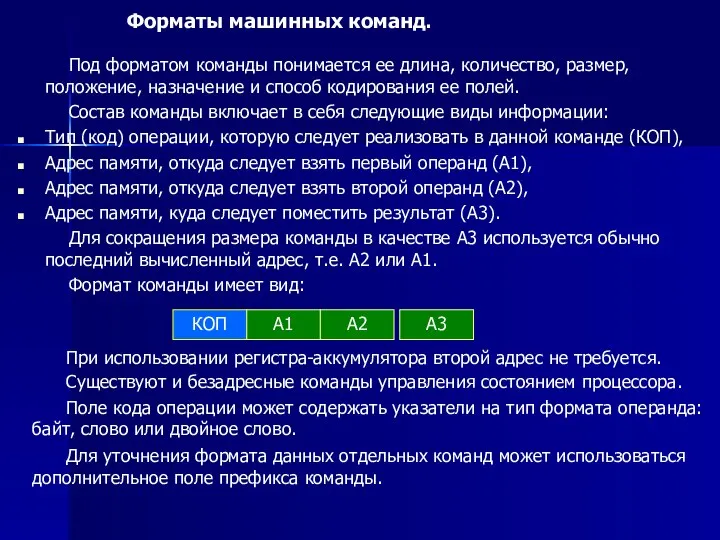

Форматы машинных команд.

Под форматом команды понимается ее длина, количество,

Форматы машинных команд.

Под форматом команды понимается ее длина, количество,

Состав команды включает в себя следующие виды информации:

Тип (код) операции, которую следует реализовать в данной команде (КОП),

Адрес памяти, откуда следует взять первый операнд (А1),

Адрес памяти, откуда следует взять второй операнд (А2),

Адрес памяти, куда следует поместить результат (А3).

Для сокращения размера команды в качестве А3 используется обычно последний вычисленный адрес, т.е. А2 или А1.

Формат команды имеет вид:

КОП

А1

А2

При использовании регистра-аккумулятора второй адрес не требуется.

Существуют и безадресные команды управления состоянием процессора.

Поле кода операции может содержать указатели на тип формата операнда: байт, слово или двойное слово.

Для уточнения формата данных отдельных команд может использоваться дополнительное поле префикса команды.

А3

Способы адресации операндов в команде.

Способ адресации определяет, каким образом

Способы адресации операндов в команде.

Способ адресации определяет, каким образом

Существует пять основных способов адресации операндов:

Непосредственная – в поле адреса команды располагается не адрес, а непосредственно сам операнд (константа),

Прямая - в поле адреса команды располагается адрес операнда,

Косвенная - в поле адреса команды располагается не адрес операнда, а адрес ячейки памяти, в которой хранится адрес операнда (адрес адреса операнда),

Относительная – адрес операнда формируется, как сумма двух слагаемых: базы, хранящемся в специальном регистре или в одном из регистров общего назначения и смещения, извлекаемого из поля адреса команды. Иногда к базе добавляется индекс, увеличивающий или уменьшающий свое значение на единицу после каждого обращения.

Безадресная – поле адреса в команде отсутствует, а адрес операнда или не имеет смысла, так как сам операнд не нужен )что характерно для системных команд), или адрес его подразумевается по умолчанию (например, аккумулятор). Одной из разновидностей безадресного обращения является использование стековой памяти или стека.

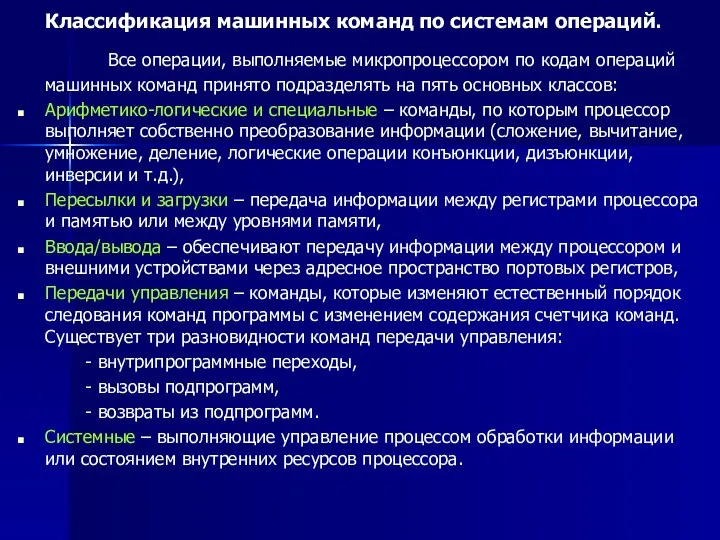

Классификация машинных команд по системам операций.

Все операции, выполняемые микропроцессором

Классификация машинных команд по системам операций.

Все операции, выполняемые микропроцессором

Арифметико-логические и специальные – команды, по которым процессор выполняет собственно преобразование информации (сложение, вычитание, умножение, деление, логические операции конъюнкции, дизъюнкции, инверсии и т.д.),

Пересылки и загрузки – передача информации между регистрами процессора и памятью или между уровнями памяти,

Ввода/вывода – обеспечивают передачу информации между процессором и внешними устройствами через адресное пространство портовых регистров,

Передачи управления – команды, которые изменяют естественный порядок следования команд программы с изменением содержания счетчика команд. Существует три разновидности команд передачи управления:

- внутрипрограммные переходы,

- вызовы подпрограмм,

- возвраты из подпрограмм.

Системные – выполняющие управление процессом обработки информации или состоянием внутренних ресурсов процессора.

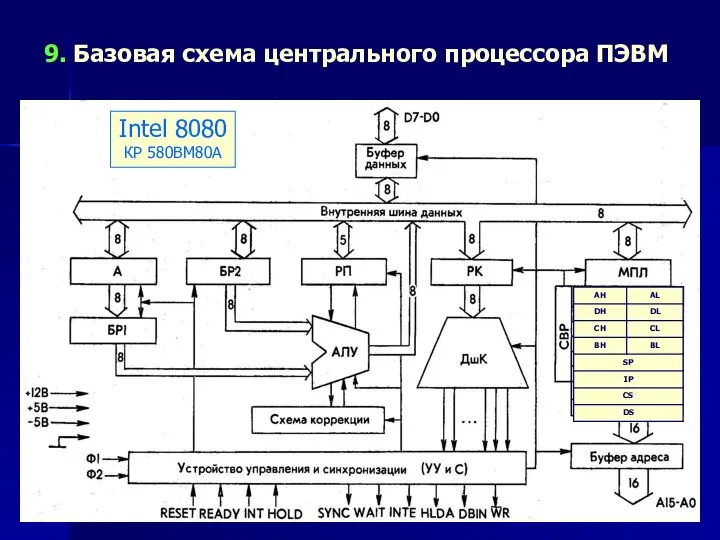

9. Базовая схема центрального процессора ПЭВМ

Intel 8080 КР 580ВМ80А

9. Базовая схема центрального процессора ПЭВМ

Intel 8080 КР 580ВМ80А

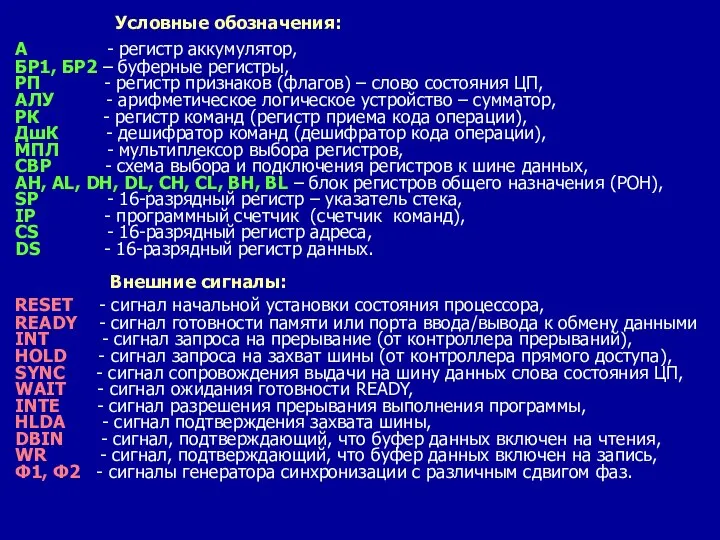

Условные обозначения:

А - регистр аккумулятор,

БР1, БР2 – буферные регистры,

РП -

Условные обозначения:

А - регистр аккумулятор,

БР1, БР2 – буферные регистры,

РП -

АЛУ - арифметическое логическое устройство – сумматор,

РК - регистр команд (регистр приема кода операции),

ДшК - дешифратор команд (дешифратор кода операции),

МПЛ - мультиплексор выбора регистров,

СВР - схема выбора и подключения регистров к шине данных,

AH, AL, DH, DL, CH, CL, BH, BL – блок регистров общего назначения (РОН),

SP - 16-разрядный регистр – указатель стека,

IP - программный счетчик (счетчик команд),

CS - 16-разрядный регистр адреса,

DS - 16-разрядный регистр данных.

Внешние сигналы:

RESET - сигнал начальной установки состояния процессора,

READY - сигнал готовности памяти или порта ввода/вывода к обмену данными

INT - сигнал запроса на прерывание (от контроллера прерываний),

HOLD - сигнал запроса на захват шины (от контроллера прямого доступа),

SYNC - сигнал сопровождения выдачи на шину данных слова состояния ЦП,

WAIT - сигнал ожидания готовности READY,

INTE - сигнал разрешения прерывания выполнения программы,

HLDA - сигнал подтверждения захвата шины,

DBIN - сигнал, подтверждающий, что буфер данных включен на чтения,

WR - сигнал, подтверждающий, что буфер данных включен на запись,

Ф1, Ф2 - сигналы генератора синхронизации с различным сдвигом фаз.

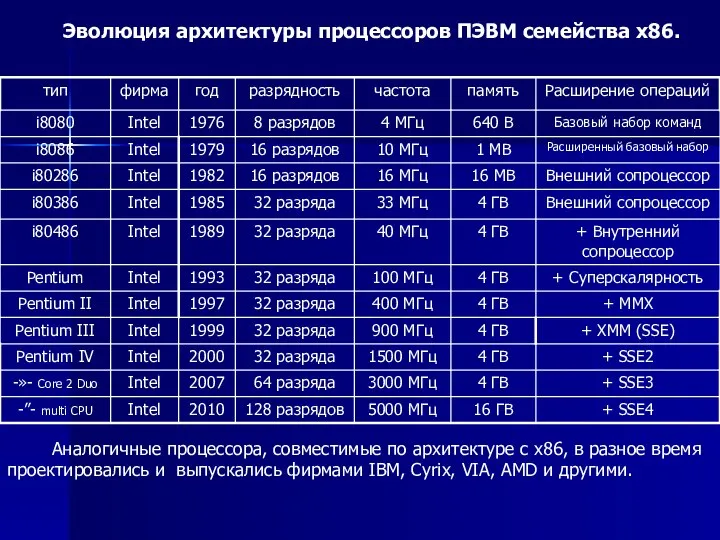

Эволюция архитектуры процессоров ПЭВМ семейства х86.

Аналогичные процессора, совместимые по

Эволюция архитектуры процессоров ПЭВМ семейства х86.

Аналогичные процессора, совместимые по

Системная память ПЭВМ

Регистр.

Это ячейка памяти (обычно триггерного

Системная память ПЭВМ

Регистр.

Это ячейка памяти (обычно триггерного

Схема 8-разрядного регистра –

Программно-доступные регистры ПЭВМ.

1. 16 (шестнадцать) Общепользовательских регистров, из них:

Восемь 32-битных регистров общего назначения eax (ax, ah, al),

ebx (bx, bh, bl), edx (dx, dh, dl), ecx (cx, ch, cl), ebp/bp, esi/si, edi/di, esp/sp.

Шесть 16-битных регистров сегментов cs, ds, ss, es, fs, gs.

Два 32-битных регистра состояния и управления – флагов eflags/flags, счетчика (указателя) команд eip/ip.

2. 8 (восемь) 32-битных отладочных регистров - dr0 .. dr7.

3. 8 (восемь) 32-битных регистров тестирования - tr0 .. tr7.

4. 5 (пять) 32-битных управляющих регистра cr0, cr1, cr2, cr3, cr4.

5. 4 (четыре) 48-битных системных адресных регистра gdtr, idtr, tr, ldtr.

6. 24 регистра данных математического сопроцессора, имеющих стековую структуру хранения обрабатываемых вещественных чисел, из них:

- 8 (восемь) 80-битных регистра для размещения вещественных чисел,

- 8 (восемь) 80-битных регистра данных MMX (блок ММХ) mmx0 .. mmx7,

- 8 (восемь)128-битных регистра данных XMM (блок ХММ) xmm0 .. xmm7 для обработки 3D-графических изображений.

Программно-регистровая модель ПЭВМ.

31 23 15 7 0

AX

Программно-регистровая модель ПЭВМ.

31 23 15 7 0

AX

EAX EDX ECX EBXEBP ESI EDI ESP

EIP EFLAGS

Регистры общего назначения (РОН).

eax (ax, ah, al) - регистр

Регистры общего назначения (РОН).

eax (ax, ah, al) - регистр

ebx (bx, bh, bl) - базовый регистр для хранения базовой части адреса,

edx (dx, dh, dl) – регистр хранения промежуточного результата (данных),

ecx (cx, ch, cl) - регистр – счетчик цикла (например, в команде LOOP),

ebp/bp – регистр–указатель базовой части адреса стека (база стека),

esi/si - регистр индекса источника (величины постоянного смещения адреса),

edi/di- регистр индекса приемника (величины постоянного смещения адреса),

esp/sp – регистр–указатель адреса последней записи в стеке (вершина стека),

Примечание: все регистры общего назначения кроме фиксированного назначения могут использоваться для адресных вычислений и для хранения результатов большинства арифметических и логических операций.

Сегментные регистры.

cs – регистр параграфа адреса исполняемой команды (сегмент кода),

ds – регистр параграфа адреса расположения области стека (сегмент стека),

ss – регистр параграфа адреса области данных (сегмент данных),

es, fs, gs – дополнительные сегментные регистры, замещаемые по префиксу

Регистры состояния и управления.

eflags/flags – регистр системных флагов результата исполнения команды,

eip/ip – регистр адреса исполняемой команды (эффективная часть адреса).

Содержание регистра флагов ПЭВМ.

Системные флаги :

Флаг трассировки флаг прерывания

Содержание регистра флагов ПЭВМ.

Системные флаги :

Флаг трассировки флаг прерывания

Флаги состояния :

Флаг вложенности задачи уровень привилегированности ввода-вывода

флаг переполнения

флаг переноса

флаг четности

вспомогательный флаг

переноса

флаг нуля

флаг знака

Флаг управления :

Флаг направления

EFLAGS FLAGS

10. Схема построения машинных кодов команд центрального процессора.

длина

10. Схема построения машинных кодов команд центрального процессора.

длина

режим адресации режим масштабирования адреса

mod – 00 – абсолютный адрес операнда (байта смещения нет)

01 – имеется один байт смещения адреса операнда

10 – имеется два байта смещения адреса операнда

11 – операнд в регистре

reg – 000 – AL или AX при w=1 ss – 00 - множитель 1

001 – CL или CX при w=1 01 - множитель 2

010 – DL или DX при w=1 10 - множитель 4

011 – BL или BX при w=1 11 - множитель 8

100 – AH или SP при w=1

101 – CH или BP при w=1

110 – DH или SI при w=1

111 – BH или DI при w=1

префиксы

Максимум 3 префикса

3Fh.

67h

66h

2Eh…

0Fh

Таблица кодов операций (КОП) базовых машинных команд (таблица декомпиляции)

Таблица кодов операций (КОП) базовых машинных команд (таблица декомпиляции)

Кодирование метода адресации (условные обозначения в таблице).

Условные обозначения в таблице:

Кодирование метода адресации (условные обозначения в таблице).

Условные обозначения в таблице:

C - Поле reg байта modR/M указывает управляющий регистр.

D - Поле reg байта modR/M указывает регистр отладки.

E - За кодом операции следует байт modR/M, описывающий операнд. Операндом может быть регистр общего назначения или адрес памяти. Если это адрес памяти, он вычисляется исходя из сегментного регистра и следующих величин: регистр базы, индексный регистр, масштабирование, смещение.

F - Регистр флагов.

G - Поле reg байта modR/M указывает регистр общего назначения.

I - Непосредственные данные (константа). Значение операнда кодируется последовательностью байтов непосредственно в команде.

J - Команда содержит относительное смещение, прибавляемое к регистру счетчика команд (EIP).

M - Байт modR/M может ссылаться только на память.

O - Команда не содержит байта modR/M; относительный адрес операнда кодируется как слово или двойное слово (в зависимости от атрибута размера адреса) непосредственно в команде. Регистр базы, регистр индекса, коэффициент масштабирования не используется.

R - Поле mod байта modR/M может указывать только на регистр общего назначения.

S - Поле reg байта modR/M указывает сегментный регистр.

T - Поле reg байта modR/M указывает регистр.

X - Адресация памяти при помощи пары регистров DS:SI; например, MOVS, COMPS, OUTS.

Y - Адресация памяти при помощи пары регистров DS:DI; например, MOVS, COMPS, INS,.

Кодирование типов операндов (условные обозначения в таблице).

Условные обозначения в таблице:

а

Кодирование типов операндов (условные обозначения в таблице).

Условные обозначения в таблице:

а

b - Байт (независимо от атрибута размера операнда).

c - Байт или слово, в зависимости от атрибута размера операнда.

d - Двойное слово (независимо от атрибута размера операнда).

p - 32- или 48-разрядный указатель, в зависимости от атрибута размера операнда.

s - 6-разрядный псевдо-дескриптор.

v - Слово или двойное слово, в зависимости от атрибута размера операнда.

w - Cлово (независимо от атрибута размера операнда).

Коды регистров в таблице.

Когда в качестве операнда используется закодированный в команде регистр, он определяется по имени, например AX, CL или ESI.

Имя регистра определяет его размер - 32, 16 или 8 бит. В случае, если размер регистра определяется атрибутом размера операнда, используется запись такого формата eXX.

Например, запись eAX означает, что при атрибуте размера операнда равном 16,

используется регистр AX, а при атрибуте размера операнда равном 32 - регистр EAX.

Для нахождения строки, содержащей нужную операцию необходимо использовать значение старших четырех битов кода операции, а для нахождения столбца - значение младших четырех битов. Если код операции равен 0FH, необходимо обратиться к таблице двухбайтовых кодов операций и использовать значение второго байта кода операции для нахождения соответствующей строки и столбца.

Дополнительные таблицы кодов операций машинных команд.

Существует ряд дополнительных таблиц расширения

Дополнительные таблицы кодов операций машинных команд.

Существует ряд дополнительных таблиц расширения

1. Команды математического сопроцессора.

Эти наборы команд доступны через инструкцию 11011ххх (или D8x) первого байта (см. основную таблицу кодов), которая называется ESC-командой.

Наборы команд математического сопроцессора содержат 8 дополнительных таблиц команд, т.е. позволяют реализовать до 1280 дополнительных машинных команд, для различных модификаций математического сопроцессора архитектуры х86.

В связи с тем, что в настоящее время реализовано только 63 машинные команды для 84-х команд ассемблера, этот набор команд обладает большой избыточностью

2. Команды дополнительных модулей SSE-расширений архитектуры х86.

Эти наборы команд сведены в отдельную таблицу команд, доступную через первый байт КОП 00001111 (или 0f), либо располагаются в таблицах команд математического сопроцессора и доступны через инструкцию 11011ххх (или D8x) первого байта (см. основную таблицу кодов).

3. Команды дополнительных модулей 3DNow!-расширений для процессоров AMD Athlon, совмещенных с архитектурой х86.

Данные наборы имеют в своем составе 3 байта КОП. Причем первые два имеют конструкцию 00001111 00001111 (или 0f 0f), т.е. расположены в собственной таблице, спроектированной фирмой AMD для своих процессоров дополнительно к х86.

4. В настоящее время разработчиками архитектур процессоров ведется работа по расширению наборов команд Ассемблера и соответствующих машинных команд для мультипроцессорных систем.

Примеры формирования кода машинной команды

Команда MOV пересылки данных:

Из регистра

Примеры формирования кода машинной команды

Команда MOV пересылки данных:

Из регистра

Из регистра 2 в регистр 1 8В

Регистр – память 88

Константа – регистр С6

Константа – память С6

Сумматор – память А3

Команда SAHF загрузка регистра флагов flags в регистр AH

9Е

Команда CBW/CWDE Преобразование байта в слово/слова в двойное слово

CBW 98

CWDE 99

11. Системы команд ассемблера для архитектуры ЦПУ х86.

Классификация базовых (целочисленных) команд

11. Системы команд ассемблера для архитектуры ЦПУ х86.

Классификация базовых (целочисленных) команд

Математический сопроцессор.

Схема центрального процессора содержит обычный сумматор, предназначен-ный

Математический сопроцессор.

Схема центрального процессора содержит обычный сумматор, предназначен-ный

При выполнении операций с вещественными числами на процессор поступа-

ют соответствующие команды (начинающиеся с символа «F») с кодом операции,

начинающимся с инструкции 11011.

Все обрабатываемые операнды передаются в буферные регистры математи-

ческого сопроцессора, представляющего собой цифровой автомат с жесткой

схемной логикой. Здесь над ними производятся все необходимые для вычислений

математические операции. Результат возвращается в аккумулятор центрального

процессора.

Если математический сопроцессор отсутствует, то исполнение математичес-

ких операций над вещественными числами осуществляется соответствующими

программами BIOS, эмулирующими работу математического сопроцессора.

Однако, при этом, вещественное число преобразуется в совокупность

простых чисел (мантиссу и степень), с которыми работает АЛУ центрального

процессора, затем производится обратное преобразование.

Программное эмулирование процесса обработки вещественных чисел

математическим сопроцессором приводит к существенному замедлению (на 2

порядка) процесса вычислений.

Принципиальная схема математического сопроцессора.

80-разрядный стековый регистр st(0)

Регистр 1

Регистр 2

Регистр

Принципиальная схема математического сопроцессора.

80-разрядный стековый регистр st(0)

Регистр 1

Регистр 2

Регистр

Внутренняя шина процессора

Матричные схемы умножения и деления чисел с плавающей точкой

WR1

WR2

Error

S

80-разрядный стековый регистр st(1)

80-разрядный стековый регистр st(2)

80-разрядный стековый регистр st(3)

80-разрядный стековый регистр st(4)

80-разрядный стековый регистр st(5)

80-разрядный стековый регистр st(6)

80-разрядный стековый регистр st(7)

Классификация команд ассемблера для математического сопроцессора.

Команды ассемблера для сопроцессора

Всего 85 команд

Передачи

Классификация команд ассемблера для математического сопроцессора.

Команды ассемблера для сопроцессора

Всего 85 команд

Передачи

Сравнения данных

Арифметические

Трансцендентные

Управления

Вещественные данных

Целочисленные данных

Десятичные данных

Загрузка констант

Обмен данными

Условная пересылка

Вещественные данных

Целочисленные данных

Анализ st(0)

С нулем

Условное сравнение

Вещественные данных

Целочисленные данных

Вспомогательные арифметические команды

Сложение

Вычитание

Умножение

Деление

Сложение

Вычитание

Умножение

Деление

Вычисление тригонометри-ческих функций

Синус

Косинус

Тангенс

Арктангенс

Вычисление логарифмов и степеней

Инициализация сопроцессора

Работа со средой

Работа со стеком

Переключение режимов

fnop

fwait

Классификация команд ассемблера для ММХ-расширения процессора.

Команды ассемблера для ММХ-расширения

Всего 41 команда

Пересылки

Классификация команд ассемблера для ММХ-расширения процессора.

Команды ассемблера для ММХ-расширения

Всего 41 команда

Пересылки

Сравнения данных

Арифметические

Упаковки (сжатия)

Инициализации

Прямая пересылка

Пересылка с расширением

Сложение

Вычитание

Умножение

Сдвигов

Логические

Дополнительные ММХ-команды (SSE)

Вычисления

Перемещения

Извлечения знака

Сложение

Вычитание

Умножение

Сложение

Вычитание

Умножение

Классификация команд ассемблера для ХММ-расширения SSE-2.

Команды ассемблера для ХММ-расширения

Всего 149 команд

Пересылки

Классификация команд ассемблера для ХММ-расширения SSE-2.

Команды ассемблера для ХММ-расширения

Всего 149 команд

Пересылки

Сравнения данных

Арифметические

Преобразования данных

Логические

Параллельные

Скалярные

Квадратный корень

max / min

Сложение

Вычитание

Умножение

Деление

Блок дополнитель-ных команд Integer MMX

Квадратный корень

max / min

Сложение

Вычитание

Умножение

Деление

Перерас-пределения

Управления состоянием

Управления кэширова-нием

Скалярные

Параллельные

С установкой eflags

Скалярные

Параллельные

И

ИЛИ

И-НЕ

Искл. ИЛИ

Классификация команд ассемблера для 3DNow!-расширения для процессоров AMD Athlon.

Команды ассемблера для

Классификация команд ассемблера для 3DNow!-расширения для процессоров AMD Athlon.

Команды ассемблера для

Всего 26 команд

Пересылки упакованных данных

Сравнения и округления упакованных данных

Арифметические действия с упакованными данными с плавающей точкой

Упаковки (сжатия) данных 4-х операндов

Прямая пересылка

Пересылка с расширением

Сложение

Вычитание

Умножение

Выборка, сдвиг и переста-новка упакованных данных

Логические действия с упакованными данными

Квадратный корень

max / min

Деление

Основные инструменты для работы с низкоуровневым программным кодом.

1. OllyDbg (www.ollydbg.de)

Основные инструменты для работы с низкоуровневым программным кодом.

1. OllyDbg (www.ollydbg.de)

2. IDA Pro (www.hex-rays.com/idapro) – интерактивный дизассемблер и отладчик приложений Работает через функции MS Debugging API в NT или библиотеку ptrace в UNIX.

3. Syser Kernel Debugger (www.sysersoft.com) – отладчик ядра ОС и процессов (не работает в Windows 7 и MS Server 2008).

4. SoftICE (в настоящее время не поддерживается) – отладчик для Windows на уровне ядра.

5. Fasm (www.flatassembler.net) - свободно распространяемый многопроходной кросс-ассемблер. Обладает небольшими размерами и очень высокой скоростью компиляции. Поддерживает как объектные форматы, так и некоторые форматы исполняемых файлов.

Помимо базового набора инструкций процессора и сопроцессора Fasm v.1.68 поддерживает наборы инструкций MMX, SSE, SSE2, SSE3, SSSE3, SSE4.1, SSE4.2, SSE4a и 3DNow!, а также EM64T и AMD64 (включая AMD SVM и Intel SMX).

6. WinHex (www.x-ways.net/winhex) - Один из лучших шестнадцатеричных редакторов машинного кода. Позволяет редактировать файлы размером более 4 Гб с жестких дисков, внешних накопителей, флешек. Имеет собственный механизм работы с файловыми системами FAT, NTFS, Ext2/3, ReiserFS, Reiser4, UFS, CDFS, UDF, а также RAID-массивами и динамическими дисками (независимо от операционной системы). В программу также встроены средства для восстановления данных, безопасного удаления файлов, инструмент для редактирования содержимого оперативной памяти, алгоритмы шифрования и т.д.

Презентация "Рубенс" - скачать презентации по МХК

Презентация "Рубенс" - скачать презентации по МХК ставропольская государственная медицинская академия Герпетический энцефалит у детей

ставропольская государственная медицинская академия Герпетический энцефалит у детей  Правоохранительные органы

Правоохранительные органы Etipower. Воздушные автоматические выключатели

Etipower. Воздушные автоматические выключатели Водно-минеральный обмен

Водно-минеральный обмен Критика и самокритика

Критика и самокритика Изменения в пенсионной системе Украины

Изменения в пенсионной системе Украины Легенды и мифы древних греков - презентация для начальной школы

Легенды и мифы древних греков - презентация для начальной школы лекция_Семья-структура, функции, динамика

лекция_Семья-структура, функции, динамика ФЗ «Об основах социального обслуживания граждан в Российской Федерации»

ФЗ «Об основах социального обслуживания граждан в Российской Федерации» Честь, достоинство и деловая репутация: философия защиты в новом информационном пространстве

Честь, достоинство и деловая репутация: философия защиты в новом информационном пространстве Колористический образ интерьера

Колористический образ интерьера Презентация Политические и правовые идеи средневековых ересей

Презентация Политические и правовые идеи средневековых ересей Сущность бренд-менеджмент

Сущность бренд-менеджмент Массивы в C#

Массивы в C# Бенито Муссолини

Бенито Муссолини  Электрические аппараты электровозов. Классификация

Электрические аппараты электровозов. Классификация Удивительный мир функций. Рано или поздно всякая правильная математическая идея находит применение в том или и

Удивительный мир функций. Рано или поздно всякая правильная математическая идея находит применение в том или и Лекция 1

Лекция 1 Образовательный курс «МАРКЕТИНГОВЫЕ СЕРВИСЫ» Киев, Украина, 2014 год

Образовательный курс «МАРКЕТИНГОВЫЕ СЕРВИСЫ» Киев, Украина, 2014 год  Формально об инъекциях. Модель инъекции. Критерий защищённости от атак инъекций

Формально об инъекциях. Модель инъекции. Критерий защищённости от атак инъекций Формы памяти Подготовила: Холбаева Вероника, студентка 3 курса, 33 группы ФСПиП

Формы памяти Подготовила: Холбаева Вероника, студентка 3 курса, 33 группы ФСПиП  Древнейшие люди

Древнейшие люди Патологические изменения кожи Выполнила : Студентка гр. 224 Крывенькая Е.С.

Патологические изменения кожи Выполнила : Студентка гр. 224 Крывенькая Е.С. Синдром недостаточности кровообращения

Синдром недостаточности кровообращения  Значение Сибирской тайги Учитель начальных классов МОУ «ЛИЦЕЙ» г. Лесосибирска Желанникова Е.И.

Значение Сибирской тайги Учитель начальных классов МОУ «ЛИЦЕЙ» г. Лесосибирска Желанникова Е.И. Диагностика и ремонт подвески рулевого управления и тормозная система легкового автомобиля

Диагностика и ремонт подвески рулевого управления и тормозная система легкового автомобиля Общая физиология ЦНС

Общая физиология ЦНС