Содержание

- 2. Chapter 7 Interconnect Delay 7.1 Elmore Delay 7.2 High-order model and moment matching 7.3 Stage delay

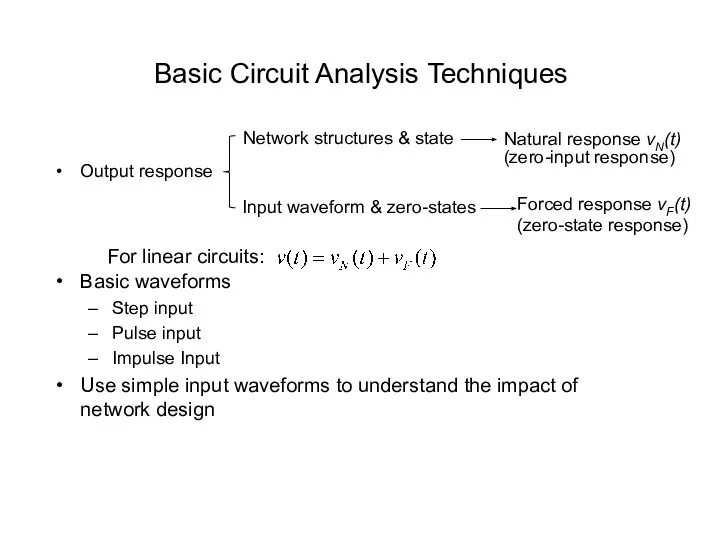

- 3. Basic Circuit Analysis Techniques Output response Basic waveforms Step input Pulse input Impulse Input Use simple

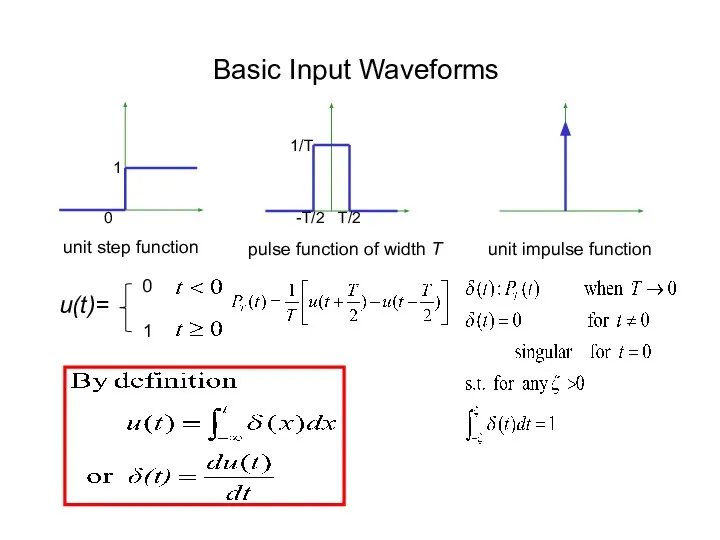

- 4. unit step function u(t)= 0 1 1 pulse function of width T 0 1/T -T/2 T/2

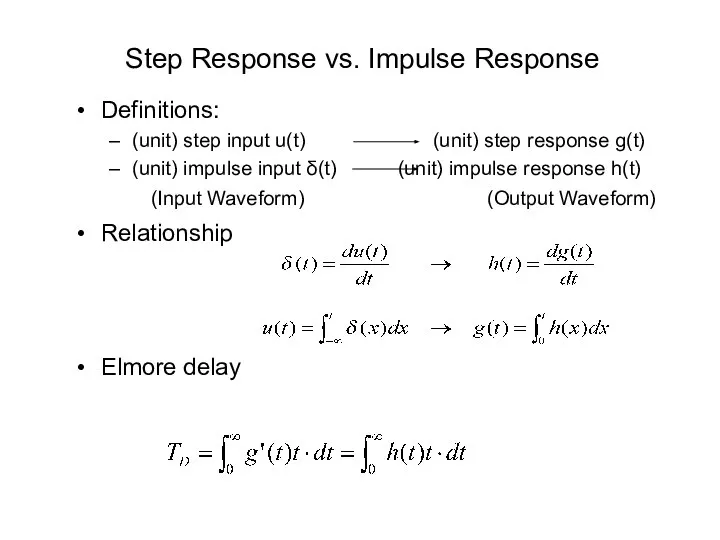

- 5. Definitions: (unit) step input u(t) (unit) step response g(t) (unit) impulse input δ(t) (unit) impulse response

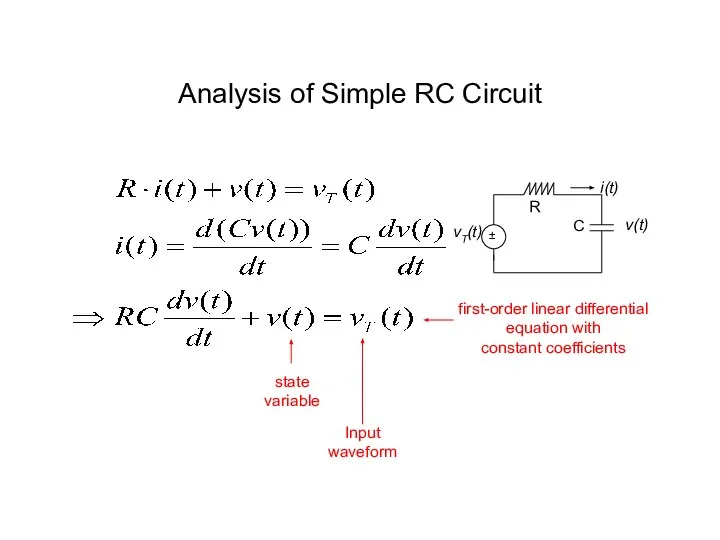

- 6. Analysis of Simple RC Circuit first-order linear differential equation with constant coefficients state variable Input waveform

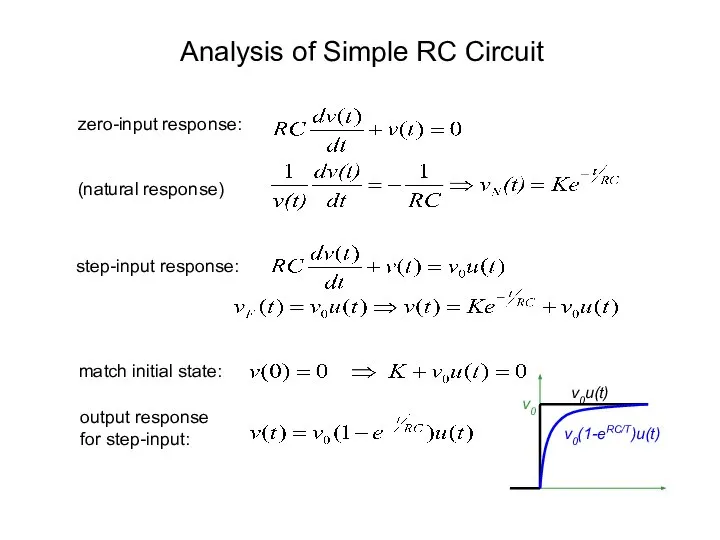

- 7. Analysis of Simple RC Circuit zero-input response: (natural response) step-input response: match initial state: output response

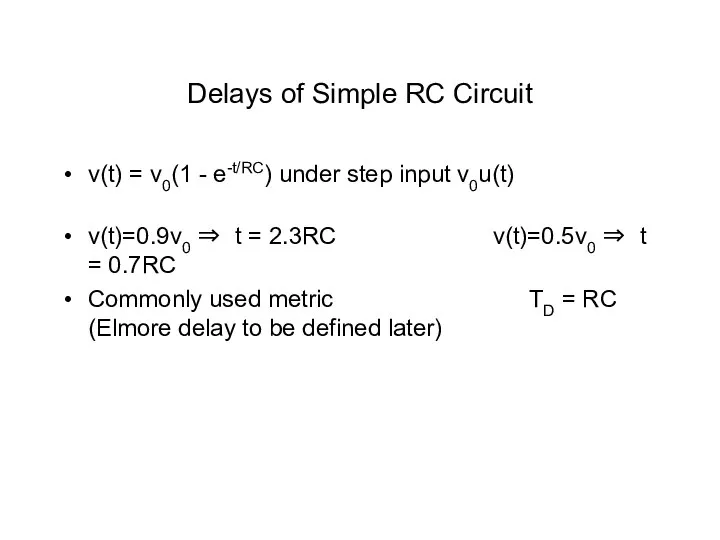

- 8. Delays of Simple RC Circuit v(t) = v0(1 - e-t/RC) under step input v0u(t) v(t)=0.9v0 ⇒

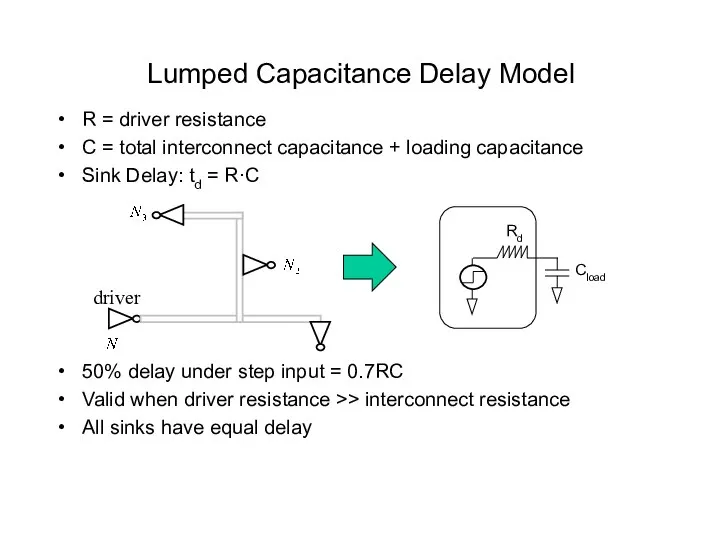

- 9. Lumped Capacitance Delay Model R = driver resistance C = total interconnect capacitance + loading capacitance

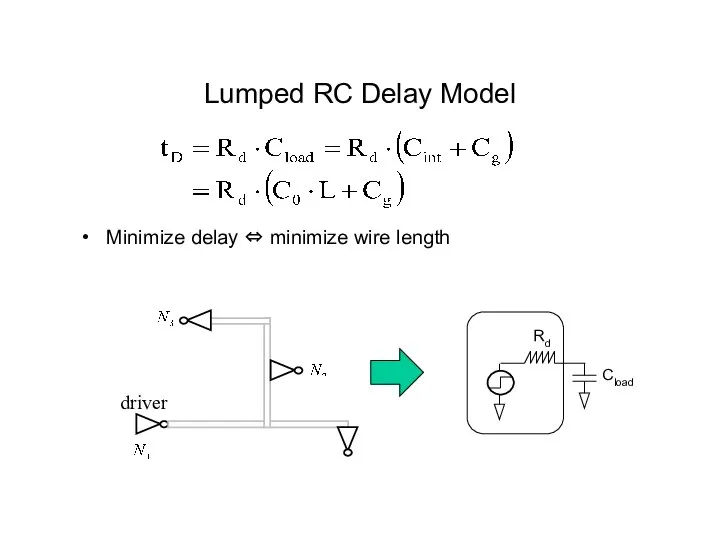

- 10. driver Lumped RC Delay Model Minimize delay ⇔ minimize wire length Rd Cload

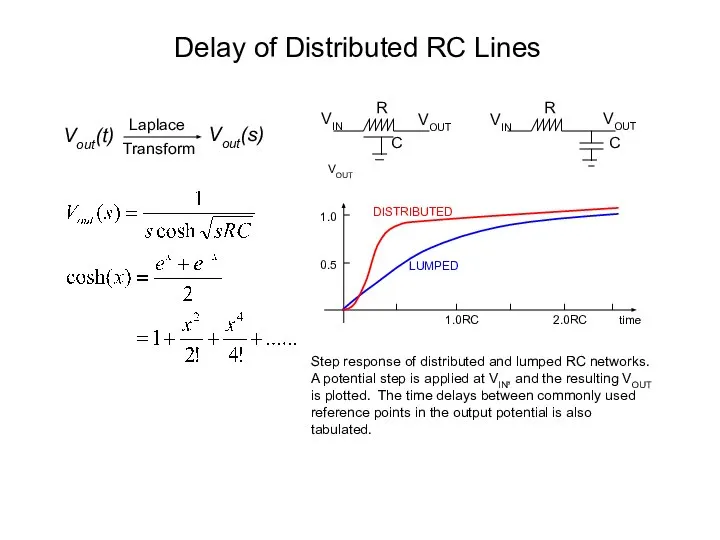

- 11. Delay of Distributed RC Lines Vout(t) Vout(s) Laplace Transform R VIN VOUT C VOUT VIN R

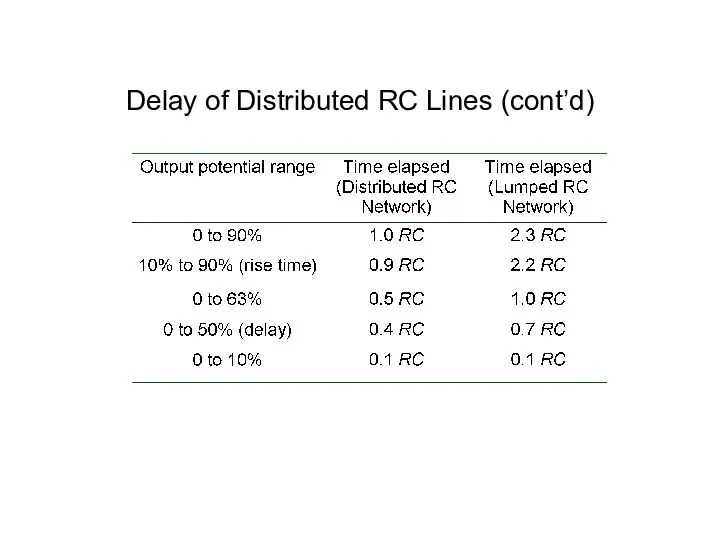

- 12. Delay of Distributed RC Lines (cont’d)

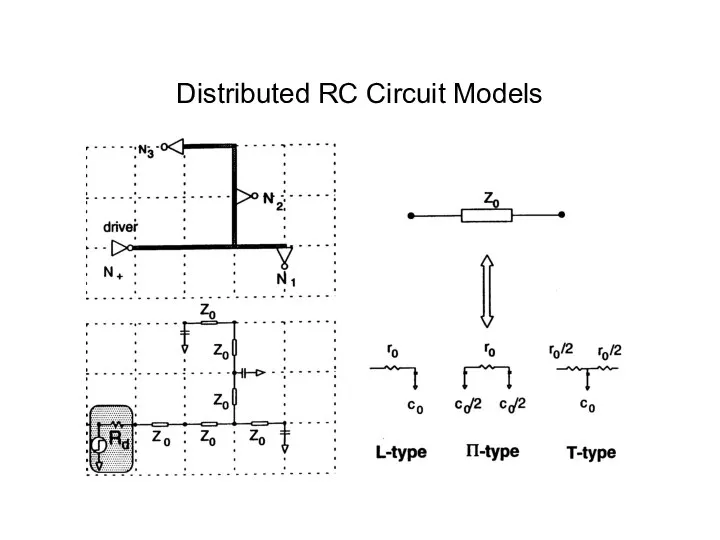

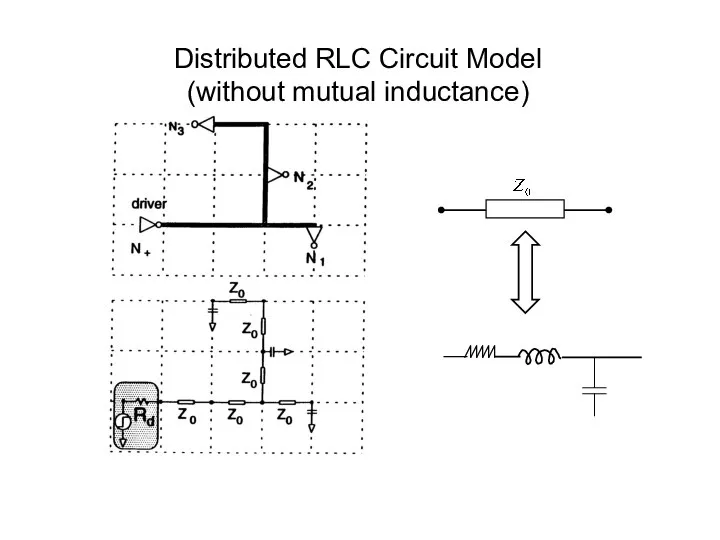

- 13. Distributed Interconnect Models Distributed RC circuit model L,T or Π circuits Distributed RCL circuit model Tree

- 14. Distributed RC Circuit Models

- 15. Distributed RLC Circuit Model (without mutual inductance)

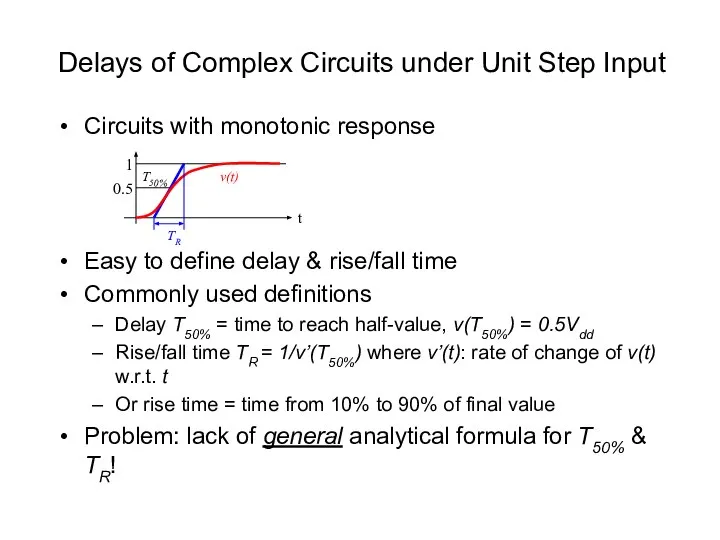

- 16. Delays of Complex Circuits under Unit Step Input Circuits with monotonic response Easy to define delay

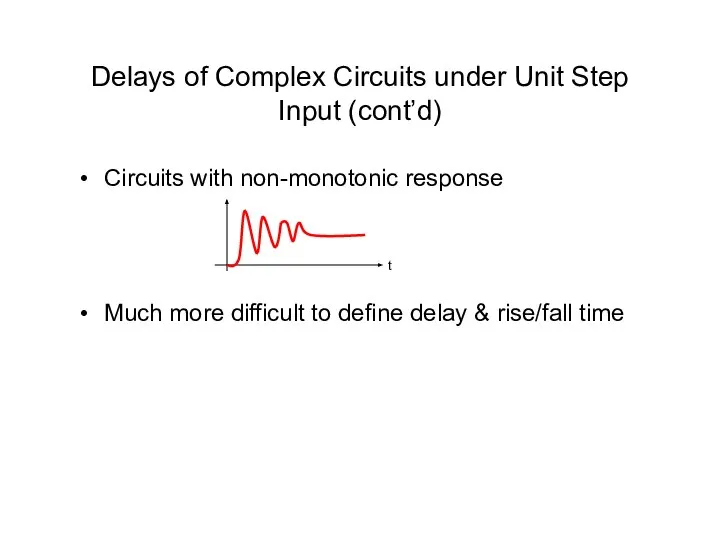

- 17. Delays of Complex Circuits under Unit Step Input (cont’d) Circuits with non-monotonic response Much more difficult

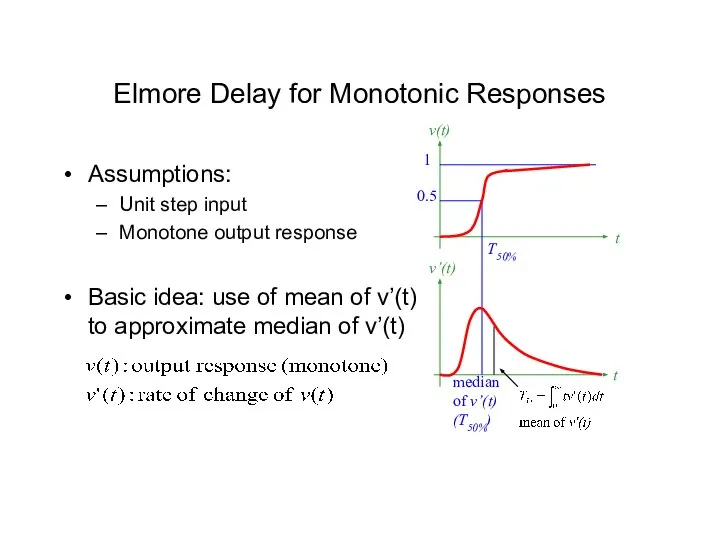

- 18. 0.5 1 T50% v(t) t t v’(t) median of v’(t) (T50%) Elmore Delay for Monotonic Responses

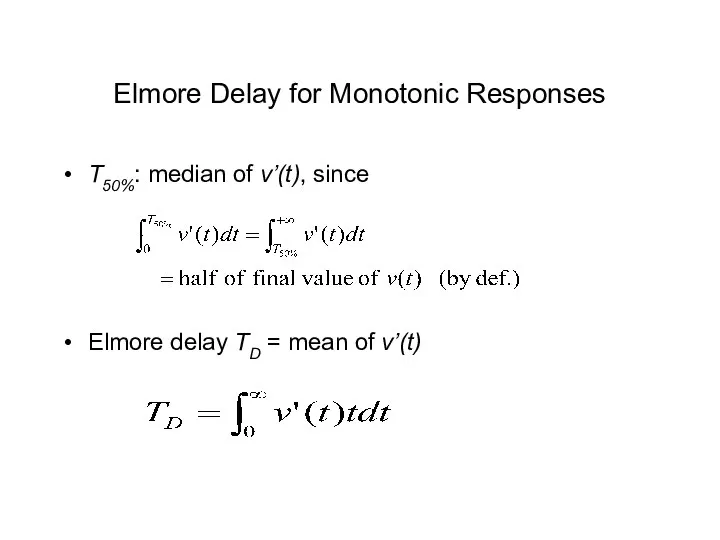

- 19. T50%: median of v’(t), since Elmore delay TD = mean of v’(t) Elmore Delay for Monotonic

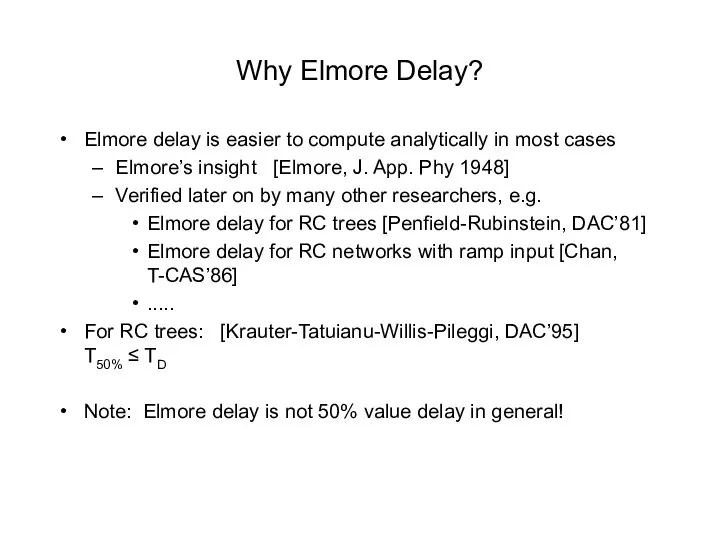

- 20. Why Elmore Delay? Elmore delay is easier to compute analytically in most cases Elmore’s insight [Elmore,

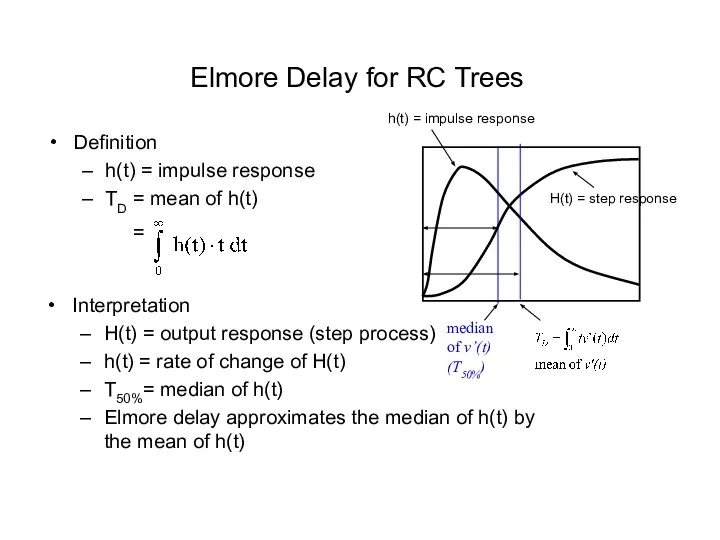

- 21. Elmore Delay for RC Trees Definition h(t) = impulse response TD = mean of h(t) =

- 22. Elmore Delay of a RC Tree [Rubinstein-Penfield-Horowitz, T-CAD’83] Lemma: Proof: Apply impulse func. at t=0: imin

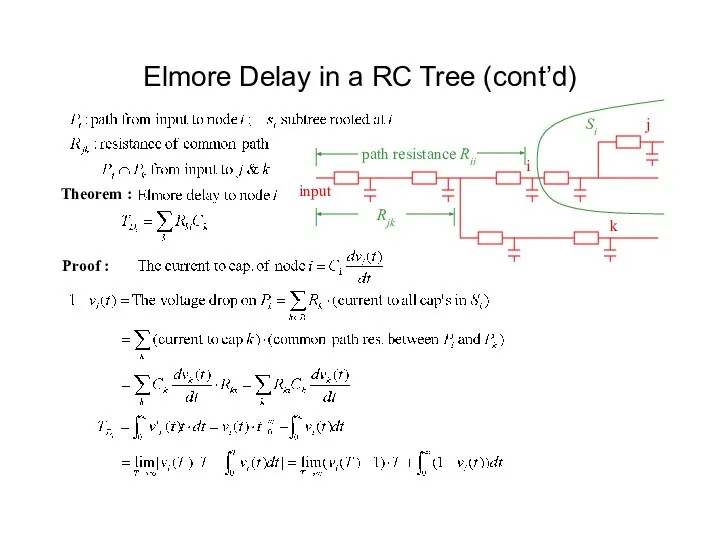

- 23. Elmore Delay in a RC Tree (cont’d) input i k j Si path resistance Rii Rjk

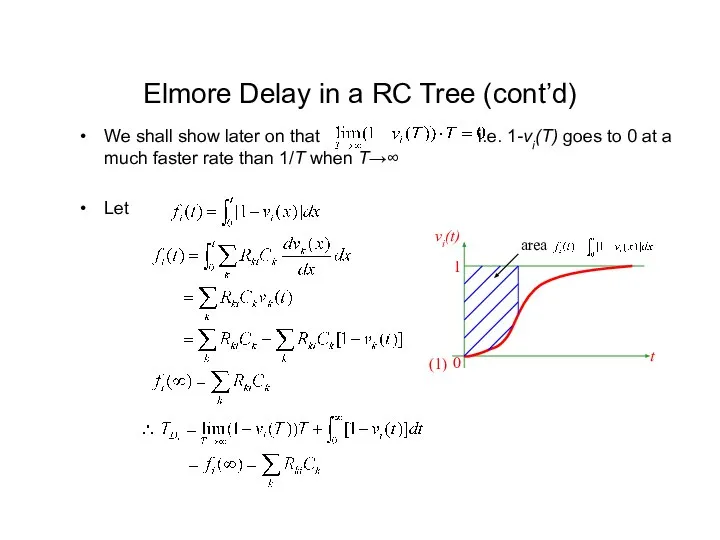

- 24. Elmore Delay in a RC Tree (cont’d) We shall show later on that i.e. 1-vi(T) goes

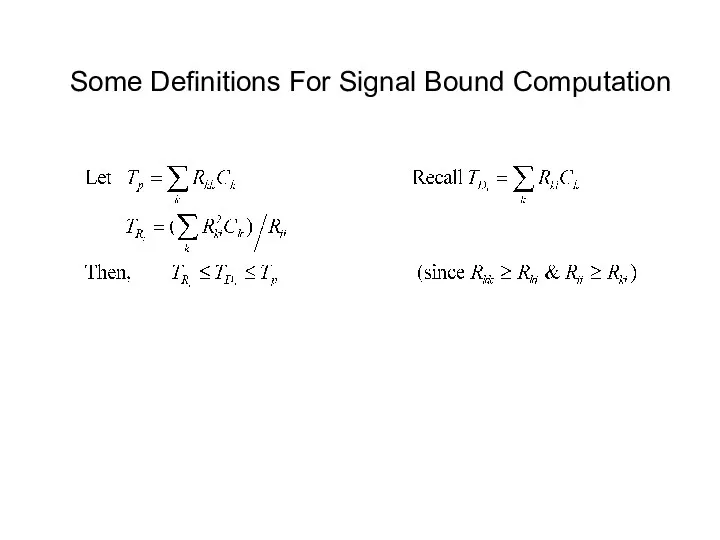

- 25. Some Definitions For Signal Bound Computation

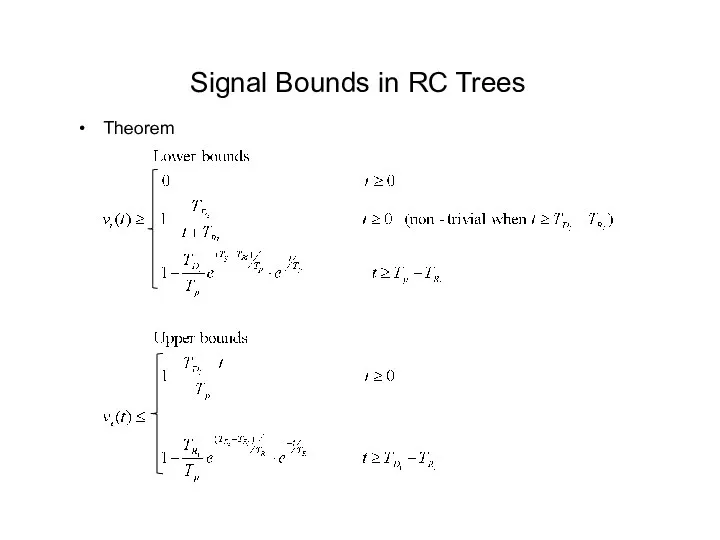

- 26. Signal Bounds in RC Trees Theorem

- 27. Delay Bounds in RC Trees

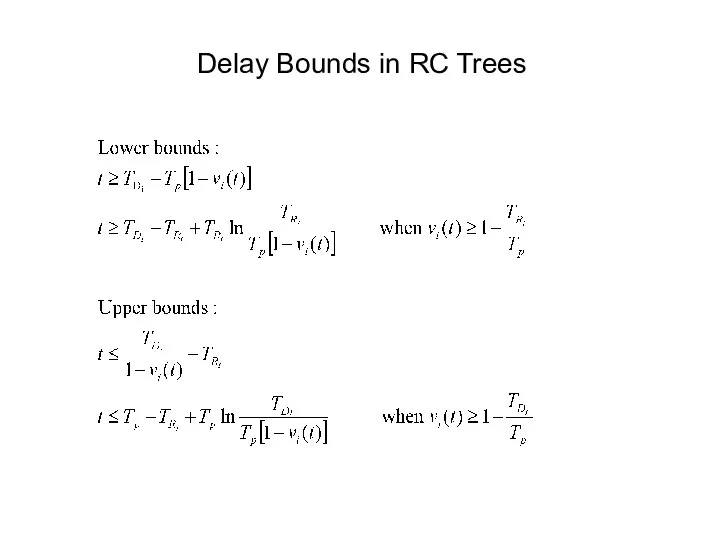

- 28. Computation of Elmore Delay & Delay Bounds in RC Trees Let C(Tk) be total capacitance of

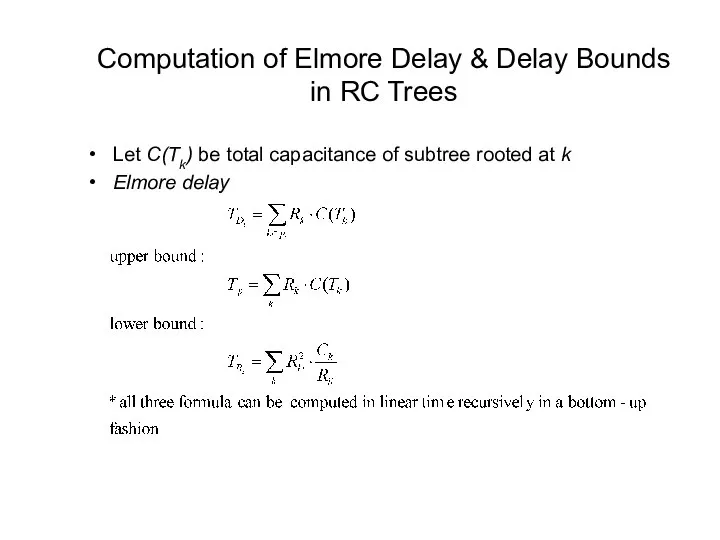

- 29. Comments on Elmore Delay Model Advantages Simple closed-form expression Useful for interconnect optimization Upper bound of

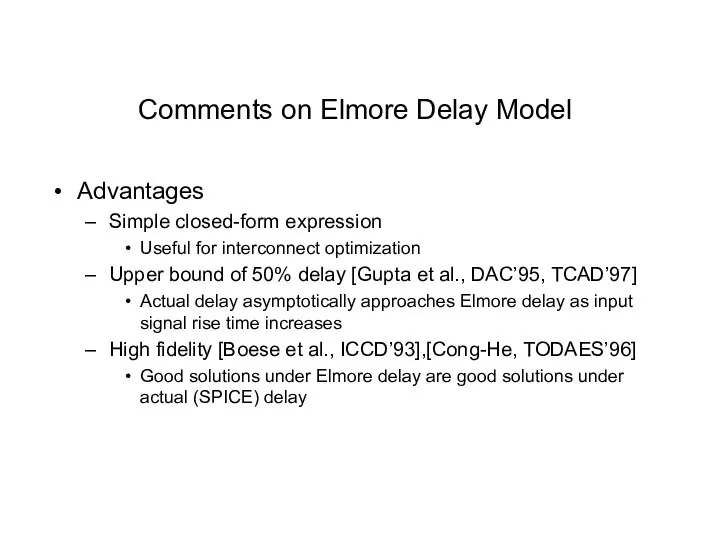

- 30. Comments on Elmore Delay Model Disadvantages Low accuracy, especially poor for slope computation Inherently cannot handle

- 31. Chapter 7.2 Higher-order Delay Model

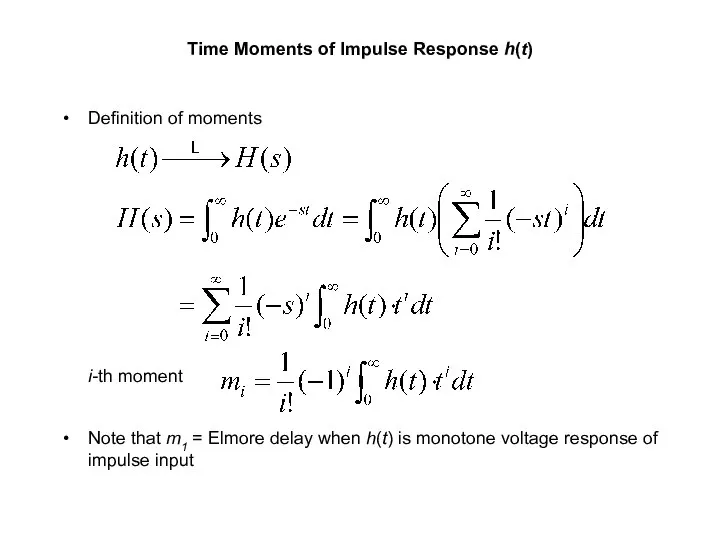

- 32. Time Moments of Impulse Response h(t) Definition of moments i-th moment Note that m1 = Elmore

- 33. Pade Approximation H(s) can be modeled by Pade approximation of type (p/q): where q Or modeled

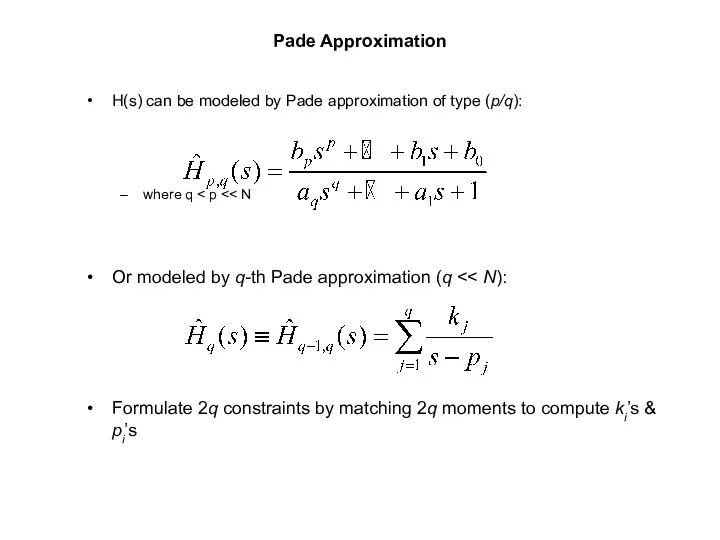

- 34. General Moment Matching Technique Basic idea: match the moments m-(2q-r), …, m-1, m0, m1, …, mr-1

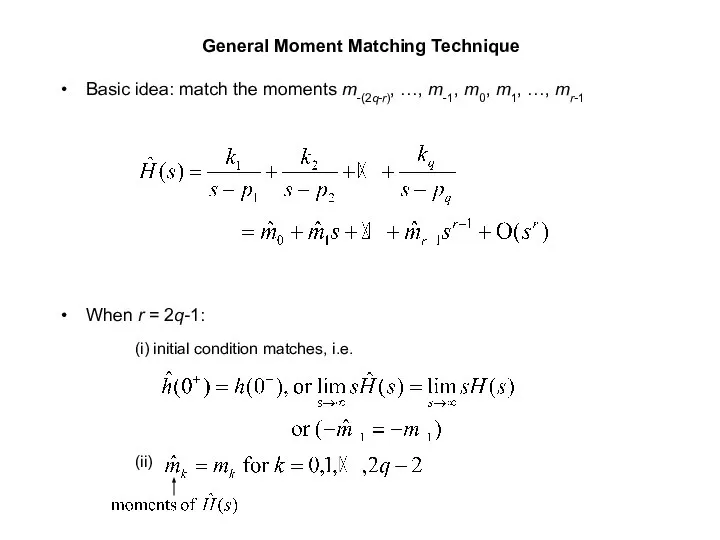

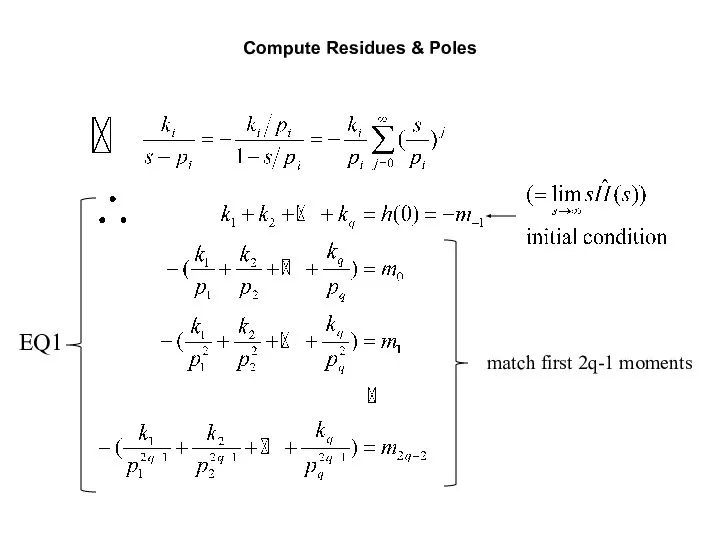

- 35. Compute Residues & Poles match first 2q-1 moments EQ1

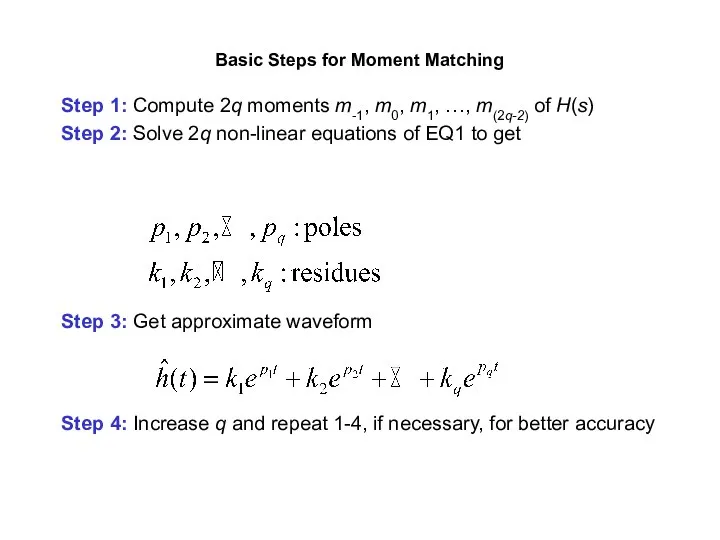

- 36. Basic Steps for Moment Matching Step 1: Compute 2q moments m-1, m0, m1, …, m(2q-2) of

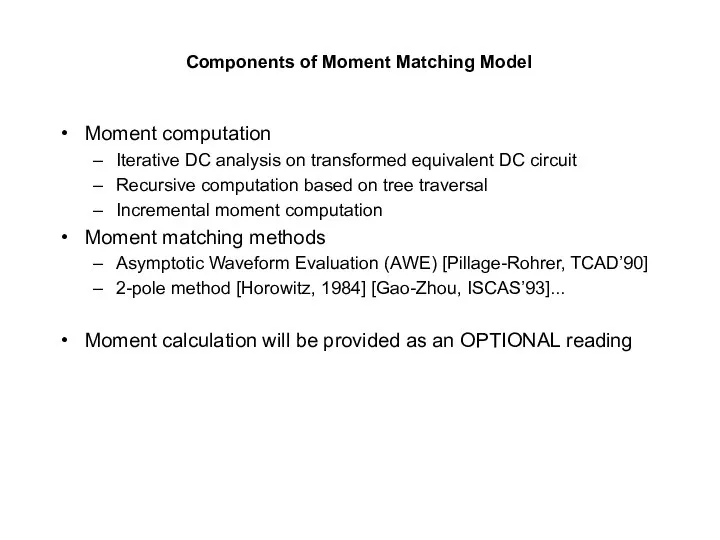

- 37. Components of Moment Matching Model Moment computation Iterative DC analysis on transformed equivalent DC circuit Recursive

- 38. Chapter 7 Interconnect Delay 7.1 Elmore Delay 7.2 High-order model and moment matching 7.3 Stage delay

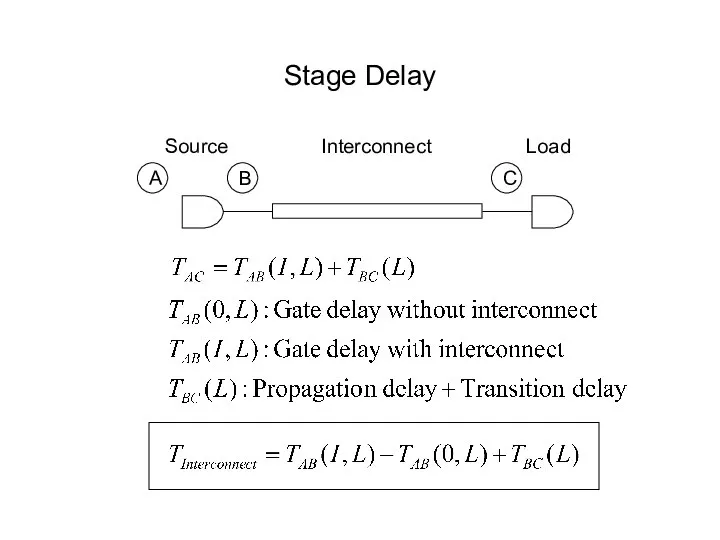

- 39. Stage Delay A B C Source Interconnect Load

- 40. Modeling of Capacitive Load First-order approximation: the driver sees the total capacitance of wires and sinks

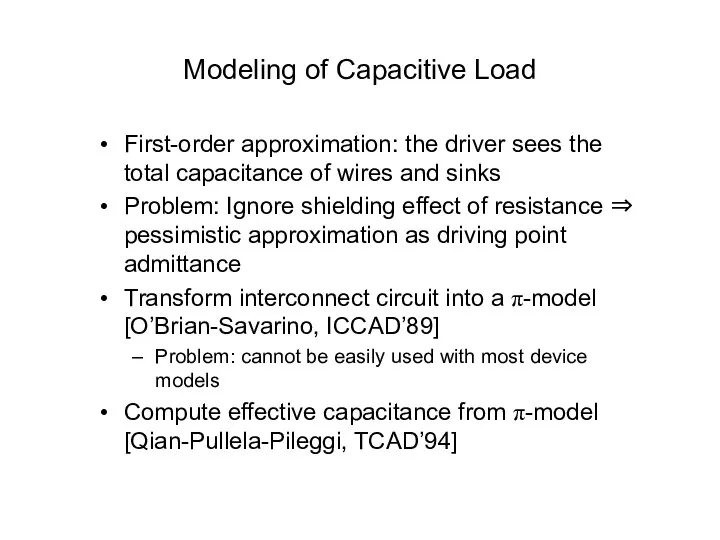

- 41. Π-Model [O’Brian-Savarino, ICCAD’89] Moment matching again! Consider the first three moments of driving point admittance (moments

- 42. Driving-Point Admittance Approximations Driving-point admittance = Sum of voltage moment-weighted subtree capacitance Approximation of the driving

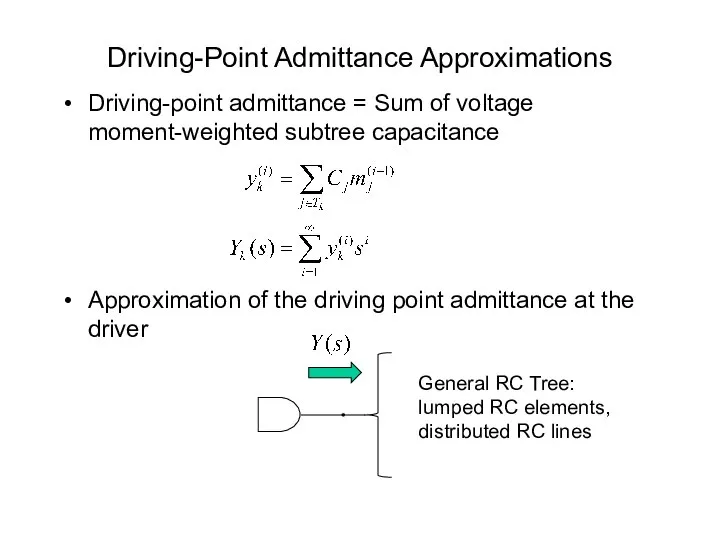

- 43. Driving-Point Admittance Approximations First order approximation: y(1) = sum of subtree capacitance Second order approximation: yk(2)

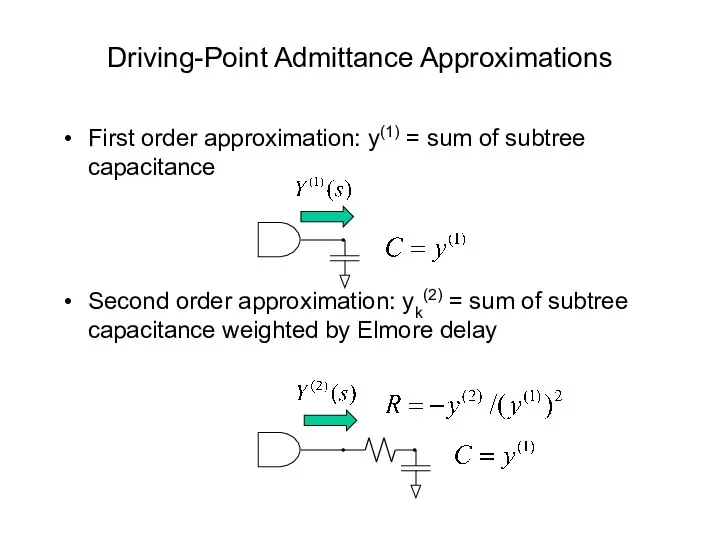

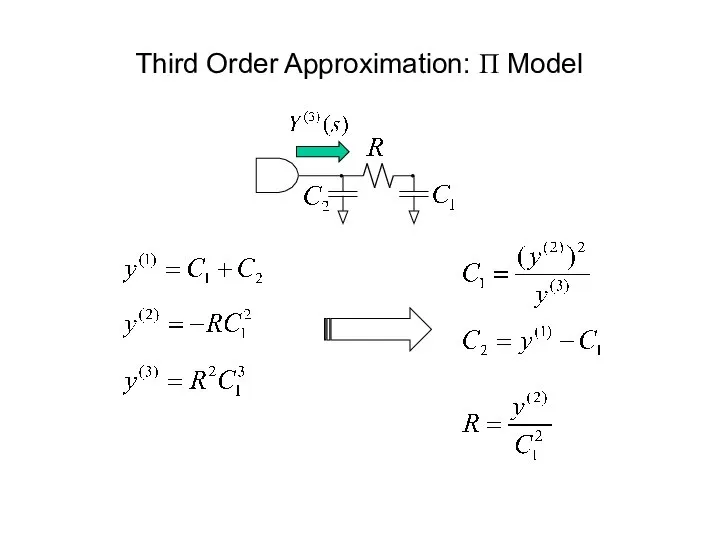

- 44. Third Order Approximation: Π Model

- 45. Current Moment Computation Similar to the voltage moment computation Iterative tree traversal: O(n) run-time, O(n) storage

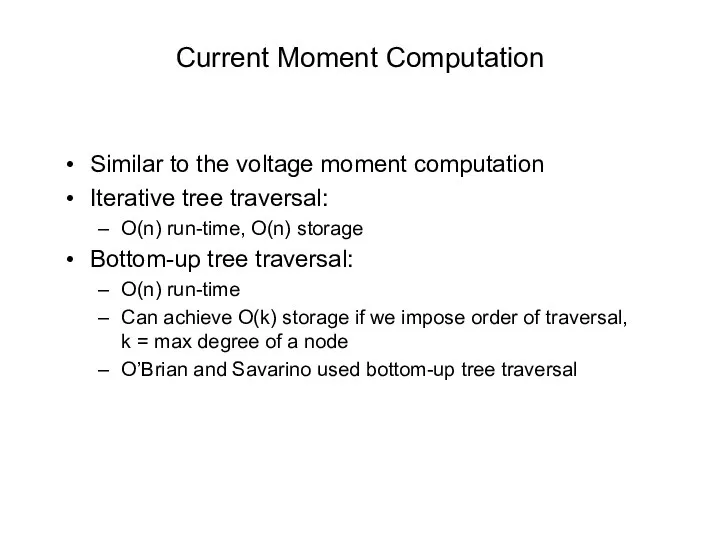

- 46. Bottom-Up Moment Computation Maintain transfer function Hv~w(s) for sink w in subtree Tv, and moment-weighted capacitance

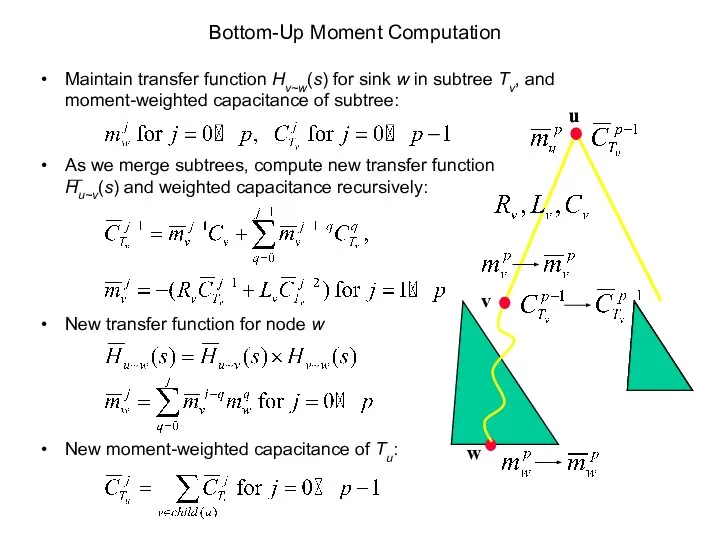

- 47. Current Moment Computation Rule #1

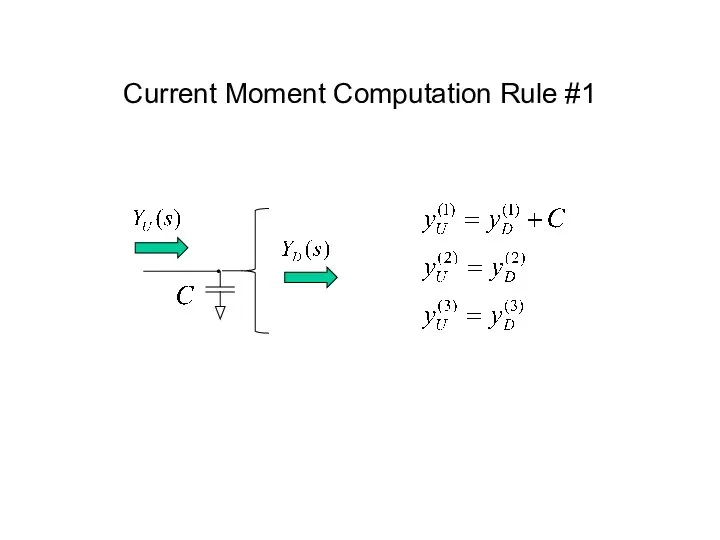

- 48. Current Moment Computation Rule #2

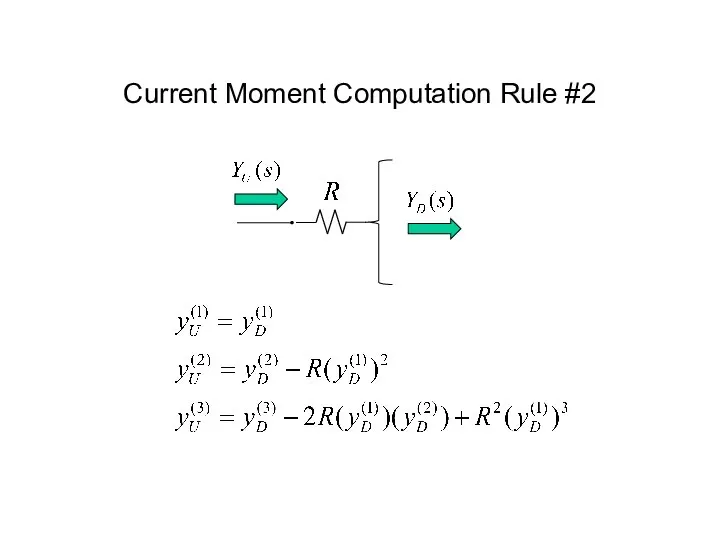

- 49. Current Moment Computation Rule #3

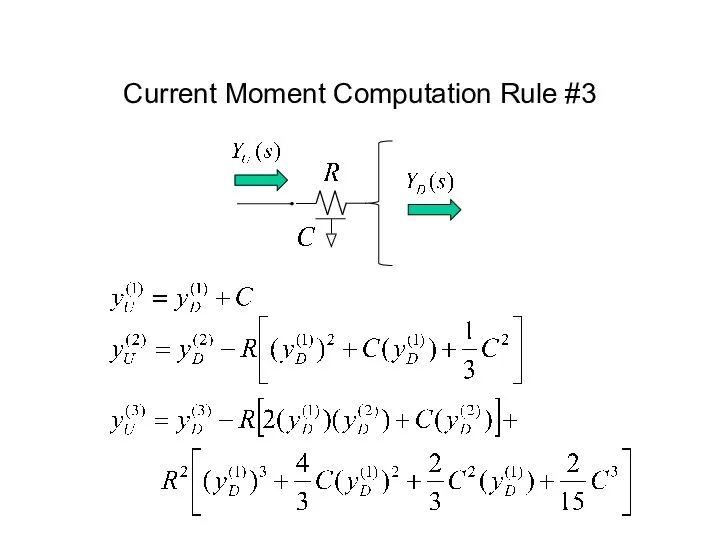

- 50. Current Moment Computation Rule #4 (Merging of Sub-trees) B Branches

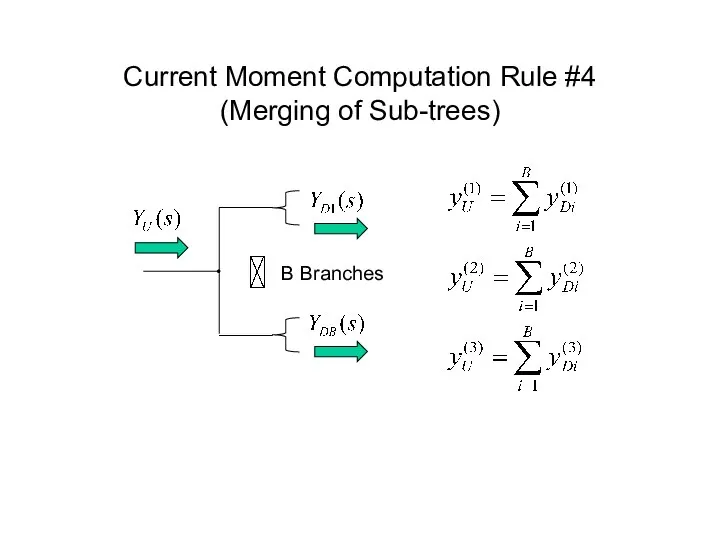

- 51. Example: Uniform Distributed RC Segment Purely capacitive Wide metal (distributive) Narrow metal (distributive) Narrow metal (lumped

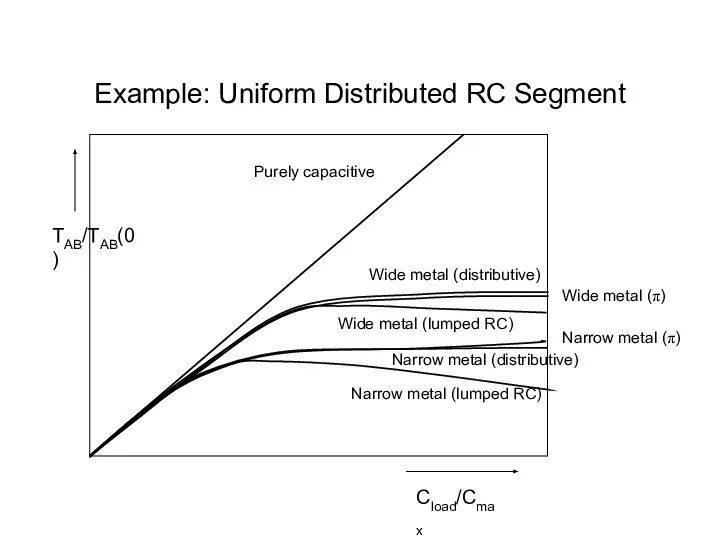

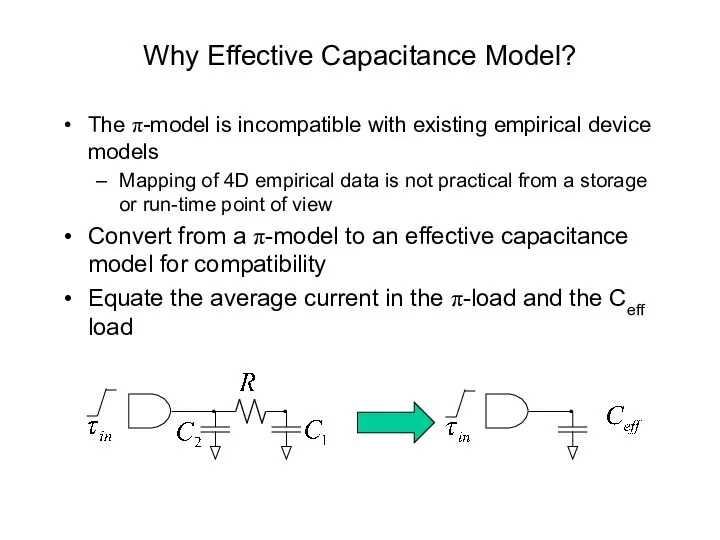

- 52. Why Effective Capacitance Model? The π-model is incompatible with existing empirical device models Mapping of 4D

- 53. Equating Average Currents tD = time taken to reach 50% point, not 50% point of input

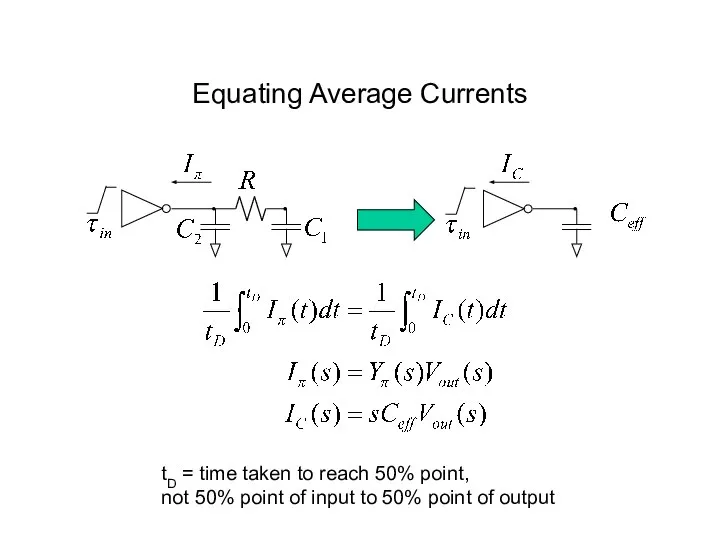

- 54. Waveform Approximation for Vout(t) Quadratic from initial voltage (Vi = VDD for falling waveform) to 20%

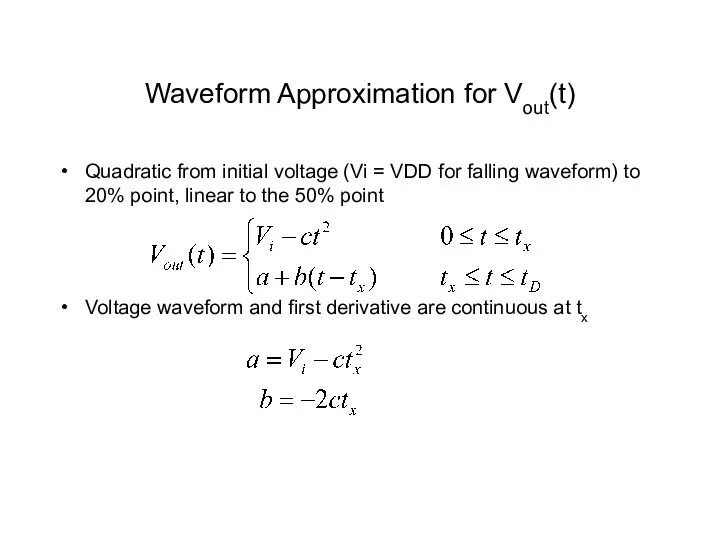

- 55. Average Currents in Capacitors Average current of C1 is not quite as simple: Current due to

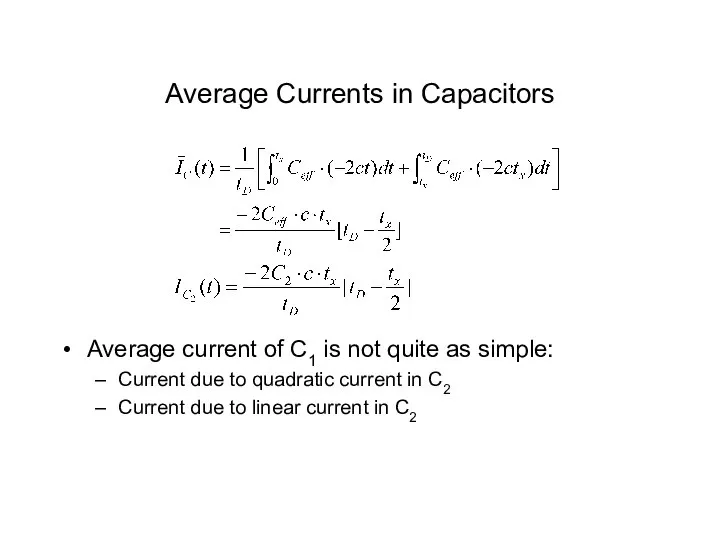

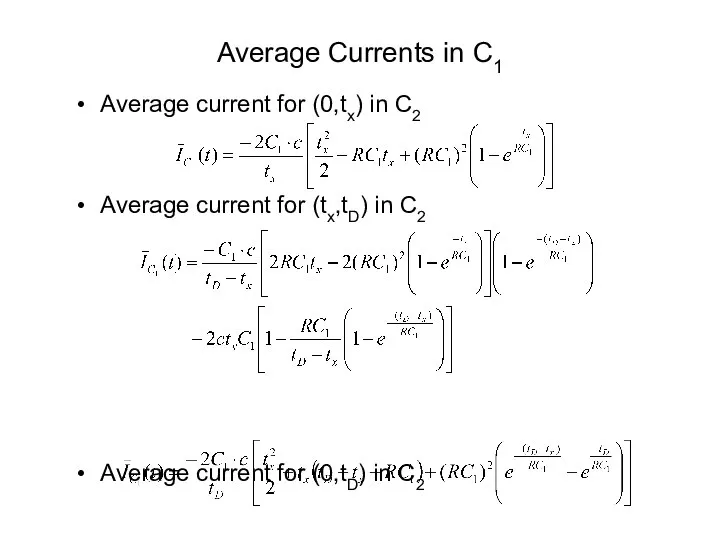

- 56. Average current for (0,tx) in C2 Average current for (tx,tD) in C2 Average current for (0,tD)

- 57. Computation of Effective Capacitance Equating average currents Problem: tD and tx are not known a priori

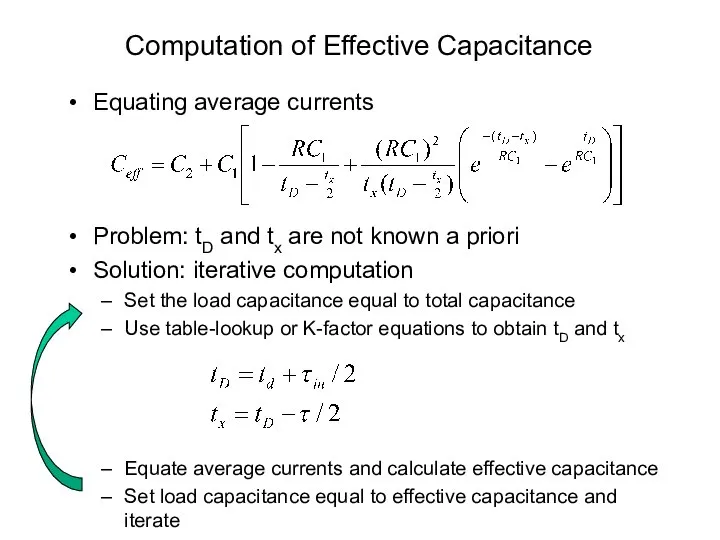

- 59. Скачать презентацию

![Elmore Delay of a RC Tree [Rubinstein-Penfield-Horowitz, T-CAD’83] Lemma: Proof: Apply](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1472894/slide-21.jpg)

![Π-Model [O’Brian-Savarino, ICCAD’89] Moment matching again! Consider the first three moments](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1472894/slide-40.jpg)

Тема занятия Ожоги и обморожения

Тема занятия Ожоги и обморожения Базовые компоненты компьютера

Базовые компоненты компьютера Ваши Воспитатели: Леонтьева Светлана Викторовна Бардаева Марина Юрьевна

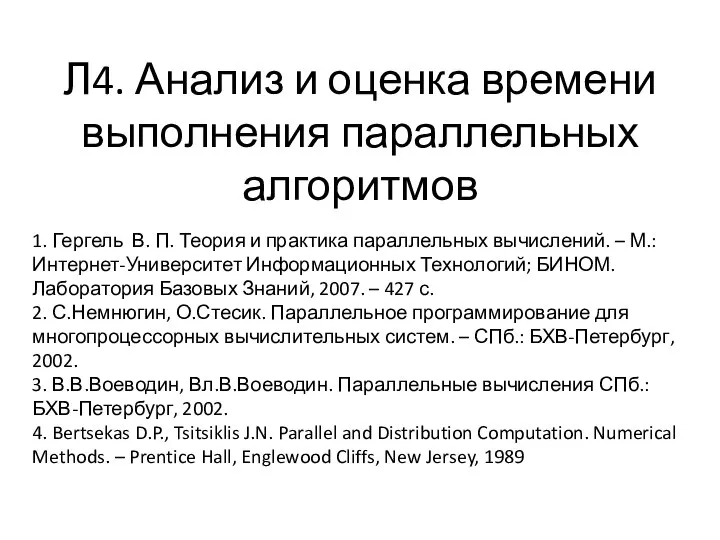

Ваши Воспитатели: Леонтьева Светлана Викторовна Бардаева Марина Юрьевна Анализ и оценка времени выполнения параллельных алгоритмов. (Лекция 4)

Анализ и оценка времени выполнения параллельных алгоритмов. (Лекция 4) Слово жизни. Об извилистых и труднопроходимых путях

Слово жизни. Об извилистых и труднопроходимых путях Создание аксессуаров из французской косынки

Создание аксессуаров из французской косынки Евангелическо-лютеранская Община Святого Георга г. Самары

Евангелическо-лютеранская Община Святого Георга г. Самары Консалтинговые услуги РФ Подготовил: Боймуродов Сухроб.

Консалтинговые услуги РФ Подготовил: Боймуродов Сухроб. Культура древней Индии

Культура древней Индии Храм Рождества Пресвятой Богородицы

Храм Рождества Пресвятой Богородицы Презентация на тему "патология систем" - скачать презентации по Медицине

Презентация на тему "патология систем" - скачать презентации по Медицине История создания и принцип работы радио

История создания и принцип работы радио Дорожки, мощение на приусадебных участках (фотографии)

Дорожки, мощение на приусадебных участках (фотографии) Синус, косинус, тангенс и котангенс. Алгебра и начала анализа, 10 класс

Синус, косинус, тангенс и котангенс. Алгебра и начала анализа, 10 класс Понятия и причины текучести персонала

Понятия и причины текучести персонала Введение в динамику механической системы

Введение в динамику механической системы Отечественные теории развивающего обучения

Отечественные теории развивающего обучения Презентация

Презентация Признаки образования рядов распределения

Признаки образования рядов распределения Классицизм_

Классицизм_ Задачи, приводящие к понятию производной.

Задачи, приводящие к понятию производной. Роль интеграции предметов гуманитарного цикла в повышении качества образования.

Роль интеграции предметов гуманитарного цикла в повышении качества образования. «Матрешка - самая известная русская игрушка». Папка-передвижка для родителей

«Матрешка - самая известная русская игрушка». Папка-передвижка для родителей Суффиксные массивы

Суффиксные массивы K-P-T vaihtelu Nominityypit Vartalot Harjoitukset (1)

K-P-T vaihtelu Nominityypit Vartalot Harjoitukset (1) Internet

Internet  Самые смешные законы США

Самые смешные законы США Имидж, поведение, репутация как фактор жизненного успеха

Имидж, поведение, репутация как фактор жизненного успеха