Содержание

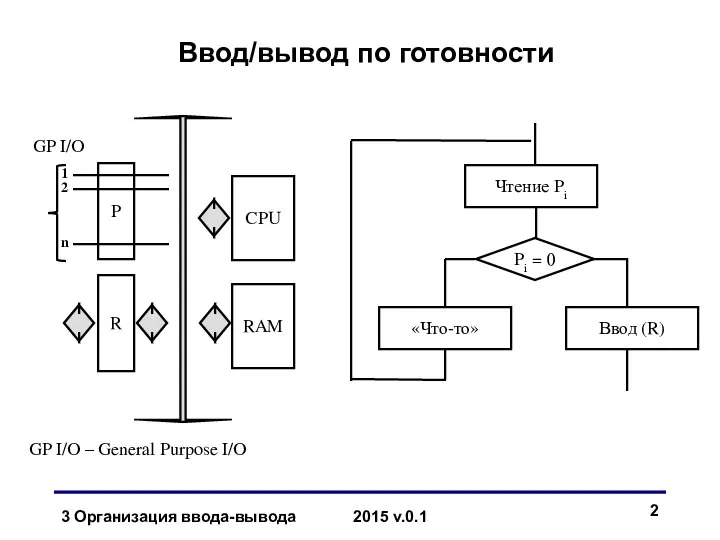

- 2. Ввод/вывод по готовности P CPU RAM R Чтение Pi Pi = 0 GP I/O GP I/O

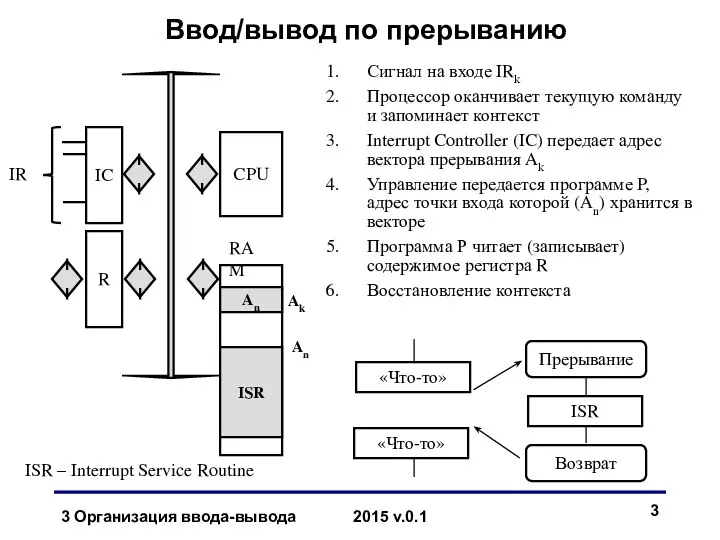

- 3. Ввод/вывод по прерыванию IC CPU R An ISR RAM Ak An IR Сигнал на входе IRk

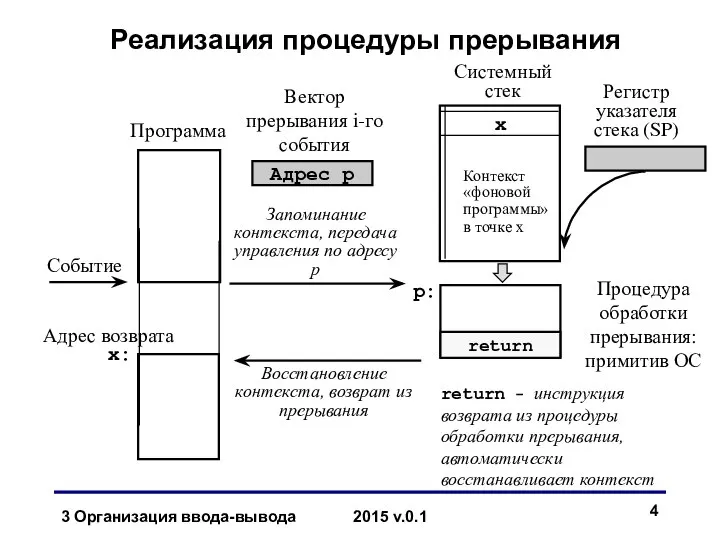

- 4. return x: Системный стек Процедура обработки прерывания: примитив ОС Программа Восстановление контекста, возврат из прерывания Контекст

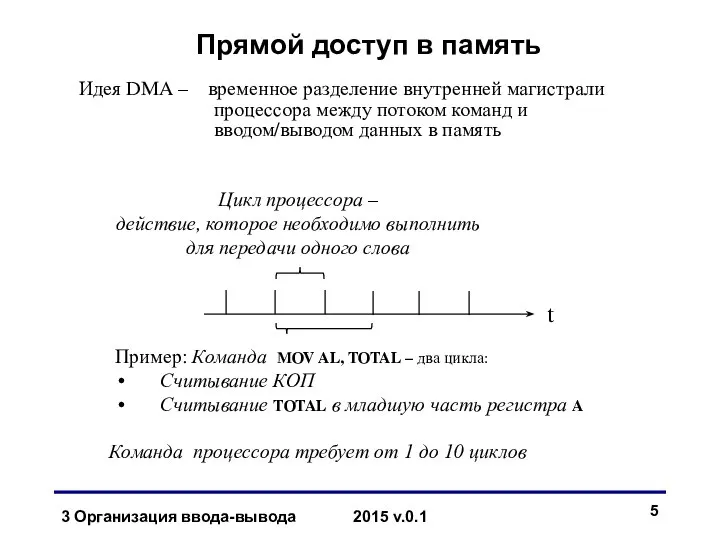

- 5. Прямой доступ в память Идея DMA – временное разделение внутренней магистрали процессора между потоком команд и

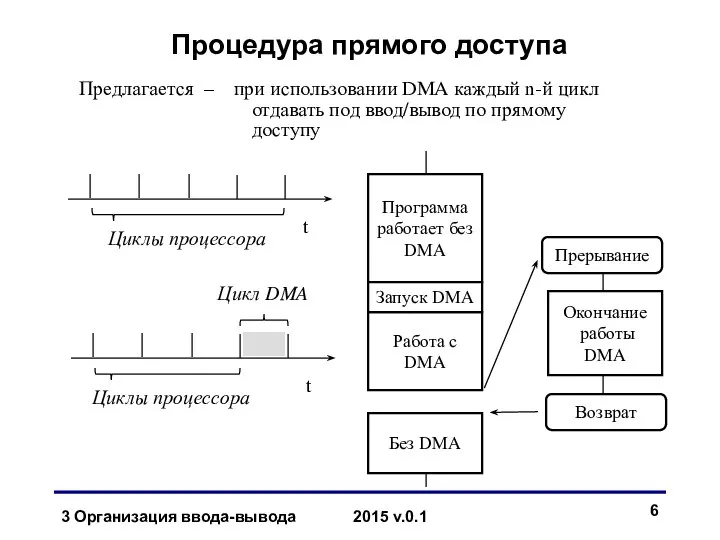

- 6. Процедура прямого доступа Предлагается – при использовании DMA каждый n-й цикл отдавать под ввод/вывод по прямому

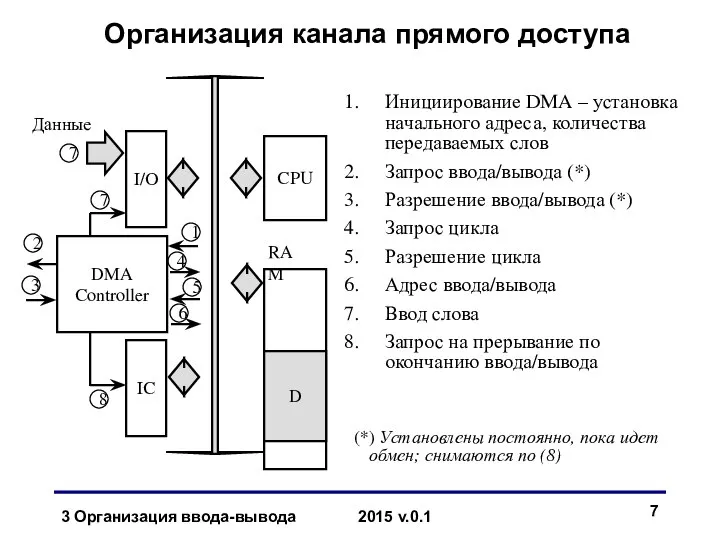

- 7. I/O CPU DMA Controller D RAM IC Данные 7 Организация канала прямого доступа Инициирование DMA –

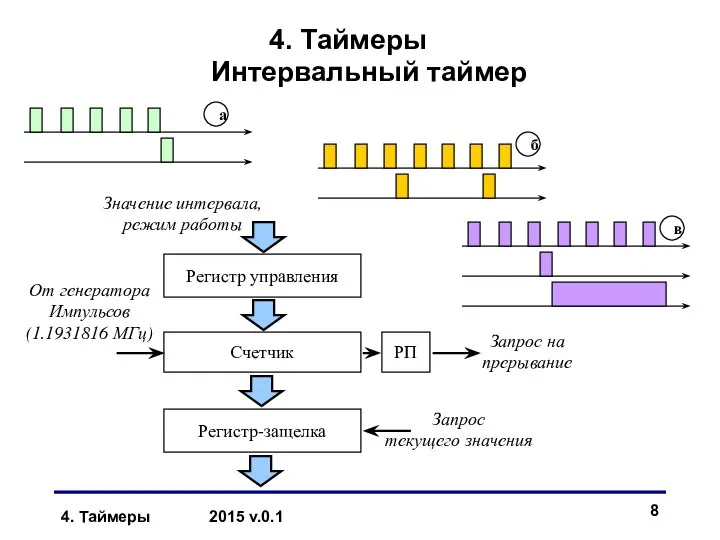

- 8. 4. Таймеры 2015 v.0.1 4. Таймеры Интервальный таймер Запрос на прерывание Счетчик Регистр-защелка От генератора Импульсов

- 9. Интервальный таймер, пример: i8254 Периодические запросы на прерывание Однократные запросы на Прерывание Генератор сигналов заданной длительности,

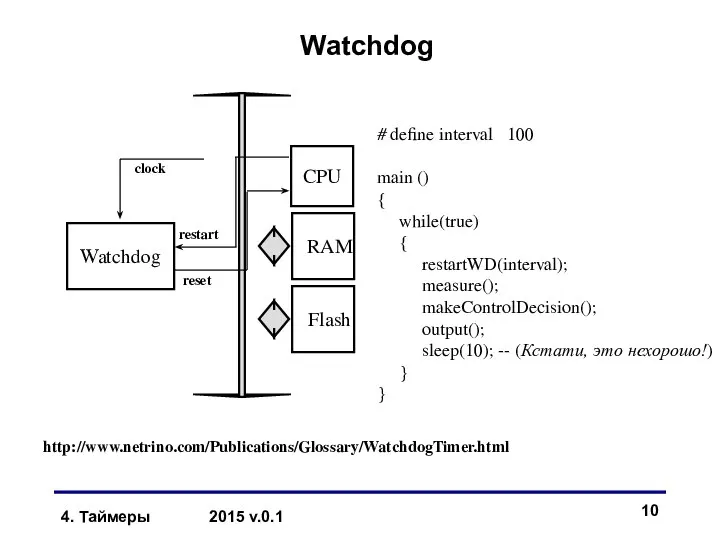

- 10. http://www.netrino.com/Publications/Glossary/WatchdogTimer.html Watchdog # define interval 100 main () { while(true) { restartWD(interval); measure(); makeControlDecision(); output(); sleep(10);

- 12. Скачать презентацию

Уявіть, що ви туристи, які подорожують до однієї з найзагадковіших країн світу

Уявіть, що ви туристи, які подорожують до однієї з найзагадковіших країн світу Practical work №9. Internet Technology

Practical work №9. Internet Technology Эйвон. Инструкция по отправке заказа

Эйвон. Инструкция по отправке заказа РЛО Т2.1.ppt

РЛО Т2.1.ppt Нормативно-правовые документы, обеспечивающие функционирование КСЗИ

Нормативно-правовые документы, обеспечивающие функционирование КСЗИ Кондрашин Владимир Петрович

Кондрашин Владимир Петрович Организационные стандарты кредитного кооператива Стратьева Елена Сергеевна, директор кредитного потребительского кооперати

Организационные стандарты кредитного кооператива Стратьева Елена Сергеевна, директор кредитного потребительского кооперати Презентация на тему "Холера" - скачать презентации по Медицине

Презентация на тему "Холера" - скачать презентации по Медицине East Germanic Languages

East Germanic Languages Методика развития физических способностей

Методика развития физических способностей Тема 2. Человек в организации

Тема 2. Человек в организации  Национальные костюмы народов России

Национальные костюмы народов России Статистические характеристики на уроке алгебры

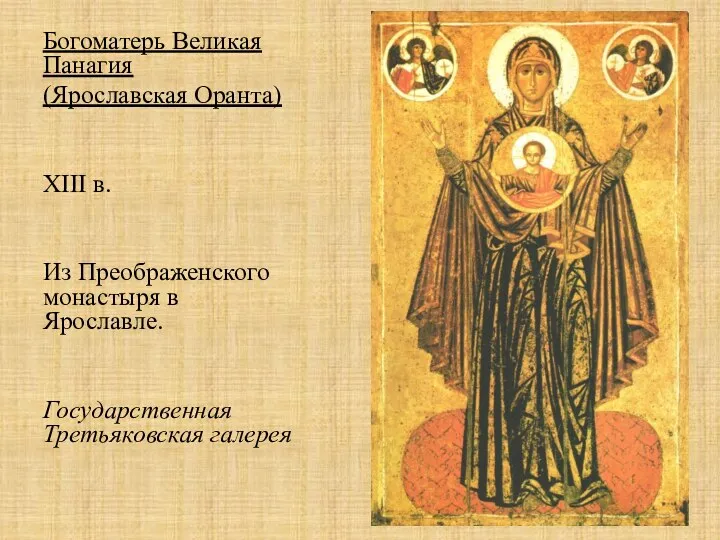

Статистические характеристики на уроке алгебры ВЕЛИКАЯ ПАНАГИЯ

ВЕЛИКАЯ ПАНАГИЯ Политическая система общества

Политическая система общества Екатерина Мазуренко, АО «Ветропак Гостомельский Стеклозавод» Стеклянная бутылка как средство маркетингового продвижения VII Меж

Екатерина Мазуренко, АО «Ветропак Гостомельский Стеклозавод» Стеклянная бутылка как средство маркетингового продвижения VII Меж Оценка эффективности ажиотажного маркетинга в социальных медиа Агентство веб-коммуникаций ErstMedia. - презентация

Оценка эффективности ажиотажного маркетинга в социальных медиа Агентство веб-коммуникаций ErstMedia. - презентация Логические задания!

Логические задания! Вероятностные модели управления запасами

Вероятностные модели управления запасами Показательные примеры активной процессуальной позиции кредиторов. (Лекция 5)

Показательные примеры активной процессуальной позиции кредиторов. (Лекция 5) Открытый классный час для учащихся 1-х классов. «Праздник вежливых ребят».

Открытый классный час для учащихся 1-х классов. «Праздник вежливых ребят». Презентация "Экономика России в 15-16 веках" - скачать презентации по Экономике

Презентация "Экономика России в 15-16 веках" - скачать презентации по Экономике Викторина «Йошкар-Оле 430 лет»

Викторина «Йошкар-Оле 430 лет» пороки развития и трансплант

пороки развития и трансплант Презентация по алгебре Формула суммы первых n членов арифметической прогрессии

Презентация по алгебре Формула суммы первых n членов арифметической прогрессии  Электрооборудование токарных сtahкob

Электрооборудование токарных сtahкob Формирование оценочных умений на уроках физики Заместитель директора по УВР, учитель физики Гришина Т.А. Еринская средняя школа 20

Формирование оценочных умений на уроках физики Заместитель директора по УВР, учитель физики Гришина Т.А. Еринская средняя школа 20 Пути развития малого и среднего бизнеса на рынке электроники России.

Пути развития малого и среднего бизнеса на рынке электроники России.