Содержание

- 2. Механизм процессов и концепция сигнала В VHDL При программировании на VHDL нужно учитывать две особенности: моделирование

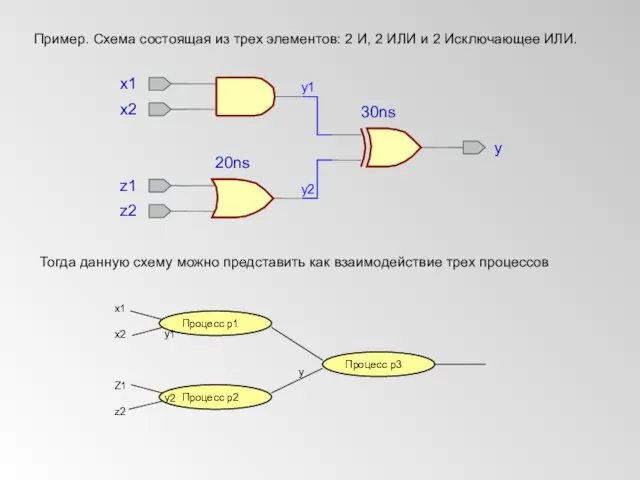

- 3. Пример. Схема состоящая из трех элементов: 2 И, 2 ИЛИ и 2 Исключающее ИЛИ. Тогда данную

- 4. Процессы p1,p2,p3 описываются в VHDL следующим образом: P1: process (x1,x2) begin . . . функционирование элемента

- 5. В VHDL есть два типа сигналов: ports - порты - это внешние входы и выходы ОП:

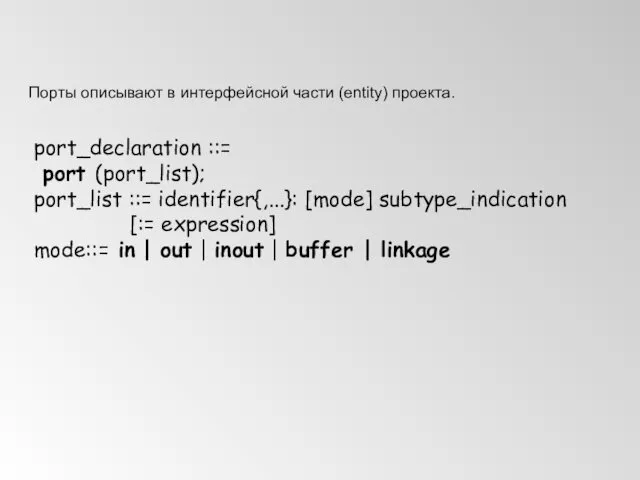

- 6. Порты описывают в интерфейсной части (entity) проекта. port_declaration ::= port (port_list); port_list ::= identifier{,...}: [mode] subtype_indication

- 8. Декларация внутреннего сигнала signal_declaration ::= signal identifier{,...}: subtype_indication [:= expression] architecture arch_name of entity_name is {

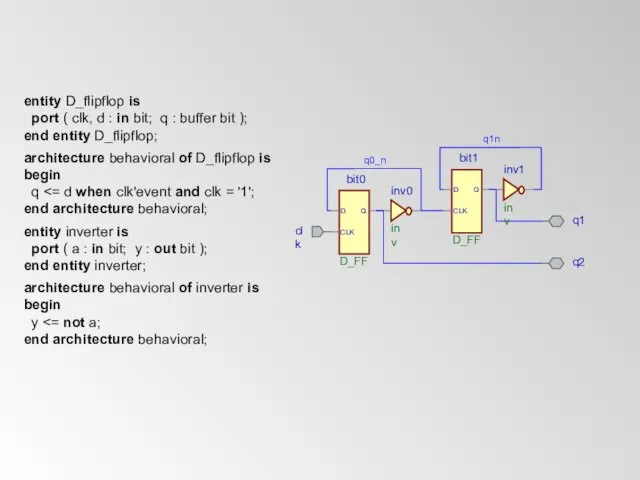

- 10. entity D_flipflop is port ( clk, d : in bit; q : buffer bit ); end

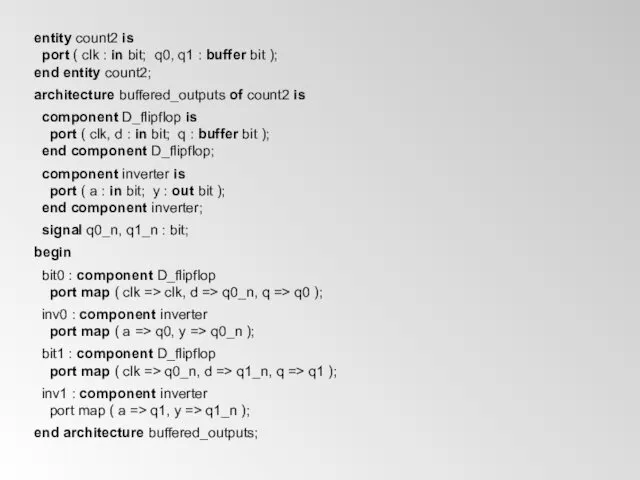

- 11. entity count2 is port ( clk : in bit; q0, q1 : buffer bit ); end

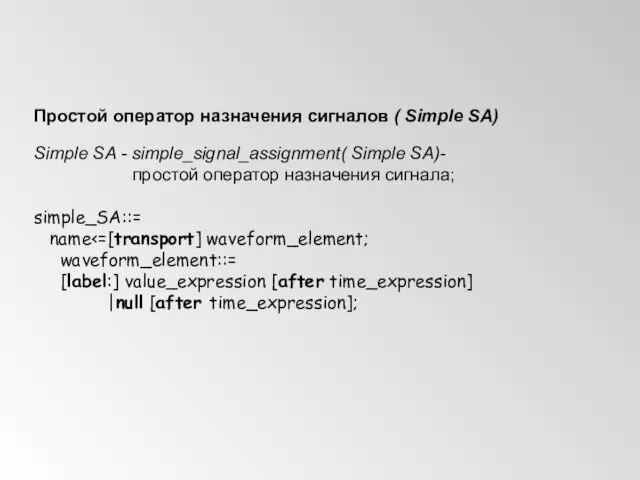

- 12. Простой оператор назначения сигналов ( Simple SA) Simple SA - simple_signal_assignment( Simple SA)- простой оператор назначения

- 13. Разновидности (Simple SA): - concurrent Simple SA (CSA) – параллельный простой оператор назначения сигнала; - siquential

- 14. Область действий CSA: - архитектура - блок

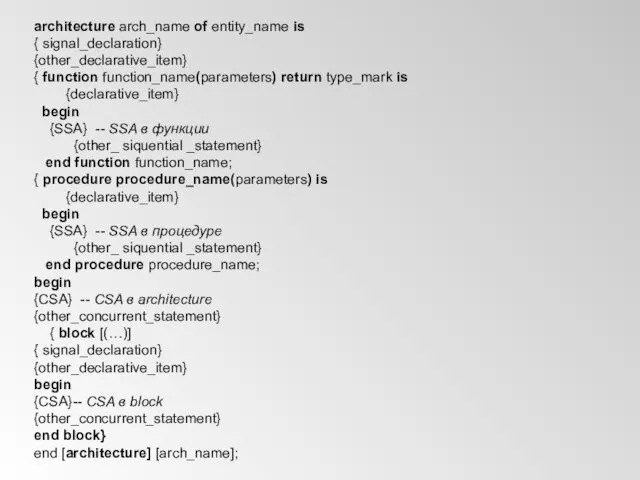

- 15. architecture arch_name of entity_name is { signal_declaration} {other_declarative_item} begin {CSA} -- CSA в архитектуре {other_concurrent_statement} {

- 16. Область действий SSA: - процесс - процедура - функция

- 17. architecture arch_name of entity_name is { signal_declaration} {other_declarative_item} { function function_name(parameters) return type_mark is {declarative_item} begin

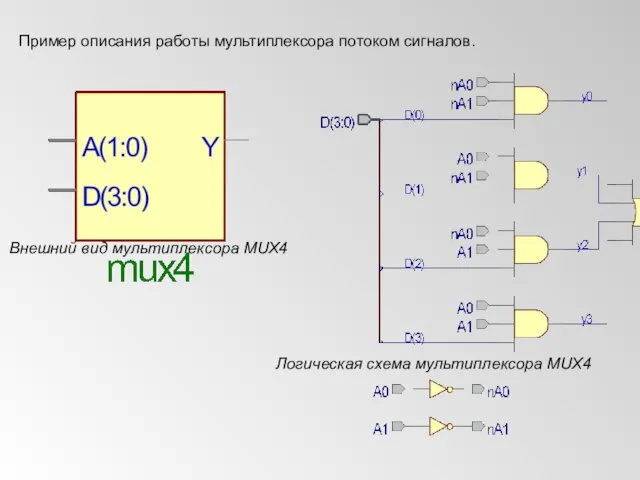

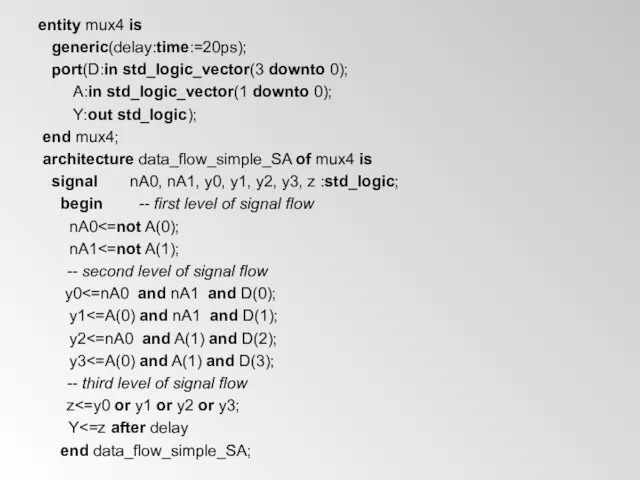

- 18. Пример описания работы мультиплексора потоком сигналов. Внешний вид мультиплексора MUX4 Логическая схема мультиплексора MUX4

- 19. entity mux4 is generic(delay:time:=20ps); port(D:in std_logic_vector(3 downto 0); A:in std_logic_vector(1 downto 0); Y:out std_logic); end mux4;

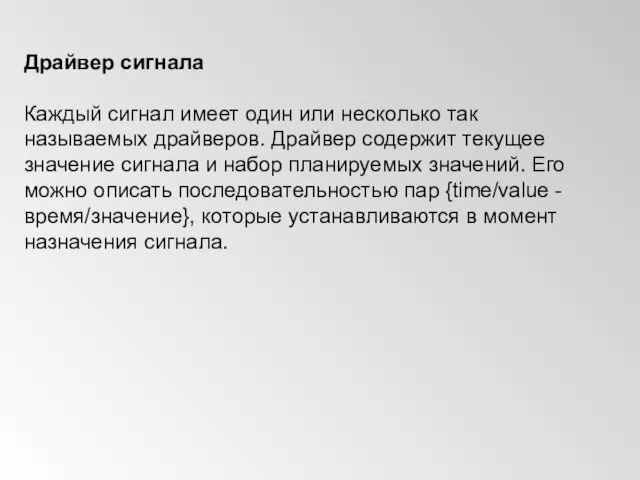

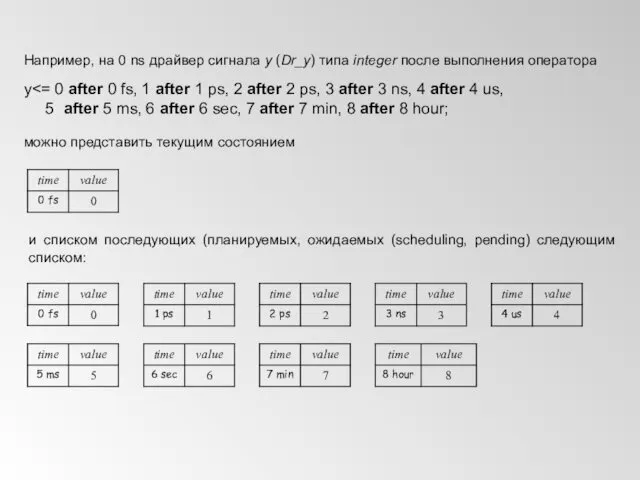

- 20. Драйвер сигнала Каждый сигнал имеет один или несколько так называемых драйверов. Драйвер содержит текущее значение сигнала

- 21. Например, на 0 ns драйвер сигнала y (Dr_y) типа integer после выполнения оператора y 5 after

- 22. Сигнал имеет несколько драйверов, если количество источников сигнала превышает 1, например при 2-направленных и трехстабильных цепей

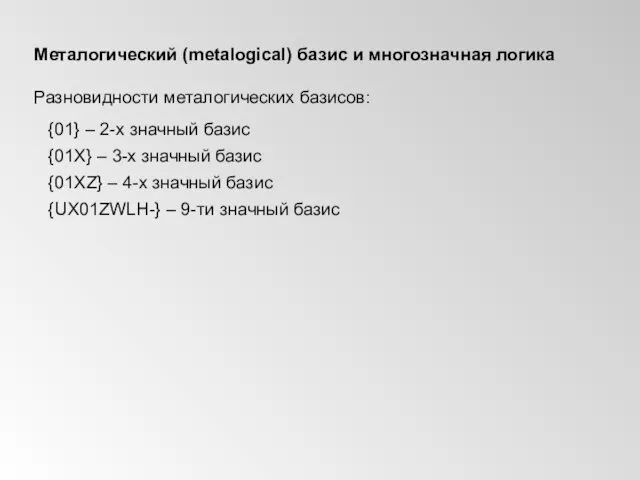

- 23. Металогический (metalogical) базис и многозначная логика Разновидности металогических базисов: {01} – 2-х значный базис {01Х} –

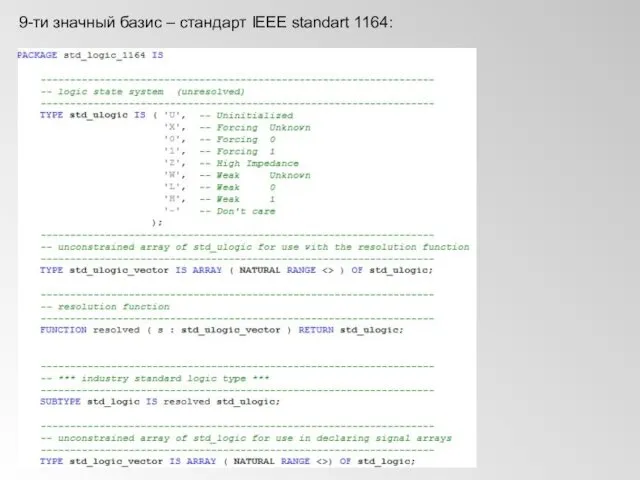

- 24. 9-ти значный базис – стандарт IEEE standart 1164:

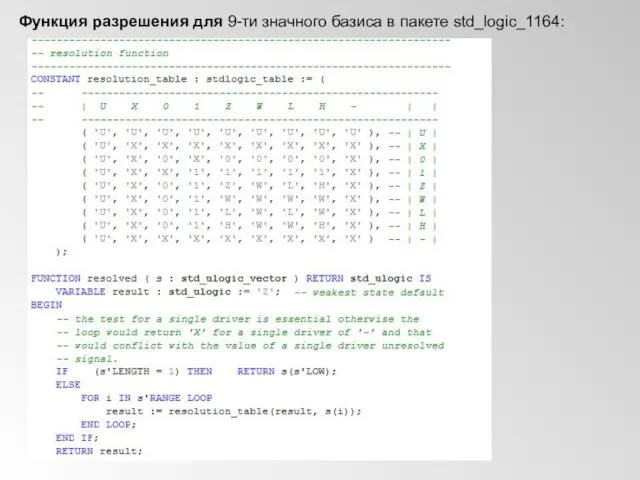

- 25. Функция разрешения для 9-ти значного базиса в пакете std_logic_1164:

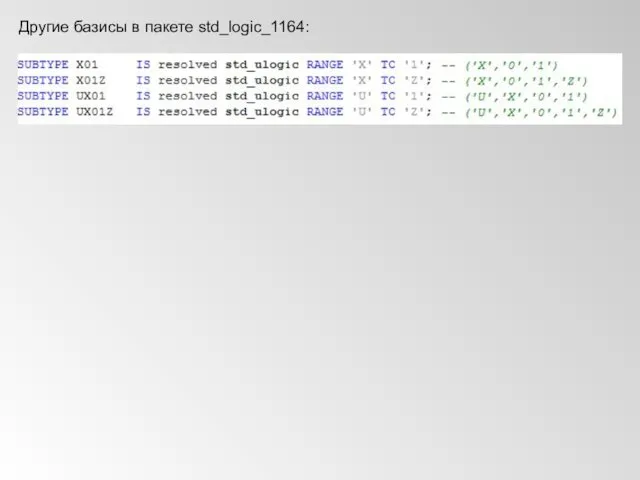

- 26. Другие базисы в пакете std_logic_1164:

- 27. Многозначная логика – это логические операции над операндами, имеющими более 2-х значений. В пакете std_logic_1164:

- 28. Реализация логических функций в 9-ти значном базисе в пакете std_logic_1164:

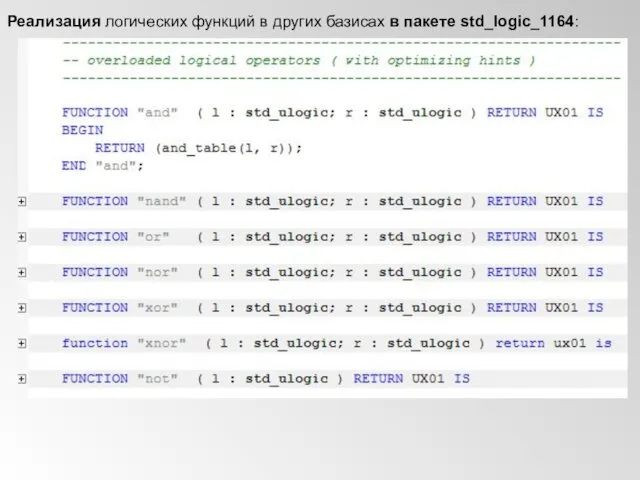

- 29. Реализация логических функций в других базисах в пакете std_logic_1164:

- 30. Моделирование задержек сигналов Простой оператор назначения сигналов simple_SA::= [Label:] signal_name waveform ::= {transaction} {,transaction} transaction::= value_expression

- 31. Разновидности задержек сигналов: - transport - транспортная - inertial - инерционная - reject inertial – инерционная

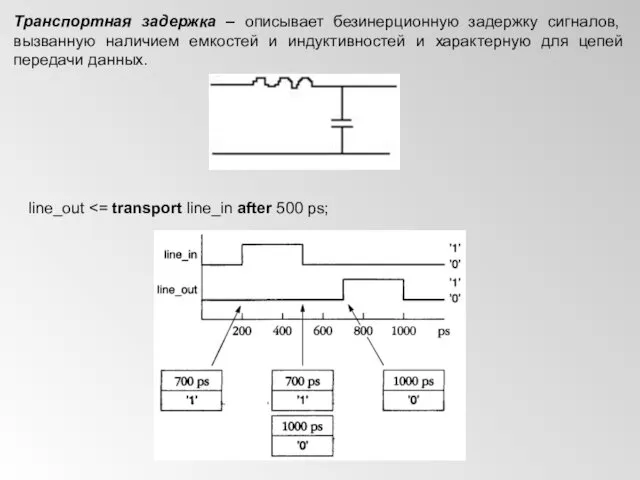

- 32. Транспортная задержка – описывает безинерционную задержку сигналов, вызванную наличием емкостей и индуктивностей и характерную для цепей

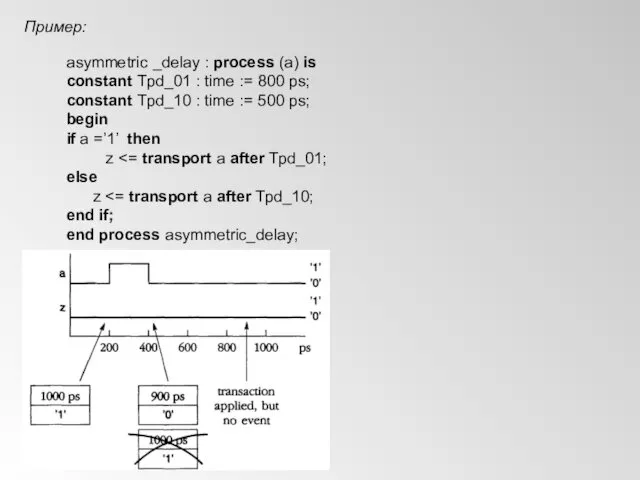

- 33. Пример: asymmetric _delay : process (a) is constant Tpd_01 : time := 800 ps; constant Tpd_10

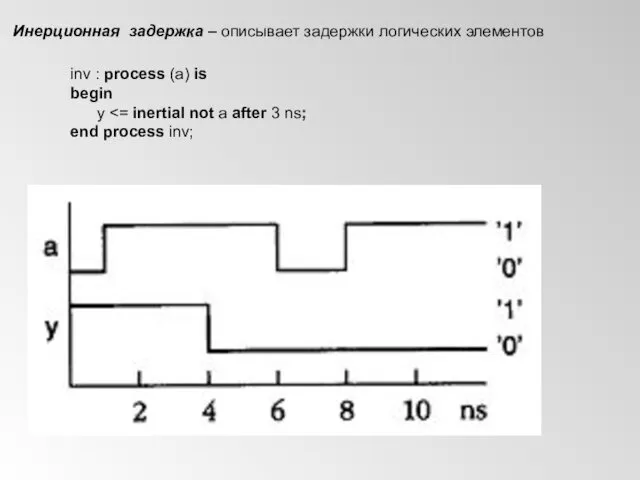

- 34. Инерционная задержка – описывает задержки логических элементов inv : process (a) is begin y end process

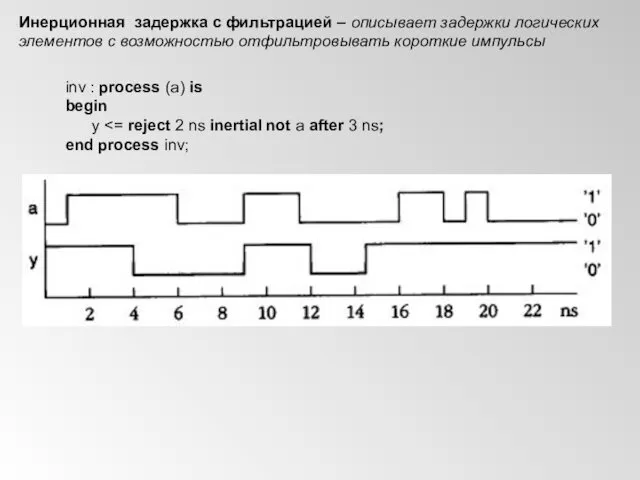

- 35. Инерционная задержка с фильтрацией – описывает задержки логических элементов с возможностью отфильтровывать короткие импульсы inv :

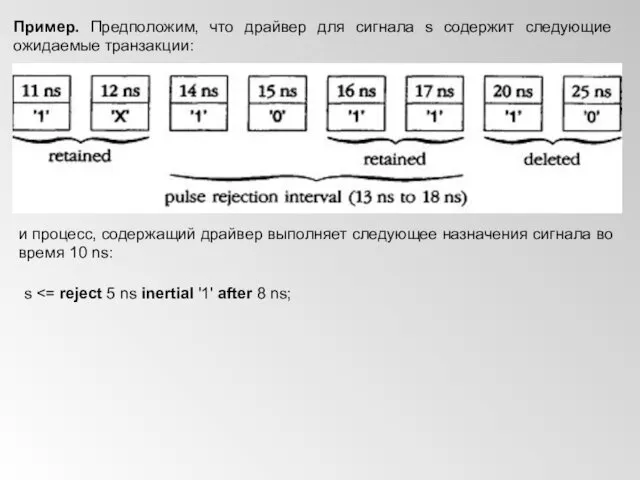

- 36. Пример. Предположим, что драйвер для сигнала s содержит следующие ожидаемые транзакции: и процесс, содержащий драйвер выполняет

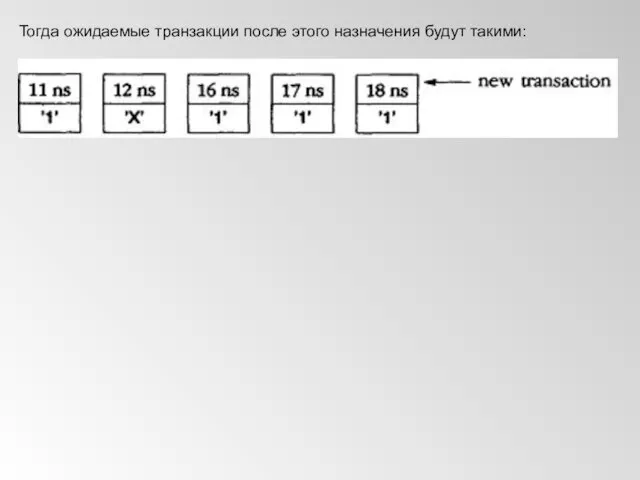

- 37. Тогда ожидаемые транзакции после этого назначения будут такими:

- 38. Дельта задержка Delta delay - ∆ Все процессы в VHDL делятся на три вида: - active

- 39. Итерационный алгоритм работы VHDL-программы:

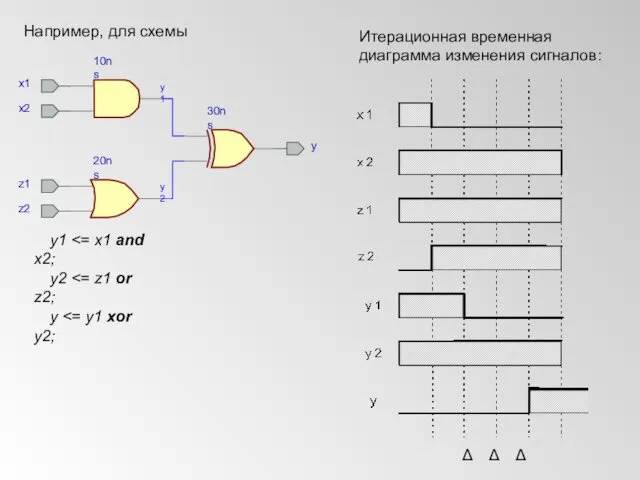

- 40. Например, для схемы y1 y2 y Итерационная временная диаграмма изменения сигналов: Δ Δ Δ

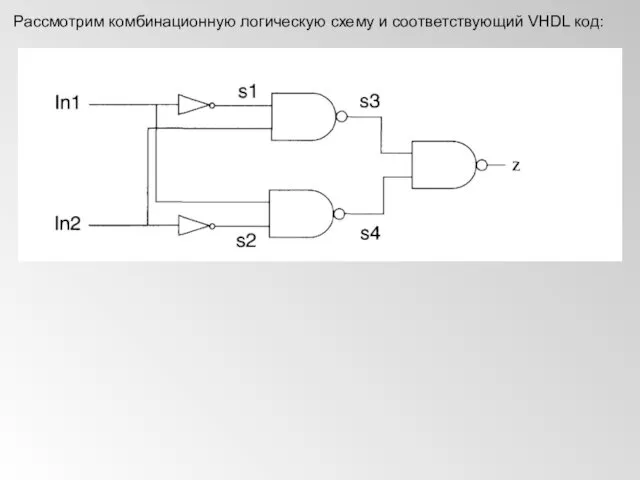

- 41. Рассмотрим комбинационную логическую схему и соответствующий VHDL код:

- 42. library IEEE; use IEEE.std_logic_1164.all; entity combinational is port (in1, in2: in std_logic; z : out std_logic);

- 43. Результаты моделирования комбинационной схемы

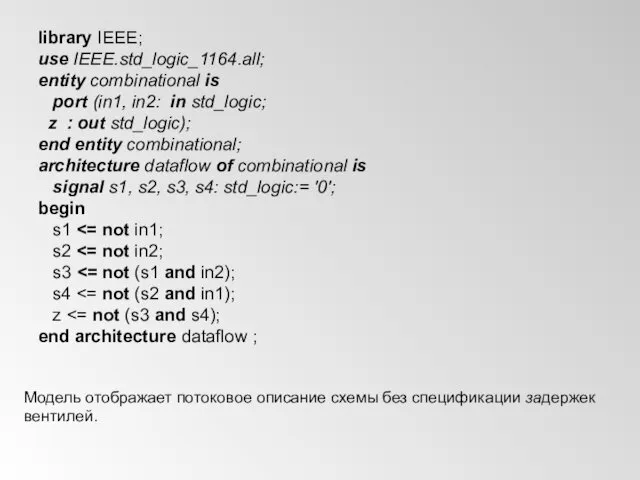

- 44. очередность дельта-событий (a) и отображение дельта-задержек (б) сигналов при моделировании;

- 45. Результаты итерационного моделирования комбинационной схемы

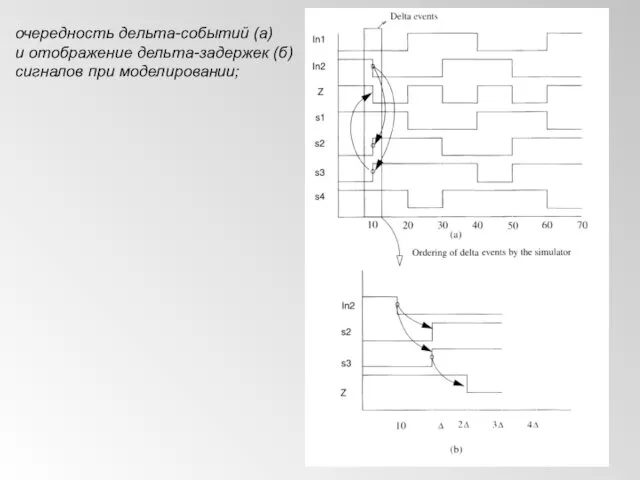

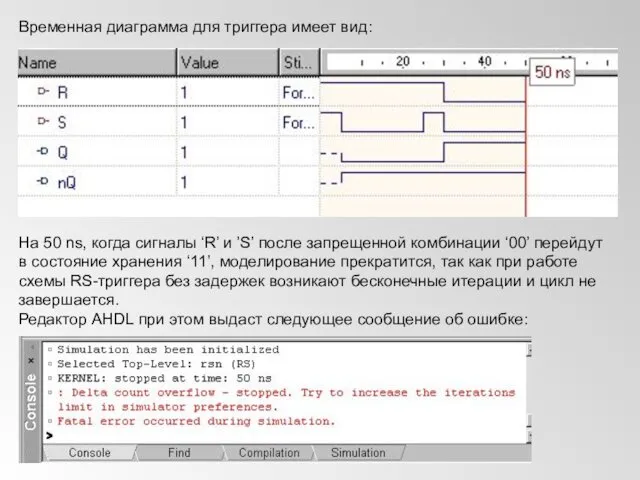

- 46. Пример моделирования RS-триггер без задержек в ЛЭ:

- 47. Временная диаграмма для триггера имеет вид: На 50 ns, когда сигналы ‘R’ и ’S’ после запрещенной

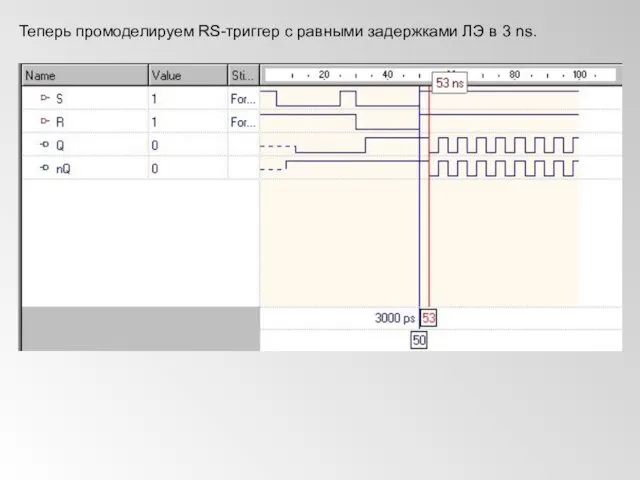

- 48. Теперь промоделируем RS-триггер с равными задержками ЛЭ в 3 ns.

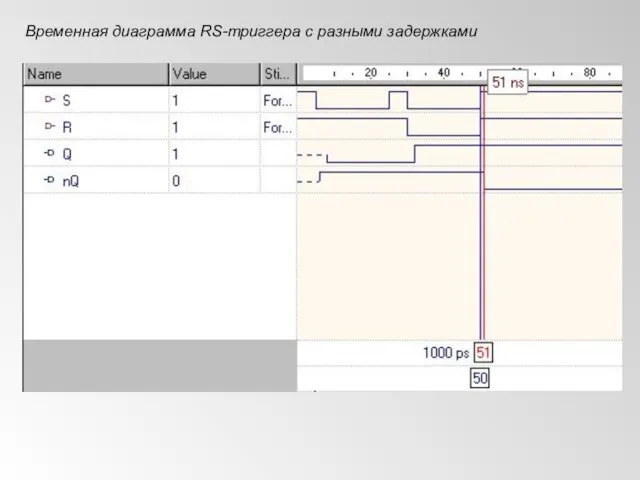

- 49. Временная диаграмма RS-триггера с разными задержками

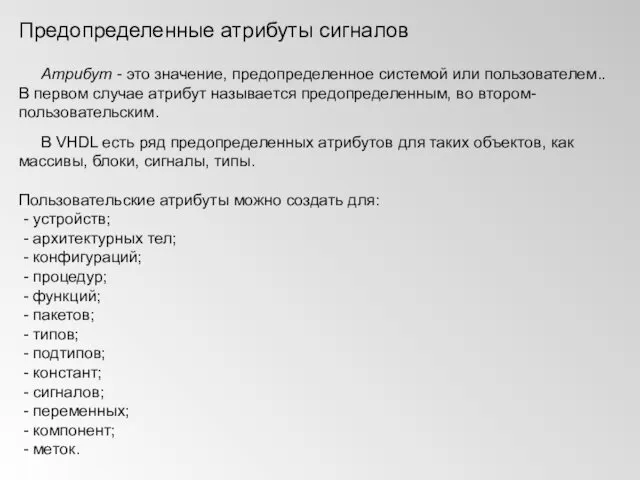

- 50. Предопределенные атрибуты сигналов Атрибут - это значение, предопределенное системой или пользователем.. В первом случае атрибут называется

- 51. attribute ::= prefix’ attribute_name[( expression )]

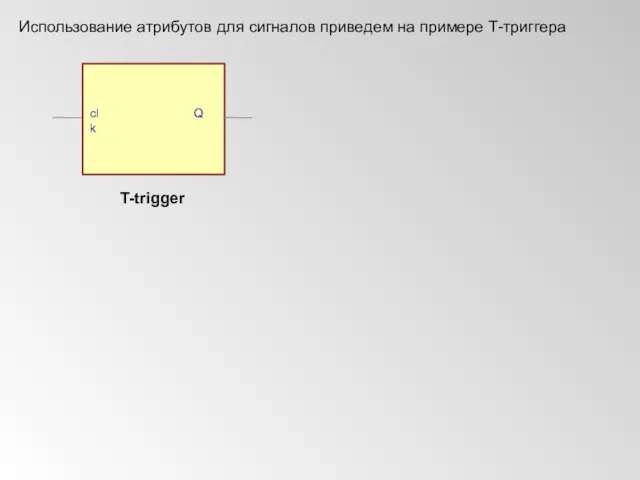

- 52. Использование атрибутов для сигналов приведем на примере Т-триггера T-trigger

- 53. VHDL-код для данного примера будет следующим entity T_FF is port( clk: in std_logic; Q: out std_logic);

- 55. Скачать презентацию

![Декларация внутреннего сигнала signal_declaration ::= signal identifier{,...}: subtype_indication [:= expression] architecture](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/496992/slide-7.jpg)

![Моделирование задержек сигналов Простой оператор назначения сигналов simple_SA::= [Label:] signal_name waveform](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/496992/slide-29.jpg)

![attribute ::= prefix’ attribute_name[( expression )]](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/496992/slide-50.jpg)

1_Введение в Web-разработку

1_Введение в Web-разработку Презентация "Устройства вывода информации. Оперативная и долговременная память" - скачать презентации по Информатике

Презентация "Устройства вывода информации. Оперативная и долговременная память" - скачать презентации по Информатике Режимы и способы обработки данных

Режимы и способы обработки данных Основні поняття комп'ютерної графіки

Основні поняття комп'ютерної графіки Вычислительные устройства и приборы, история вопроса. Эволюция ЭВМ. ААС 01

Вычислительные устройства и приборы, история вопроса. Эволюция ЭВМ. ААС 01 Памятка ДомКлик для клиента

Памятка ДомКлик для клиента Особенности построения системы и организации обучения по профессиям рабочих по специальности: Оператор компьютерной графики

Особенности построения системы и организации обучения по профессиям рабочих по специальности: Оператор компьютерной графики Час Кода. Классный час 5-9 класс

Час Кода. Классный час 5-9 класс Чат для обмена мгновенными сообщениями

Чат для обмена мгновенными сообщениями Понятие высказывания. Основные логические операции. Формулы логики

Понятие высказывания. Основные логические операции. Формулы логики Содержание сквозного курса информатики 7-11 класс Гилёв Сергей Григорьевич, учитель физики и информатики школы № 49

Содержание сквозного курса информатики 7-11 класс Гилёв Сергей Григорьевич, учитель физики и информатики школы № 49 Формирование образовательного контента для размещения в региональном репозитории

Формирование образовательного контента для размещения в региональном репозитории Информация и информационные процессы. Кодирование информации

Информация и информационные процессы. Кодирование информации Хозяйство Беларуси (инфографика)

Хозяйство Беларуси (инфографика) Вирусы и антивирусные программы (10 класс) - Презентация_

Вирусы и антивирусные программы (10 класс) - Презентация_ Разработка программы управления шаговым двигателем при помощи Arduino через драйвер А4988

Разработка программы управления шаговым двигателем при помощи Arduino через драйвер А4988 Информатика и информация

Информатика и информация Виды компьютерных вирусов Подготовила: Жигалова Катя Проверила: Выпрева Вера Владимировна

Виды компьютерных вирусов Подготовила: Жигалова Катя Проверила: Выпрева Вера Владимировна Основные логические операции

Основные логические операции Моделирование, как метод познания. Общие свойства моделей

Моделирование, как метод познания. Общие свойства моделей Алгоритм. Свойства алгоритма

Алгоритм. Свойства алгоритма Разработка ИС с распределенным доступом для межведомственного обмена информацией

Разработка ИС с распределенным доступом для межведомственного обмена информацией Интелектуалды жүйелер

Интелектуалды жүйелер ZPG Ульбор

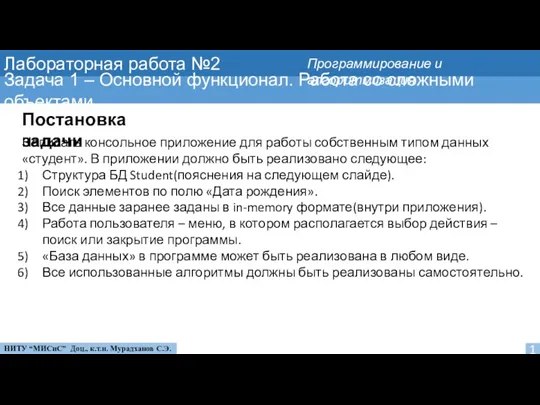

ZPG Ульбор Программирование и алгоритмизация. Лабораторная работа №2

Программирование и алгоритмизация. Лабораторная работа №2 Компьютерные и дистанционные технологии в образовании

Компьютерные и дистанционные технологии в образовании Аппаратные ключи защиты

Аппаратные ключи защиты Алгоритмическая структура ветвления

Алгоритмическая структура ветвления